## TMS320C6000 Technical Brief

Literature Number: SPRU197D February 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

#### **Preface**

### **Read This First**

#### About This Manual

This book is an introduction to the TMS320C6000 platform of digital signal processor (DSP) devices. This book describes the CPU architecture, peripherals, and development tools for the TMS320C6000 DSPs. Unless otherwise specified, all references to the 'C6000 refer to the TMS320C6000 platform of DSPs, 'C62x refers to the TMS320C62x fixed-point DSPs in the 'C6000 platform, and 'C67x refers to the TMS320C67x floating-point DSPs in the 'C6000 platform.

#### How to Use This Manual

The following table summarizes the information in this technical brief:

| If you are looking for information about: | Turn to these chapters:        |

|-------------------------------------------|--------------------------------|

| Code generation tools                     | Chapter 5, Development Support |

| CPU architecture                          | Chapter 2, CPU Architecture    |

| Development support tools                 | Chapter 5, Development Support |

| Direct-memory access (DMA)                | Chapter 4, Peripherals         |

| Evaluation tools                          | Chapter 5, Development Support |

| External memory interface                 | Chapter 3, Memory              |

|                                           | Chapter 4, Peripherals         |

| Host-port interface                       | Chapter 4, Peripherals         |

| Memory map                                | Chapter 3, <i>Memory</i>       |

| Multichannel buffered serial port (McBSP) | Chapter 4, Peripherals         |

| Peripherals                               | Chapter 4, <i>Peripherals</i>  |

| Timers                                    | Chapter 4, Peripherals         |

|                                           |                                |

#### Related Documentation From Texas Instruments

The following books describe the TMS320C62x/C67x devices and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320C6201 Digital Signal Processor Data Sheet** (literature number SPRS051) describes the features of the TMS320C6201 and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6202 Digital Signal Processor Data Sheet** (literature number SPRS072) describes the features of the TMS320C6202 and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6211 Digital Signal Processor Data Sheet** (literature number SPRS073) describes the features of the TMS320C6211 and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6701 Digital Signal Processor Data Sheet** (literature number SPRS067) describes the features of the TMS320C6701 and provides pinouts, electrical specifications, and timings for the device.

- TMS320C62x/C67x CPU and Instruction Set Reference Guide (literature number SPRU189) describes the 'C62x/C67x CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- TMS320C6201/C6701 Peripherals Reference Guide (literature number SPRU190) describes common peripherals available on the TMS320C6201/C6701 digital signal processors. This book includes information on the internal data and program memories, the external memory interface (EMIF), the host port, multichannel buffered serial ports, direct memory access (DMA), clocking and phase-locked loop (PLL), and the power-down modes.

- TMS320C6202/C6211 Peripheral Addendum to the TMS320C6201/C6701 Peripherals Reference Guide (literature number SPRU290) describes common peripherals available on the TMS320C6202/C6211 digital signal processors. This book includes information on the internal data and program memories, the external memory interface (EMIF), the host port, multichannel buffered serial ports, direct memory access (DMA), clocking and phase-locked loop (PLL), and the power-down modes.

- **TMS320C62x/C67x Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C62x/C67x DSPs and includes application program examples.

- **TMS320C6x Assembly Language Tools User's Guide** (literature number SPRU186) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C6x generation of devices.

- TMS320C6x Optimizing C Compiler User's Guide (literature number SPRU187) describes the 'C6x C compiler and the assembly optimizer. This C compiler accepts ANSI standard C source code and produces assembly language source code for the 'C6x generation of devices. The assembly optimizer helps you optimize your assembly code.

- TMS320C6x C Source Debugger User's Guide (literature number SPRU188) tells you how to invoke the 'C6x simulator and emulator versions of the C source debugger interface. This book discusses various aspects of the debugger, including command entry, code execution, data management, breakpoints, profiling, and analysis.

- TMS320 DSP Development Support Reference Guide (literature number SPRU011) describes the TMS320 family of digital signal processors and the tools that support these devices. Included are code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). Also covered are available documentation, seminars, the university program, and factory repair and exchange.

#### **Trademarks**

Classico, MicroLite, and Virtuoso Nano are trademarks of Eonic Systems, Inc.

Code Composer and Code Maestro are trademarks of GO DSP Corporation.

EVP is a trademark of D2 Technologies.

InvisiLink is a trademark of ViaDSP, Inc.

PC is a trademark of International Business Machines Corporation.

Solaris, SunOS, and Sun-3 are trademarks of Sun Microsystems, Inc.

SPI is a trademark of Motorola, Inc.

320 Hotline On-line, TI, VelociTI, XDS510, and XDS510WS are trademarks of Texas Instruments Incorporated.

Windows and Windows NT are registered trademarks of Microsoft Corporation.

#### If You Need Assistance . . .

|        | World-Wide Web Sites                                                   |                                         |                                                             |

|--------|------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------|

|        | TI Online                                                              | http://www.ti.con                       | n                                                           |

|        | Semiconductor Product Information Center (PIC)                         |                                         | n/sc/docs/pic/home.htm                                      |

|        | DSP Solutions                                                          | http://www.ti.con                       |                                                             |

|        | 320 Hotline On-line ™                                                  |                                         | n/sc/docs/dsps/support.htm                                  |

|        | North America, South America, Ce                                       | ntral Amarica                           |                                                             |

| _      |                                                                        |                                         |                                                             |

|        | Product Information Center (PIC)                                       | (972) 644-5580                          |                                                             |

|        | TI Literature Response Center U.S.A.                                   | (800) 477-8924                          | Fov: (244) 620 7742                                         |

|        | Software Registration/Upgrades U.S.A. Factory Repair/Hardware Upgrades | (214) 638-0333                          | Fax: (214) 638-7742                                         |

|        | U.S. Technical Training Organization                                   | (281) 274-2285<br>(972) 644-5580        |                                                             |

|        | DSP Hotline                                                            | (281) 274-2320                          | Fax: (281) 274-2324                                         |

|        | DSP Modem BBS                                                          | (281) 274-2323                          | 1 ax. (201) 214 2024 Email: dopine ti.com                   |

|        | DSP Internet BBS via anonymous ftp to ftp://ft                         | ` '                                     | 0bbs                                                        |

|        |                                                                        | , , , , , , , , , , , , , , , , , , , , |                                                             |

| l⊐.    | Europe, Middle East, Africa                                            | LL de                                   |                                                             |

|        | European Product Information Center (EPIC)                             |                                         | Fa 122 4 20 70 40 22                                        |

|        | 0 0 11                                                                 | +33 1 30 70 11 69                       | Fax: +33 1 30 70 10 32                                      |

|        | Email: epic@ti.com  Deutsch +49 8161 80 33 11 or -                     | . 22 4 20 70 44 60                      |                                                             |

|        |                                                                        | +33 1 30 70 11 66                       |                                                             |

|        | <u> </u>                                                               | +33 1 30 70 11 63                       |                                                             |

|        |                                                                        | +33 1 30 70 11 67                       |                                                             |

|        |                                                                        | +33 1 30 70 11 99                       |                                                             |

|        |                                                                        | +33 4 93 22 25 40                       |                                                             |

|        | Europe Customer Training Helpline                                      |                                         | Fax: +49 81 61 80 40 10                                     |

| $\Box$ | Asia-Pacific                                                           |                                         |                                                             |

| Ι".    | Literature Response Center                                             | +852 2 956 7288                         | Fax: +852 2 956 2200                                        |

|        | Hong Kong DSP Hotline                                                  | +852 2 956 7268                         |                                                             |

|        | Korea DSP Hotline                                                      | +82 2 551 2804                          | Fax: +82 2 551 2828                                         |

|        | Korea DSP Modem BBS                                                    | +82 2 551 2914                          | 1 dx. 102 2 00 1 2020                                       |

|        | Singapore DSP Hotline                                                  |                                         | Fax: +65 390 7179                                           |

|        | Taiwan DSP Hotline                                                     | +886 2 377 1450                         | Fax: +886 2 377 2718                                        |

|        | Taiwan DSP Modem BBS                                                   | +886 2 376 2592                         |                                                             |

|        | Taiwan DSP Internet BBS via anonymous ftp t                            | to ftp://dsp.ee.tit.edu                 | u.tw/pub/TI/                                                |

|        | Japan                                                                  |                                         |                                                             |

|        | -                                                                      | 1-0026 (in Japan)                       | Fax: +0120-81-0036 (in Japan)                               |

|        | +03-3457-0972 or (INT                                                  | ` ' '                                   | Fax: +03-3457-1259 or (INTL) 813-3457-1259                  |

|        | DSP Hotline +03-3769-8735 or (INT                                      | ,                                       | Fax: +03-3457-7071 or (INTL) 813-3457-7071                  |

|        | DSP BBS via Nifty-Serve                                                | Type "Go TIASP"                         | , , , , , , , , , , , , , , , , , , , ,                     |

|        | Documentation                                                          |                                         |                                                             |

| Ι'''   |                                                                        | n documentation inle                    | ease include the following information that is on the title |

|        | page: the full title of the book, the publication of                   |                                         | <u> </u>                                                    |

|        | Mail: Texas Instruments Incorporated                                   | aate, and the intelati                  | Email: dsph@ti.com                                          |

|        | Technical Documentation Services,                                      | MS 702                                  | Email doping mooni                                          |

|        | P.O. Box 1443                                                          |                                         |                                                             |

|        | Houston, Texas 77251-1443                                              |                                         |                                                             |

|        | When calling a Literature Pospense Cont                                |                                         | ntation, please specify the literature number of the        |

**Note:** When calling a Literature Response Center to order documentation, please specify the literature number of the book.

## **Contents**

| 1 | Intro      | duction                  |                                                                                                                                            | . 1-1 |

|---|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   |            | ribes the<br>al applica  | e main features of the TMS320C62x/C67x devices, the history of TI DSPs, anations.                                                          | d     |

|   | 1.1        | The TN<br>1.1.1<br>1.1.2 | MS320 Family of Digital Signal Processors  History, Development, and Advantages of TMS320 DSPs  Typical Applications for the TMS320 Family | . 1-2 |

|   | 1.2<br>1.3 |                          | es and Options of the TMS320C62x/C67x Deviceses                                                                                            |       |

| 2 | Desci      | ribes the                | cture                                                                                                                                      |       |

|   | 2.1        | TMS32                    | 20C62x/C67x Block Diagram                                                                                                                  | . 2-2 |

|   | 2.2        |                          | I Processing Unit (CPU)                                                                                                                    |       |

|   | 2.3        |                          | ata Paths                                                                                                                                  |       |

|   |            | 2.3.1                    | General-Purpose Register Files                                                                                                             | . 2-4 |

|   |            | 2.3.2                    | Functional Units                                                                                                                           | . 2-7 |

|   |            | 2.3.3                    | TMS320C62x/C67x Control Register Files                                                                                                     | . 2-8 |

|   |            | 2.3.4                    | TMS320C67x Control Register File Extensions                                                                                                | . 2-9 |

|   |            | 2.3.5                    | Register File Cross Paths                                                                                                                  | . 2-9 |

|   |            | 2.3.6                    | Memory, Load, and Store Paths                                                                                                              | 2-10  |

|   |            | 2.3.7                    | Data-Address Paths                                                                                                                         | 2-10  |

|   | 2.4        | Mappir                   | ng Between Instructions and Functional Units                                                                                               | 2-11  |

|   | 2.5        | Addres                   | sing Modes                                                                                                                                 | 2-18  |

|   | 2.6        | Interru                  | ots                                                                                                                                        | 2-19  |

| 3 |       | ory                                                                                   | 3-1    |

|---|-------|---------------------------------------------------------------------------------------|--------|

|   | Desci | ribes the on-chip memory and external memory access.                                  |        |

|   | 3.1   | Memory Maps                                                                           | 3-2    |

|   | 3.2   | Internal Memory                                                                       | 3-4    |

|   |       | 3.2.1 TMS320C6201 (Revision 2)                                                        | 3-4    |

|   |       | 3.2.2 TMS320C6201B (Revision 3)                                                       |        |

|   |       | 3.2.3 TMS320C6701                                                                     | 3-5    |

|   |       | 3.2.4 TMS320C6202                                                                     | 3-6    |

|   |       | 3.2.5 TMS320C6211                                                                     | 3-6    |

|   |       | 3.2.6 Data Memory Access                                                              | 3-7    |

|   |       | 3.2.7 TMS320C6201, 'C6202, 'C6701                                                     |        |

|   |       | 3.2.8 TMS320C6211                                                                     |        |

|   |       | 3.2.9 Peripheral Bus                                                                  |        |

|   |       | 3.2.10 Expansion Bus                                                                  |        |

|   | 3.3   | External Memory Interface (EMIF)                                                      |        |

|   |       |                                                                                       |        |

| 4 | -     | pherals                                                                               |        |

|   |       | cribes the peripherals available for the TMS320C62x/C67x devices, such as various     | ous    |

|   |       | ory configurations, ports, timers, direct-memory access, and power-down logic.        |        |

|   | 4.1   | Direct Memory Access (DMA) Controller                                                 |        |

|   | 4.2   | Enhanced Direct Memory Access (EDMA)                                                  |        |

|   | 4.3   | Host-Port Interface (HPI)                                                             |        |

|   | 4.4   | Expansion Bus (XB)                                                                    |        |

|   | 4.5   | External Memory Interface (EMIF)                                                      |        |

|   |       | 4.5.1 SDRAM Interface                                                                 |        |

|   |       | 4.5.2 SBSRAM Interface                                                                |        |

|   |       | 4.5.3 Asynchronous Interface                                                          | . 4-14 |

|   | 4.6   | Boot Configuration Logic                                                              | . 4-16 |

|   |       | 4.6.1 Device Reset                                                                    | . 4-16 |

|   |       | 4.6.2 Boot Configuration                                                              | . 4-16 |

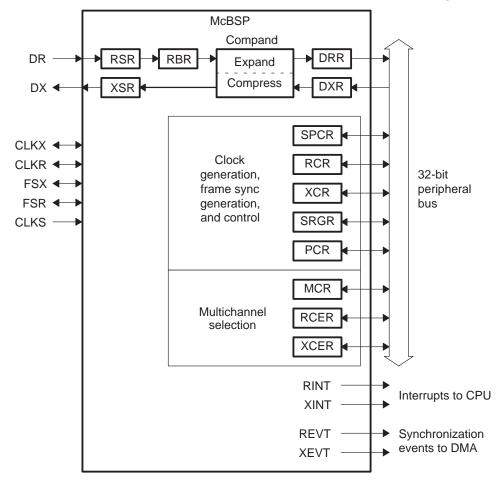

|   | 4.7   | Multichannel Buffered Serial Port (McBSP)                                             | . 4-18 |

|   | 4.8   | Timers                                                                                | . 4-21 |

|   | 4.9   | Interrupt Selector                                                                    | . 4-22 |

|   | 4.10  | Power-Down Logic                                                                      | . 4-23 |

| 5 | Deve  | elopment Support                                                                      | 5-1    |

|   |       | ribes the tools, third-party support web site, documentation, and workshops available |        |

|   | 5.1   | Code Generation Tools                                                                 | 5-2    |

|   | 5.2   | Evaluation Tools                                                                      | 5-6    |

|   | 5.3   | Third-Party Support                                                                   |        |

|   | 5.4   | Web Site and Documentation                                                            |        |

|   | 0'    |                                                                                       |        |

| Α |       | sary                                                                                  | A-1    |

|   | ⊏xpia | ains terms, abbreviations, and acronyms used throughout this technical brief.         |        |

# **Figures**

| 1–1  | The TMS320 Family of Digital Signal Processors (DSPs)            | 1-3  |

|------|------------------------------------------------------------------|------|

| 2–1  | TMS320C62x/C67x Block Diagram                                    | 2-2  |

| 2–2  | TMS320C62x CPU Data Paths                                        | 2-5  |

| 2–3  | TMS320C67x CPU and Data Paths                                    | 2-6  |

| 3–1  | TMS320C6201/C6202/C6701 Memory Maps                              | 3-2  |

| 3–2  | TMS320C6211 Memory Map                                           | 3-3  |

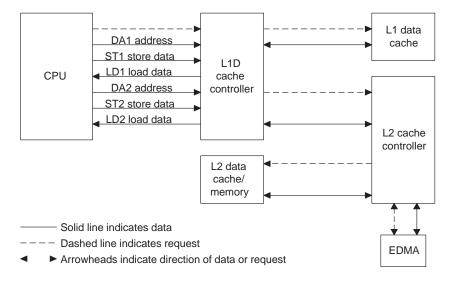

| 3–3  | TMS320C6201/C6202/C6701 Data Memory Controller Interconnect      | 3-8  |

| 3–4  | TMS320C6211 Data Memory Controller Interconnect                  | 3-9  |

| 4–1  | Host-port Interface (HPI) Block Diagram                          | 4-6  |

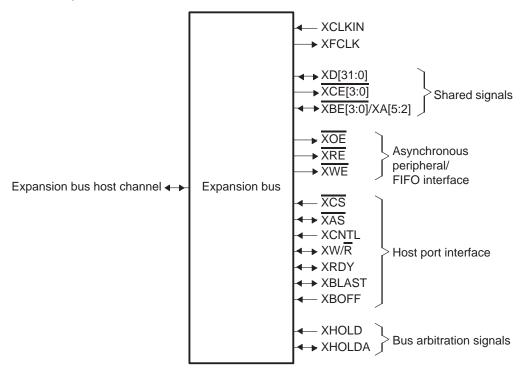

| 4–2  | Expansion Bus                                                    |      |

| 4–3  | Synchronous Interface                                            | 4-10 |

| 4–4  | External Memory Interface (EMIF) Block Diagram                   | 4-12 |

| 4–5  | EMIF to SDRAM Interface                                          | 4-13 |

| 4–6  | EMIF to SBSRAM Interface                                         | 4-14 |

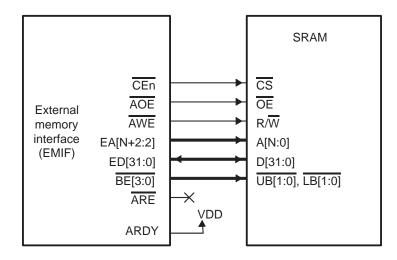

| 4–7  | EMIF to SRAM Interface                                           | 4-14 |

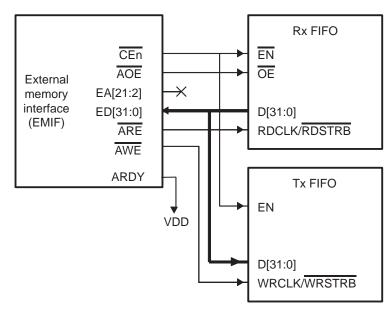

| 4–8  | EMIF to FIFO Interface                                           | 4-15 |

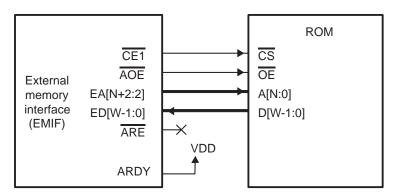

| 4–9  | EMIF to ROM Interface                                            | 4-15 |

| 4–10 | Multichannel Buffered Serial Port (McBSP) Internal Block Diagram | 4-19 |

| 5–1  | Code Development Flow Chart                                      | 5-3  |

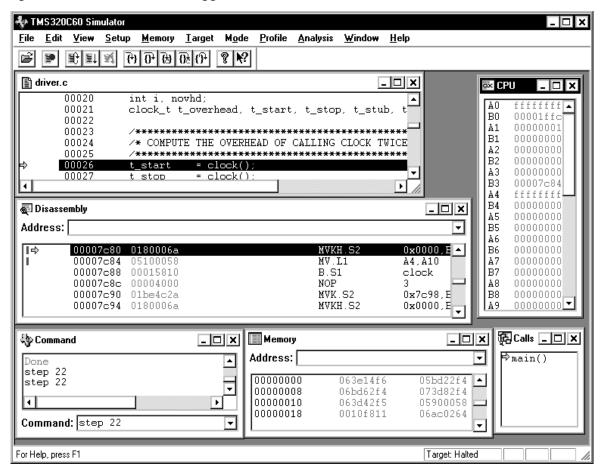

| 5–2  | Windows C Debugger Interface                                     | 5-6  |

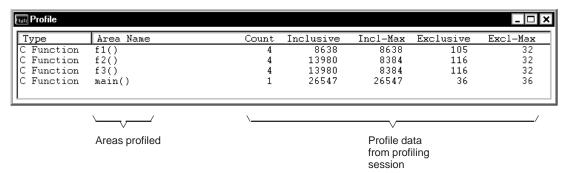

| 5–3  | An Example of the Profile Window                                 | 5-7  |

## **Tables**

| 1–1 | Typical Applications for the TMS320 Family of Digital Signal Processors (DSPs)         | -<br>-4 |

|-----|----------------------------------------------------------------------------------------|---------|

| 2–1 | Functional Units and Operations Performed                                              | -7      |

| 2–2 | Control Registers                                                                      |         |

| 2–3 | TMS320C67x Control Register File Extensions                                            |         |

| 2–4 | Fixed-Point Instruction to Functional Unit Mapping                                     | 11      |

| 2–5 | Functional Unit to Fixed-Point Instruction Mapping                                     | 12      |

| 2–6 | Floating-Point Instruction to Functional Unit Mapping                                  | 15      |

| 2–7 | Functional Unit to Floating-Point Instruction Mapping                                  | 16      |

| 2–8 | Indirect Address Generation for Load/Store                                             | 18      |

| 3–1 | TMS320C6000 Internal Memory Configurations                                             | -4      |

| 3–2 | TMS320C6000 Cache Architectures 3                                                      | -4      |

| 3–3 | L2 Operation Modes                                                                     | -7      |

| 4–1 | TMS320C6000 Peripherals                                                                | -2      |

| 4–2 | Multichannel Buffered Serial Port (McBSP) Registers 4-2                                |         |

| 4–3 | Multichannel Buffered Serial Port (McBSP) CPU Interrupts and DMA Event Synchronization |         |

| 4–4 | Peripheral Interrupts                                                                  | 22      |

| 5–1 | Selected TMS320C6000 C Compiler Intrinsics                                             |         |

| 5–2 | Contacts for Third-Party Support                                                       |         |

|     |                                                                                        |         |

## Chapter 1

### Introduction

The TMS320C6000 platform of digital signal processors (DSPs) is part of the TMS320 family of DSPs. The TMS320C62x ('C62x) devices are fixed-point DSPs in the TMS320C6000 platform. The TMS320C67x ('C67x) devices are floating-point DSPs in the TMS320C6000 platform.

The TMS320C62x and TMS320C67x are code compatible and both feature the VelociTI™ architecture. The VelociTI architecture is a high-performance, advanced, very-long-instruction-word (VLIW) architecture developed by Texas Instruments, making these DSPs excellent choices for multichannel and multifunction applications. VelociTI, together with the development tool set and evaluation tools, provides faster development time and higher performance for embedded DSP applications through increased instruction-level parallelism.

#### Topic Page

| 1.1 | The TMS320 Family of Digital Signal Processors                        |

|-----|-----------------------------------------------------------------------|

| 1.2 | Introduction to the TMS320C6000 Platform of Digital Signal Processors |

| 1.3 | Features and Options of the TMS320C62x/C67x Devices 1-6               |

#### 1.1 The TMS320 Family of Digital Signal Processors

The TMS320 family consists of 16-bit and 32-bit fixed- and floating-point devices. These DSPs possess the operational flexibility of high-speed controllers and the numerical capability of array processors. The following characteristics make this family the ideal choice for a wide range of processing applications:

| Very flexible instruction set             |

|-------------------------------------------|

| Inherent operational flexibility          |

| High-speed performance                    |

| Innovative, parallel architectural design |

| Cost-effectiveness                        |

#### 1.1.1 History, Development, and Advantages of TMS320 DSPs

In 1982, Texas Instruments introduced the TMS32010 — the first fixed-point DSP in the TMS320 family. Before the end of the year, the *Electronic Products* magazine awarded the TMS32010 the title "Product of the Year". The TMS32010 became the model for future TMS320 generations.

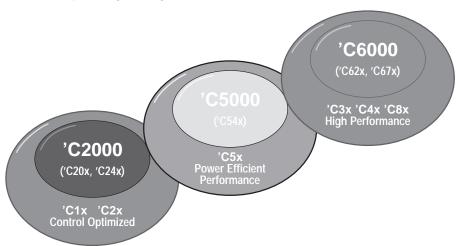

Today, the TMS320 family consists of three supported platforms including the TMS320C2000, TMS320C5000, and TMS320C6000. Within the 'C6000 platform there are two generations, the TMS320C62x and TMS320C67x, with performance and features that are reflective of Texas Instruments' commitment to lead the world in DSP solutions.

Each generation of TMS320 devices uses a core central processing unit (CPU) that is combined with a variety of on-chip memory and peripheral configurations. These various configurations satisfy a wide range of needs in the worldwide electronics market. When memory and peripherals are integrated with a CPU into one chip, the overall system cost is greatly reduced, and circuit board space is reduced. Figure 1–1 shows the progression of the TMS320 family of devices.

Figure 1–1. The TMS320 Family of Digital Signal Processors (DSPs)

#### 1.1.2 Typical Applications for the TMS320 Family

The TMS320 family of DSPs offers adaptable approaches to traditional signal-processing problems, such as vocoding, filtering, and error coding. Furthermore, the TMS320 family supports complex applications that often require multiple operations to be performed simultaneously. Table 1–1 lists many of the typical applications of the TMS320 family.

Table 1–1. Typical Applications for the TMS320 Family of Digital Signal Processors (DSPs)

| Automotive                                                                                                                                                                                                                       | Consumer                                                                                                                                                                                                                             | Control                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Adaptive ride control Antiskid brakes Cellular telephones Digital radios Engine control Global positioning Navigation Vibration analysis Voice commands                                                                          | Digital radios/TVs Educational toys Music synthesizers Pagers Power tools Radar detectors Solid-state answering machines                                                                                                             | Disk drive control Engine control Laser printer control Motor control Robotics control Servo control                        |

| General-Purpose                                                                                                                                                                                                                  | Graphics/Imaging                                                                                                                                                                                                                     | Industrial                                                                                                                  |

| Adaptive filtering Convolution Correlation Digital filtering Fast Fourier transforms Hilbert transforms Waveform generation Windowing                                                                                            | 3-D computing Animation/digital maps Homomorphic processing Image compression/transmission Image enhancement Pattern recognition Robot vision Workstations                                                                           | Numeric control Power-line monitoring Robotics Security access                                                              |

| Instrumentation                                                                                                                                                                                                                  | Medical                                                                                                                                                                                                                              | Military                                                                                                                    |

| Digital filtering Function generation Pattern matching Phase-locked loops Seismic processing Spectrum analysis Transient analysis                                                                                                | Diagnostic equipment Fetal monitoring Hearing aids Patient monitoring Prosthetics Ultrasound equipment                                                                                                                               | Image processing Missile guidance Navigation Radar processing Radio frequency modems Secure communications Sonar processing |

| Telecomn                                                                                                                                                                                                                         | nunications                                                                                                                                                                                                                          | Voice/Speech                                                                                                                |

| 1200- to 56 600-bps modems Adaptive equalizers ADPCM transcoders Base stations Cellular telephones Channel multiplexing Data encryption Digital PBXs Digital speech interpolation (DSI) DTMF encoding/decoding Echo cancellation | Faxing Future terminals Line repeaters Personal communications systems (PCS) Personal digital assistants (PDA) Speaker phones Spread spectrum communications Digital subscriber loop (xDSL) Video conferencing X.25 packet switching | Speaker verification Speech enhancement Speech recognition Speech synthesis Speech vocoding Text-to-speech Voice mail       |

#### 1.2 Introduction to the TMS320C6000 Platform of Digital Signal Processors

With performance of up to 2000 million instructions per second (MIPS) at 250 MHz and a complete set of development tools, the TMS320C6000 DSPs offer cost-effective solutions to high-performance DSP programming challenges. The TMS320C6000 development tools include a new C compiler, an assembly optimizer that simplifies programming and scheduling, and a Windows™ debugger interface.

The TMS320C6000 DSPs give system architects unlimited possibilities to differentiate their products. High performance, ease of use, and affordable pricing make the TMS320C6000 platform the ideal solution for multichannel, multifunction applications, such as:

|   | Pooled modems                                                                                   |

|---|-------------------------------------------------------------------------------------------------|

|   | Wireless local loop base stations                                                               |

|   | Beam-forming base stations                                                                      |

|   | Remote access servers (RAS)                                                                     |

|   | Digital subscriber loop (DSL) systems                                                           |

|   | Cable modems                                                                                    |

|   | Multichannel telephony systems                                                                  |

|   | Virtual reality 3-D graphics                                                                    |

|   | Speech recognition                                                                              |

|   | Audio                                                                                           |

|   | Radar                                                                                           |

| _ | Atmospheric modeling                                                                            |

| _ | Finite element analysis                                                                         |

|   | Imaging (examples: fingerprint recognition, ultrasound, and MRI)                                |

|   | e TMS320C6000 platform is also an ideal solution for exciting new applicas; for example:        |

|   | Personalized home security with face and hand/fingerprint recognition                           |

|   | Advanced cruise control with global positioning systems (GPS) navigation and accident avoidance |

|   | Remote medical diagnostics                                                                      |

#### 1.3 Features and Options of the TMS320C62x/C67x Devices

of applications

and 250 MHz respectively (6.67-, 6-, 5-, and 4-ns cycle times). All of these DSPs execute up to eight 32-bit instructions every cycle. The core CPU consists of 32 general-purpose registers of 32-bit word length and eight functional units: Two multipliers □ Six ALUs The 'C62x/C67x devices have a complete set of optimized development tools, including an efficient C compiler, an assembly optimizer for simplified assembly-language programming and scheduling, and a Windows-based debugger interface for visibility into source code execution characteristics. A hardware emulation board, compatible with the TI XDS510™ emulator interface, is also available. This tool complies with IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture. Features of the 'C62x/C67x include: Advanced VLIW CPU with eight functional units, including two multipliers and six arithmetic units ■ Executes up to eight instructions per cycle for up to ten times the performance of typical DSPs Allows designers to develop highly effective RISC-like code for fast development time Instruction packing ■ Gives code size equivalence for eight instructions executed serially or in parallel ■ Reduces code size, program fetches, and power consumption All instructions execute conditionally. Reduces costly branching Increases parallelism for higher sustained performance Code executes as programmed on independent functional units. Industry's most efficient C compiler on DSP benchmark suite Industry's first assembly optimizer for fast development and improved parallelization 8/16/32-bit data support, providing efficient memory support for a variety

The 'C6211, 'C6701, 'C6201, and 'C6202 devices operate at 150, 167, 200,

|     | 40-bit arithmetic options that add extra precision for vocoders and other computationally intensive applications                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Saturation and normalization provide support for key arithmetic operations.                                                                                                      |

|     | Field manipulation and instruction extract, set, clear, and bit counting support common operation found in control and data manipulation applications.                           |

| The | e 'C67x has the following features:                                                                                                                                              |

|     | Peak 1336 MIPS at 167 MHz                                                                                                                                                        |

|     | Peak 1G FLOPS at 167 MHz for single-precision operations                                                                                                                         |

|     | Peak 250M FLOPS at 167 MHz for double-precision operations                                                                                                                       |

|     | Peak 688M FLOPS at 167 MHz for multiply and accumulate operations                                                                                                                |

|     | Hardware support for single-precision (32-bit) and double-precision (64-bit) IEEE floating-point operations.                                                                     |

|     | 32 $\times$ 32-bit integer multiply with 32- or 64-bit result.                                                                                                                   |

| Αv  | ariety of memory and peripheral options are available for the 'C62x/C67x:                                                                                                        |

|     | Large on-chip RAM for fast algorithm execution                                                                                                                                   |

|     | 32-bit external memory interface supports SDRAM, SBSRAM, SRAM, and other asynchronous memories, for a broad range of external memory requirements and maximum system performance |

|     | Host port access to 'C62x/C67x memory and peripherals                                                                                                                            |

|     | Multichannel DMA controller                                                                                                                                                      |

|     | Multichannel serial port(s)                                                                                                                                                      |

|     | 32-bit timer(s)                                                                                                                                                                  |

## Chapter 2

### **CPU Architecture**

The VelociTI architecture makes the 'C6000 DSPs the first off-the-shelf DSPs to use an enhancement of traditional VLIW to achieve high performance through increased instruction-level parallelism. A traditional VLIW architecture consists of multiple execution units running in parallel that perform multiple instructions during a single clock cycle. Parallelism is the key to extremely high performance and takes these next-generation DSPs well beyond the performance capabilities of traditional superscalar designs. VelociTI is a highly deterministic architecture, with few restrictions on how or when instructions are fetched, executed, or stored. This architectural flexibility is key to the breakthrough efficiency levels of the 'C6000 compiler.

| Topi | C Page                                                 |

|------|--------------------------------------------------------|

| 2.1  | TMS320C62x/C67x Block Diagram                          |

| 2.2  | Central Processing Unit (CPU)                          |

| 2.3  | CPU Data Paths                                         |

| 2.4  | Mapping Between Instructions and Functional Units 2-11 |

| 2.5  | Addressing Modes 2-18                                  |

| 2.6  | Interrupts 2-19                                        |

#### 2.1 TMS320C62x/C67x Block Diagram

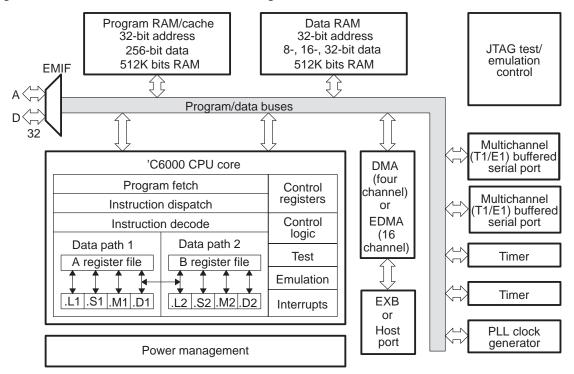

The 'C62x/C67x processor consists of three main parts: CPU (or the *core*), peripherals, and memory. Eight functional units operate in parallel, with two similar sets of the basic four functional units. The units communicate using a cross path between two register files, each of which contains 16 32-bit registers. Program parallelism is defined at compile time because there is no data dependency checking done in hardware during run time. The 256-bit-wide program memory fetches eight 32-bit instructions every single cycle.

Figure 2–1 is the block diagram for the TMS320C62x/C67x devices. The 'C62x/C67x devices come with on-chip program and data memory, which may be configured as cache on some devices. Peripherals include a direct memory access (DMA) controller, power-down logic, external memory interface (EMIF), serial port(s), expansion bus or host port, and timer(s). Check the data sheet for your device to determine the specific peripheral configurations you have.

Figure 2-1. TMS320C62x/C67x Block Diagram

#### 2.2 Central Processing Unit (CPU)

The 'C62x/C67x CPU, in Figure 2–1, is common to all the 'C62x/C67x devices. The CPU contains: Program fetch unit Instruction dispatch unit Instruction decode unit ☐ 32 32-bit registers ☐ Two data paths, each with four functional units Control registers Control logic ☐ Test, emulation, and interrupt logic The CPU has two data paths (A and B) in which processing occurs. Each data path has four functional units (.L, .S, .M, and .D) and a register file containing 16 32-bit registers. The functional units execute logic, shifting, multiply, and data address operations. All instructions except loads and stores operate on the registers. The two data-addressing units (.D1 and .D2) are exclusively responsible for all data transfers between the register files and memory. The four functional units of a data path have a single data bus connected to registers on the other side of the CPU so that the units can exchange data with the register file on the opposite side. Register access across the CPU supports one read and write operation per cycle. The two sets of functional units include the following items: ☐ Two multipliers ☐ Six arithmetic logic units (ALUs) ☐ Two register files, each containing 16 32-bit registers Each functional unit is controlled by a 32-bit instruction. The instruction fetch,

Each functional unit is controlled by a 32-bit instruction. The instruction fetch, instruction dispatch, and instruction decode blocks can deliver up to eight 32-bit instructions from the program memory to the functional units every cycle. The control register file provides methods to configure and control various aspects of processor operation. Access to the control registers is provided from datapath B.

The VLIW processing flow begins when a 256-bit-wide instruction fetch packet (IFP) is fetched from the internal program memory. The instructions linked together for simultaneous execution (up to eight instructions) form an execute packet. For more details on the processing, see the data sheet for your particular device.

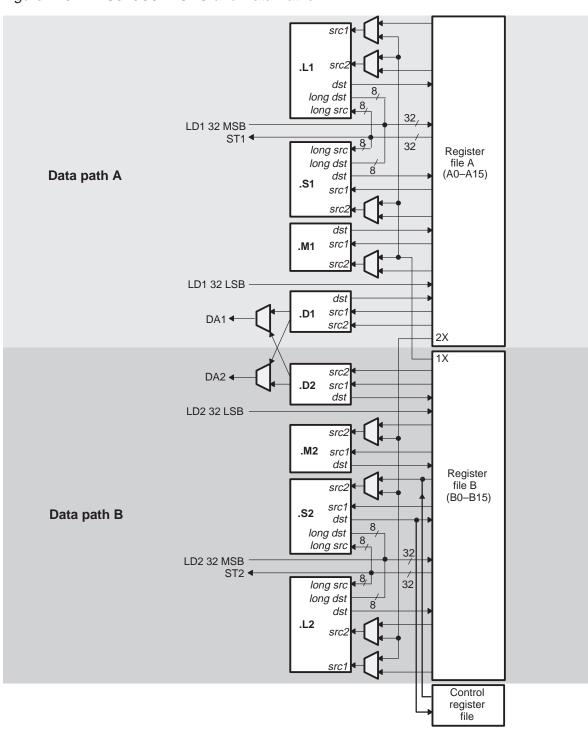

#### 2.3 CPU Data Paths

Figure 2–2 shows the 'C62x CPU data paths and Figure 2–3 shows the 'C67x CPU data paths, which consist of:

Two general-purpose register files (A and B)

Eight functional units (.L1, .L2, .S1, .S2, .M1, .M2, .D1, and .D2)

Two load-from-memory paths (LD1 and LD2)

Two store-to-memory paths (ST1 and ST2)

Two register file cross paths (1X and 2X)

Two data address paths (DA1 and DA2)

#### 2.3.1 General-Purpose Register Files

There are two general-purpose register files (A and B) in the 'C62x/C67x data paths. Each of these files contains 16 32-bit registers (A0–A15 for file A and B0–B15 for file B). The general-purpose registers can be used for data or data-address pointers. Registers A1, A2, B0, B1, and B2 can be used for condition registers. Registers A4–A7 and B4–B7 can be used for circular addressing.

The general-purpose register files support 32- and 40-bit fixed-point data. 32-bit data can be contained in any general-purpose register. 40-bit data is contained across two registers; the 32 LSBs of the data are placed in an even register and the remaining eight MSBs are placed in the eight LSBs of the next upper register (which is always an odd register). The 'C67x also uses these register pairs to hold 64-bit double-precision floating-point values.

.L1 dst 8, long dst long src 32, ST1 **←** long src Register file A (A0–A15) long dst dst .S1 Data path A src1 src2 dst .M1 src1 src2 LD1 dst .D1 src1 DA1 **◆** src2 2X 1X src2 DA2 ◀ .D2 src1 dst LD2 src2 .M2 src1 dst Register file B src2 (B0-B15) Data path B src1 .S2 dst long dst 8, long src 32 ST2 ◀ long src 8, long dst dst .L2 src2 Control register file

Figure 2-2. TMS320C62x CPU Data Paths

Figure 2-3. TMS320C67x CPU and Data Paths

#### 2.3.2 Functional Units

The eight functional units in the 'C62x/C67x data paths can be divided into two groups of four; each functional unit in one data path is almost identical to the corresponding unit in the other data path. The functional units are described in Table 2–1.

Most data lines in the CPU support 32-bit operands, and some support long (40-bit) operands. Each functional unit has its own 32-bit write port into a general-purpose register file. All units ending in 1 (for example, .L1) write to register file A and all units ending in 2 write to register file B. Each functional unit has two 32-bit read ports for source operands *src1* and *src2*. Four units (.L1, .L2, .S1, and .S2) have an extra 8-bit-wide port for 40-bit long writes as well as an 8-bit input for 40-bit long reads. Because each unit has its own 32-bit write port, all eight units can be used in parallel every cycle.

Table 2–1. Functional Units and Operations Performed

| Functional Unit    | Fixed-Point Operations                                                                                                                                                                               | Floating-Point Operations                                                                                         |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| .L unit (.L1,.L2)  | 32/40-bit arithmetic and compare operations<br>Leftmost 1 or 0 bit counting for 32 bits<br>Normalization count for 32 and 40 bits<br>32-bit logical operations                                       | Arithmetic operations Conversion operations: DP $\rightarrow$ SP, INT $\rightarrow$ DP, INT $\rightarrow$ SP      |

| .S unit (.S1, .S2) | 32-bit arithmetic operations 32/40-bit shifts and 32-bit bit-field operations 32-bit logical operations Branches Constant generation Register transfers to/from the control register file (.S2 only) | Compare reciprocal and reciprocal square-root operations Absolute value operations SP to DP conversion operations |

| .M unit (.M1, .M2) | $16 \times 16$ bit multiply operations                                                                                                                                                               | 32 	imes 32 bit multiply operations Floating-point multiply operations                                            |

| .D unit (.D1, .D2) | 32-bit add, subtract, linear and circular address calculation Loads and stores with a 5-bit constant offset Loads and stores with a 15-bit constant offset (.D2 only)                                | Load double word with a 5-bit constant offset                                                                     |

#### 2.3.3 TMS320C62x/C67x Control Register Files

One unit (.S2) can read from and write to the control register file, shown in Figure 2–2 and Figure 2–3. Table 2–2 lists the control registers contained in the control register file and describes each. Each control register is accessed by the MVC instruction.

Table 2-2. Control Registers

|              | Register                             |                                                                                                                                 |

|--------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Abbreviation | Name                                 | Description                                                                                                                     |

| AMR          | Addressing mode register             | Specifies whether to use linear or circular addressing for each of eight registers; also contains sizes for circular addressing |

| CSR          | Control status register              | Contains the global interrupt enable bit, cache control bits, and other miscellaneous control and status bits                   |

| IFR          | Interrupt flag register              | Displays status of interrupts                                                                                                   |

| ISR          | Interrupt set register               | Allows you to set pending interrupts manually                                                                                   |

| ICR          | Interrupt clear register             | Allows you to clear pending interrupts manually                                                                                 |

| IER          | Interrupt enable register            | Allows enabling/disabling of individual interrupts                                                                              |

| ISTP         | Interrupt service table pointer      | Points to the beginning of the interrupt service table                                                                          |

| IRP          | Interrupt return pointer             | Contains the address to be used to return from a maskable interrupt                                                             |

| NRP          | Nonmaskable interrupt return pointer | Contains the address to be used to return from a nonmaskable interrupt                                                          |

| PCE1         | Program counter, E1 phase            | Contains the address of the fetch packet that contains the execute packet in the E1 pipeline stage                              |

#### 2.3.4 TMS320C67x Control Register File Extensions

The 'C67x has three additional configuration registers to support floating point operations (see Table 2–3). The registers specify the desired floating-point rounding mode for the .L and .M units. They also contain bit fields to warn if *src1* and *src2* are NaN (not a number) or denormal numbers, and if the result overflows, underflows, is inexact, infinite, or invalid. There are also fields to warn if a divide by 0 was performed, or if a compare was attempted with a NaN source.

Table 2–3. TMS320C67x Control Register File Extensions

|              | Register                                         |                                                                                            |

|--------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|

| Abbreviation | Name                                             | Description                                                                                |

| FADCR        | Floating-point adder configuration register      | Specifies underflow mode, rounding mode, NaNs, and other exceptions for the .L unit.       |

| FAUCR        | Floating-point auxiliary configuration register  | Specifies underflow mode, rounding mode, NaNs, and other exceptions for the .S unit. $ \\$ |

| FMCR         | Floating-point multiplier configuration register | Specifies underflow mode, rounding mode, NaNs, and other exceptions for the .M unit. $ \\$ |

#### 2.3.5 Register File Cross Paths

Each functional unit reads directly from and writes directly to the register file within its own data path. That is, the .L1, .S1, .D1, and .M1 units write to register file A and the .L2, .S2, .D2, and .M2 units write to register file B. The register files are connected to the opposite-side register file's functional units via the 1X and 2X cross paths. These cross paths allow functional units from one data path to access a 32-bit operand from the opposite side's register file. The 1X cross path allows data path A's functional units to read their source from register file B and the 2X cross path allows data path B's functional units to read their source from register file A.

Six of the functional units have access to the opposite side's register file via a cross path. The .M1, .M2, .S1, and .S2 units' *src2* inputs are multiplex-selectable between the cross path and the same side register file. The .L1 and .L2 units' *src1* and *src2* inputs are also multiplex-selectable between the cross path and the same side register file.

Only two cross paths, 1X and 2X, exist in the 'C62x/C67x CPUs. This limits one source read from each data path's opposite register file per cycle, or two crosspath source reads per cycle.

#### 2.3.6 Memory, Load, and Store Paths

There are two 32-bit paths for loading data from memory to the register file: LD1 for register file A, and LD2 for register file B. The 'C67x also has a second 32-bit load path for both register files A and B, which allows the LDDW instruction to simultaneously load two 32-bit registers into side A and two 32-bit registers into side B. There are also two 32-bit paths, ST1 and ST2, for storing register values to memory from each register file. The store paths are shared with the .L and .S long read paths.

#### 2.3.7 Data-Address Paths

The data-address paths (DA1 and DA2) shown in Figure 2–2 and Figure 2–3 coming out of the .D units allow data addresses generated from one register file to support loads and stores to memory from the other register file. However, loads and stores executed in parallel must load to and from the same register file or both use a crosspath to the opposite register.

#### 2.4 Mapping Between Instructions and Functional Units

Table 2-4 shows the mapping between instructions and functional units and Table 2–5 shows the mapping between functional units and instructions for the TMS320C62x/C67x fixed-point instructions.

Table 2-4. Fixed-Point Instruction to Functional Unit Mapping

| .L Unit | .M Unit | .S Unit |      | .D Unit               |                      |

|---------|---------|---------|------|-----------------------|----------------------|

| ABS     | MPY     | ADD     | SET  | ADD                   | STB (15-bit offset)‡ |

| ADD     | MPYU    | ADDK    | SHL  | ADDAB                 | STH (15-bit offset)‡ |

| ADDU    | MPYUS   | ADD2    | SHR  | ADDAH                 | STW (15-bit offset)‡ |

| AND     | MPYSU   | AND     | SHRU | ADDAW                 | SUB                  |

| CMPEQ   | MPYH    | B disp  | SHRL | LDB                   | SUBAB                |

| CMPGT   | MPYHU   | B IRP†  | SUB  | LDBU                  | SUBAH                |

| CMPGTU  | MPYHUS  | B NRP†  | SUBU | LDH                   | SUBAW                |

| CMPLT   | MPYHSU  | B reg   | SUB2 | LDHU                  | ZERO                 |

| CMPLTU  | MPYHL   | CLR     | XOR  | LDW                   |                      |

| LMBD    | MPYHLU  | EXT     | ZERO | LDB (15-bit offset)‡  |                      |

| MV      | MPYHULS | EXTU    |      | LDBU (15-bit offset)‡ |                      |

| NEG     | MPYHSLU | MV      |      | LDH (15-bit offset)‡  |                      |

| NORM    | MPYLH   | MVC†    |      | LDHU (15-bit offset)‡ |                      |

| NOT     | MPYLHU  | MVK     |      | LDW (15-bit offset)‡  |                      |

| OR      | MPYLUHS | MVKH    |      | MV                    |                      |

| SADD    | MPYLSHU | MVKLH   |      | STB                   |                      |

| SAT     | SMPY    | NEG     |      | STH                   |                      |

| SSUB    | SMPYHL  | NOT     |      | STW                   |                      |

| SUB     | SMPYLH  | OR      |      |                       |                      |

| SUBU    | SMPYH   |         |      |                       |                      |

| SUBC    |         |         |      |                       |                      |

| XOR     |         |         |      |                       |                      |

| ZERO    |         |         |      |                       |                      |

<sup>†</sup>S2 only ‡D2 only

Table 2-5. Functional Unit to Fixed-Point Instruction Mapping

|             |          | Functio | nal Units  |          |

|-------------|----------|---------|------------|----------|

| Instruction | .L Unit  | .M Unit | .S Unit    | .D Unit  |

| ABS         | <b>V</b> |         |            |          |

| ADD         | ~        |         | ~          | V        |

| ADDU        | <b>~</b> |         |            |          |

| ADDAB       |          |         |            | ~        |

| ADDAH       |          |         |            | ~        |

| ADDAW       |          |         |            | <b>~</b> |

| ADDK        |          |         | ~          |          |

| ADD2        |          |         | ~          |          |

| AND         | ~        |         | ~          |          |

| В           |          |         | ~          |          |

| B IRP       |          |         | <b>/</b> † |          |

| B NRP       |          |         | <b>/</b> † |          |

| B reg       |          |         | <b>/</b> † |          |

| CLR         |          |         | ~          |          |

| CMPEQ       | <b>V</b> |         |            |          |

| CMPGT       |          |         |            |          |

| CMPGTU      |          |         |            |          |

| CMPLT       |          |         |            |          |

| CMPLTU      | ~        |         |            |          |

| EXT         |          |         | ~          |          |

| EXTU        |          |         | ~          |          |

| IDLE        |          |         |            |          |

| LDB mem     |          |         |            | ~        |

| LDBU mem    |          |         |            | ~        |

| LDH mem     |          |         |            | ~        |

| LDHU mem    |          |         |            |          |

<sup>†</sup>S2 only ‡D2 only

Table 2–5. Functional Unit to Fixed-Point Instruction Mapping (Continued)

|                          |         | Functio  | nal Units |            |

|--------------------------|---------|----------|-----------|------------|

| Instruction              | .L Unit | .M Unit  | .S Unit   | .D Unit    |

| LDW mem                  |         |          |           | ~          |

| LDB mem (15-bit offset)  |         |          |           | <b>/</b> ‡ |

| LDBU mem (15-bit offset) |         |          |           | <b>/</b> ‡ |

| LDH mem (15-bit offset)  |         |          |           | <b>/</b> ‡ |

| LDHU mem (15-bit offset) |         |          |           | <b>/</b> ‡ |

| LDW mem (15-bit offset)  |         |          |           | <b>/</b> ‡ |

| LMBD                     | ~       |          |           |            |

| MPY                      |         | ~        |           |            |

| MPYU                     |         | ~        |           |            |

| MPYUS                    |         | ~        |           |            |

| MPYSU                    |         | ~        |           |            |

| MPYH                     |         | ~        |           |            |

| MPYHU                    |         | ~        |           |            |

| MPYHUS                   |         | ~        |           |            |

| MPYHSU                   |         | ~        |           |            |

| MPYHL                    |         | ~        |           |            |

| MPYHLU                   |         | ~        |           |            |

| MPYHULS                  |         | ~        |           |            |

| MPYHSLU                  |         | <b>/</b> |           |            |

| MPYLH                    |         | ~        |           |            |

| MPYLHU                   |         | ~        |           |            |

| MPYLUHS                  |         | ~        |           |            |

| MPYLSHU                  |         | ~        |           |            |

| MV                       | ~       |          |           | V          |

| MVC†                     |         |          | ~         |            |

| MVK                      |         |          |           |            |

<sup>†</sup> S2 only ‡ D2 only

Table 2–5. Functional Unit to Fixed-Point Instruction Mapping (Continued)

| _                       |          | Functio | nal Units |            |

|-------------------------|----------|---------|-----------|------------|

| Instruction             | .L Unit  | .M Unit | .S Unit   | .D Unit    |

| MVKH                    |          |         | ~         |            |

| MVKLH                   |          |         | u         |            |

| NEG                     | ~        |         | ~         |            |

| NOP                     |          |         |           |            |

| NORM                    | <b>~</b> |         |           |            |

| NOT                     | <b>~</b> |         | ~         |            |

| OR                      | <b>~</b> |         | ~         |            |

| SADD                    | $\nu$    |         |           |            |

| SAT                     | $\nu$    |         |           |            |

| SET                     |          |         | ~         |            |

| SHL                     |          |         | ~         |            |

| SHR                     |          |         | ~         |            |

| SHRU                    |          |         | $\nu$     |            |

| SMPY                    |          | $\nu$   |           |            |

| SMPYH                   |          | u       |           |            |

| SMPYHL                  |          | $\nu$   |           |            |

| SMPYLH                  |          | u       |           |            |

| SSHL                    |          |         |           |            |

| SSUB                    | u        |         |           |            |

| STB mem                 |          |         |           | V          |

| STH mem                 |          |         |           |            |

| STW mem                 |          |         |           | ~          |

| STB mem (15-bit offset) |          |         |           | <b>/</b> ‡ |

| STH mem (15-bit offset) |          |         |           | <b>/</b> ‡ |

| STW mem (15-bit offset) |          |         |           | <b>/</b> ‡ |

| SUB                     | $\nu$    |         | $\nu$     | V          |

<sup>†</sup>S2 only ‡D2 only

Table 2–5. Functional Unit to Fixed-Point Instruction Mapping (Continued)

|             | Functional Units |         |         |          |  |

|-------------|------------------|---------|---------|----------|--|

| Instruction | .L Unit          | .M Unit | .S Unit | .D Unit  |  |

| SUBU        | <b>/</b>         |         | ~       |          |  |

| SUBAB       |                  |         |         |          |  |

| SUBAH       |                  |         |         | $\nu$    |  |

| SUBAW       |                  |         |         |          |  |

| SUBC        | $\vee$           |         |         |          |  |

| SUB2        |                  |         | ~       |          |  |

| XOR         | u                |         | ~       |          |  |

| ZERO        | ~                |         | ~       | <b>V</b> |  |

<sup>†</sup>S2 only

Table 2–6 shows the mapping between instructions and functional units and Table 2–7 shows the mapping between functional units and instructions for the TMS320C67x floating-point instructions.

Table 2-6. Floating-Point Instruction to Functional Unit Mapping

| .L Unit | .M Unit                               | .S Unit | .D Unit |

|---------|---------------------------------------|---------|---------|

| ADDDP   | MPYDP                                 | ABSDP   | ADDAD   |

| ADDSP   | MPYI                                  | ABSSP   | LDDW    |

| DPINT   | MPYID                                 | CMPEQDP |         |

| DPSP    | MPYSP                                 | CMPEQSP |         |

| INTDP   |                                       | CMPGTDP |         |

| INTDPU  |                                       | CMPGTSP |         |

| INTSP   |                                       | CMPLTDP |         |

| INTSPU  |                                       | CMPLTSP |         |

| SPINT   |                                       | RCPDP   |         |

| SPTRUNC |                                       | RCPSP   |         |

| SUBDP   |                                       | RSQRDP  |         |

| SUBSP   |                                       | RSQRSP  |         |

|         |                                       | SPDP    |         |

|         | · · · · · · · · · · · · · · · · · · · |         |         |

<sup>‡</sup>D2 only

Table 2-7. Functional Unit to Floating-Point Instruction Mapping

| Functional Units |         |         |         |         |                 |

|------------------|---------|---------|---------|---------|-----------------|

| Instruction      | .L Unit | .M Unit | .S Unit | .D Unit | Туре            |

| ABSDP            |         |         | ~       |         | 2-cycle DP      |

| ABSSP            |         |         | ~       |         | Single cycle    |

| ADDAD            |         |         |         | ~       | Single cycle    |

| ADDDP            | ~       |         |         |         | ADDDP/<br>SUBDP |

| ADDSP            | ~       |         |         |         | Four cycle      |

| CMPEQDP          |         |         | ~       |         | DP compare      |

| CMPEQSP          |         |         | ~       |         | Single cycle    |

| CMPGTDP          |         |         | ~       |         | DP compare      |

| CMPGTSP          |         |         | ~       |         | Single cycle    |

| CMPLTDP          |         |         | ~       |         | DP compare      |

| CMPLTSP          |         |         | 1       |         | Single cycle    |

| DPINT            | ~       |         |         |         | 4-cycle         |

| DPSP             | ~       |         |         |         | 4-cycle         |

| DPTRUNC          | ~       |         |         |         | 4-cycle         |

| INTDP            | ~       |         |         |         | INTDP           |

| INTDPU           | ~       |         |         |         | INTDP           |

| INTSP            | ~       |         |         |         | 4-cycle         |

| INTSPU           | ~       |         |         |         | 4-cycle         |

| LDDW             |         |         |         | ~       | Load            |

| MPYDP            |         | ~       |         |         | MPYDP           |

| MPYI             |         | ~       |         |         | MPYI            |

| MPYID            |         | ~       |         |         | MPYID           |

| MPYSP            |         | ~       |         |         | 4-cycle         |

| RCPDP            |         |         | ~       |         | 2-cycle DP      |

| RCPSP            |         |         | ~       |         | Single cycle    |

| RSQRDP           |         |         | ~       |         | 2-cycle DP      |

| RSQRSP           |         |         | ~       |         | Single cycle    |

Table 2–7. Functional Unit to Floating-Point Instruction Mapping(Continued)

|             | Functional Units |         |         |         |                 |

|-------------|------------------|---------|---------|---------|-----------------|

| Instruction | .L Unit          | .M Unit | .S Unit | .D Unit | Туре            |

| SPDP        |                  |         | ~       |         | 2-cycle DP      |

| SPINT       | ~                |         |         |         | 4-cycle         |

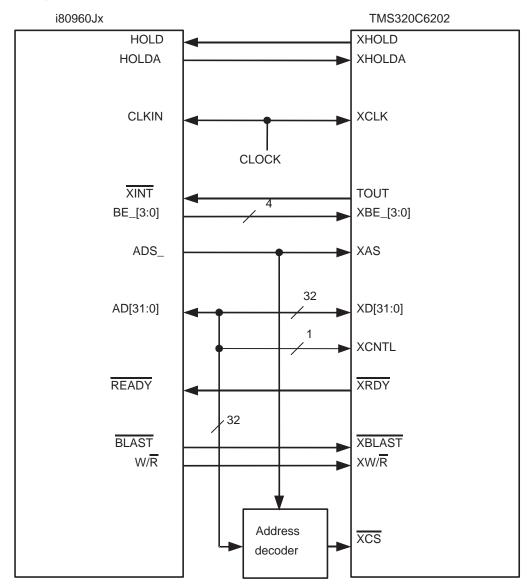

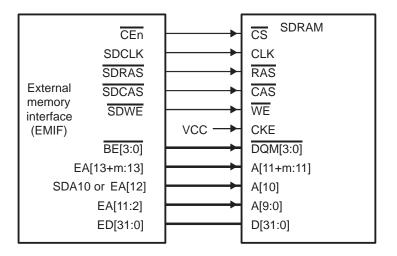

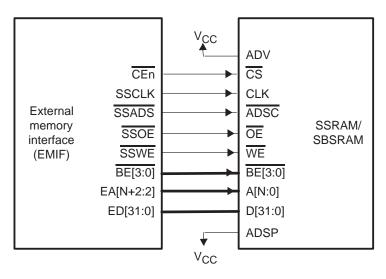

| SPTRUNC     | ~                |         |         |         | 4-cycle         |