## TMS320C6203, TMS320C6203B

## **Digital Signal Processors**

### Silicon Errata

C6203 Silicon Revision 1.x

C6203B Silicon Revisions 2.x, 3.0, 3.1

SPRZ174L November 2000 Revised February 2004

Copyright © 2003, Texas Instruments Incorporated

#### **REVISION HISTORY**

This silicon errata revision history highlights the technical changes made to the SPRZ174K revision to make it an SPRZ174L revision.

**Scope:** This document has been reviewed for technical accuracy; the technical content is up-to-date as of the specified release date.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS |

|----------------|-----------------------------|

|                | None                        |

### Contents

| Introduction       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Quality and R  | eliability Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TMX Definitio      | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TMP Definitio      | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2 Revision Iden  | tification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C6203B Silicon R   | evision 3.1 Known Design Exceptions to Functional Specifications and Usage Notes $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C6203B Silicon Re  | evision 3.0 Known Design Exceptions to Functional Specifications and Usage Notes $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1 Usage Notes    | for Silicon Revision 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2 Silicon Revisi | on 3.0 Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Advisory 3.0.1     | Memory: Potential Read After Write Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C6203B Silicon Re  | evision 2.5 Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL Component Cl   | nange                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Advisory 2.5.1     | EMIF: Synchronous-Burst Memory AC Timing Differs From Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Advisory 2.5.2     | EMIF: Synchronous DRAM AC Timing Differs From Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.5.3     | XBUS FIFO: Expansion Bus Synchronous FIFO AC Timing Differs From Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.5.4     | XBUS 8:1 Ratio Limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.5.5     | XBUS: XBUS and DMA Hang When Using XRDY During ASYNC I/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

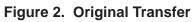

| Advisory 2.5.6     | XBUS – EMIF: Sync Host XBUS to EMIF SDRAM Corruption of Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C6203B Silicon Re  | evision 2.1 Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

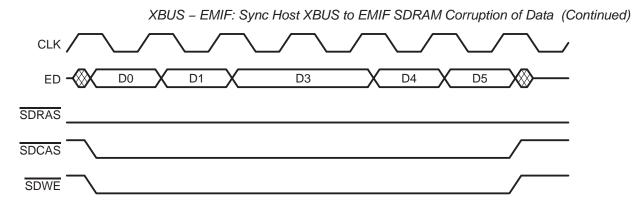

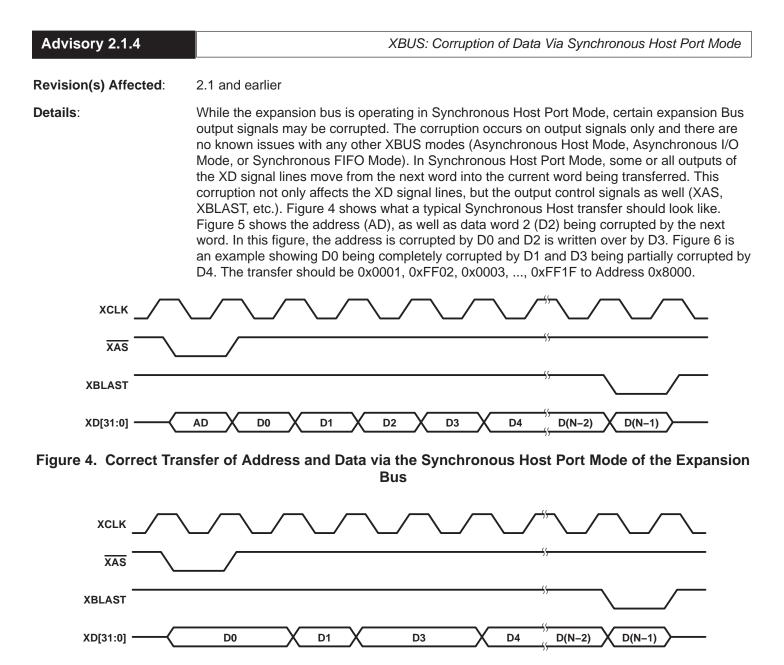

| Advisory 2.1.4     | XBUS: Corruption of Data Via Synchronous Host Port Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C6203 Silicon Rev  | vision 1.x Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 1.x.1     | XBUS: FIFO Data and Control Signals Zero Delay/Skewed From XFCLK High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Documentation S    | upport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | <ul> <li>1.1 Quality and R<br/>TMX Definitio<br/>TMP Definitio<br/>TMS Definitio</li> <li>1.2 Revision Iden</li> <li>C6203B Silicon Revision</li> <li>C6203B Silicon Revision</li> <li>3.1 Usage Notes</li> <li>3.2 Silicon Revision</li> <li>Advisory 3.0.1</li> <li>C6203B Silicon Revision</li> <li>Advisory 2.5.1</li> <li>Advisory 2.5.2</li> <li>Advisory 2.5.3</li> <li>Advisory 2.5.4</li> <li>Advisory 2.5.5</li> <li>Advisory 2.5.5</li> <li>Advisory 2.5.6</li> <li>C6203B Silicon Revision</li> <li>Advisory 2.1.4</li> <li>C6203 Silicon Revision</li> <li>Advisory 1.x.1</li> </ul> | TMX Definition         TMX Definition         TMS Definition         1.2 Revision Identification         C6203B Silicon Revision 3.1 Known Design Exceptions to Functional Specifications and Usage Notes         C6203B Silicon Revision 3.0 Known Design Exceptions to Functional Specifications and Usage Notes         3.1 Usage Notes for Silicon Revision 3.0         3.2 Silicon Revision 3.0 Known Design Exceptions to Functional Specifications         Advisory 3.0.1       Memory: Potential Read After Write Error         C6203B Silicon Revision 2.5 Known Design Exceptions to Functional Specifications         PLL Component Change       PLL         Advisory 2.5.1       EMIF: Synchronous-Burst Memory AC Timing Differs From Data Sheet         Advisory 2.5.2       EMIF: Synchronous DRAM AC Timing Differs From Data Sheet         Advisory 2.5.3       XBUS FIFO: Expansion Bus Synchronous FIFO AC Timing Differs From Data Sheet         Advisory 2.5.4       XBUS 8:1 Ratio Limitation         Advisory 2.5.5       XBUS and DMA Hang When Using XRDY During ASYNC I/O Read         Advisory 2.5.6       XBUS – EMIF: Sync Host XBUS to EMIF SDRAM Corruption of Data         C6203B Silicon Revision 2.1 Known Design Exceptions to Functional Specifications         Advisory 2.1.4       XBUS: Corruption of Data Via Synchronous Host Port Mode         C6203 Silicon Revision 1.x Known Design Exc |

#### 1 Introduction

This document describes the silicon updates to the functional specifications for the TMS320C6203 silicon releases 1.x and earlier, and for the TMS320C6203B silicon releases 2.x, 3.0, and 3.1.

For additional information, see the latest version of *TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190) and the latest verion of *TMS320C6203B Fixed-Point Digital Signal Processor* data sheet (literature number SPRS086).

#### 1.1 Quality and Reliability Conditions

#### **TMX Definition**

Texas Instruments (TI) does not warranty either (1) electrical performance to specification, or (2) product reliability for products classified as "TMX." By definition, the product has not completed data sheet verification or reliability performance qualification according to TI Quality Systems Specifications.

The mere fact that a "TMX" device was tested over a particular temperature and voltage ranges should not, in any way, be construed as a warranty of performance.

#### **TMP** Definition

TI does not warranty product reliability for products classified as "TMP." By definition, the product has not completed reliability performance qualification according to TI Quality Systems Specifications; however, products are tested to a published electrical and mechanical specification.

#### TMS Definition

Fully-qualified production device.

All trademarks are the property of their respective owners.

#### 1.2 Revision Identification

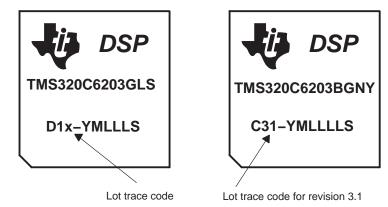

The device revision can be determined by the lot trace code marked on the top of the package. The location for the lot trace codes for the GLS and the GNY packages are shown in Figure 1 and Table 1.

NOTE: Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" at the beginning of the device name.

#### Figure 1. Example, Lot Trace Code for TMS320C6203 and TMS320C6203B

| Lot Trace Code | Silicon Revision | Comments                                                                                                                                                                            |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31             | 3.1              | TMS320C6203 <b>B</b> (GNZ/GNY). There are <i>no</i> known design exceptions to functional specifications or usage notes for TMS320C6203B silicon revision 3.1.                      |

| 30             | 3.0              | TMS320C6203 <b>B</b> (GNZ/GNY). All advisory issues presented on TMS320C6203B silicon revision 2.5 and earlier and TMS320C6203 silicon revision 1.x and earlier have been resolved. |

| 2x             | 2.x              | TMS320C6203B (GNZ/GLS). Revisions beyond 2.5 have been done to improve yield and are functionally the same as Rev. 2.5.                                                             |

| 1x             | 1.x              | TMS320C6203 (GNZ/GLS). There have been multiple silicon revisions done to improve yield that are functionally the same.                                                             |

#### Table 1. Lot Trace Code Names

# 2 C6203B Silicon Revision 3.1 Known Design Exceptions to Functional Specifications and Usage Notes

There are no known design exceptions to functional specifications or usage notes for the TMS320C6203B silicon revision 3.1.

# 3 C6203B Silicon Revision 3.0 Known Design Exceptions to Functional Specifications and Usage Notes

#### 3.1 Usage Notes for Silicon Revision 3.0

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 3.2 Silicon Revision 3.0 Known Design Exceptions to Functional Specifications

| Advisory 3.0.1        | Memory: Potential Read After Write Error                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision(s) Affected: | 2.x and 3.0                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Details:              | In the event that ALL of the following five conditions are met simultaneously, a data bit misread may occur in internal device memory:                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                       | 1. Write immediately followed by a read                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | 2. The write and read occur in back-to-back cycles without any stalls                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                       | <ol> <li>Read must be in same 16-bit-wide bank as preceding write.</li> <li>(The addressing structure of the physical banks is described below.)</li> </ol>                                                                                                                                                                                                |  |  |  |  |  |  |

|                       | <ol> <li>Read must access the same physical column as the preceding write (read offset from<br/>write by a multiple of 0x100 bytes)</li> </ol>                                                                                                                                                                                                             |  |  |  |  |  |  |

|                       | 5. Read value must be of a different state than that of the preceding write (e.g., if write value is 0x0, then read value must be different from 0x0)                                                                                                                                                                                                      |  |  |  |  |  |  |

|                       | Note: The read and/or write conditions can occur via the CPU, DMA, or a combination of the two.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                       | <ul> <li>CPU Write, DMA Read</li> </ul>                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | <ul> <li>CPU Write, CPU Read</li> </ul>                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | <ul> <li>DMA Write, DMA Read</li> </ul>                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | <ul> <li>DMA Write, CPU Read</li> </ul>                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | Back-to-back accesses typically occur in tightly looped code. Tightly looped code rarely does both reads and writes to the same bank offset by a multiple of 0x100 bytes. In algorithms that do stride by this amount, typically loads are done for different iterations than stores so they are not offset in the software pipelined loop by this amount. |  |  |  |  |  |  |

Memory: Potential Read After Write Error (Continued)

The C6203B data memory consists of 16 separate 16-bit-wide banks. These banks are broken down into 2 blocks, each containing 2 subblocks of 4 banks. Data memory is addressed as follows:

| ADDR[31]   | $\rightarrow$ | Data Memory Select |

|------------|---------------|--------------------|

| ADDR[3019] | $\rightarrow$ | Reserved           |

| ADDR[18]   | $\rightarrow$ | Block Select       |

| ADDR[17]   | $\rightarrow$ | Subblock Select    |

| ADDR[168]  | $\rightarrow$ | Row Select         |

| ADDR[73]   | $\rightarrow$ | Column Select      |

| ADDR[21]   | $\rightarrow$ | 16-bit Bank Select |

| ADDR[0]    | $\rightarrow$ | Byte Enable        |

Only when a write followed by a read occurs and the Row Select bits (ADDR[16..8]) are different will this error potentially occur.

For example, the error may occur using the following sequence:

Write 0x12345678 to address 0x80010042

Read from address 0x80010542 ← Only Row Select changes

In this case, the read may come back with a different value than expected.

The error will *not* occur under the following sequences:

Write 0xFEDCBA98 to address 0x80010054

Read from address 0x80030554 ← Different Block

or

Write 0x55AA55AA to address 0x80010042

Read from address 0x80010562 ← Different column

Assuming all five conditions above have been met, this issue is more likely to be encountered at:

- 1.5-V, rather than 1.7-V core supply voltage. 1.7 V significantly reduces the likelihood of the error.

- Higher, rather than lower, device case operating temperature

- Higher, rather than lower, device operating frequency. 250-MHz operation significantly reduces the likelihood of error.

Note that this behavior is **NOT** a reliability risk. It should not degrade for a given set of operating conditions and code.

**Workaround**: The occurrence of all five conditions is application-specific. Code should be examined to determine if the five conditions above are met. If all conditions are met, insert at least one dead cycle between the write and read.

#### 4 C6203B Silicon Revision 2.5 Known Design Exceptions to Functional Specifications

Changes shown in this section refer to two data sheets by their literature numbers: *TMS320C6203 Fixed-Point Digital Signal Processor* data sheet (literature number SPRS086D) and *TMS320C6202, TMS320C6202B, TMS320C6203, TMS320C6204 Fixed-Point Digital Signal Processors* data sheet (literature number SPRS104A). The SPRS104A data sheet has been replaced with SPRS104C, when the TMS320C6203 device was moved back to SPRS086D and then later updated to become the TMS320C6203B device-specific data sheet (SPRS086I or later). Errata values relate solely to a specific revision of the silicon and do not appear in either data sheet.

#### **PLL Component Change**

#### Details:

New component values must be implemented to optimize the performance of the PLL on revision 2.x of the C6203B DSP. Earlier revisions should still use the values listed in the data sheet. The new values added to the PLL Component Selection Table of the C6203 (rev 1.x), C6203B (rev 2.x) data sheet are as follows:

- R1 45.3 Ω

- C1 47 nF

- C2 10 pF

Workaround:

Use the values in Table 2.

#### Table 2. TMS320C6203, TMS320C6203B PLL Component Selection Table<sup>†</sup>

| CLKMODE‡ | CLKIN<br>RANGE<br>(MHz) | CPU CLOCK<br>FREQUENCY<br>RANGE (MHz) | CLKOUT2<br>RANGE<br>(MHz) | R1 [±1%]<br>(Revision No.)        | C1 [±10%]<br>(Revision No.)     | C2 [±10%]<br>(Revision No.)      | TYPICAL<br>LOCK TIME<br>(μs) |

|----------|-------------------------|---------------------------------------|---------------------------|-----------------------------------|---------------------------------|----------------------------------|------------------------------|

| x4       | 32.5–75                 |                                       |                           |                                   |                                 |                                  |                              |

| x6       | 21.7–50                 |                                       |                           |                                   |                                 |                                  | 75                           |

| x7       | 18.6–42.9               |                                       |                           |                                   | 27 nF (1.x)<br>47 nF (2.x, 3.x) | 560 pF (1.x)<br>10 pF (2.x, 3.x) |                              |

| x8       | 16.3–37.5               | 130–300                               | 65–150                    | 60.4 Ω (1.x)<br>45.3 Ω (2.x, 3.x) |                                 |                                  |                              |

| x9       | 14.4–33.3               |                                       |                           | 45.5 \$2 (2.8, 5.8)               | 47 HF (2.X, 3.X)                |                                  |                              |

| x10      | 13–30                   |                                       |                           |                                   |                                 |                                  |                              |

| x11      | 11.8–27.3               |                                       |                           |                                   |                                 |                                  |                              |

<sup>†</sup> Under some operating conditions, the maximum PLL lock time may vary as much as 150% from the specified typical value. For example, if the typical lock time is specified as 100 μs, the maximum value may be as long as 250 μs.

<sup>‡</sup>CLKMODE x1, x4, x6, x7, x8, x9, x10, and x11 apply to the GLS device. The GJL device is restricted to x1, x4, x8, and x10 multiply factors.

| Advisory 2.5.1        | EMIF: Synchronous-Burst Memory AC Timing Differs From Data Sheet                                                                                                                                                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.5 and earlier                                                                                                                                                                                                                                                                                                                                  |

| Details:              | The timing parameters in Table 3 and Table 4 differ from the ones specified in the C6203 data sheet (SPRS104A) and the <i>TMS320C6203B Fixed-Point Digital Signal Processor</i> data sheet (SPRS086I or later). Table 3 and Table 4 list the differences between the data sheet values and the actual values on silicon revision 2.5 or earlier. |

|                       | The change in ac timings may cause SBSRAM interface timing violations, especially at low or high temperature conditions.                                                                                                                                                                                                                         |

| Table                 | 3. Timing Requirements For Synchronous-Burst SRAM Cycles                                                                                                                                                                                                                                                                                         |

| NO. |                                                         | SPRS   | •   | OLD VAL<br>-300 | UES) | 2.5 AN | ID EARI<br>-250, | LIER VAI<br>-300 | UES | UNIT |

|-----|---------------------------------------------------------|--------|-----|-----------------|------|--------|------------------|------------------|-----|------|

|     |                                                         | MIN    | MAX | MIN             | MAX  | MIN    | MAX              | MIN              | MAX |      |

| 8   | th(CKO2H-EDV) Hold time, read EDx valid after CLKOUT2 h | gh 2.0 |     | 1.5             |      | 2.0    |                  | 1.9              |     | ns   |

## Table 4. Switching Characteristics Over Recommended Operating Conditions For Synchronous-BurstSRAM Cycles 1‡

| NO. |                             | SPRS                                                             | 104A (O<br>-250, | LD VALU<br>-300 | ES)     | 2.5 AN | UNIT    |     |         |     |    |

|-----|-----------------------------|------------------------------------------------------------------|------------------|-----------------|---------|--------|---------|-----|---------|-----|----|

|     |                             |                                                                  | MIN              | MAX             | MIN     | MAX    | MIN     | MAX | MIN     | MAX |    |

| 2   | <sup>t</sup> oh(CKO2H-CEV)  | Output hold time, CEx valid after CLKOUT2 high                   | P – 3            |                 | P – 2.3 |        | P – 4.3 |     | P – 4.1 |     | ns |

| 4   | <sup>t</sup> oh(CKO2H-BEIV) | Output hold time, BEx invalid after CLKOUT2 high                 | P – 3            |                 | P – 2.3 |        | P – 4.3 |     | P – 4.1 |     | ns |

| 6   | <sup>t</sup> oh(CKO2H-EAIV) | Output hold time, EAx invalid after<br>CLKOUT2 high              | P – 3            |                 | P – 2.3 |        | P –4. 3 |     | P – 4.1 |     | ns |

| 10  | <sup>t</sup> oh(CKO2H-ADSV) | Output hold time, SDCAS/SSADS valid after CLKOUT2 high           | P – 3            |                 | P – 2.3 |        | P – 4.3 |     | P – 4.1 |     | ns |

| 12  | <sup>t</sup> oh(CKO2H-OEV)  | Output hold time, SDRAS/SSOE valid after CLKOUT2 high            | P – 3            |                 | P – 2.3 |        | P – 4.3 |     | P – 4.1 |     | ns |

| 13  | <sup>t</sup> osu(EDV-CKO2H) | Output setup time, EDx valid before<br>CLKOUT2 high <sup>§</sup> | P – 1.2          |                 | P + 0.1 |        | P – 1.2 |     | P – 0.3 |     | ns |

| 14  | <sup>t</sup> oh(CKO2H-EDIV) | Output hold time, EDx invalid after<br>CLKOUT2 high              | P – 3            |                 | P – 2.3 |        | P – 4.4 |     | P – 4.2 |     | ns |

| 16  | <sup>t</sup> oh(CKO2H-WEV)  | Output hold time, SDWE/SSWE valid after CLKOUT2 high             | P – 3            |                 | P – 2.3 |        | P – 4.3 |     | P – 4.1 |     | ns |

<sup>†</sup> P = 1/CPU clock frequency in ns. For example, when running parts at 300 MHz, use P = 3.3 ns.

\$ SDCAS/SSADS, SDRAS/SSOE, and SDWE/SSWE operate as SSADS, SSOE, and SSWE, respectively, during SBSRAM accesses.

§ For the first write in a series of one or more consecutive adjacent writes, the write data is generated one CLKOUT2 cycle early to accommodate the ED enable time.

#### Workaround:

Although these new numbers do not coincide with current memory specifications, no problems associated with these misalignments have been reported. It is suggested that the fastest available memories be used to reduce the possibility of setup and hold timing violations. Silicon revision 3.0 will correct this issue.

| Advisory 2.5.2        | EMIF: Synchronous DRAM AC Timing Differs From Data Sheet                                                                                                                                                                                                                                                                                         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.5 and earlier                                                                                                                                                                                                                                                                                                                                  |

| Details:              | The timing parameters in Table 5 and Table 6 differ from the ones specified in the C6203 data sheet (SPRS104A) and the <i>TMS320C6203B Fixed-Point Digital Signal Processor</i> data sheet (SPRS086I or later). Table 5 and Table 6 list the differences between the data sheet values and the actual values on silicon revision 2.5 or earlier. |

|                       | The change in ac timings may cause SDRAM interface timing violations, especially at low or high temperature conditions.                                                                                                                                                                                                                          |

| -                     | Table 5. Timing Requirements For Synchronous DRAM Cycles                                                                                                                                                                                                                                                                                         |

| NO. |                                                                         | SPR     | 104A (C<br>-250, | )LD VAL<br>-300 | UES) | 2.5 AN | D EAR<br>-250, | LIER VA<br>-300 | LUES | UNIT |

|-----|-------------------------------------------------------------------------|---------|------------------|-----------------|------|--------|----------------|-----------------|------|------|

|     |                                                                         | MIN     | MAX              | MIN             | MAX  | MIN    | MAX            | MIN             | MAX  |      |

| 7   | t <sub>su</sub> (EDV-CKO2H) Setup time, read EDx valid before CLKOUT2 h | igh 1.2 |                  | 0.5             |      | 1.2    |                | 1.2             |      | ns   |

| 8   | th(CKO2H-EDV) Hold time, read EDx valid after CLKOUT2 high              | 2.7     |                  | 2               |      | 2.9    |                | 2.8             |      | ns   |

## Table 6. Switching Characteristics Over Recommended Operating Conditions For Synchronous DRAM Cycles <sup>†‡</sup>

| NO. | P                            | ARAMETER                                                       | SPRS10  | LD VALUE<br>-300 | 2.5 AN  | UNIT |         |     |         |  |    |

|-----|------------------------------|----------------------------------------------------------------|---------|------------------|---------|------|---------|-----|---------|--|----|

|     |                              | MIN                                                            | MAX     | MIN              | MAX     | MIN  | MAX     | MIN | MAX     |  |    |

| 1   | <sup>t</sup> osu(CEV-CKO2H)  | Output setup time, CEx valid before CLKOUT2 high               | P – 0.9 |                  | P + 0.6 |      | P – 0.9 |     | Р       |  | ns |

| 2   | <sup>t</sup> oh(CKO2H-CEV)   | Output hold time, CEx valid after CLKOUT2 high                 | P – 2.9 |                  | P – 1.8 |      | P – 4.2 |     | P – 4.0 |  | ns |

| 3   | <sup>t</sup> osu(BEV-CKO2H)  | Output setup time, BEx valid before CLKOUT2 high               | P – 0.9 |                  | P + 0.6 |      | P – 0.9 |     | Р       |  | ns |

| 4   | <sup>t</sup> oh(CKO2H-BEIV)  | Output hold time, BEx invalid after CLKOUT2 high               | P – 2.9 |                  | P – 1.8 |      | P – 4.2 |     | P – 4.0 |  | ns |

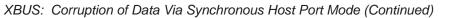

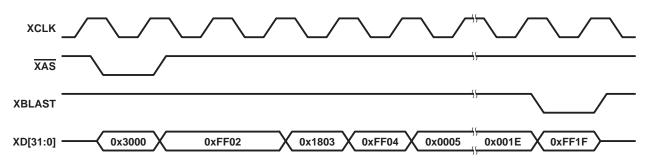

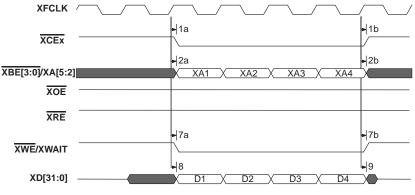

| 5   | <sup>t</sup> osu(EAV-CKO2H)  | Output setup time, EAx valid before CLKOUT2 high               | P – 0.9 |                  | P + 0.6 |      | P – 0.9 |     | Р       |  | ns |