TMS320VC5503 Digital Signal Processor Silicon Errata

> SPRZ218C April 2004 – Revised April 2008

### **REVISION HISTORY**

This revision history highlights the technical changes made to SPRZ218B to generate SPRZ218C.

Scope:

Make changes to Section 3.10 Power Management Advisories

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25             | Section 3.10, Power Management Advisories:<br>- Advisory PM_1. The Title changed <b>from</b><br>"Repeated Interrupts During CPU Idle" <b>to</b><br>"Repeated Interrupts Durring CLKGEN Domain Idle".<br>Details:<br>- Changed instances of CPU in idle state <b>from</b> "CPU" <b>to</b> "CLKGEN"<br>Workaround:<br>- Changed instances of CPU in idle state <b>from</b> "CPU" <b>to</b> "CLKGEN" |

## Contents

| 1 | Intro | ntroduction             |                                                                                                                                                                                                                       |     |  |

|---|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

|   | 1.1   | Device ar               | nd Development-Support Tool Nomenclature                                                                                                                                                                              | . 5 |  |

|   | 1.2   | Revision                | Identification                                                                                                                                                                                                        | . 6 |  |

| 2 | Usa   | ge Notes .              |                                                                                                                                                                                                                       | . 7 |  |

|   |       | RTC: Sec                | onds Alarm Functionality                                                                                                                                                                                              | . 7 |  |

| 3 | Kno   | -                       | Marginality/Exceptions to Functional Specifications                                                                                                                                                                   |     |  |

|   | 3.1   | Summary                 | of Advisories                                                                                                                                                                                                         | . 8 |  |

|   | 3.2   | Device-Le               | evel Advisories                                                                                                                                                                                                       | 10  |  |

|   |       | DL_2<br>DL_7            | Software Modification of MPNMC Bit is Not Pipeline-Protected<br>RETI Instruction may Affect the XF State                                                                                                              | 10  |  |

|   |       | DL_10                   | First Word of Data on Consecutive DMA Transmissions Using McBSP is Lost                                                                                                                                               |     |  |

|   | 3.3   |                         | mory Access (DMA) Advisories                                                                                                                                                                                          |     |  |

|   |       | DMA_1<br>DMA_2          | Early Sync Event Stops Block Transfer<br>DMA Does Not Support Burst Transfers From EMIF to EMIF                                                                                                                       |     |  |

|   | 3.4   | External                | Memory Interface (EMIF) Advisories                                                                                                                                                                                    | 13  |  |

|   |       | EMIF_8<br>EMIF_9        | ARDY Pin Requires Strong Pullup Resistor         External Memory Write After Read Reversal                                                                                                                            |     |  |

|   |       |                         | Block Write Immediately Following a Block Read May Cause Data Corruption                                                                                                                                              |     |  |

|   |       | EMIF_11                 | EMIF Asynchronous Access Hold = 0 is Not Valid for Strobe > 3                                                                                                                                                         |     |  |

|   |       |                         | 8-Bit Asynchronous Writes on 5503 EMIF Not Supported<br>After Changing CE Control Registers and Disabling SDRAM Clock in Divide-by-8 and<br>Divide-by-16 Modes, Asynchronous Access Followed by SDRAM Access Will Not |     |  |

|   |       |                         | Supply a Ready Signal to CPU                                                                                                                                                                                          |     |  |

|   |       |                         | SETUP = 2 Configuration is not Valid for Asynchronous Memory                                                                                                                                                          |     |  |

|   | 3.5   |                         | d Host Port Interface (EHPI) Advisories                                                                                                                                                                               |     |  |

|   |       | EHPI_5<br>EHPI_6        | HPID Read Following a HPID Write While HRDY Low Corrupts the Read                                                                                                                                                     | 17  |  |

|   |       |                         | Address to Increment to the Incorrect Address                                                                                                                                                                         | 17  |  |

|   | 3.6   | Real-Time               | e Clock (RTC) Advisories                                                                                                                                                                                              | 18  |  |

|   |       | RTC_3<br>RTC_4<br>RTC_5 | RTC Interrupts are Perceived by the User as Happening One Second BeforeAny Year Ending in 00 Will Appear as a Leap YearMidnight and Noon Transitions Do Not Function Correctly in 12h Mode                            | 18  |  |

|   | 3.7   |                         | grated Circuit (I <sup>2</sup> C) Advisories                                                                                                                                                                          |     |  |

|   | 0.7   | 12C_3<br>12C_5          | ARDY Interrupt is not Generated Properly in Non-Repeat Mode if STOP Bit is Set         Repeated Start Mode Does Not Work                                                                                              | 20  |  |

|   |       |                         |                                                                                                                                                                                                                       |     |  |

|                                     | I2C_6                       | Bus Busy Bit Does Not Reflect the State of the $I^2C$ Bus When the $I^2C$ is in Reset    |    |  |

|-------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|----|--|

|                                     | I2C_8                       | DMA Receive Synchronization Pulse Gets Generated Falsely                                 | 21 |  |

| 3.8                                 | Multicha                    | nnel Buffered Serial Port (McBSP) Advisories                                             | 22 |  |

|                                     | MCBSP_                      | 1 McBSP May Not Generate a Receive Event to DMA When Data Gets Copied<br>From RSR to DRR | 22 |  |

| 3.9                                 | 3.9 Emulation Advisories 23 |                                                                                          |    |  |

|                                     | EMU_1                       | Emulation Prone to Failure Under Certain Situations                                      | 23 |  |

| 3.10 Power Management Advisories 25 |                             |                                                                                          | 25 |  |

|                                     | PM_1                        | Repeated Interrupts During CPU Idle                                                      | 25 |  |

| 3.11                                | Hardware                    | e Accelerator Advisories                                                                 | 26 |  |

|                                     | HWA_1                       | Pixel Interpolation Hardware Accelerator                                                 | 26 |  |

| Documentation Support               |                             |                                                                                          |    |  |

4

#### 1 Introduction

This document describes the silicon updates to the functional specifications for the TMS320VC5503. The updates are applicable to:

- TMS320VC5503 (144-pin LQFP, PGE suffix)

- TMS320VC5503 (179-pin MicroStar BGA™, GHH suffix)

The advisory numbers in this document are not always sequential. Some advisory numbers have been removed as they do not apply to the device revisions specified in this document. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

Issues related to CPU operation are documented in the *TMS320C55x DSP CPU Programmer's Reference Supplement* (literature number SPRU652).

#### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all TMS320<sup>™</sup> DSP devices and support tools. Each TMS320<sup>™</sup> DSP commercial family member has one of three prefixes: TMX, TMP, or TMS. Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- TMS Fully qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

- TMDS Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

MicroStar BGA and TMS320 are trademarks of Texas Instruments. Other trademarks are the property of their respective owners.

#### 1.2 Revision Identification

The device revision can be determined by the lot trace code marked on the top of the package. The locations for the lot trace codes for the PGE and the GHH packages are shown in Figure 1 and Figure 2, respectively. The location of other markings may vary per device.

Qualified devices in the PGE and GHH packages are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

Lot Trace Code

### Figure 1. Example Markings for VC5503, PGE Package, Revision 1.0

Figure 2. Example Markings for VC5503, GHH Package, Revision 1.0

### 2 Usage Notes

Usage Notes highlight and describe particular situations where the device's behavior may not match the presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

### **RTC: Seconds Alarm Functionality**

On the 5503 device, the Seconds Alarm Register (RTCSECA) *cannot* be used to generate an alarm every second, but the update-ended interrupt can.

The Real-Time Clock (RTC) executes an update cycle once per second to update the current time in the time/calendar registers:

- Seconds Register (RTCSEC)

- Minutes Register (RTCMIN)

- Hours Register (RTCHOUR)

- Day of the Week and Day Alarm Register (RTCDAYW)

- Day of the Month (Date) Register (RTCDAYM)

- Month Register (RTCMONTH)

- Year Register (RTCYEAR)

At the end of every update cycle, the RTC sets the update-ended interrupt flag (UF) in the Interrupt Flag Register (RTCINTFL). If the update-ended interrupt enable bit (UIE) in the Interrupt Enable Register (RTCINTEN) is set to 1, an interrupt request is sent to the CPU.

### TMS320VC5503 Silicon Errata

## 3 Known Design Marginality/Exceptions to Functional Specifications

### 3.1 Summary of Advisories

Table 1 provides a quick reference of all advisories by number, silicon revision affected, and lists their respective page location.

| Advisory<br>Number | Advisory                                                                                                                                                                                   | Revision(s)<br>Affected | Page     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|

|                    | Device-Level Advisories                                                                                                                                                                    | -                       | <u>.</u> |

| DL_2               | Software Modification of MPNMC Bit is Not Pipeline-Protected                                                                                                                               | 1.0                     | 10       |

| DL_7               | RETI Instruction may Affect the XF State                                                                                                                                                   | 1.0                     | 10       |

| DL_10              | First Word of Data on Consecutive DMA Transmissions Using McBSP is Lost                                                                                                                    | 1.0                     | 11       |

|                    | Direct Memory Access (DMA) Advisories                                                                                                                                                      | •                       |          |

| DMA_1              | Early Sync Event Stops Block Transfer                                                                                                                                                      | 1.0                     | 12       |

| DMA_2              | DMA Does Not Support Burst Transfers From EMIF to EMIF                                                                                                                                     | 1.0                     | 12       |

|                    | External Memory Interface (EMIF) Advisories                                                                                                                                                | -                       |          |

| EMIF_8             | ARDY Pin Requires Strong Pullup Resistor                                                                                                                                                   | 1.0                     | 13       |

| EMIF_9             | External Memory Write After Read Reversal                                                                                                                                                  | 1.0                     | 13       |

| EMIF_10            | Block Write Immediately Following a Block Read May Cause Data Corruption                                                                                                                   | 1.0                     | 14       |

| EMIF_11            | EMIF Asynchronous Access Hold = 0 is Not Valid for Strobe > 3                                                                                                                              | 1.0                     | 14       |

| EMIF_12            | 8-Bit Asynchronous Writes on 5503 EMIF Not Supported                                                                                                                                       | 1.0                     | 15       |

| EMIF_13            | After Changing CE Control Registers and Disabling SDRAM Clock in Divide-by-8 and Divide-by-16<br>Modes, Asynchronous Access Followed by SDRAM Access Will Not Supply a Ready Signal to CPU | 1.0                     | 15       |

| EMIF_14            | SETUP = 2 Configuration is not Valid for Asynchronous Memory                                                                                                                               | 1.0                     | 16       |

|                    | Enhanced Host Port Interface (EHPI) Advisories                                                                                                                                             |                         | •        |

| EHPI_5             | HPID Read Following a HPID Write While HRDY Low Corrupts the Read                                                                                                                          | 1.0                     | 17       |

| EHPI_6             | HPIC/HPIA Access Following an Autoincremented HPID Write Causes Next HPID Address to Increment to the Incorrect Address                                                                    | 1.0                     | 17       |

|                    | Real-Time Clock (RTC) Advisories                                                                                                                                                           | -                       |          |

| RTC_3              | RTC Interrupts are Perceived by the User as Happening One Second Before                                                                                                                    | 1.0                     | 18       |

| RTC_4              | Any Year Ending in 00 Will Appear as a Leap Year                                                                                                                                           | 1.0                     | 18       |

| RTC_5              | Midnight and Noon Transitions Do Not Function Correctly in 12h Mode                                                                                                                        | 1.0                     | 19       |

|                    | Inter-Integrated Circuit (I <sup>2</sup> C) Advisories                                                                                                                                     |                         |          |

| I2C_3              | ARDY Interrupt is not Generated Properly in Non-Repeat Mode if STOP Bit is Set                                                                                                             | 1.0                     | 20       |

| I2C_5              | Repeated Start Mode Does Not Work                                                                                                                                                          | 1.0                     | 20       |

| I2C_6              | Bus Busy Bit Does Not Reflect the State of the $I^2C$ Bus When the $I^2C$ is in Reset                                                                                                      | 1.0                     | 21       |

| I2C_8              | DMA Receive Synchronization Pulse Gets Generated Falsely                                                                                                                                   | 1.0                     | 21       |

| Table 1 | Quick | Reference    | Table |

|---------|-------|--------------|-------|

|         | QUICK | IVELEI ELICE | Table |

| Advisory<br>Number                                   | Advisory                                                                            | Revision(s)<br>Affected | Page |

|------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------|------|

| Multichannel Buffered Serial Port (McBSP) Advisories |                                                                                     |                         |      |

| MCBSP_1                                              | McBSP May Not Generate a Receive Event to DMA When Data Gets Copied From RSR to DRR | 1.0                     | 22   |

| Emulation Advisories                                 |                                                                                     |                         |      |

| EMU_1                                                | Emulation Prone to Failure Under Certain Situations                                 | 1.0                     | 23   |

| Power Management Advisories                          |                                                                                     |                         |      |

| PM_1                                                 | Repeated Interrupts During CPU Idle                                                 | 1.0                     | 25   |

| Hardware Accelerator Advisories                      |                                                                                     |                         |      |

| HWA_1                                                | Pixel Interpolation Hardware Accelerator                                            | 1.0                     | 26   |

### Table 1. Quick Reference Table (Continued)

## TMS320VC5503 Silicon Errata

### 3.2 Device-Level Advisories

| Advisory DL_2           | Software Modification of MPNMC Bit is Not Pipeline-Protected                                                                                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                       |

| Details:                | Software modification of the MPNMC bit in status register 3 (ST3_55) is not pipeline-protected so changes to the device memory map may not become valid before the instructions that immediately follow the modification. |

| Assembler Notification: | None                                                                                                                                                                                                                      |

| Workaround:             | Insert six NOPs after the MPNMC modification.                                                                                                                                                                             |

| Advisory DL_7           | RETI Instruction may Affect the XF State                                                                                                                                                                                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                       |

| Details:                | The XF pin state is saved on the stack as a part of the ST1 context saving during interrupts servicing. If the XF pin state is changed inside the ISR, upon execution of the RETI, the XF bit will be restored to the value prior to entering the ISR. If XF state is not changed inside the ISR, then there is no issue. |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                      |

| Workaround:             | BIOS takes care of this problem with software workaround, which is transparent to the users.<br>Non-BIOS users who are changing XF pin state in an ISR should also modify the ST1 value<br>on the stack to maintain the correct XF pin state upon exiting the ISR.                                                        |

| Advisory DL_10          | First Word of Data on Consecutive DMA Transmissions Using McBSP is Lost                                                                                                                                                                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                                            |

| Details:                | When executing multiple DMA transfers consecutively using the same DMA Transmit Channel<br>and McBSP, an extra DMA TX request generated by the McBSP at the end of the first transfer<br>will not be serviced by the DMA until the next DMA transfer is initiated by the McBSP. At the<br>next DMA transfer, this DMA TX request will be serviced as soon as the DMA TX channel is<br>enabled. |

|                         | This transmitted data will remain valid on the bus as long as the McBSP is disabled. However, once the McBSP is enabled, it sends out another DMA TX request, and the DMA transmits the second word. This results in the loss of the first word of data on consecutive DMA transmissions.                                                                                                      |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                                                                                           |

| Workaround:             | Only the systems where McBSP is turned off following each block of DMA transfer are affected. In such case, a dummy DMA transfer with the DMA synchronization event set to no sync event will flush out the pending TX request from the McBSP before programming the DMA to send the next block of data to the McBSP.                                                                          |

### 3.3 Direct Memory Access (DMA) Advisories

| Advisory DMA_1          | Early Sync Event Stops Block Transfer                                                                                                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                            |

| Details:                | When a DMA block transfer is initiated by a sync event, if the same sync event occurs before the last element of the block transfer has been completed, an event drop occurs and the channel becomes disabled. |

| Assembler Notification: | None                                                                                                                                                                                                           |

| Workaround:             | Ensure that the duration between the sync events is long enough to allow the block transfer to complete. The DMA end-of-block interrupt can be used as an indicator.                                           |

| Advisory DMA_2          | DMA Does Not Support Burst Transfers From EMIF to EMIF                                                                                                                                                         |

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                            |

| Details:                | The DMA controller does not support burst mode transfers with the EMIF as both the source and the destination port.                                                                                            |

| Assembler Notification: | None                                                                                                                                                                                                           |

| Workaround:             | Do not use burst mode for EMIF-to-EMIF transfers.                                                                                                                                                              |

### 3.4 External Memory Interface (EMIF) Advisories

| Advisory EMIF_8         | ARDY Pin Requires Strong Pullup Resistor                                                                                                              |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                   |

| Details:                | When the parallel bus is used to access external memory, a strong pullup resistor is required for the ARDY pin for the asynchronous memory interface. |

| Assembler Notification: | None                                                                                                                                                  |

| Workaround:             | Pull up ARDY with a 2.2-k $\Omega$ resistor.                                                                                                          |

| Advisory EMIF_9         | External Memory Write After Read Reversal                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                      |

| Details:                | If an external memory write is followed immediately by an external memory read, the external memory read will occur first, followed by the write. See the example below. |

|                         | Example:<br>MOV #1770h, *(100001h) ; External Memory Write<br>MOV *(#100000h), AR1 ; External Memory Read                                                                |

| Assembler Notification: | None                                                                                                                                                                     |

| Workaround:             | Insert two NOPs between the memory write/read pair.                                                                                                                      |

|                         | Example:<br>MOV #1770h, *(10000lh) ; External Memory Write<br>NOP<br>NOP<br>MOV *(#100000h), AR1 ; External Memory Read                                                  |

| Advisory EMIF_10        | Block Write Immediately Following a Block Read May Cause Data Corruption                                                                                                            |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                 |

| Details:                | When performing a block write immediately following a block read, data may get corrupted. See the example below.                                                                    |

|                         | Example:<br>Write 0x55 to addr1<br>Write 0xAA to addr2<br>Read addr1<br>Read addr2                                                                                                  |

|                         | When executed, the above code will follow this order:<br>Write 0x55 to addr1<br>Read addr1<br>Write 0xAA to addr2<br>Read addr2                                                     |

| Assembler Notification: | None                                                                                                                                                                                |

| Workaround:             | Insert two NOPs between write and read. Since reads occur before writes in the pipeline, the read must be delayed after the write so that the read does not occur before the write. |

| Advisory EMIF_11        | EMIF Asynchronous Access Hold = 0 is Not Valid for Strobe > 3                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                |

| Details:                | For asynchronous EMIF accesses, a hold time of 0 is not valid for strobe lengths greater than 3 cycles if the ARDY_OFF bit is not set. If the above configuration is used but the ARDY_OFF bit is clear, then the EMIF automatically gives a hold time of 1 cycle. |

| Assembler Notification: | None                                                                                                                                                                                                                                                               |

| Workaround:             | None                                                                                                                                                                                                                                                               |

| Advisory EMIE 12        | 9 Dit Asymptronous Writes on EE02 EMIE Not Supported                                                                                                                                                                                                                       |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory EMIF_12        | 8-Bit Asynchronous Writes on 5503 EMIF Not Supported                                                                                                                                                                                                                       |

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                        |

| Details:                | 8-bit asynchronous writes are not supported; however, 8-bit asynchronous reads are supported.                                                                                                                                                                              |

| Assembler Notification: | None                                                                                                                                                                                                                                                                       |

| Workaround:             | None                                                                                                                                                                                                                                                                       |

| Advisory EMIF_13        | After Changing CE Control Registers and Disabling SDRAM Clock in Divide-by-8 and<br>Divide-by-16 Modes, Asynchronous Access Followed by SDRAM Access Will Not Supply<br>a Ready Signal to CPU                                                                              |

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                        |

| Details:                | If the SDRAM clock (EMIF.CLKMEM) is set to divide-by-8 and divide-by-16 of the CPU clock<br>and if the user disables the SDRAM clock before accessing asynchronous memory, the EMIF<br>will fail to supply the ready signal to the CPU under the following two conditions: |

|                         | <ul> <li>Case 1:<br/>SDRAM access</li> <li>Switch off the SDRAM clock</li> <li>Change CE Space Control Register to Asynchronous Mode</li> <li>Perform an asynchronous access to the <i>same</i> CE space</li> </ul>                                                        |

|                         | <ul> <li>Case 2:<br/>SDRAM access</li> <li>Switch off the SDRAM clock</li> <li>Change CE Space Control Register to Asynchronous Mode</li> <li>Perform an asynchronous access to a <i>different</i> CE space</li> </ul>                                                     |

|                         | This failure of the ready signal will make the CPU wait indefinitely.                                                                                                                                                                                                      |

| Assembler Notification: | None                                                                                                                                                                                                                                                                       |

| Workaround:             | Switch the SDRAM clock to divide-by-1 before programming the CE Space Control Register to asynchronous memory.                                                                                                                                                             |

| Advisory EMIF_14        | SETUP = 2 Configuration is not Valid for Asynchronous Memory                                                                                               |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                        |

| Details:                | When using the EMIF in asynchronous memory mode, a read or write SETUP time setting of two clocks actually behaves like timing of one clock of setup time. |

| Assembler Notification: | None                                                                                                                                                       |

| Workaround:             | If a read setup time of two clocks is required for asynchronous memory, a value of three clock cycles must be used.                                        |

### TMS320VC5503 Silicon Errata

### 3.5 Enhanced Host Port Interface (EHPI) Advisories

| Advisory EHPI_5         | HPID Read Following a HPID Write While HRDY Low Corrupts the Read                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details:                | Whether in muxed or non-muxed mode, if a data read overlaps with a HRDY low from a previous data write, the EHPI address used for the read access will be the same as the one preceding the data write.                                                                                                                                                                                                                                                                 |

|                         | The only case not affected by this bus is the non-autoincremented write->read from the same address. In the case of autoincremented write followed by autoincremented read, normally, the address will be incremented after the write, but if the read access is initiated while the HRDY is low, it will not be incremented due to the problem. If one more autoincremented read is performed after this, the EHPI address used will be twice the incremented version. |

| Assembler Notification: | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Workaround:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | <ul> <li>Muxed Mode: Following a sequence of EHPI write(s), perform a HPIA update before<br/>initiating an EHPI read access.</li> </ul>                                                                                                                                                                                                                                                                                                                                 |

|                         | <ul> <li>Non-Muxed Mode: Following a sequence of EHPI write(s), add a dummy HPID read<br/>before initiating the actual EHPI read access.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

| Advisory EHPI_6         | HPIC/HPIA Access Following an Autoincremented HPID Write Causes Next HPID<br>Address to Increment to the Incorrect Address                                                                                                                                                                                                                                                                                                                                              |

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details:                | If any HPIA/HPIC access is pipelined with a previous autoincremented write, the succeeding autoincremented HPID access (whether write or read) will use the same address as the previous write. In other words, the address will not be incremented. Only Muxed Mode is affected.                                                                                                                                                                                       |

**Workaround**: Muxed Mode: Following a sequence of EHPI write(s), perform an HPIA update before initializing an EHPI read/write access.

Assembler Notification: None

## TMS320VC5503 Silicon Errata

## 3.6 Real-Time Clock (RTC) Advisories

| Advisory RTC_3          | RTC Interrupts are Perceived by the User as Happening One Second Before                                                                                                                                                                                                                                                                                                                              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:                | When the user reads the Real Time Clock time register, these register are read one second after the RTC's internal timer counter register. The RTC interrupts are triggered by the internal counter register, thus it seems to the user that the interrupt was triggered one second earlier. For example, an alarm set to every minute alarm generates an interrupt at xx:xx:59 instead of xx:xx:00. |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                                                                                                 |

| Workaround:             | Take into account the one second difference when using the alarm interrupt.                                                                                                                                                                                                                                                                                                                          |

| Advisory RTC_4          | Any Year Ending in 00 Will Appear as a Leap Year                                                                                                                                            |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                         |

| Details:                | Since the year can be varied from 00–99 only, any year ending with 00 will always appear as a Leap Year, which is not always the case. For example, 2100 ends in 00 and is not a Leap Year. |

| Assembler Notification: | None                                                                                                                                                                                        |

| Workaround:             | None                                                                                                                                                                                        |

| Advisory RTC_5          | Midnight and Noon Transitions Do Not Function Correctly in 12h Mode                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                        |

| Details:                | The normal transition from Midnight and Noon should be the following:                                      |

|                         | 11:59am $\rightarrow$ 12:00pm $\rightarrow$ 12:59pm $\rightarrow$ 1:00pm                                   |

|                         | 11:59pm $\rightarrow$ 12:00am $\rightarrow$ 12:59am $\rightarrow$ 1:00am                                   |

|                         | However, if the RTC is used in the 12h time format, the transitions around Noon and Midnight are as below: |

|                         | 11:59am $\rightarrow$ 12:00am $\rightarrow$ 12:59am $\rightarrow$ 1:00pm                                   |

|                         | 11:59pm $\rightarrow$ 12:00pm $\rightarrow$ 12:59pm $\rightarrow$ 1:00am                                   |

| Assembler Notification: | None                                                                                                       |

| Workaround:             | The problem can be worked around using the 24h mode.                                                       |

# 3.7 Inter-Integrated Circuit (I<sup>2</sup>C) Advisories

| Advisory I2C_3          | ARDY Interrupt is not Generated Properly in Non-Repeat Mode if STOP Bit is Set                                                                                                                                                                                                                                                |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                           |

| Details:                | In non-repeat mode, if the STP bit of ICMDR is set, the master sends the STOP condition and does not assert ARDY interrupt after sending data. If the STP bit is set, the I <sup>2</sup> C sends the STOP condition and clears the ARDY bit.                                                                                  |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                          |

| Workaround:             | If the ARDY interrupt is desired after sending data, start the data transfer without setting the STP bit. If the STOP bit is not set beforehand, the master will not send the STOP condition and asserts the ARDY interrupt after sending the data. Set the STP bit when the last ARDY interrupt arrives (all data sent out). |

| Advisory I2C_5          | Repeated Start Mode Does Not Work                                     |

|-------------------------|-----------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                   |

| Details:                | Repeated Start Mode does not work on the I <sup>2</sup> C peripheral. |

| Assembler Notification: | None                                                                  |

| Workaround:             | None                                                                  |

| Advisory I2C_6          | Bus Busy Bit Does Not Reflect the State of the $I^2C$ Bus When the $I^2C$ is in Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Details:                | The Bus Busy bit (BB) indicates the status of the I <sup>2</sup> C bus. The Bus Busy bit is set to '0' when the bus is free and set to '1' when the bus is busy. The I <sup>2</sup> C peripheral cannot detect the state of the I <sup>2</sup> C bus when it is in reset (IRS bit is set to '0'); therefore, the Bus Busy bit will keep the state it was at when the peripheral was placed in reset. The Bus Busy bit will stay in that state until the I <sup>2</sup> C peripheral is taken out of reset (IRS bit set to '1') and a START condition is detected on the I <sup>2</sup> C bus. When the device is powered up, the Bus Busy bit will stay stuck at the default value of '0' until the IRS bit is set to '1' and the I <sup>2</sup> C peripheral detects a START condition. |

|                         | Systems using a multi-master configuration can be affected by this issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Workaround:             | Wait a certain period after taking the I <sup>2</sup> C peripheral out of reset (setting the IRS bit to '1') before starting the first data transfer. The period should be set equal to or larger than the total time it takes for the longest data transfer in the application. By waiting this amount of time, it can be ensured that any previous transfers finished. After this point, BB will correctly reflect the state of the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                              |

| Advisory I2C_8          | DMA Receive Synchronization Pulse Gets Generated Falsely                                                                                                                                                                                                                                                                                                                   |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                                                                                                                        |

| Details:                | When receiving an I <sup>2</sup> C data stream in master mode (i.e., a read is performed), and the DMA is started, a DMA synchronization event is triggered upon enabling the DMA channel if a byte is present in the DRR (even if it has already been read). This leads to the first byte read being a duplicate of the previous byte that was already read from the DRR. |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                                                                                       |

| Workaround:             | Set DMA transfers from DRR to read one more byte than necessary and discard the first byte.                                                                                                                                                                                                                                                                                |

### 3.8 Multichannel Buffered Serial Port (McBSP) Advisories

| Advisory MCBSP_1        | McBSP May Not Generate a Receive Event to DMA When Data Gets Copied<br>From RSR to DRR                                                                                                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | 1.0                                                                                                                                                                                                                                                                              |

| Details:                | When there is heavy peripheral activity, and the DRR is read, a new receive interrupt might not be generated to the DMA when data in the RSR is copied to the DRR. When this condition occurs, the McBSP overwrites the DRR before the DMA had an opportunity to read its value. |

|                         | This problem arises when the DRR read occurs at the "exact moment" the REVT needs to be generated. The DRR servicing gets delayed if there are other heavy DMA channels or CPU activities on the peripheral bus.                                                                 |

| Assembler Notification: | None                                                                                                                                                                                                                                                                             |

| Workaround:             | Optimize the peripheral bus access by the CPU and the DMA by carefully scheduling the DMA and CPU activities so the DMA channel servicing the DRR is not stalled to the point where new data is about the move in the DRR.                                                       |

### 3.9 Emulation Advisories

| Advisory EMU_1        | Emulation Prone to Failure Under Certain Situations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision(s) Affected: | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Details:              | Under certain conditions, the emulation hardware may corrupt the emulation control state machine or may cause it to lose synchronization with the emulator software. When emulation commands fail as a result of the problem, Code Composer Studio <sup>™</sup> Integrated Development Environment (IDE) may be unable to start or it may report errors when interacting with the TMS320C55x <sup>™</sup> DSP (for example, when halting the CPU, reaching a breakpoint, etc.).                                                                       |  |  |  |

|                       | This phenomenon is observed when an erroneous clock edge is generated from the TCK signal inside the $C55x^{TM}$ DSP. This can be caused by several factors, acting independently or cumulatively:                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                       | • TCK transition times (as measured between 2.5 V and 0.6 V) in excess of 3 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                       | <ul> <li>Operating the C55x DSP in a socket, which can aggravate noise or glitches on the<br/>TCK input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                       | <ul> <li>Poor signal integrity on the TCK line from reflections or other layout issues.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

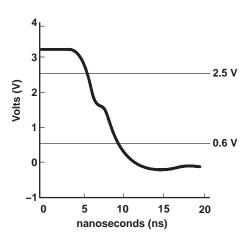

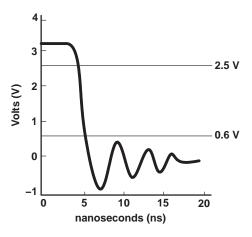

|                       | A TCK edge that can cause this problem might look similar to the one shown in Figure 3. A TCK edge that does not cause the problem will look similar to the one shown in Figure 4. The key difference between the two figures is that Figure 4 has a clean and sharp transition whereas Figure 3 has a "knee" in the transition zone. Problematic TCK signals may not have a knee that is as pronounced as the one in Figure 3. Due to the TCK signal amplification inside the chip, any perturbation of the signal can create erroneous clock edges. |  |  |  |

|                       | As a result of the faster edge transition, there is increased ringing in Figure 4. As long as the ringing does not cross logic input thresholds (0.6 V for falling edges, and 2.5 V for rising edges), this ringing is acceptable.                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                       | When examining a TCK signal for this issue, either in board simulation or on an actual board, it is very important to probe the TCK line as close to the DSP input pin as possible. In simulation, it should not be difficult to probe right at the DSP input. For most physical boards, this means using the via for the TCK pad on the back side of the board. Similarly, ground for the probe should come from one of the nearby ground pad vias to minimize EMI noise picked up by the probe.                                                     |  |  |  |

Code Composer Studio, TMS320C55x, and C55x are trademarks of Texas Instruments.

Emulation Prone to Failure Under Certain Situations (Continued)

Figure 3. Bad TCK Transition

Figure 4. Good TCK Transition

Workaround: As the problem may be caused by one or more of the above factors, one or more of the steps outlined below may be necessary to fix it:

- Avoid using a socket

- Ensure the board design achieves rise times and fall times of less than 3 ns with clean monotonic edges for the TCK signal.

- For designs where TCK is supplied by the emulation pod, use a C55x Emulation Adapter Board, part number DSP8102U. To order a C55x Emulation Adapter Board, please contact the TI Product Information Center (PIC).

| Advisory PM_1           | Repeated Interrupts During CLKGEN Domain Idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|