# Technical Article Complete Clock-tree Solutions That Make a Hardware Designer's Life Easier

Arvind Sridhar

Are you solving your system clocking needs using discrete crystals and clock oscillators? It does seem like an obvious approach for most hardware designers, who do not have the time to scour the internet for optimized clock-tree solutions including clock generator ICs and buffer/distribution devices. Although less time consuming, the approach of using discrete crystals and oscillators can often lead to an increase in bill-of-materials (BOM) cost and lower performance of the overall system. WEBENCH® Clock Architect is the industry's first clock and timing tool that recommends a system clock-tree solution covering devices from TI's extensive clocking portfolio. The patented, multiple-part recommendation algorithm – the backbone of the tool – provides quick solutions and a hassle-free experience for designers searching for high-performance, flexible clocking solutions.

Aside from recommending optimized clock-tree solutions, the tool features advanced phased-locked loop (PLL) filter-design capability and phase-noise simulation, enabling you to simulate and optimize clock-tree designs to meet your system needs. Let's take a look at some of the more recent feature upgrades.

You can now enter custom phase-noise profiles for external references such as crystal oscillators (XOs), voltage-controlled crystal oscillators (VCXOs) and voltage-controlled oscillators (VCOs). Accurate modeling of external reference sources helps greatly improve the accuracy of the device output clock-phase noise/jitter-simulation results. See Figure 1.

1

|                                                | CLOCK                                                                                    | ARCHITECT                                             |  |  |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| 1. Click here                                  | LMK03318                                                                                 |                                                       |  |  |  |  |

|                                                | Enter Custom Phase Noise for Reference or VCO/VCXO For device details.see product folder |                                                       |  |  |  |  |

|                                                | Outputs LoopFilter 2. Enter custom phase noi                                             | se of reference clock                                 |  |  |  |  |

| Input LMK03318                                 |                                                                                          |                                                       |  |  |  |  |

| So Mitz D Input                                | CLKOUT0 CLKOUT2 CLKOUT4                                                                  |                                                       |  |  |  |  |

| VCO LVPECL 156-25 MHz                          |                                                                                          | ioise Metrics as measured at CLKOUT0, LVPECL : 156.25 |  |  |  |  |

| 5000 MHz LVDS 123.0 MHz 50.0 MHz               | Integrated Noise Metrics                                                                 | Phase Noise                                           |  |  |  |  |

| LVCMOS                                         | Phase Noise Integration Rar Load Custom Plase Nois                                       | 4                                                     |  |  |  |  |

|                                                | 12 kHz to Set custom phase noise for:                                                    | REF I                                                 |  |  |  |  |

| -                                              | Phase Noise Area     x (kHz)     y (dBc/Hz)                                              |                                                       |  |  |  |  |

| Project ID: 537                                | O Spur Area                                                                              | Total<br>REF                                          |  |  |  |  |

| Project Name: Project 537 - [LMK03318]         | <ul> <li>Both Phase Noise and St</li> </ul>                                              |                                                       |  |  |  |  |

| Total Cost: \$7.50 (1ku)<br>Total Area: 49 mm* | Noise Metric                                                                             | Ciear & Reset Noise                                   |  |  |  |  |

| Total Current: 349.5 mA                        | RMS Jitter                                                                               | Set custom phase noise                                |  |  |  |  |

| Jitter Metric: 110 fs                          | Equivalent Flat Noise                                                                    | CLKOUTD                                               |  |  |  |  |

| Description:                                   | SAR Add row Delete row                                                                   |                                                       |  |  |  |  |

| Notes:                                         | Tin: You can now two column                                                              | thom Microsoft Excel (or a tab-                       |  |  |  |  |

|                                                | Phase Noise delimited dataset) and paste i                                               | nto the grid above. Just click an                     |  |  |  |  |

| Update                                         | Offs empty row and then use CTRL                                                         | +V to paste.                                          |  |  |  |  |

| 1                                              | 12 Mil -141.2 dBCHZ                                                                      | 10 kHz 100 kHz 1 MHz 10 MHz 100 MHz                   |  |  |  |  |

|                                                | 100 kHz .139.4 dBcHz                                                                     | Offset Frequency (Hz)                                 |  |  |  |  |

|                                                | 20000 kHz .162.7 dBcHz                                                                   | Scaling                                               |  |  |  |  |

|                                                | Simulation Input                                                                         | X Min 12 kHz X Max 20 MHz Sport display               |  |  |  |  |

|                                                | X Min 12 kHz Number of Points: 101                                                       | Ymin .200 dBc Ymax .60 dBc O dBcMz                    |  |  |  |  |

|                                                | X Max 20 MHz Update Simulation Data                                                      | Reset to default ( OBc                                |  |  |  |  |

|                                                |                                                                                          | PLL Settings Spur Table                               |  |  |  |  |

|                                                |                                                                                          | Filter type: Designed Filter                          |  |  |  |  |

|                                                |                                                                                          |                                                       |  |  |  |  |

|                                                |                                                                                          | Denta Signia Order   •                                |  |  |  |  |

|                                                |                                                                                          | Randomization PLL N: 100 +                            |  |  |  |  |

|                                                |                                                                                          | Unrandomized                                          |  |  |  |  |

|                                                |                                                                                          | Update Simulation                                     |  |  |  |  |

|                                                |                                                                                          |                                                       |  |  |  |  |

Figure 1. Enter Custom Phase-noise for Reference Clocks

WEBENCH Clock Architect lets you select a specific TI clocking device (or multiple devices using regular expressions) from a drop-down list. Figure 2 is a screenshot of the step during which you select the device of your choice, enter the input and output frequencies, and design a loop filter or simulate phase noise.

|           |                  |                   |                 |                   | Power      | LED                      | LED Architect | Power Architect | FPGA/µP | HotSwap | Simple Switche |

|-----------|------------------|-------------------|-----------------|-------------------|------------|--------------------------|---------------|-----------------|---------|---------|----------------|

| Basic     | Advanced         |                   | Generate Solut  | tions             |            |                          |               |                 |         |         |                |

|           |                  |                   |                 |                   | Part Fil   | ter                      |               |                 |         |         |                |

| LMK03     | 7                | Clear             | Filter 2 pa     | arts match this f | filter.    |                          |               |                 |         |         |                |

| LMK033    |                  | 13                |                 |                   |            |                          |               |                 |         |         |                |

| LMK033    |                  |                   | -               | C                 | lock Desig | n Entry                  | 1             |                 |         |         |                |

| Fixed Out | put Frequencies  | A                 | dd              | ~                 |            |                          |               |                 |         |         |                |

| Name      | Freq (MHz)       | Format            | Count           |                   | -          | Enter device filter here |               |                 |         |         |                |

| fixed0    | 125              | LVDS              | 1               | Remove            |            |                          |               |                 |         |         |                |

| fixed1    | 156.25           | LVPECL            | 1               | Remove            |            |                          |               |                 |         |         |                |

| fixed2    | 50               | LVCMOS            | 1               | Remove            |            |                          |               |                 |         |         |                |

|           |                  |                   |                 |                   |            |                          |               |                 |         |         |                |

|           |                  |                   |                 |                   | _          |                          |               |                 |         |         |                |

| Auton     | natically genera | te input frequen  | cies for each s | olution.          |            |                          |               |                 |         |         |                |

| Uncheck   | this box to ente | r desired input f | requencies      |                   |            |                          |               |                 |         |         |                |

|           |                  |                   |                 |                   |            |                          |               |                 |         |         |                |

Figure 2. Device Filter

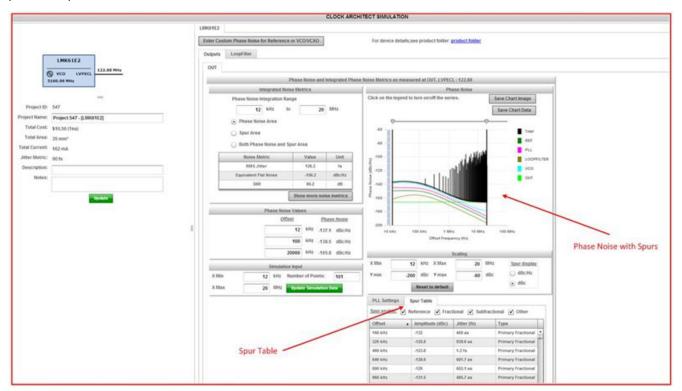

The phase-noise simulation results from the tool match actual silicon performance closely. However, until recently, the phase-noise simulation of fractional-N PLLs did not include spurs. The latest upgrade to WEBENCH Clock Architect includes modeling of the PLL phase detector and fractional, subfractional and other part-specific spurs for a majority of devices. We constantly strive to improve spur modeling in the tool and continue to add part-specific upgrades. Figure 3 shows an example of a fractional-N PLL generated output clock phase-noise plot with spurs.

Figure 3. Output Clock Phase-noise Plot with Spurs

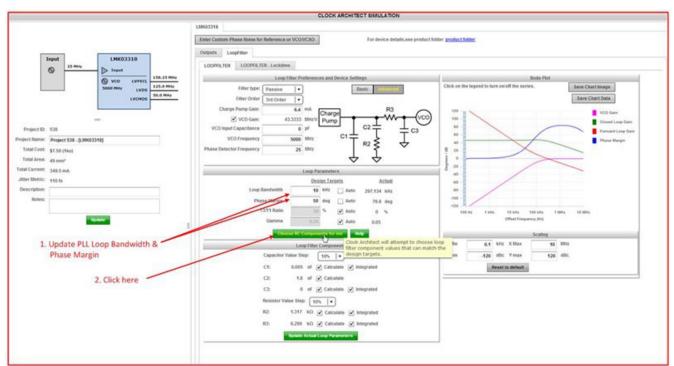

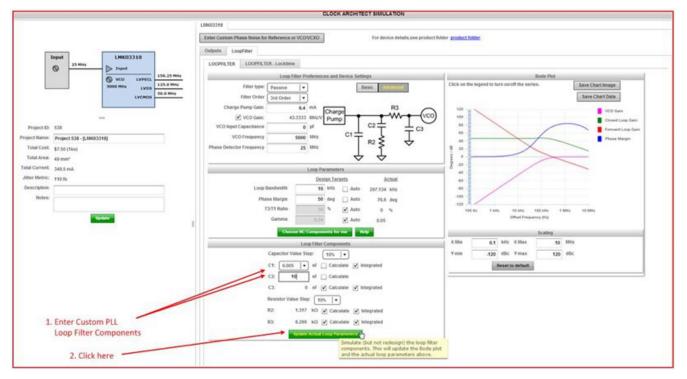

We have also made some upgrades to the PLL filter-design capabilities. With the latest release, advanced users can customize loop-filter parameters such as PLL bandwidth, phase margin and gamma, shown in the screenshot of Figure 4. You can enter custom loop-filter component values or select from a list of integrated values (when available for the device), and then check loop stability by monitoring the Bode plot (See Figure 5). With the inclusion of PLL lock-time modeling capability, you can verify the impact of your loop-filter design strategies to the PLL lock time (and phase noise) and consider necessary trade-offs (Figure 6).

3

#### Figure 4. Custom Loop Parameter Selection

### Figure 5. Custom Loop Filter Component Selection and Simulation

|                                    | CLOCK ARCHITECT SIMULATION                                                          |                                |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|

|                                    | LI02571                                                                             |                                |  |  |  |  |

|                                    | Enter Custom Phase Noise for Reference of VCOVCKO For device details, see product 9 | ilder product folder           |  |  |  |  |

|                                    | Outputs LeopFilter                                                                  |                                |  |  |  |  |

| Input LH0(2571                     | LOOPFILTER LOOPFILTER-Locktime                                                      |                                |  |  |  |  |

| O 15 Mills D Input                 |                                                                                     |                                |  |  |  |  |

| VCD Sinewaye 125.0 Mey             | Analog Locktime                                                                     | Transient Response             |  |  |  |  |

| 5000 MHz                           | Shart Frequency State                                                               | Envelope +                     |  |  |  |  |

| -                                  |                                                                                     | S040 - Crivetope -             |  |  |  |  |

| Project ID: 540                    | Final Frequency 5010 1012                                                           | 5030                           |  |  |  |  |

| ject Name: Project 540 - [LBD2571] | Settle Tolerance 1000 Hz                                                            |                                |  |  |  |  |

| Total Cost: \$4.50 (1ks)           | 1. Click here                                                                       | J 8000 -                       |  |  |  |  |

| Total Area: 36 mm*                 | Trequency Response Results.                                                         | 8010                           |  |  |  |  |

| M Current: 41 mA                   | PLLLock Tane 73.009 gs                                                              | 1 /                            |  |  |  |  |

| ther tiletric: 254 fs              | Total Lock Time 73,009 an 2. Enter Lock Time simulation                             | * 5000 · · ·                   |  |  |  |  |

| iscription:                        | Peak Time 14.014 yn parameters here                                                 | 4390 -                         |  |  |  |  |

| Notes:                             | Peak frequency 5011.579 MHz                                                         |                                |  |  |  |  |

| Rystatio                           |                                                                                     | 4300                           |  |  |  |  |

| al second                          | VCO Calibration                                                                     | 4579                           |  |  |  |  |

|                                    | VCO Calibration Time: 0 µs                                                          | 8 20 40 60 60 100<br>Time (pr) |  |  |  |  |

|                                    |                                                                                     | Scaling                        |  |  |  |  |

|                                    |                                                                                     | X min: 0 X max: 101            |  |  |  |  |

|                                    |                                                                                     |                                |  |  |  |  |

Figure 6. Lock Time Simulation and Estimation

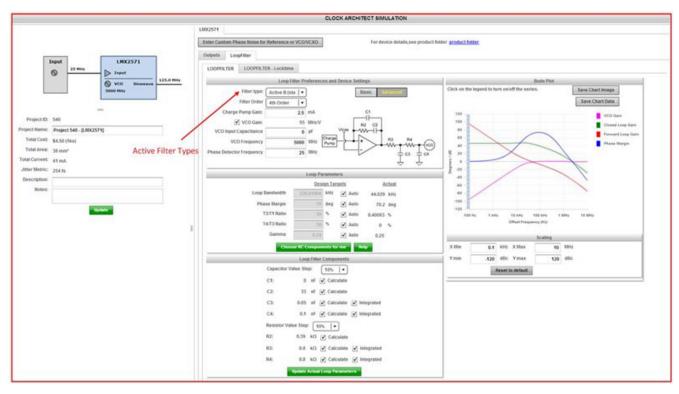

Until recently, WEBENCH Clock Architect supported passive loop-filter design only. Now, with the latest upgrades, the tool supports active loop-filter designs (under Advanced settings). Passive-loop filters are typically preferable to active-loop filters given their low cost, simplicity and in-band phase noise. But in certain cases – where the VCO requires a higher tuning voltage than the PLL charge pump can provide, or when the input impedance of the VCXO is inadequate – active filters are necessary. See the drop-down menu in Figure 7.

Figure 7. Active Loop Filter Selection and Simulation

The last major upgrade to WEBENCH Clock Architect is the ability to share designs with other users. You can generate a PDF report containing all of your design details with a single click of the Share Project button shown in Figure 8.

5

|                                                                                                                                                           | Back New Sim Print Share Project Share Project 1. Click here to share desi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input LMK03318                                                                                                                                            | LARK03318  Enter Custom Phase Noise for Reference or VCOVCXO Outputs LoopFilter  2. Enter details here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30.72 HHz<br>VCO<br>4915.2 HHz<br>Project ID: 548                                                                                                         | CLKOUTO Share with Individuals Share with Public Share with Individuals Share with Public Share this project with: Enter the email address of the recipient. Separate multiple addresses with commas. Add your notes for this project: Save Chart Image Save Chart Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Project Name: Project 548 - [LMK03318] Total Cost: \$7.50 (1ku) Total Area: 49 mm* Total Current: 282 mA Jitter Metric: 110 fs Description: Notes: Notes: | Shere this project       Clear       Cancel         How Share A Project works:       Fish         How Share A Project works:       Clear         How Share a project with anyone, even if they are not a current user of VEER/CK. Each person will reach invitation.       If the person you invite is new to The web site, we will pre-create a Sign. On the project is copied into their workspace. If they already have WEER/CH personal disk space, they will, receive a different link taking them directly to their new project. The sender will also receive an email confirmation for each invitation.       If the person you invite is new to The web site, we will pre-create a Sign. On the project is copied into their workspace. If they already have WEER/CH personal disk space, they will, receive a different link taking them directly to their mere project.       Too Bare         Kiten       Sper diabetee that conce copied, a project remains independent. All intere changes are reflected only in the individual user's workspace. Changes by any one person do not affect the project of another. You can, of course, share a project again after changes are made.       Sper diabetee         X Mare       20 Mit?       Declar Semiclobal total       extended only in the individual user's workspace.         Y Mare       20 Mit?       Declar Semiclobal total       extended only in the individual user's workspace.         Y Mare       20 Mit?       Declar Semiclobal total       extended only in the individual user's workspace.         Y Mare       20 Mit?       Declar Semiclobal total       extended only in the indindividual                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                           | Filter type:     Designed Filter     Image: Construction of the constru |

Figure 8. Share Designs

TI has a healthy portfolio of flexible and high-performance clock generators, clock jitter cleaners, radio frequency (RF) PLLs/synthesizers, clock buffers and oscillators to meet the stringent needs of your applications.

My favorite clock generator and programmable oscillator are the LMK03328 and LMK61E2, respectively. These devices have ultra-low RMS jitter performance (100fs typical), flexibility (integrated EEPROM and ROM) and are feature-rich (support frequency-margining). You can use WEBENCH Clock Architect to simulate the phase noise for your next design using these devices and many more at TI.com.

#### Additional Resources

- View WEBENCH Clock Architect training videos:

- WEBENCH Clock Architect Updates

- WEBENCH Clock Architect Introduction

- WEBENCH Clock Architect Simulation & Optimization

- Find out more about TI's clock and timing portfolio.

- · Read other blog posts about clocks and timing.

- Additional PLL simulator software http://www.ti.com/tool/pllatnumsim-sw

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated