# POR Generation in TPS65903x, TPS65917-Q1, TPS65919-Q1, and TPS65916 Devices

Karl Wallinger

Integrated Power Management

1

### ABSTRACT

Three different methods are available to make sure the TPS659038-Q1, TPS659039-Q1, TPS659037, TPS65917-Q1, TPS65919-Q1, and TPS65916 devices generate a power-on reset (POR) at each power cycle. These methods are limiting the falling VCC slew rate, limiting the rising VCC slew rate, and discharging LDOVRTC when power is off. This application note describes the POR generation behavior and a detailed description of each of these three methods.

#### Contents

| 1 | Introd | Juction                 | 2 |

|---|--------|-------------------------|---|

| 2 | POR    | Generation Details      | 2 |

|   | 2.1    | VCC1 Falling Slew Rate  | 2 |

|   |        | VCC1 Rising Slew Rate   |   |

|   |        | Discharging LDOVRTC_OUT |   |

|   |        |                         |   |

|   |        | List of Figures         |   |

#### List of Figures

| 1 | VCC Falling Profile                | 2 |

|---|------------------------------------|---|

| 2 | VCC Rising Profile                 | 3 |

| 3 | LDOVRTC Discharge With No Resistor | 3 |

| 4 | LDOVRTC Discharge With Resistor    | 4 |

| 4 | LOOVING Discharge with Resistor    |   |

# Trademarks

All trademarks are the property of their respective owners.

**NOTE:** This document only applies to silicon versions 1.3 or earlier for the TPS65903x devices. Newer versions of silicon do not have the VCC slew rate or LDOVRTC discharge requirements to generate a POR. This document applies to all silicon versions of the TPS65917-Q1, TPS65919-Q1, and TPS65916 devices.

(1)

### 1 Introduction

The TPS659038-Q1, TPS659039-Q1, TPS659037, TPS65917-Q1, TPS65919-Q1, and TPS65916 devices generate a power-on reset (POR) when the VCC1 supply voltage is less than the POR threshold defined in the device data sheet. These devices use VCC1 sampling to generate a POR event, which means a fast-decreasing VCC1 voltage can have the VCC1 supply powered off without generating a POR event. If the VCC1 supply is powered off without a POR event, the device may not power up correctly at the next power-on condition, therefore generating a POR event at every power cycle is important. This application note describes different application conditions which will make sure a POR event is generated.

## 2 POR Generation Details

To generate a POR event, the device uses VCC1 sampling to detect if the VCC1 supply voltage is less than the POR threshold. The device measures the VCC1 value every 1 ms with 10% variation, so the time between samples is from 0.9 ms to 1.1 ms. If any one of these samples detects that the VCC1 supply voltage is less than the POR threshold, a POR event is generated and the device is reset.

If a POR event is not generated from the VCC1 samples, a POR event can still be generated by discharging the voltage on the LDOVRTC\_OUT pin because the LDOVRTC regulator is the supply to the POR generation circuit. When the voltage on the LDOVRTC\_OUT pin is fully discharged, a POR event is generated the next time the VCC1 voltage is supplied to the PMIC.

Three conditions make sure a POR event is generated in the device. These conditions are as follows:

- The VCC1 supply has a falling slew rate less than 90 mV/ms between 1.9 V and 1.8 V.

- The VCC1 supply has a rising slew rate less than 90 mV/ms between 1.8 V and 1.9 V.

- The LDOVRTC\_OUT pin voltage is discharged to less than 100 mV, with an off time of at least 300 ms.

The following sections describe each of these conditions in more detail.

#### 2.1 VCC1 Falling Slew Rate

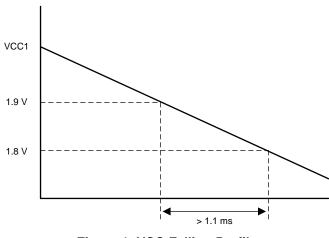

The POR comparator can accurately detect a POR event with a minimum VCC1 voltage of 1.8 V. Because the minimum POR threshold value in the device data sheet is 1.9 V, this means there is a 100mV voltage range in which the device can always detect a POR event. As long as one POR sample occurs within this voltage range, a POR event is generated. Because the maximum time between two samples is 1.1 ms, the maximum slew rate to generate a POR event is calculated in Equation 1. Therefore, if the falling slew rate is less than 90 mV/ms, a POR event is generated when the VCC1 pin is discharged below the POR threshold, as shown in Figure 1.

Figure 1. VCC Falling Profile

2

#### www.ti.com

#### 2.2 VCC1 Rising Slew Rate

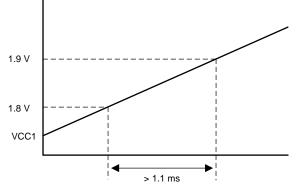

If a POR event is not generated when the VCC1 voltage decreases below the POR threshold, then the POR circuit is not reset. In this case, the comparator used to detect a POR event on the falling edge of the VCC1 voltage is still active, even when the VCC1 voltage is rising at the next power-up event. When the VCC1 voltage is between 1.8 V and 1.9 V and the POR comparator samples the VCC1 voltage, the POR comparator detects that the VCC1 voltage is less than the POR threshold and generates a POR event. These samples will also be at most 1.1 ms apart, so a rising VCC1 slew rate less than 90 mV/ms will also generate a POR event as shown in Figure 2.

Figure 2. VCC Rising Profile

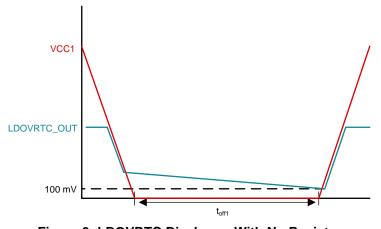

#### 2.3 Discharging LDOVRTC OUT

The LDOVRTC regulator is the power supply for the internal logic of the device, including the POR logic. Even if the POR comparator does not detect that the VCC1 voltage is less than the POR threshold, resetting the internal POR logic also generates a POR event. The POR event is generated by discharging the LDOVRTC voltage so that the device resets its internal active-low POR signal. The LDOVRTC\_OUT pin requires a 2.2-uF capacitor to ground. In addition, a 3.9-k $\Omega$  resistor can be connected from the LDOVRTC\_OUT pin to ground as described in the device data sheet. When no resistor is connected and the VCC1 voltage is discharged, the LDOVRTC regulator is turned off and the voltage on the LDOVRTC OUT pin discharges very slowly with an off time, t<sub>off1</sub>, greater than 1 s. In this case, the LDOVRTC OUT pin should be discharged to less than 100 mV to generate POR event as shown in Figure 3.

Figure 3. LDOVRTC Discharge With No Resistor

3

POR Generation Details

4

www.ti.com

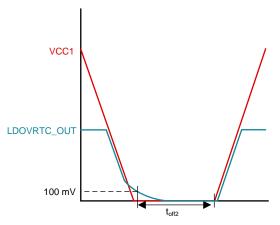

When a resistor is connected from the LDOVRTC\_OUT pin to ground, then the LDOVRTC\_OUT pin should be discharged to less than 100 mV for at least 300 ms to generate a POR event with an off time,  $t_{off2}$ , greater than 300 ms as shown in Figure 4. After the VCC1 voltage is discharged and the LDOVRTC\_OUT pin voltage decreases to less than 500 mV, the internal transistors are all in the high-impedance state, and residual voltage on the internal logic nodes is possible. Having the  $t_{off2}$  time greater than 300 ms allows the internal nodes to discharge enough to generate a POR event.

Figure 4. LDOVRTC Discharge With Resistor

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated