OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

$\mathsf{OMAP}^\mathsf{TM}$

### Public version

OMAP44xx Multimedia Device OMAP4430 Silicon Revision 2.x OMAP4460 Silicon Revision 1.x OMAP4470 Silicon Revision 1.0

Texas Instruments OMAP™ Family of Products

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Version H

# Technical Reference Manual

Literature Number: SWPU245H October 2010–Revised October 2012

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### **WARNING: EXPORT NOTICE**

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorization from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

-US ECCN: 3E991 -EU ECCN: EAR99

And may require export or re-export license for shipping it in compliance with the applicable regulations of certain countries.

### OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 . Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

|     | _                 | _        |  |

|-----|-------------------|----------|--|

| Tab | ام م <del>د</del> | Cantanta |  |

| 120 | () ()             | Contents |  |

|   |                | Table of Contents                              | _    |

|---|----------------|------------------------------------------------|------|

|   |                | ures                                           |      |

|   |                | bles                                           |      |

|   | List of AB     | REVIATIONs                                     | 6    |

| R | evision Hi     | story                                          | .7   |

| 1 | Introdu        | ction                                          | 8    |

| • |                | ature List                                     |      |

|   |                | dio mixing in OMAP4                            |      |

|   |                | dio mixing of multichannel audio               |      |

| 2 |                | vel view of the ABE-HAL services               |      |

| _ | 2.1.1          | AESS processing                                |      |

|   | 2.1.2          |                                                |      |

|   |                | AESS memory access                             |      |

| 3 |                | services                                       |      |

| ၁ |                | ta Types used for APIs                         |      |

|   |                | rdware control API list                        |      |

|   |                | abe reset hal                                  |      |

|   | 3.2.1<br>3.2.2 | abe_reset_narabe_load_fw                       |      |

|   | 3.2.2          | abe_reload_fw                                  |      |

|   | 3.2.3<br>3.2.4 | abe_reload_rwabe_write_event_generator         |      |

|   | 3.2.4<br>3.2.5 | abe_write_event_generatorabe_read_use_case_opp |      |

|   | 3.2.6          | abe_reau_use_case_oppabe_set_opp_ processing   |      |

|   | 3.2.7          | abe_set_opp_processingabe_connect_serial_port  |      |

|   | 3.2.8          | abe_connect_tdm_port                           |      |

|   | 3.2.9          | abe_init_ping_pong_buffer                      |      |

|   | 3.2.10         |                                                |      |

|   | 3.2.11         |                                                |      |

|   |                | abe_connect_cbpr_dmareq_port                   |      |

|   |                | abe_enable_data_transfer                       |      |

|   |                | abe_disable_data_transfer                      |      |

|   |                | abe_reset_port                                 |      |

|   | 3.2.16         | abe_set_ping_pong_buffer                       | . 25 |

|   | 3.2.17         | abe_read_next_ping_pong_buffer                 | . 25 |

|   | 3.2.18         | abe_read_remaining_data                        | . 26 |

|   | 3.2.19         | abe_read_offset_from_ping_buffer               | .26  |

|   |                | abe_read_port_address                          |      |

|   | 3.2.21         | abe_write_select_pdm_output                    | . 26 |

|   | _              | gnal processing API list                       |      |

|   | 3.3.1          | abe_write_gain, abe_write_mixer                |      |

|   | 3.3.2          | abe_set_router_configuration                   |      |

|   | 3.3.3          | abe_write_equalizer                            |      |

|   | 3.3.4          | abe_write_asrc                                 |      |

|   | 3.3.5          | abe_use_compensated_gain                       |      |

|   | 3.3.6          | abe_mute_gain                                  |      |

|   | 3.3.7<br>3.3.8 | abe_unmute_gain                                |      |

|   | 3.3.0<br>3.3.9 | abe_read_gainabe_mono_mixer                    |      |

|   |                | erface and accessory control API               | 30   |

|   | 3.4.1          | abe_irq_processing                             |      |

|   | 3.4.1<br>3.4.2 | abe_liq_processingabe_clear_irq                |      |

|   | 3.4.2<br>3.4.3 | abe_clear_irqabe_connect_debug_trace           |      |

|   |                | ta paths graphical view                        |      |

|   | 3.5.1          | Data paths and features of the HAL releases 09 |      |

|   |                | SS registers descriptions                      |      |

|   | J.J / L        |                                                | J_   |

# OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

www.ti.com

|   | 3.7  | Ports characteristics                                    | 33  |

|---|------|----------------------------------------------------------|-----|

|   | 3.8  | ABE Gains and MCPDM saturation                           | 35  |

|   | 3.9  | Clocks and peripheral synchronization                    | 35  |

| 4 | Pro  | gramming examples                                        | 36  |

|   | 4.1  | AESS reset                                               | 36  |

|   | 4.2  | Multimedia player in low-power mode                      | 36  |

|   | 4.3  | System tones player                                      |     |

|   | 4.4  | Voice calls                                              | 38  |

|   | 4.5  | Switching DMIC sources while rotating the screen         | 38  |

|   | 4.6  | Equalizer                                                | 39  |

|   | 4.7  | Equalizer for microphones and decimation to 48kHz        |     |

|   | 4.8  | Equalizer for side-tone                                  |     |

|   | 4.9  | FM radio recording on-the-fly                            | 41  |

|   | 4.10 | AE processing - Drift management                         | 42  |

|   | 4.11 | Serial ports FIFO thresholds                             |     |

|   | 4.12 | Audio Clicks                                             | 42  |

|   | 4.13 | Use-Case transitions                                     | 44  |

|   | 4.13 | 3.1 Opening and closing ports – start/stop code sequence | .44 |

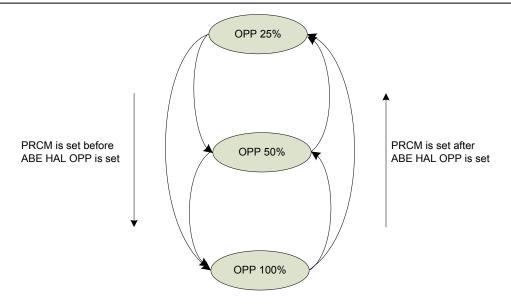

|   | 4.13 | 3.2 OPP transitions                                      | 44  |

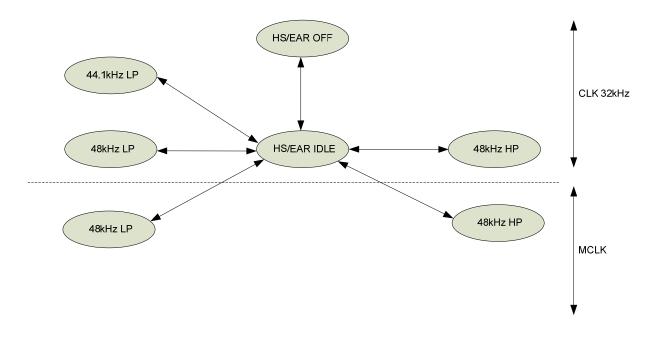

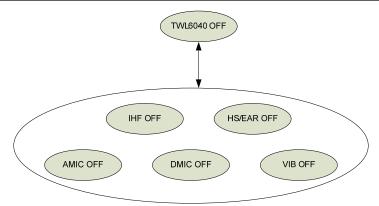

|   | 4.13 | 3.3 TWL6040 transitions                                  | 45  |

| 5 | Deb  | ugging ABE                                               | 51  |

| _ | 5.1  | FIFO locations                                           |     |

|   | 52   | Debug trace                                              | 52  |

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 . Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### **LIST OF FIGURES**

| Figure 1 – Real-time mixing and filtering in ABE                                    | 8  |

|-------------------------------------------------------------------------------------|----|

| Figure 2 – OMAP multimedia mixers                                                   | 10 |

| Figure 3 – Multichannel mixing and routing (HDMI)                                   | 11 |

| Figure 4 – ABE logical/physical port mapping                                        | 13 |

| Figure 5 – ABE-MMAV10GS70 Block Diagram                                             | 14 |

| Figure 6 – Data exchanged between peripherals and DMEM through ATC ports            | 15 |

| Figure 7 – Extracts from the Attila functional specification for sDMA request lines | 16 |

| Figure 8 – Data exchanged between a DMA and DMEM through ATC ports                  | 17 |

| Figure 9 – Data exchanged between a DMA and DMEM using the ping-pong protocol       | 18 |

| Figure 10 – Ping-Pong protocol                                                      | 19 |

| Figure 12 – Processing flow with OPP values of the release 09                       | 31 |

| Figure 13 – ABE HAL gain settings, versus the low-power configuration of TWL6040    | 35 |

| Figure 14 – ABE HAL for ABE-AESS reset                                              | 36 |

| Figure 15 – ABE HAL for enabling low-power audio player                             | 37 |

| Figure 16 – ABE HAL for low-latency tones generation                                | 38 |

| Figure 17 – ABE HAL for Voice call settings                                         | 38 |

| Figure 18 – ABE HAL codes for uplink router configuration                           | 39 |

| Figure 19 – Matlab source code for equalizer coefficients' computation              | 40 |

| Figure 20 – ABE HAL for loading equalizer's coefficients                            | 40 |

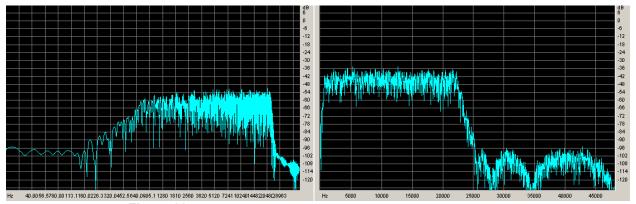

| Figure 21 – White noise high-pass filtered (log scale, linear scale)                | 40 |

| Figure 22 – Matlab source code for microphone equalizer computation                 | 41 |

| Figure 23 – ABE HAL for loading microphone equalizer's coefficients                 | 41 |

| Figure 24 – OPP transitions                                                         | 45 |

| Figure 25 – Headset / Earphone transitions                                          | 46 |

| Figure 26 – Hands-free transitions                                                  | 47 |

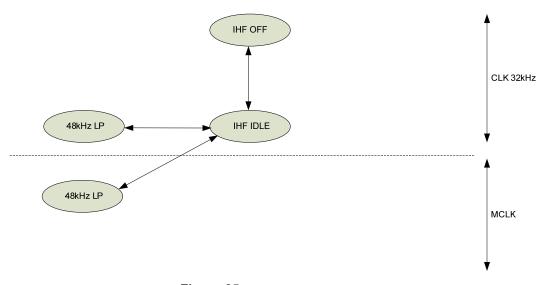

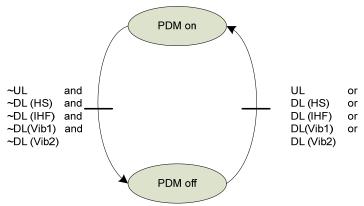

| Figure 27 – PDM states transitions                                                  |    |

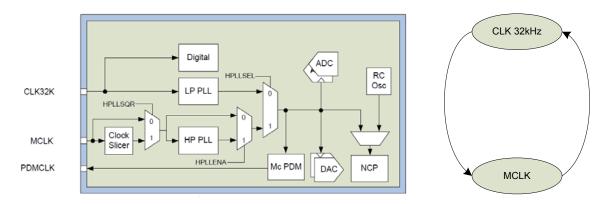

| Figure 28 – TWL6040 clocks tree and transitions                                     |    |

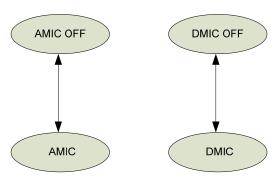

| Figure 29 – Microphones transitions                                                 | 49 |

| Figure 30 – TWI 6040 Power-Down conditions                                          | 50 |

LIST OF TABLES

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

| Table 1 : ABE-HAL Feature list                           | 9  |

|----------------------------------------------------------|----|

| Table 2 : ABE Physical ports list                        | 12 |

| Table 3 : Logical ports and default protocols            | 13 |

| Table 4 : ATC Descriptor configuration (From [1])        | 16 |

| Table 5 : List of the data types                         | 20 |

| Table 6 : Mixers' port indexes                           | 27 |

| Table 7 : Gains' port indexes                            | 28 |

| Table 8 : AESS registers                                 | 32 |

| Table 9 : Port and protocol                              | 33 |

| Table 10 : Use-cases and OPP                             | 34 |

| Table 11 : Clocks configurations with DMIC               | 35 |

| Table 12 : McBSP thresholds                              | 42 |

| Table 13: Maximum gains to set in downlink paths DL1/DL2 | 50 |

| Table 14 : ATC DMA requests                              |    |

| Table 15 · ATC FIFO DMFM offset                          | 52 |

### LIST OF ABREVIATIONS

**AE**: Audio Engine, part of the AESS. Makes the signal processing operations

AESS: Audio Engine Sub-System, part of ABE. Includes AE, ATC, timers and clock control ATC: Audio Traffic Controller. Makes the data move between the DMEM and peripherals

**DMEM**: Data memory, part of the AE. Used to control the processing and do data moves with ATC.

SMEM, PMEM, CMEM: AE tightly coupled memories (samples, program, coefficients)

**HAL**: Hardware Abstraction software Layer

**OPP**: clock percentage operating point (100%, 50%, 25%)

FW: Audio Engine Firmware

Physical Ports: ports managed by the ATC (DMA, DMIC, McPDM, McBSP, etc...)

**AE Ports**: I/O connections of the FW to the physical ports. **Link**: data connection between a Physical port and an AE Port. AE Feature: signal processing operation inserted in the audio stream

ASRC. EQ: asynchronous sample-rate converter, equalizer

MMI: Man Machine Interface

MP3 use-case: Audio player can be not only MP3 but any MPEG player, OGG, WMA, etc... Sink, Source: from the host processor point of view some AE port are sink or source of samples OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 . Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

# **Revision History**

| Version | Literature<br>Number | Date             | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.94    | N/A                  | June<br>2010     | Added a chapter for AMIC/DMIC equalizer computation  Added a separate capability of tuning AMIC and DMIC with abe_write_equ()  Added abe_use_compensated_gain(), abe_(un)mute_gain(),  Removed abe_set_dmic_filter(), abe_select_main_port()  Changed the IIR25 coefficients description  Updated the write_equalizer API, and add a recommendation to lower the gain. Updated the description of time synchronizations.                                               |

| 0.95    | N/A                  | October<br>2010  | Corrected description of the APIs: abe_init_ping-pong_buffer, abe_connect_dmareq_ping_pong_port, abe_connect_irq_ping_pong_port, abe_set_ping_pong_buffer, abe_read_next_ping_pong_buffer, abe_read_remaining_data. Corrected Ping-Pong FW function pseudo description. Corrected Programming example for Ping Pong with MCU IRQ.                                                                                                                                      |

| A       | SWPU245              | December<br>2010 | Added description of new API abe_read_offset_from_ping_buffer.  Added 44.1KHz support at MM_EXT_OUT port at OPP25. Added description of abe_read_gain API. Updated description of APIs abe_write_gain, abe_mute_gain, abe_unmute_gain. Added data paths graphical view related to HAL 09 releases.  Added a chapter on AESS registers. Port naming clarification.                                                                                                      |

| В       | SWPU245              | January<br>2011  | Added new APIs abe_reload_fw, added a chapter on start/stop programming sequences and audio clicks, removed abe_read_hardware_description. Removed vx_dl_split data type.                                                                                                                                                                                                                                                                                              |

| С       | SWPU245              | March<br>2011    | No changes between OMAP4430 Silicon Rev 2.x version (SWPU245B) and OMAP4430 Silicon Rev 2.x / OMAP4460 Silicon Rev 1.0 version (SWPU245C). This document covers both OMAP4430 and OMAP4460 Devices.                                                                                                                                                                                                                                                                    |

| D       | SWPU245              | May<br>2011      | Added the available gain list to API abe_write_gain description. Added distinct BT_UL gain support. Corrected figure ABE firmware data paths and features of HAL versions 09 such that 7 channels are supported at MM_UL port.  Added new API abe mono mixer description.                                                                                                                                                                                              |

| E       | SWPU245              | August<br>2011   | No changes between version D and version E. Internal alignment only. Replaced 4460 Silicon Rev 1.0 by 4460 Silicon Rev 1.x                                                                                                                                                                                                                                                                                                                                             |

| F       | SWPU245              | November<br>2011 | No changes between OMAP4430 Silicon Rev 2.x / OMAP4460 Silicon Rev 1.x version (SWPU245E) and OMAP4430 Silicon Rev2.x / OMAP4460 Silicon Rev 1.x / OMAP4470 Silicon Rev 1.0 version (SWPU245F), with the exception of the clarification of the impossibility to access in 8/16bits words formats, the auto-gating description, Slimbus and Vibra/TDM ports removed, AESS register update for auto-gating. This document covers OMAP4430 OMAP4460 and OMAP4470 Devices. |

| G       | SWPU245              | June<br>2012     | Added new API abe_connect_tdm_port and abe_write_select_pdm_output                                                                                                                                                                                                                                                                                                                                                                                                     |

| Н       | SWPU245              | October<br>2012  | Added new APIs: abe_disable_data_transfer and : abe_enable_data_transfer in order to stop/start I/O task processing and abe_set_mux_demux_tdm_parameters  Api. Remove API abe_write_select_pdm_output and API abe_set_tdm_parameters                                                                                                                                                                                                                                   |

### 1 Introduction

The purpose of this document is to detail the implementation of audio use-cases using the Audio Engine (AE) of the Audio Back-End (ABE) and its Hardware Abstraction Layer (HAL).

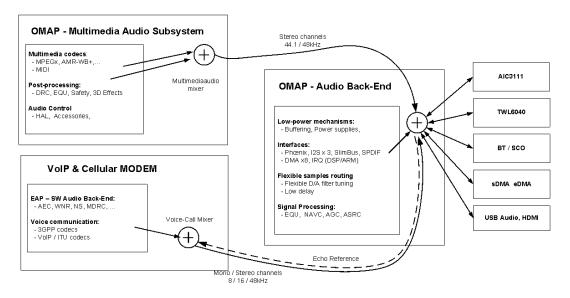

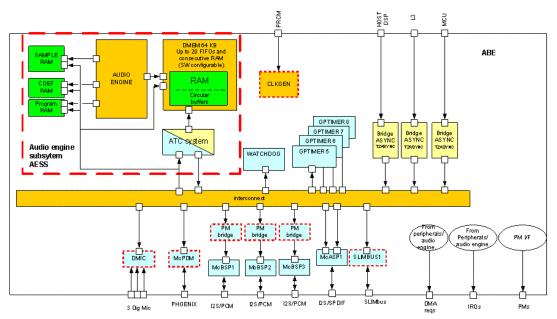

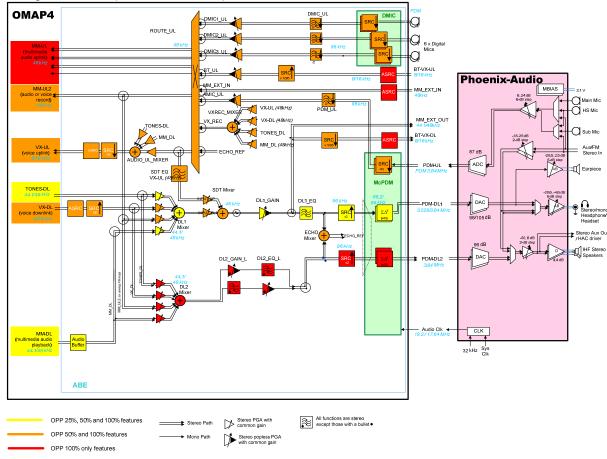

The figure below depicts an example of the main audio processing blocks. The ARM host processor is in charge of the OMAP4 ABE HAL and the multimedia players. An external Modem device is in charge of the cellular voice processing. The Audio Engine of the ABE holds the real-time mixer feature.

Figure 1 - Real-time mixing and filtering in ABE

The ABE is in charge of the hard-real time mixing and basic filtering of the audio streams originated from the host processors or from hardware peripherals (MIDI players, FM radio, external Modem devices, A/D converters). For example generating tones on top of FM radio or managing the sound equalization is possible without going through the host processors.

The functional partitioning between HAL and Audio upper layers is:

- The HAL is in charge of the abstraction of the Audio Engine (AE) memory mapping, the AESS (Audio Engine Sub-System) control registers.

The routing of the samples to TWL6040 is managed in the AE. There is no routing capability in TWL6040: the PDM-DL interface slots 0/1 are dedicated to earphone and headset drivers, slots 2/3 are dedicated to hands free driver, slot 5 and the control line are dedicated to Vibra/Haptics.

When the Audio Engine generates an interrupt to the host, the HAL will manage the interpretation.

Audio upper layers make the interface of the ABE hardware device drivers (McBSP, McASP, McPDM, DMIC) to other device drivers (I2C, UART) and to the operating system. OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 . Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### 1.1 Feature List

This paragraph lists the ABE-HAL features.

| Features     | Comments                                                                                                                                                            |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ports        | ABE-HAL allows connections to sDMA to hardware FIFOs of :                                                                                                           |  |  |  |

|              | MM_UL_PORT for up to 7 data paths (3 stereo + 1 mono channels)                                                                                                      |  |  |  |

|              | MM_UL2_PORT dedicated to audio recording                                                                                                                            |  |  |  |

|              | VX_UL_PORT holding the voice uplink path                                                                                                                            |  |  |  |

|              | TONES_DL_PORT used for the low-latency notification tones VX_DL_PORT holding the voice-downlink path                                                                |  |  |  |

|              | MM DL PORT dedicated to multimedia and low-power audio use-cases with an                                                                                            |  |  |  |

|              | optional ping-pong buffer.                                                                                                                                          |  |  |  |

|              | The ports are exchanging 8 to 32bits data MSB aligned on a 32bits container. MM_DL allows receiving two concatenated 16bits Left/Right samples per 32bits accesses. |  |  |  |

|              | The sampling rate is 48kHz. Voice paths use 8 or 16kHz. MM_DL use 44.1kHz or 48kHz.                                                                                 |  |  |  |

|              | The sampling rate of MM_DL and voice ports can be adjusted with 1ppm accuracy using the asynchronous sample-rate converters.                                        |  |  |  |

| Gain control | The mixer's gain balancing is tuned with 0.1dB precision with smoothed transitions                                                                                  |  |  |  |

| Routing      | Allows routing capabilities of microphones and the "echo reference" path                                                                                            |  |  |  |

| OPP          | The allowed OPP and clock values are tunable                                                                                                                        |  |  |  |

| Equalizer    | The two downlink audio paths are equalized and can be tuned dynamically.                                                                                            |  |  |  |

|              | DMIC compensation of spectrum distortion                                                                                                                            |  |  |  |

Table 1 : ABE-HAL Feature list

### 1.2 Audio mixing in OMAP4

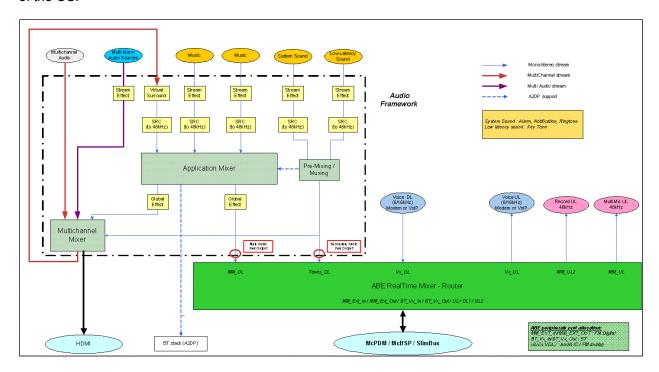

ABE implements the real-time mixer and routers of the OMAP multimedia software architecture. The picture below describes the typical connections found when ABE is used with the multimedia framework of the OS.

Figure 2 - OMAP multimedia mixers

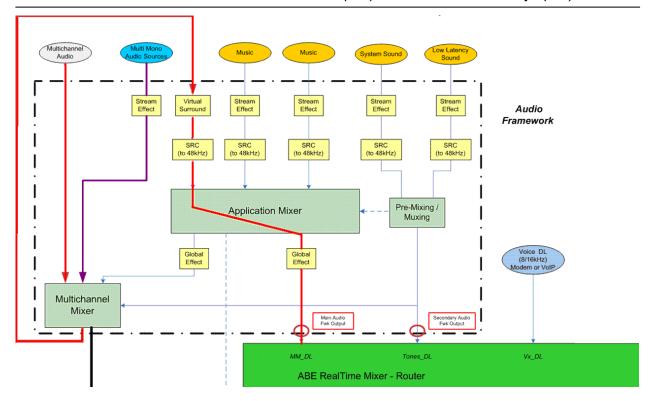

### 1.3 Audio mixing of multichannel audio

ABE is optimized for stereo audio streams. When multichannel needs to be played on the headset, the Host CPU is in charge of the virtual surround 5.1 to stereo translation. The resulted stereo stream can be processed and routed in ABE:

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Figure 3 – Multichannel mixing and routing (HDMI)

## 2 Top level view of the ABE-HAL services

This section gives the user's view of the HAL services, starting with an introduction to the data exchanged with the upper layers.

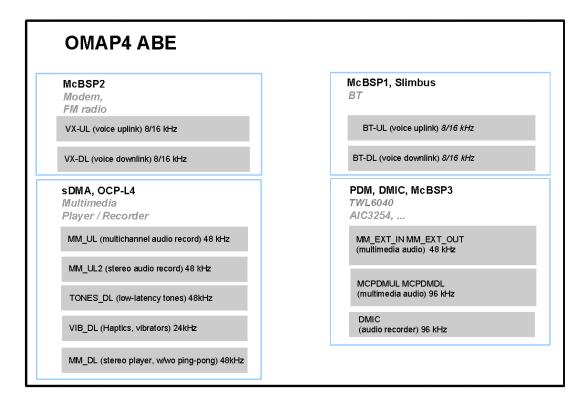

| Physical port | Samping      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | rate (kHz)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMIC          | 96           | Digital microphones Always used in the configuration of six samples sent to AESS. When DMIC is used in ultra-sonic mode the samples are not going through AESS, but directly go through the sDMA. The DMIC ABE IP can be configured with several clock speeds on the OMAP I/O pads, the high clock speed results in higher quality and higher power consumption. The DMIC IP distorts the spectrum shape differently depending on this clock speed. The HAL reconfigures the AESS correction filters depending on the selected clock speed. |

| MCPDMUL       | 96           | Analog microphones from TWL6040 sampled at 96kHz.  Always used in the configuration of two samples sent to AESS.  When MCPDMUL are used in ultra-sonic mode the samples are not going through AESS, but directly go through the sDMA                                                                                                                                                                                                                                                                                                        |

| MCPDMDL       | 88.2/96      | Downlink TWL6040 paths sampled at 96kHz. Always used in the configuration of six samples sent from AESS.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MCBSP1 TX/RX  | 8/16/48      | Used for Bluetooth voice and music                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MCBSP2 RX/TX  | 8/16/48      | Used for the external cellular Modem and FM radio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MCBSP3 RX/TX  | 8/16/44.1/48 | Replacement of the MCPDMUL and MCPDMDL interfaces in case of connections to audio ICs like AlC3254                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MCASP         | NA           | Only used for the SPDIF use-case. Cannot be used with AESS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CBPr0 CBPr6   | 4            | Circular buffer with release capability of the sDMA request.  Each CBPr is respectively connected to an sDMA request line 0  6. DMA requests are sent on 4kHz rate. The sDMA will be programmed to exchange from 4 bytes to 384 bytes on each ABE sDMA request.                                                                                                                                                                                                                                                                             |

| CBPr7         | 4/96         | Unused. sDMA line #7 is reserved for AESS purpose and debug. The host application should reserve a memory place for receiving 128 bytes of traced AESS internal data on a 4kHz rate. This data will be used for post-mortem analysis.                                                                                                                                                                                                                                                                                                       |

Table 2: ABE Physical ports list

Concerning the naming rule, "RX" means reception from ABE point of view: for example MM\_DL is receiving data from sDMA and McBSP1\_RX corresponds to the RX pins of the serial interface. "DL" means "downlink" as inherited from Modem point of view ("forward" direction down from the antenna to the mobile direction): for example BT\_DL port is intended to send voice from the network to the Bluetooth earpiece.

| Logical port | FS (kHz) | Description                                        |  |

|--------------|----------|----------------------------------------------------|--|

| MM_UL (TX)   | 48       | Multichannel (x7) audio record                     |  |

|              |          | Default configuration :                            |  |

|              |          | DMA connected to CBPr3, stereo MSB aligned         |  |

| MM_UL2 (TX)  | 48       | Stereo audio record                                |  |

|              |          | Default configuration :                            |  |

|              |          | DMA connected to CBPr4, stereo MSB aligned samples |  |

| VX_UL (TX)   | 8/16     | Modem voice path uplink                            |  |

|              |          | Default configuration :                            |  |

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0.

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

|                 | 1       | D144                                                                                                                                                                                    |  |

|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |         | DMA connected to CBPr2, stereo MSB aligned samples                                                                                                                                      |  |

| PDM (TX)        | 88.2/96 | Dedicated MCPDMDL IP (overlays the McBSP3_TX)                                                                                                                                           |  |

| MM_EXT_OUT (TX) | 44.1/48 | Multimedia output port                                                                                                                                                                  |  |

| BT_VX_DL (TX)   | 8/16    | Voice output port (Bluetooth)                                                                                                                                                           |  |

| MM_EXT_IN (TX)  | 48      | Multimedia input port                                                                                                                                                                   |  |

| TDM (TX)        | 48      | Dedicated to McBSP3_TX as replacement of McPDM_DL                                                                                                                                       |  |

| TDM (RX)        | 48      | Dedicated to McBSP3_RX as replacement of McPDM_UL                                                                                                                                       |  |

| PDM (RX)        | 96      | Dedicated MCPDMUL IP (overlays the McBSP3_RX)                                                                                                                                           |  |

| DMIC (RX)       | 96      | Dedicated DMIC IP                                                                                                                                                                       |  |

| MM_DL (RX)      | 44.1/48 | Multimedia stereo player port. Can be used either with sDMA through CBPr or using a large Ping-Pong buffer.  Default configuration:  DMA connected to CBPr0, stereo MSB aligned samples |  |

| VX_DL (RX)      | 8/16    | Modem voice path downlink Default configuration: DMA connected to CBPr1, stereo MSB aligned samples                                                                                     |  |

| TONES_DL (RX)   | 44.1/48 | Low latency notification tones and key beeps Default configuration: DMA connected to CBPr5, stereo MSB aligned samples                                                                  |  |

| MM_EXT_IN (RX)  | 48      | Multimedia input port                                                                                                                                                                   |  |

| BT_VX_UL (RX)   | 8/16    | Voice input port (Bluetooth)                                                                                                                                                            |  |

Table 3: Logical ports and default protocols

Figure 4 – ABE logical/physical port mapping

### 2.1.1 AESS processing

In audio player low-power mode, the audio engine can operate at 48 kHz or 44.1 KHz. When configured for 44.1 kHz the Audio Engine processes all inputs at 44.1 kHz. No resampling is performed. The

sampling frequency on the Audio Engine ports is 44.1 kHz, and data format can be 16/24/32 bits per word mono or stereo. In all other cases, the Audio Engine processing consists in resampling the input samples to 48 kHz stereo format, doing the mixing and filtering operation, and saving the samples to a sink port with a new sampling and data formats. The sampling frequencies on the Audio Engine ports are 8/16/48 kHz, and the data format can be 16/24/32 bits per words mono or stereo, except in audio player low-power mode, which can use also 44.1 kHz.

ABE consists in the AESS (Audio Engine SubSystem), timers and peripherals (audio serial ports). The HAL is in charge of programming the AESS.

Figure 5 - ABE-MMAV10GS70 Block Diagram

The AE executes a list of operations in an infinite loop. When the loop reaches the end of the list, the AE goes into Idle. The AESS generates a pulse (an "EVENT") on every 10.4167 µs (1/96kHz) period in order to awake the AE and let it run its processing list of subroutines. The HAL is in charge of the content of this list which will depend on the OPP. The HAL selects the hardware signal in charge of the EVENT generation.

The AE is reading its processing parameters (gain control, filter coefficients, etc...) from DMEM (data memory) or CMEM (coefficient memory) / SMEM (samples buffer memory).

The ATC receives the DMA requests from audio peripherals and exchanges data using the DMEM buffers. The AE and the ATC are synchronized by the HAL: the audio serial ports peripherals names and corresponding buffer addresses will be identical in ATC and AE.

Setting an audio channel will consist in connecting the AESS-ATC stream of data to one of the I/O ports of the AE network of processing features.

There is one processing network for each OPP. The higher the OPP the higher the number of processing tasks. Each network gives the use-case capabilities of the given OPP. All the features corresponding to a given OPP are active and launched with default coefficients parameters. The HAL can modify the parameters on-the-fly.

The AE interacts with the host processors through the DMEM and by sending interrupts.

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0.

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### 2.1.2 AE Port - Protocols

The AE exchanges the audio samples through the DMEM using 32-bit access. DMEM can be read and written to using either the slave port for DMA and Host access (32-bit access), or through the master port for hardware peripherals.

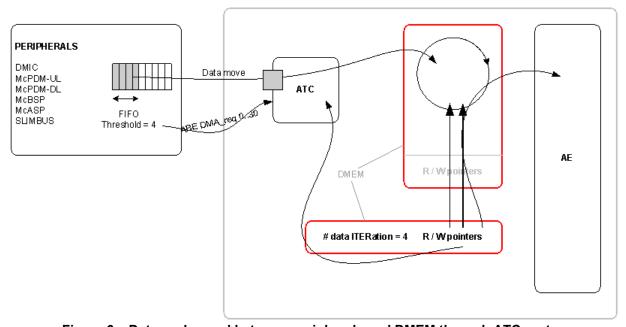

The picture below corresponds to the second case: once the FIFO threshold of the peripheral is reached an ABE\_DMA\_request is sent to the ATC (Audio Traffic Controller). The ATC decodes its corresponding buffer descriptor in DMEM (R/W pointers and iteration on data move) and executes the transfers. ATC updates the pointers. The AE uses pointers values in DMEM during data access. ATC iteration and peripheral threshold must be aligned.

The ATC is using the same clock of the Audio Engine (196.608 MHz at OPP100%). There is one ATC cycle for reading the descriptor, one cycle per sample exchange to DMEM (4 clock periods per bus-interconnect cycle) and one cycle more for the descriptor update. Due to those latencies and to the ratio between bus clock and processing clock, from the Host processor programmer's point of view, it is not recommended to make processing operation directly in DMEM, but rather read blocks of data to the host memory space and copy back to DMEM once the computations are finished.

Figure 6 – Data exchanged between peripherals and DMEM through ATC ports

The AE has always the priority on DMEM accesses and can slow down the ATC transfers. The AE is designed in order not to make long consecutive DMEM accesses. ATC accesses for peripherals are processed in queue, each peripheral has its own priority which corresponds to its ABE\_DMA\_req signal index to the AESS. Peripherals must not be programmed with long ITERation fields in the ATC programmation because the bus-interconnect communication is locked until the transfer is finished. The bus-interconnect slave port accesses do not contribute to ATC transfer delays.

| Bits | Size | Field Name | Function |

|------|------|------------|----------|

| 1    | I    |            |          |

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

|        | 7  | RW | RDPT    | Read pointer relative address (LSB)                                          |

|--------|----|----|---------|------------------------------------------------------------------------------|

|        | 1  |    |         | Reserved (must be zero)                                                      |

|        | 7  | RW | CBSIZE  | Circular buffer size                                                         |

|        | 1  | RW | IRQDEST | IRQ destination (0 DSP, 1 MCU)                                               |

| 32-bit | 1  | RW | CBERR   | Repport circular buffer errors                                               |

| LSB    | 5  |    |         | Reserved (must be zero)                                                      |

|        | 1  | RW | CBDIR   | Circular buffer direction                                                    |

|        | 1  | R  | CBEMPTY | Circular buffer empty                                                        |

|        | 7  | RW | WRPT    | Write pointer relative address                                               |

|        | 1  |    |         | Reserved - must be zero (MSB)                                                |

|        | 12 | RW | BADD    | Base address (LSB)                                                           |

| 32-bit | 7  | RW | ITER    | Iteration = number of samples<br>transferred on each AESS_DMAreq<br>received |

| MSB    | 6  | RW | SRCID   | Source ID peripheral                                                         |

|        | 6  | RW | DESTID  | Destination ID peripheral                                                    |

|        | 1  | RW | DESEN   | Descriptor activation (MSB)                                                  |

Table 4 : ATC Descriptor configuration (From [1])

Exchanging data from the Host to DMEM consists in making access to circular and ping-pong buffers.

### 2.1.2.1 Data move with ATC through CBPr AESS registers

The ATC manages the circular buffers which are seen from the host through registers (AESS CBPr registers). Eight registers have a DMA release capability: the DMA request line of the DMA is controlled by the AE.

| S_DMA_100 | ABE_DMAREQ 0 | Audio Back-End module – request FIFO 0 |  |

|-----------|--------------|----------------------------------------|--|

| S_DMA_101 | ABE_DMAREQ 1 | Audio Back-End module – request FIFO 1 |  |

| S_DMA_102 | ABE_DMAREQ 2 | Audio Back-End module – request FIFO 2 |  |

| S_DMA_103 | ABE_DMAREQ 3 | Audio Back-End module – request FIFO 3 |  |

| S_DMA_104 | ABE_DMAREQ 4 | Audio Back-End module – request FIFO 4 |  |

| S_DMA_105 | ABE_DMAREQ 5 | Audio Back-End module – request FIFO 5 |  |

| S_DMA_106 | ABE_DMAREQ 6 | Audio Back-End module – request FIFO 6 |  |

Figure 7 - Extracts from the Attila functional specification for sDMA request lines

The AESS DMA 7 is reserved in the AE to by-pass the MCBSP TX FIFOs and to dump debug traces to the host using the port "DEBUG PORT". So only the first 7 DMA channels are available to the Host.

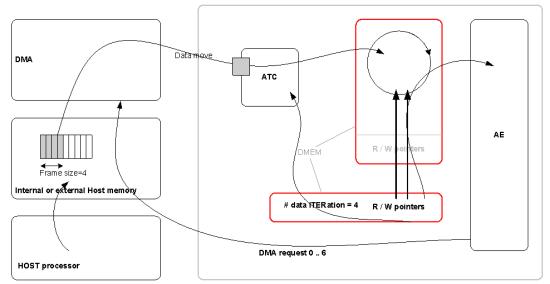

The HAL programs the ATC descriptor ITERation with always one for DMA transfers. The DMA is set to transfer the needed amount of data. The example below corresponds to 16 kHz speech samples exchanged from the Host, the frame size is 4 mono samples. The DMA points to one of the eight ATC registers (named "CIRCULAR BUFFER PERIPHERAL R 0 ... 6"). The HAL service delivers the ATC register address and the DMA frame length.

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0.

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Figure 8 - Data exchanged between a DMA and DMEM through ATC ports

Each time a DMA request is received for a synchronized channel, the DMA logical channel is activated and an amount of data is moved. The amount of data can be (vocabulary definition extracted from DMA4 specification):

An element

A complete element, for example, 16/32 bits are transferred in response to a DMA request.

An entire frame

A complete frame of several elements is transferred in response to a DMA request.

An entire block

A complete block of several frames is transferred in response to a DMA request.

An entire packet

A complete packet of several blocks is transferred in response to a DMA request.

For example the multichannel logical port "MM\_UL2" (stereo channel) will be set with 32-bit elements, frames of 4 elements and blocks of 12 frames. The "12" comes from the AE processing loop (this loop is 250  $\mu$ s long) respective to the audio sampling rate 48 kHz: 12 = 48 000 x 250 $\mu$ s. The HAL manages all those programmation details.

#### 2.1.2.2 Data move using DMEM accesses

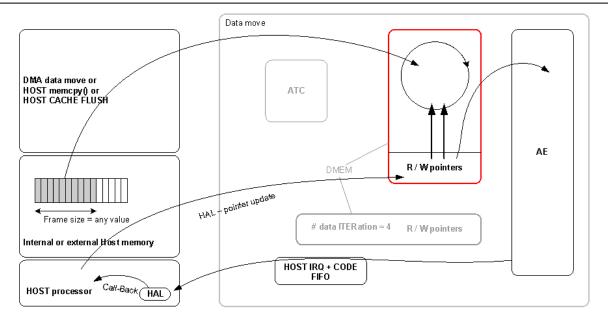

For ping-pong buffers the size is only limited by the DMEM free area.

The **ping-pong protocol** consists in loading the DMEM memory using the bus-interconnect slave port using the DMA data move or the host CPU copy with two buffers managed independently with only two pieces of information (base address and buffer size).

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Figure 9 - Data exchanged between a DMA and DMEM using the ping-pong protocol

The host processor receives an IRQ once the "ping" buffer is emptied, the "pong" buffer is always assumed to have been filled one step in advance. The HAL decodes the IRQ source by reading the FIFO of IRQ codes located in DMEM and making a call-back to the audio player framework.

This protocol can also be used with a DMA: the corresponding DMA request line will be activated on every half-buffer size being emptied and the DMA will generate the IRQ to the Host.

The size of each buffer is assumed to change going from the one to the other. The read pointer is initialized to the next base address when reaching the size of the current buffer. The FW pseudo code will be:

While the read pointer is smaller than the current SIZE of the buffer do Read data from post-incremented read pointer End while

When the read pointer becomes equal to the buffer SIZE, FW will check whether the next buffer is ready (updated with new data), and

- if the next buffer is ready, FW will switch buffers (read pointer gets updated to the base address of the next buffer) and will generate Ping Pong IRQ to the Host.

- Otherwise, if the next buffer is not ready (SIZE = 0), FW will not switch the buffer and will play the last valid sample until the new data becomes available.

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0.

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Figure 10 - Ping-Pong protocol

Another typical Ping-Pong operation consists in letting the sDMA read the audio samples from a huge buffer in external memory. The ABE will awake the sDMA on each Ping/Pong boundaries. The Host processor receives an IRQ when the sDMA reaches the half of the huge external buffer.

In the case the DSP is used to generate the Ping/Pong audio samples the time sequence of operation will be :

- 1. The Ping and Pong base addresses are defined from ABE-HAL (ARM side) and communicated to the DSP

- 2. DSP fills the Ping buffer

- 3. ABE HAL on ARM configures the data path and starts the path with "abe\_enable\_data\_transfer()"

- 4. The ABE firmware starts reading the Ping and immediately generates an IRQ to tell the DSP to fill the Pong buffer

- 5. DSP fills the Pong buffer upon reception of the IRQ, then goes in low-power mode.

- 6. The ABE firmware reads the Pong buffer and immediately generates an IRQ to tell the DSP to fill the Ping buffer

- 7. DSP fills the Ping buffer upon reception of the IRQ, then goes in low-power mode

- 8. The ABE firmware reads the Ping and generates an IRQ to tell the DSP to fill the Pong ... etc ...

### 2.1.3 AESS memory access

AESS can only be addressed with 32bits addressing, from MPU/DSP or from the sDMA. The accesses made to DMEM or CBPr registers in 8bits or 16bits modes will results in bus errors.

### 3 List of services

The following services are provided by the ABE-HAL:

### 3.1 Data Types used for APIs

| Name of the type | Physical allocation                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| abe_samp_t       | enum                                                         | Types of samples formats:  - MONO_MSB: Mono channel, samples MSB aligned in one 32 bits container  - MONO_RSHIFTED_16: Mono channel, samples LSB aligned on 16bits in one 32 bits container  - STEREO_RSHIFTED_16: Stereo channel, Two LSB samples aligned on 16bits in two 32 bits containers. Left sample is exchanged first, then the Right sample.  - STEREO_16_16: Two 16-bit samples Right (MSB) / Left (LSB) in one 32-bit container  - STEREO_MSB: stereo channel defined with MSB aligned samples in two 32bits container. Left sample is exchanged first.  - THREE_MSB, FOUR_MSB, FIVE_MSB, SIX_MSB, SEVEN_MSB: three to seven channels defined with MSB aligned samples in 32bits containers, for MM_UL port only. |

| equ_t            | structure of :<br>equ_param1<br>equ_param2<br>up to 24 Q6.26 | Filter coefficients with three formats allowed: type of filter filter length Coefficients in AESS arithmetic format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| data_format_t    | structure of :<br>freq_t f,<br>samp_t<br>samp_format         | Sampling frequency of the stream Sample format type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| dma_t            | struct {                                                     | Data used for the DMA initialization:  Number of "elements" to be exchanged on each AE DMAreq L3 address of the audio exchanges using CBPr registers  Physical addresses in the L3 and L4 space of the buffer in DMEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 5: List of the data types

### 3.2 Hardware control API list

All API can be called at any time. When the OPP value does not correspond to the addressed feature some artifacts may appear due to a sudden change in the signal amplitude.

### 3.2.1 abe\_reset\_hal

Prototype:u32 abe\_reset\_hal (void);

Parameter:

**Operations**: reset the HAL by reloading the static variables and default AESS registers. Called after a PRCM cold-start of ABE.

### 3.2.2 abe\_load\_fw

Prototype: u32 abe\_reload\_fw\_param (u32 \*FW);

Parameter: pointer to the firmware binary table

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

**Operations**: load the Audio Engine firmware located in the file "abe\_firmware.c". This file incorporates the version number of the firmware, which must be in line with the version of the HAL. If the firmware was already loaded the PMEM will not be reloaded again.

### 3.2.3 abe\_reload\_fw

Prototype: u32 abe\_load\_fw\_param (u32 \*FW);

Parameter: pointer to the firmware binary table

**Operations**: load the Audio Engine firmware located in the file "abe\_firmware.c". This file incorporates the version number of the firmware, which must be in line with the version of the HAL. The ABE is supposed to be coming from an ABE hardware reset: the AE is stalled and the PMEM will be loaded.

### 3.2.4 abe\_write\_event\_generator

Prototype:u32 abe\_write\_event\_generator (u32 e);

#### Parameters:

e: EVENT\_TIMER, EVENT\_44100.

Operations: loads the AESS event generator hardware source: either 48kHz or 44.1kHz based.

### 3.2.5 abe\_read\_use\_case\_opp

Prototype:u32 abe\_read\_use\_case\_opp (u32 \*u, u32 \*o);

### Parameter:

o: returned data is the OPP value

u: list of active simultaneous use-cases, ends with a zero.

**Operations**: This API is used to anticipate the OPP value when transitioning to a new use-case. The input parameter is the list of all the anticipated use-case activity. This API returns the lowest possible OPP based on the desired use-case to be implemented.

### 3.2.6 abe\_set\_opp\_processing

Prototype:u32 abe\_set\_opp\_processing (u32 opp)

### Parameter:

New processing network and OPP:

- 1: OPP 25%: simple multimedia features, including low-power player, VDD=0.93V, ABE FCLK=49MHz

- 2: OPP 50%: multimedia and voice calls, VDD=0.93V, ABE FCLK=98MHz

- 3: OPP100%: multimedia complex use-cases, VDD=1.1V, ABE FCLK=196MHz

**Operations**: OPP management is under the responsibility of the operating system and PRCM device drivers. Once the OS decides to change OPP value, the FW must change the task-list scheduling. This API tells the FW scheduler to execute only the task corresponding to the given OPP. The corresponding AE ports and tasks are supposed to be set/reset accordingly before this switch in order to change the OPP index on the fly without audio artifacts. No hardware configuration and programming is needed during an OPP switch: the AESS has a set of pins directly connected to PRCM. Going from low OPP to

TEXAS INSTRUMENTS www.ti.com

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

high OPP, the API must be called <u>after</u> the clock change. Similarly the API must be called <u>before</u> the clock change when going from high to lower OPP.

### 3.2.7 abe\_connect\_serial\_port

Prototype:u32 abe\_connect\_serial\_port (u32 id, abe\_data\_format\_t \*f, u32

mcbsp id);

# Parameters : id: port name

f : data format

i : peripheral ID (McBSP #1, #2, #3)

**Operations**: enables the data exchanges between a **McBSP** and an ATC buffer in DMEM. This API is used to connect 44.1/48kHz McBSP streams to MM\_EXT\_OUT, 48kHz McBSP streams to MM\_EXT\_IN and 8/16kHz voice streams to VX\_UL, VX\_DL, BT\_VX\_UL, BT\_VX\_DL.

### 3.2.8 abe\_set\_mux\_demux\_tdm\_parameters

Prototype:u32 abe\_set\_tdm\_parameters (u32 id, u32 nbchanel, u32 type, u32

buff1\_labelID, u32 buff2\_labelID,u32 buff3\_labelID,u32 buff4\_labelID,u32

shift\_channel1,u32 shift\_channel2,u32 shift\_channel3,u32 shift\_channel4);

#### Parameters:

id: port name

nbchanel: number of chanel to transfer type: 0= mux, 1= demux, 2 = tdm mode

buff1\_labelID..buff4\_labelID: LabelID of each couple of stereo channel to transfer to the output shift\_channel1..shift\_channel4: Schift value to apply for each stereo channel, range value: -2..-30

**Operations**: This API sets all parameters in DMEM for TDM port or for MUX, DEMUX configurations. No port is not open, just configured.

**Note**: Shift value is -2 maximum value to ensure non saturation values on the output. Port name is MMEXTOUT or TDM.

This API can only be used with: MM\_EXT\_OUT\_PORT, TDM\_DL\_PORT, PDM\_DL\_PORT, MM\_UL\_PORT, DMIC PORT.

### Examples:

```

abe_set_mux_demux_tdm_parameters(MM_EXT_OUT_PORT,2,2,OUT_DL1_Route_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,0,0,0,0);

abe_set_mux_demux_tdm_parameters(TDM_DL_PORT,8,2,OUT_DL1_Route_labelID,OUT_DL2_Route_labelID,OUT_DL1_Route_labelID,OUT_DL2_Route_labelID,0,0,0,0);

abe_set_mux_demux_tdm_parameters(PDM_DL_PORT,4,0,McPDM_Out1_labelID,McPDM_Out2_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,0,0,0,0);

abe_set_mux_demux_tdm_parameters(MM_UL_PORT,6,0,OUT_MMUL_12_Route_labelID,OUT_MMUL_34_Route_labelID,OUT_MMUL_56_Route_labelID,Dummy_Regs_labelID,0,0,0,0);

abe_set_mux_demux_tdm_parameters(DMIC_PORT,6,1,DMIC0_96_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_labelID,Dummy_Regs_l

```

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### 3.2.9 abe\_connect\_tdm\_port

Prototype:u32 abe\_connect\_tdm\_port (u32 id, abe\_data\_format\_t \*f, u32

mcbsp id);

### Parameters:

id: port namef: data format

i : peripheral ID (McBSP #1, #2, #3)

**Operations**: enables the data exchanges between a **McBSP** and an ATC buffer in DMEM. This API is used to connect 44.1/48kHz. This API permits to transfer up to 8 channels.

Nota: only MM\_EXT\_OUT port can be used with this API.

### 3.2.10 abe\_init\_ping\_pong\_buffer

Prototype : u32 abe\_init\_ping\_pong\_buffer (u32 id, u32 size\_bytes, u32 n\_buffers, u32 \*p)

### Parameters:

id: port name

size\_bytes : half-buffer (ping) size

n buffers: number of half-buffers, must be set to 2

p: returned pointer to the base address of the ping-pong buffer

### 3.2.11 abe connect dmareg ping pong port

### Parameters:

id: port name

f: desired data format

d: desired dma request line (0..7)

s: half-buffer (ping) size

returned\_dma\_t : returned pointer to the base address of the ping-pong buffer and number of samples to exchange during a DMA request.

**Operations**: enables the data exchanges between a DMA. On each dma\_request activation the DMA will exchange "s" bytes and switch to the "pong" buffer for a new buffer exchange.

### 3.2.12 abe\_connect\_irq\_ping\_pong\_port

**Prototype**: u32 abe\_connect\_dmareq\_ping\_pong\_port (port\_id id, data\_format\_t \*f, u32 i, u32 s, u32 \*p, u32 flag);

### Parameters:

id: port name

f: desired data format

i: index of the call-back subroutine to call

s: half-buffer (ping) size

TEXAS INSTRUMENTS www.ti.com

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

p: returned pointer to the base address of the ping-pong buffer flag : determines whether it is MCU or DSP IRQ ( PING\_PONG\_WITH\_MCU\_IRQ / PING\_PONG\_WITH\_DSP\_IRQ)

**Operations**: enables the data exchanges between a direct access to the DMEM memory of ABE using cache flush. On each IRQ activation a subroutine registered with "abe\_add\_subroutine" will be called. This subroutine will generate a number of samples, and will copy these samples to DMEM memory, and then it will call API "abe\_set\_ping\_pong\_buffer" to notify that the new amount of samples is available in the pong buffer.

### 3.2.13 abe\_connect\_cbpr\_dmareq\_port

#### Parameters:

id: port name

f : desired data format

d: desired dma\_request line (0..7)

a : returned pointer to the base address of the CBPr register and number of samples to exchange during a DMA\_request.

**Operations**: enables the data exchange between a DMA and the ABE through the CBPr registers of AESS.

### Note:

For MMUL port, sample format is MMUL\_2, MMUL\_4, MMUL\_6

### 3.2.14 abe\_enable\_data\_transfer

Prototype: u32 abe enable data transfer (u32 id)

### Parameter :

p: port identifier

**Operations**: enables the ATC descriptor. Starting a channel is done in the following sequence: the port is initialized, ATC descriptor is enabled, the peripheral is started. See paragraph "start/stop sequences".

#### 3.2.15 abe disable data transfer

Prototype:u32 abe\_disable\_data\_transfer (u32 id)

### Parameter:

p: port identifier

**Operations**: disables the ATC descriptor. Closing a channel is done in the following sequence: the port is stopped, ATC descriptor is disabled, the peripheral is stopped. See paragraph "start/stop sequences".

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

3.2.16 abe\_enable\_io\_task

Prototype:u32 abe\_enable\_io\_task (u32 id)

Parameter : id: port identifier

**Operations**: Enables i/o task processing for a defined port. Note: Only available for BT-VX-DL and BT-VX-UL ports

3.2.17 abe\_disable\_io\_task

Prototype:u32 abe\_disable\_io\_task (u32 id)

Parameter : id: port identifier

**Operations**: Disables i/o task processing for a defined port. Note: Only available for BT-VX-DL and BT-VX-UL ports

3.2.18 abe\_reset\_port

Prototype:u32 abe\_reset\_port (u32 id)

Parameters : id: port name

**Operations**: stop the port activity and reload default parameters on the associated processing features.

3.2.19 abe\_set\_ping\_pong\_buffer

Prototype:u32 abe\_set\_ping\_pong\_buffer (u32 port, u32 n\_bytes)

Parameter : port : ABE port ID

n\_bytes: number of bytes loaded in the next buffer

**Operations**: Notifies FW that the host processor completed the data transfer, and that the next pingpong buffer has been updated with n bytes.

3.2.20 abe read next ping pong buffer

Prototype:u32 abe\_read\_next\_ping\_pong\_buffer (u32 port, u32 \*p, u32 \*n);

Parameter:

port : ABE port ID

p: returned base address to the next available buffer in bytes offset of DMEM

n: returned buffer size in bytes

TEXAS INSTRUMENTS www.ti.com

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

Operations: Returns the next base address of the next ping pong buffer and its size.

### 3.2.21 abe\_read\_remaining\_data

Prototype:u32 abe\_read\_remaining\_data (u32 port, u32 \*n);

# Parameters :

port : ABE port ID

n: pointer to the amount of remaining data in the ping-pong buffer

**Operations**: This API is used to compute the amount of data remaining in the big input buffers for the purpose of audio/video synchronization.

### 3.2.22 abe\_read\_offset\_from\_ping\_buffer

Prototype:u32 abe\_read\_offset\_from\_ping\_buffer (u32 port, u32 \*n);

### Parameters:

port : ABE port ID

n: pointer to the current ping-pong buffer firmware read pointer

**Operations**: This API is used to compute the current ping pong firmware read pointer. The read pointer is provided as the offset from the Ping Pong buffer start address (Ping start address) and is represented in samples.

### 3.2.23 abe\_read\_port\_address

Prototype:u32 abe\_read\_port\_address (u32 port, abe\_dma\_t \*dma2);

### Parameter :

Port ID: port id

dma: output pointer to the DMA iteration and data destination pointer

Operations: This API returns the address of the DMA register used on this audio port.

### 3.2.24 abe\_write\_select\_pdm\_output

Prototype: u32 abe\_write\_select\_pdm\_output (u32 path);

### Parameter:

Path: 1 for output on handset, 2 for output on handsfree, 3 for output on headset and handsfree at the same time

**Operations**: This API selects output for OPP25 path between headset or handsfree or the 2 ones at the same time.

### 3.3 Signal processing API list

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0.

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

### 3.3.1 abe\_write\_gain, abe\_write\_mixer

Prototype:u32 abe\_write\_gain (u32 id, u32 f\_g, u32 ramp, u32 p)

abe\_write\_mixer has the same prototype and behavior (legacy).

#### Parameters:

allow overflows.

Id : name of the gain/mixer

f g : input gains (millibels)

ramp: ramp time (milliseconds) of the gain/mixer

p: port corresponding to the above gains

**Operations**: Load the input gain coefficients in FW memory. If the gain of interest is currently muted, this API will update the gain value to be loaded in FW memory once this gain gets unmuted. In the case the automatic gain adaptation is set, if the sum of all the gains of mixers MIXDL1, MIXDL2, MIXVXREC, MIXAUDUL is larger than 0dB, than all the input gains values will be adjusted in order to not

| Mixer ID    | Port           |

|-------------|----------------|

| DL1_MIXER   | TONES_DL path  |

|             | VX_DL path     |

|             | MM_DL path     |

|             | MM_UL2 path    |

| DL2_MIXER   | TONES_DL path  |

|             | VX_DL path     |

|             | MM_DL path     |

|             | MM_UL2 path    |

| SDT_MIXER   | Uplink path    |

|             | Downlink path  |

| ECHO_MIXER  | DL1_MIXER path |

|             | DL2_MIXER path |

| AUDUL_MIXER | TONES_DL path  |

|             | Uplink path    |

|             | MM_DL path     |

| VXREC_MIXER | TONES_DL path  |

|             | VX_DL path     |

|             | MM_DL path     |

|             | VX_UL path     |

Table 6 : Mixers' port indexes

| Mixer ID   | Port       |

|------------|------------|

| DMIC1_GAIN | LEFT path  |

|            | RIGHT path |

| DMIC2_GAIN | LEFT path  |

|            | RIGHT path |

| DMIC3_GAIN | LEFT path  |

|            | RIGHT path |

| AMIC_GAIN  | LEFT path  |

|            | RIGHT path |

| DL1_GAIN   | LEFT path  |

| _          | RIGHT path |

| DL2_GAIN   | LEFT path  |

|            | RIGHT path |

| BTUL_GAIN  | LEFT path  |

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

RIGHT path

Table 7 : Gains' port indexes

### 3.3.2 abe\_set\_router\_configuration

Prototype:u32 abe\_set\_router\_configuration (u32 id, u32 k, u32 \*param)

#### Parameters:

Id : name of the router configuration : unused router t : routing information

**Operations**: The uplink router takes its input from DMIC (6 samples), AMIC (2 samples), MM-EXT-UL (2 samples) and BT-VX-UL (up to 2 samples). Each sample will be individually stored into an intermediate table of 16 elements. The table is used to route the samples to three directions: MM\_UL, MM\_UL2 and VX\_UL ports.

Switching the microphone sources can be done on-the-fly.

Example: the 10 first index of the routing are used for MM\_UL channels which are respectively connected DMIC1\_LEFT (MM\_UL[0]), DMIC1\_RIGH (MM\_UL[1]), DMIC2\_LEFT (MM\_UL[2]), DMIC2\_RIGH (MM\_UL[3]), DMIC3\_LEFT (MM\_UL[4]), DMIC3\_RIGH (MM\_UL[5]), NULL\_DATA (MM\_UL[6]), NULL\_DATA (MM\_UL[7]).

```

VX_UL will be connected to AMIC_LEFT (VX_UL[0]), AMIC_RIGHT (VX_UL[1]).

```

### 3.3.3 abe\_write\_equalizer

Prototype:u32 abe\_write\_equalizer (u32 id, abe\_equ\_t \*param)

#### Parameters:

Id: name of the equalizer Param: equalizer coefficients

**Operations**: Load the coefficients in CMEM. After reloading the firmware the default coefficients corresponds to "no equalizer feature". Once the coefficients are loaded the memory of the filter is reseted.

### 3.3.4 abe\_write\_asrc

Prototype:u32 abe\_write\_asrc (u32 port, s32 dppm)

## Parameters :

port : port name

dppm : drift value to compensate [ppm]

**Operations**: Load the drift parameters to FW memory.

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 .

Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

If this API is not called, the FM will manage itself the drift adaptation. After reloading the firmware and enabling the corresponding port, the default parameters correspond to ASRC adaptation with switching drift between 250ppm and -250ppm.

Loading the drift value with null pointer disables the feature.

Loading the drift value with the value different than null pointer, corresponds to ASRC adaptation with switching drift between loaded value and negated loaded value.

Note that the correct usage of this API is to call it only after the appropriate port's data transfer has already been enabled. Otherwise, enabling of a particular port's data transfer after this API has already been called will overwrite the ASRC parameters set by this API.

### 3.3.5 abe\_use\_compensated\_gain

Prototype : u32 abe\_use\_compensated\_gain (u32 id)

Parameter : Id: port id

**Operations**: this API sets a flag. This flag is used to adjust the input mixer's gains in order to always have a maximum 0dB sum for all the gains. Setting the flag results in avoiding saturations in the mixer.

### 3.3.6 abe\_mute\_gain

Prototype: u32 abe\_mute\_gain (u32 id, u32 p)

Parameter:

Id: mixer id

P: sub port id

**Operations**: this API mutes the gain on a specific port of the mixer.

### 3.3.7 abe\_unmute\_gain

**Prototype**: u32 abe unmute gain (u32 id, u32 p)

Parameter: Id: mixer id P: sub port id

**Operations**: this API restores the original gain from the mixer's port.

### 3.3.8 abe\_read\_gain

Prototype: u32 abe\_read\_gain (u32 id, u32 p)

Parameter: Id: mixer id P: sub port id

**Operations**: this API provides the input gain value currently loaded in FW memory. If the gain of interest is currently muted, this API will provide the gain value to be loaded in FW memory once this gain gets unmuted.

### 3.3.9 abe\_mono\_mixer

Prototype: u32 abe\_mono\_mixer (u32 id, u32 on\_off)

Parameter:

Id: mixer id (MIXDL1/MIXDL2 only)

on\_off : enable\disable flag

TEXAS INSTRUMENTS

www.ti.com

OMAP4430 Silicon Rev 2.x - OMAP4460 Silicon Rev 1.x - OMAP4470 Silicon Rev 1.0 Audio Back-End (ABE) and Hardware Abstraction Layer (HAL) Addendum

**Operations**: this API programs DL1/DL2 mixers to provide mono samples at the output. If mono mixer is enabled, the same sample will be provided to both Left and Right mixer outputs.

### 3.4 Interface and accessory control API

### 3.4.1 abe\_irq\_processing

Prototype: u32 abe irg processing (void);

**Operations**: This subroutine will check the ABE IRQ source and act accordingly. IRQ sources are originated from the Ping-Pong protocols (call-backs to the multimedia player).

### 3.4.2 abe\_clear\_irq

Prototype : u32 abe\_clear\_irq (void);

**Operations**: This subroutine will clear the MCU IRQ.

### 3.4.3 abe\_connect\_debug\_trace

Prototype : u32 abe\_connect\_debug\_trace (dma\_t \*a);

### Parameters :

a : returned pointer to the DMEM base address of the trace buffer and number of bytes to exchange after a DMA request.

**Operations**: returns the address and size of the real-time debug trace buffer, the content of which will vary from one firmware release to an other.