$\mathsf{OMAP}^{\mathsf{TM}}$

# OMAP4470 Multimedia Device Engineering Samples ES1.0 Texas Instruments OMAP<sup>TM</sup> Family of Products

# Data Manual Operating Condition Addendum *Version 1.0*

Public Version

Literature Number: SWPU325 February 13

OMAP is a trademark of Texas Instruments Incorporated.

page: 1

# **HISTORY**

| Version | Date      | Notes |

|---------|-----------|-------|

| 1.0     | 15-Jan-13 | 1     |

# Note:

1. Creation.

#### **WARNING: EXPORT NOTICE**

Recipient agrees that it will not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S, EU and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S or other applicable laws, without obtaining prior authorisation from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

-US ECCN: 3E991 -EU ECCN: 3E991

and may require export or re-export license for shipping it in compliance with certain countries regulations.

# **TABLE OF CONTENTS**

| O  | MAP4                            | 1470 MULTIMEDIA DEVICE                                                                                                                                    | 1        |

|----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1  | INT                             | TRODUCTION                                                                                                                                                | 5        |

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | DEVICE SUPPORT NOMENCLATURE  OMAP4470 MIPI® DISCLAIMER  TRADEMARKS  COMMUNITY RESOURCES  ABOUT THIS MANUAL  ominal, Minimum, Maximum Voltages Terminology |          |

| 2  | RE                              | ECOMMENDED OPERATION                                                                                                                                      | 11       |

|    | 2.1<br>2.2<br>2.3<br>2.4        | MICRO PROCESSOR UNIT (MPU) CLOCKS                                                                                                                         | 14<br>16 |

| 3  | OP                              | PP DEPENDENCIES                                                                                                                                           | 21       |

| 4  | MA                              | AXIMUM FREQUENCY BY INTERFACE                                                                                                                             | 22       |

| ١N | /IPORT                          | TANT NOTICE                                                                                                                                               | 25       |

### 1 INTRODUCTION

The aim of this document is to describe the operating conditions of the following OMAP4470 devices:

- OMAP4470-1500

- OMAP4470-1300

This document contains the description of each OPP (Operating Performance Point) for processors clocks and device core clocks.

#### NOTE

OPP50, OPP100, OPPTB, OPPNT and OPPNTSB may also be called OPP50, OPP100, OPP\_TURBO, OPP\_NITRO and OPP\_NTSB in other OMAP documents.

Table 1-1 describes the supported  $vdd_mpu$  ( $V_{DD1}$ ) operating performance point (OPP) for each OMAP4470 devices.

Table 1-1. OMAP4470 vdd mpu (V<sub>DD1</sub>) Operating Points<sup>(1)</sup>

| OMAP4470<br>Devices         | OPP50 | OPP100 | ОРРТВ | OPPNT | OPPNTSB |

|-----------------------------|-------|--------|-------|-------|---------|

| V <sub>DD1</sub> (vdd_mpu)  |       |        |       |       |         |

| OMAP4470-1500 (MPU@1500MHz) | √     | √      | √     | √     | V       |

| OMAP4470-1300 (MPU@1300MHz) | √     | √      | √     | √     |         |

<sup>(1)</sup> This table is specific to  $vdd_mpu(V_{DD1})$  with AVS feature enabled.

Table 1-2 describes the supported  $vdd_iva$  ( $V_{DD2}$ ) operating performance point (OPP) for each OMAP4470 devices.

Table 1-2. OMAP4470 vdd\_iva (V<sub>DD2</sub>) Operating Points<sup>(1)</sup>

| OMAP4470<br>Devices        | OPP50 | OPP100       | ОРРТВ        | OPPNT        | OPPNTSB  |

|----------------------------|-------|--------------|--------------|--------------|----------|

| V <sub>DD2</sub> (vdd_iva) |       |              |              |              |          |

| OMAP4470-1500 (IVA@500MHz) | √     | $\checkmark$ | $\checkmark$ | $\checkmark$ | <b>√</b> |

| OMAP4470-1300 (IVA@430MHz) | √     | √            | √            | √            |          |

<sup>(1)</sup> This table is specific to vdd\_iva (V<sub>DD2</sub>) operating performance points with AVS feature enabled.

Table 1-3 describes two sets of supported vdd\_core ( $V_{DD3}$ ) operating performance point (OPP) for each OMAP4470 devices.

Table 1-3. OMAP4470 vdd\_core (V<sub>DD3</sub>) Operating Points<sup>(1)</sup>

| OMAP4470<br>Devices                             | OPP50 | OPP100       | OPP119       |

|-------------------------------------------------|-------|--------------|--------------|

| V <sub>DD3</sub> (vdd_core) – High Performances |       |              |              |

| OMAP4470-1500 (SGX @384MHz, L3@233MHz)          | √     | $\checkmark$ | $\checkmark$ |

| OMAP4470-1300 (SGX @384MHz, L3@233MHz)          | √     | √            | $\checkmark$ |

| V <sub>DD3</sub> (vdd_core) – Low Power         |       |              |              |

| OMAP4470-1500 (SGX @384MHz, L3@200MHz)          | √     | V            | √            |

| OMAP4470-1300 (SGX @384MHz, L3@200MHz)          | √     | √            | √            |

<sup>(1)</sup> This table is specific to vdd\_core (V<sub>DD3</sub>) operating performance points with AVS feature enabled.

#### **NOTE**

OMAP  $^{\text{TM}}$  4 processors are intended for manufacturers of smartphones and other mobile devices, as well as enterprise, industrial and consumer markets.

# 1.1 Device Support Nomenclature

This device is currently in development. Experimental / Prototype devices are shipped against the following disclaimer:

"This product is still in development and is intended for internal evaluation purposes." Notwithstanding any provision to the contrary, TI makes no warranty expressed, implied, or statutory, including any implied warranty of merchantability of fitness for a specific purpose, for experimental / prototype devices.

# 1.2 OMAP4470 MIPI® Disclaimer

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. The material contained herein is provided on an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence.

ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document; and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance with the contents of this Document.

The use or implementation of the contents of this Document may involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents, patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any IPR or claims of IPR as respects the contents of this Document or otherwise. Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

MIPI Alliance, Inc. c/o IEEE-ISTO 445 Hoes Lane Piscataway, NJ 08854 Attn: Board Secretary 252 Read This First SWPU231M-July 2010-Revised November 2010 Copyright ©

# 1.3 Trademarks

OMAP, TMS320DMC64x, C64x, ICECrusher, ICEPick and SmartReflex are trademarks of Texas Instruments Incorporated. PicoDLP is a registered trademark of Texas Instruments Incorporated.

ARM, Jazelle, and Thumb are registered trademarks of ARM Limited.

ETM, ETB, ARM9, CoreSight, ISA, Cortex, and Neon are trademarks of ARM Limited.

Java is a trademark of Sun Microsystems, Inc.

Bluetooth is a registered trademark of Bluetooth SIG, Inc. and is licensed to Texas Instruments.

HDQ is a trademark of Benchmarg.

1-Wire is a registered trademark of Dallas Semiconductor.

Windows, WinMobile, and Direct3D are trademarks of Microsoft Corporation in the United States and other countries.

USSE and POWERVR are trademarks or registered trademarks of Imagination Technologies Ltd.

Mentor Graphics is a registered trademark of Mentor Graphics Corporation or its affiliated companies in the United States and other countries.

OpenGL is a trademark of Silicon Graphics, Inc.

OpenVG and OpenMAX are trademarks of Khronous Group, Inc.

Arteris is a trademark of Arteris, Inc.

RealVideo is a registered trademark of RealNetworks, Inc.

SD is a registered trademark of Toshiba Corporation.

eSD is a trademark of SD Association.

MMC and eMMC are trademarks of MultiMediaCard Association.

SonicsMX, Sonics3220 are trademarks or registered trademarks of Sonics, Inc.

JTAG is a registered trademark of JTAG Technologies, Inc.

Linux is a registered trademark of Linus Torvalds.

On2 is a registered trademark of On2 Technologies.

Symbian and all Symbian-based trademarks and logos are trademarks of Symbian Software Limited.

Synopsys is a registered trademark of Synopsys, Inc.

I2S is a trademark of Phillips Electronics.

#### OMAP4470 ES1.0 DM Operating Condition Addendum Public Version 1.0 - SWPU325

I<sup>2</sup>C is a trademark of Phillips Semiconductor Corp.

SLIMbus and MIPI are registered trademarks of the Mobile Industry Processor Interface (MIPI) Alliance.

Flex-OneNAND and OneNAND are trademarks of SAMSUNG Electronics, Corporation.

Palm OS is a registered trademark of Palm Inc.

All other trademarks are the property of their respective owners.

# 1.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### TI Embedded Processors Wiki Texas Instruments Embedded Processors Wiki.

Established to help developers get started with Embedded Processors from Texas Instruments and to foster innovation and growth of general knowledge about the hardware and software surrounding these devices.

# 1.5 About This Manual

Nominal, Minimum, Maximum Voltages Terminology

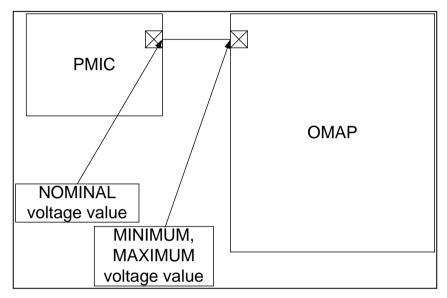

Figure 1-1. Nominal, Minimum, Maximum Voltages Terminology

The Figure 1-1 describes the location of the voltages specified in this manual.

- Board design must guaranty that the minimum pre-AVS voltage values documented in Table 2-1, Table 2-3, Table 2-5 (MPU, IVA, CORE - Initial Pre-AVS Voltages Settings) tables are met at the OMAP balls.

- The nominal voltage value documented in Table 2-1, Table 2-3, Table 2-5 tables is the recommended voltage to be applied at power IC (PMIC) level, taking into account board IR drop and PMIC tolerance.

- Maximum voltage value should not be exceeded at OMAP ball level to prevent accelerated aging

of the device.

### 2 RECOMMENDED OPERATION

# 2.1 Micro Processor Unit (MPU) Clocks

#### **CAUTION**

For more information on nominal, minimum, maximum voltages location, see the Figure 1-1, Nominal, Minimum, Maximum Voltages Terminology.

Table 2-1 shows the recommended VDD1 (corresponding to vdd mpu, MPU voltage) initial voltages settings with AVS class 1.5 enabled.

Table 2-1: MPU - Initial pre-AVS Voltages Settings (5)

|                             | RETENTION (4) | 0     | OPPBOOT (4) |       | OPP50 (1)(6) |       | OPP100 (1)(6) |       | OPPTB (1)(3) |       | OPPNT (1)(3) |       | 3)    | OPPNTSB (1)(3) |       | 1)(3) |       |       |       |

|-----------------------------|---------------|-------|-------------|-------|--------------|-------|---------------|-------|--------------|-------|--------------|-------|-------|----------------|-------|-------|-------|-------|-------|

|                             | MIN           | MIN   | NOM         | MAX   | MIN          | NOM   | MAX           | MIN   | NOM          | MAX   | MIN          | NOM   | MAX   | MIN            | NOM   | MAX   | MIN   | NOM   | MAX   |

| V <sub>DD1</sub> (2)(5) (V) | 0.750         | 0.890 | 0.937       | 0.984 | 0.999        | 1.037 | 1.066         | 1.140 | 1.200        | 1.260 | 1.247        | 1.312 | 1.378 | 1.306          | 1.375 | 1.444 | 1.306 | 1.387 | 1.444 |

- (1) Enabling AVS feature is mandatory for these OPPs (OPP50, OPP100, OPPTB, OPPNT or OPPNTSB) to avoid impact on device reliability and lifetime POH (Power-On-Hours).

- (2) These V<sub>DD1</sub> (vdd\_mpu) voltage ranges define the safe V<sub>DD1</sub> (vdd\_mpu) voltage ranges to be used before using AVS class 1.5 feature for OPPs calibration. The minimum voltage may be lower after calibration than this specification.

- (3) ABB (adaptive body biasing polarization) feature must be enabled for OPPTB, OPPNT and OPPNTSB operating points following the ABB programming feature steps described in PRCM chapter of OMAP4470 TRM.

- (4) Retention and OPPBOOT V<sub>DD1</sub> (vdd\_mpu) voltage ranges are defined with AVS feature disabled.

- (5) Nominal voltage value documented in this table corresponds to the voltage to be applied at power IC (PMIC) level. Whereas minimum and maximum voltage values correspond to the possible voltage at OMAP ball level.

- (6) OPP50 or OPP100 can be used with AVS disabled for short periods of time (i.e. for ROM code or boot loader) as long as only one CPU is active. This is not applicable to OPPTB, OPPNT, OPPNTSB.

OMAP is a trademark of Texas Instruments Incorporated.

1. . . . . .

page: 11

Table 2-2 describes the standard processors clocks speed characteristics vs V<sub>DD1</sub> (corresponding to vdd\_mpu, MPU voltage) with AVS class 1.5 enabled or disabled.

Table 2-2: MPU Clocks AC Performances (2)

|                                 |                                                  | OPP50                 |                 | OI                    | PP100           | 0                     | РРТВ     | OI                    | PPNT     | OPPNTSB               |                         |

|---------------------------------|--------------------------------------------------|-----------------------|-----------------|-----------------------|-----------------|-----------------------|----------|-----------------------|----------|-----------------------|-------------------------|

| Description                     | Source Clock                                     | Max<br>Freq.<br>(MHz) | Ratio           | Max<br>Freq.<br>(MHz) | Ratio           | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio                   |

| DPLL_MPU<br>Locked<br>Frequency | -                                                | 1600                  | -               | 1600                  | -               | 1100                  | -        | 1300                  | -        | 1500                  | -                       |

| MPU_DPLL_CLK                    | DPLL_MPU<br>Locked<br>Frequency<br>(CLKOUT_M2)   | 400                   | 2 *<br>(M2 = 2) | 800                   | 2 *<br>(M2 = 1) | -                     | ı        | ı                     | ı        | ı                     | -                       |

| MPU_DPLL_CLK                    | DPLL_MPU<br>Locked<br>Frequency<br>(CLKOUTX2_M3) | -                     | -               | -                     | -               | 1100                  | (M3 = 1) | 1300                  | (M3 = 1) | 1500                  | (M3 = 1) <sup>(1)</sup> |

<sup>(1)</sup> This ratio is configurable by software programming. For more information, see the Power, Reset, and Clock Management / Clock Manager Functional Description / Internal Clock Generation section of the OMAP4470 TRM.

#### **NOTE**

The programmable divider for the asynchronous bridge to Audio Back-end (ABE) must be set to MPU\_DPLL\_CLK / 8 when MPU\_DPLL\_CLK clock frequency is above 800MHz. It can be set to MPU\_DPLL\_CLK / 4 for MPU\_DPLL\_CLK clock running at 800MHz or lower.

The programmable divider for the asynchronous bridge to L3 and Memory Adapter (MA) interfaces to EMIF must be set to MPU\_DPLL\_CLK / 4 when MPU\_DPLL\_CLK clock frequency is above 800MHz. They can be set to MPU\_DPLL\_CLK / 2 for MPU\_DPLL\_CLK clock running at 800MHz or lower.

For more information on the programmable dividers for the asynchronous bridges, see the CM\_MPU\_MPU\_CLKCTRL register, CLKSEL\_ABE\_DIV\_MODE and CLKSEL\_EMIF\_DIV\_MODE bits, in the OMAP4470 TRM.

Please make sure to set the corresponding register bits to 0x1 before increasing the MPU\_DPLL\_CLK clock frequency above 800MHz.

Please make sure to decrease the MPU\_DPLL\_CLK clock frequency at or below 800MHz before setting the corresponding register bits to 0x0.

<sup>(2)</sup> The DPLL ratios documented in this table are recommended ratios. Other values may apply.

#### **CAUTION**

During MPU DVFS sequencing to a higher OPP, please make sure to increase the voltage prior to the clocks frequencies.

During MPU DVFS sequencing to a lower OPP, please make sure to decrease the clocks frequencies prior to the voltage.

Not respecting this MPU DVFS sequencing may lead to internal timing violations.

#### **CAUTION**

When MPU requires higher voltage and higher CORE voltage, CORE voltage has be increased prior to MPU voltage, then CORE clocks frequencies have to be increased prior to MPU clocks frequencies. When MPU allows lower voltage and lower CORE voltage, MPU clocks frequencies have to be decreased prior to CORE clocks frequencies, then MPU voltage has be decreased prior to CORE voltage.

Not respecting this MPU and CORE DVFS sequencing may lead to internal timing violations or/and insufficient OMAP interconnect throughput.

# 2.2 Imaging and Video Accelerator (IVA) Clocks

#### CAUTION

For more information on nominal, minimum, maximum voltages location, see the Figure 1-1, Nominal, Minimum, Maximum Voltages Terminology.

Table 2-3 shows the recommended V<sub>DD2</sub> (corresponding to vdd iva, IVA voltage) initial voltages settings with AVS class 1.5 enabled.

Table 2-3: IVA - Initial pre-AVS Voltages Settings

|                                        | RETENTION (4) | 0     | OPPBOOT (4) |       | OPP50 (1)(6) |       | OPP100 (1)(6) |       | OPPTB (1)(3) |       | OPPNT (1)(3) |       | 3)    | OPPNTSB (1)(2)(3) |       | (2)(3) |       |      |       |

|----------------------------------------|---------------|-------|-------------|-------|--------------|-------|---------------|-------|--------------|-------|--------------|-------|-------|-------------------|-------|--------|-------|------|-------|

|                                        | MIN           | MIN   | NOM         | MAX   | MIN          | NOM   | MAX           | MIN   | NOM          | MAX   | MIN          | NOM   | MAX   | MIN               | NOM   | MAX    | MIN   | NOM  | MAX   |

| V <sub>DD2</sub> <sup>(2)(5)</sup> (V) | 0.750         | 0.879 | 0.925       | 0.971 | 0.902        | 0.962 | 0.997         | 1.080 | 1.137        | 1.194 | 1.223        | 1.287 | 1.351 | 1.306             | 1.375 | 1.444  | 1.306 | 1.38 | 1.444 |

- (1) Enabling AVS feature is mandatory for these OPPs (OPP50, OPP100, OPPTB, OPPNT or OPPNTSB) to avoid impact on device reliability and lifetime POH (Power-On-Hours).

- (2) These V<sub>DD2</sub> (vdd\_iva) voltage ranges define the safe V<sub>DD2</sub> (vdd\_iva) voltage ranges to be used before using AVS class 1.5 feature for OPPs calibration. The minimum voltage may be lower after calibration than this specification.

- (3) ABB (adaptive body biasing polarization) feature must be enabled for OPPTB, OPPNT and OPPNTSB operating points following the ABB programming feature steps described in PRCM chapter of OMAP4470 TRM.

- (4) Retention and OPPBOOT V<sub>DD2</sub> (vdd\_iva) voltage ranges are defined with AVS feature disabled.

- (5) Nominal voltage value documented in this table corresponds to the voltage to be applied at power IC (PMIC) level. Whereas minimum and maximum voltage values correspond to the possible voltage at OMAP ball level.

- (6) OPP50 or OPP100 can be used with AVS disabled for short periods of time (i.e. for ROM code or boot loader) as long as only one CPU is active. This is not applicable to OPPTB, OPPNT, OPPNTSB.

OMAP is a trademark of Texas Instruments Incorporated.

page: 14

All other trademarks are the property of their respective owners.

Table 2-4 describes the standard processors clocks speed characteristics vs V<sub>DD2</sub> (corresponding to vdd\_iva, IVA voltage) with AVS class 1.5 disabled or enabled.

Table 2-4: IVA Clocks AC Performances (2)

|                           |                                               | C                     | PP50      | OF                    | P100     | OF                    | РРТВ     | OF                    | PPNT     | OPPNTSB               |          |

|---------------------------|-----------------------------------------------|-----------------------|-----------|-----------------------|----------|-----------------------|----------|-----------------------|----------|-----------------------|----------|

| Description               | Source Clock                                  | Max<br>Freq.<br>(MHz) | Ratio     | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio    |

| DPLL_IVA Locked Frequency | -                                             | 1862                  | -         | 1862                  | -        | 992                   | -        | 1290                  | -        | 1500                  | -        |

| IVAHD_ROOT_CLK            | DPLL_IVA<br>Locked Frequency<br>(CLKOUTX2_M5) | 133                   | (M5 = 14) | 266                   | (M5 = 7) | 331                   | (M5 = 3) | 430                   | (M5 = 3) | 500                   | (M5 = 3) |

| DSP_ROOT_CLK              | DPLL_IVA<br>Locked Frequency<br>(CLKOUTX2_M4) | 232.8                 | (M4 = 8)  | 465.5                 | (M4 = 4) | 496                   | (M4 = 2) | 430                   | (M4 = 3) | 500                   | (M4 = 3) |

<sup>(1)</sup> This ratio is configurable by software programming. For more information, see the Power, Reset, and Clock Management / Clock Manager Functional Description / Internal Clock Generation section of the OMAP4470 TRM

#### **CAUTION**

During IVA DVFS sequencing to a higher OPP, please make sure to increase the voltage prior to the clocks frequencies.

During IVA DVFS sequencing to a lower OPP, please make sure to decrease the clocks frequencies prior to the voltage.

Not respecting this IVA DVFS sequencing may lead to internal timing violations.

#### **CAUTION**

When IVA requires higher voltage and higher CORE voltage, CORE voltage has be increased prior to IVA voltage, then CORE clocks frequencies have to be increased prior to IVA clocks frequencies. When IVA allows lower voltage and lower CORE voltage, IVA clocks frequencies have to be decreased prior to CORE clocks frequencies, then IVA voltage has be decreased prior to CORE voltage.

Not respecting this IVA and CORE DVFS sequencing may lead to internal timing violations or/and insufficient OMAP interconnect throughput.

<sup>(2)</sup> The DPLL ratios documented in this table are recommended ratios. Other values may apply.

# 2.3 Core and Peripheral Clocks

#### **CAUTION**

For more information on nominal, minimum, maximum voltages location, see the Figure 1-1, Nominal, Minimum, Maximum Voltages Terminology.

Table 2-5 shows the recommended VDD3 (corresponding to vdd core, CORE and Graphic accelerator voltage at ball level) voltage ranges. GPU and Core are in the same voltage domain.

**Table 2-5: Core Voltages**

|                             | RETENTION (4) | 0     | OPPBOOT <sup>(4)</sup> |       |      | OPP50 <sup>(3)</sup> |      |       | OPP100 <sup>(3</sup> | 3)    | OPP119 (3)(5) |      |      |

|-----------------------------|---------------|-------|------------------------|-------|------|----------------------|------|-------|----------------------|-------|---------------|------|------|

|                             | MIN           | MIN   | NOM                    | MAX   | MIN  | NOM                  | MAX  | MIN   | NOM                  | MAX   | MIN           | NOM  | MAX  |

| V <sub>DD3</sub> (1)(2) (V) | 0.750         | 0.879 | 0.925                  | 0.971 | 0.93 | 0.98                 | 1.03 | 1.069 | 1.126                | 1.181 | 1.12          | 1.19 | 1.24 |

- (1) This table defines:

- Either, the safe V<sub>DD3</sub> (vdd\_core) voltage ranges to be used before using a AVS class 1.5 feature for OPPs calibration. After calibration, the minimum voltage may be lower than this specification.

- Or, the safe V<sub>DD3</sub> (vdd\_core) voltage ranges to be used when AVS class 1.5 feature is disabled.

- (2) Nominal voltage value documented in this table corresponds to the voltage to be applied at power IC (PMIC)

- level. Whereas minimum and maximum voltage values correspond to the possible voltage at OMAP ball level.

(3) Enabling AVS feature is mandatory for these OPPs (OPP50, OPP100, OPP119) to avoid impact on device reliability and lifetime POH (Power-On-Hours).

- Retention and OPPBOOT V<sub>DD3</sub> (vdd\_core) voltage ranges are defined with AVS feature disabled.

- (5) OPP119 operating point corresponds to the Overdrive mode.

Table 2-6 and Table 2-7 show the standard device speed characteristics vs V<sub>DD3</sub> (vdd\_core voltage).

Table 2-6: Core Clocks AC Performances – HIGH Performances - From DPLL CORE (3)

|                              |                            | OP           | P50             | OF           | P100            | OPF          | P119 <sup>(2)</sup> |

|------------------------------|----------------------------|--------------|-----------------|--------------|-----------------|--------------|---------------------|

|                              |                            | Max<br>Freq. |                 | Max<br>Freq. |                 | Max<br>Freq. |                     |

| Description                  | Source Clock               | (MHz)        | Ratio           | (MHz)        | Ratio           | (MHz)        | Ratio               |

| DPLL_CORE Locked Frequency   | -                          | 1864         | -               | 1864         | -               | 1864         | -                   |

| CORE_X2_CLK                  |                            |              | (M5 = 8)        |              | (M5 = 8)        |              | (M5 = 4)            |

| (CLKOUTX2_M5)                | DPLL_CORE Locked Frequency | 233          | (1)             | 233          | (1)             | 466          | (1)                 |

|                              |                            |              | (M4 = 8)        |              | (M4 = 8)        |              | (M4 = 8)            |

| DLL_X2_CLK (CLKOUTX2_M4)     | DPLL_CORE Locked Frequency | 233          | (1)             | 233          | (1)             | 233          | (1)                 |

| CORE_CLK                     | CORE_X2_CLK                | 233          | 1 (1)           | 233          | 1 (1)           | 466          | 1 <sup>(1)</sup>    |

| L3_ICLK                      | CORE_CLK                   | 116.5        | 2 (1)           | 116.5        | 2 (1)           | 233          | 2 (1)               |

| L4_ICLK                      | L3_ICLK                    | 58.25        | 2 (1)           | 58.25        | 2 (1)           | 116.5        | 2 (1)               |

|                              |                            |              | 2 * (M2 =<br>2) |              | 2 * (M2 =<br>2) |              | 2 * (M2 =<br>1)     |

| PHY_ROOT_CLK (CLKOUT_M2)     | DPLL_CORE Locked Frequency | 466          | (1)             | 466          | (1)             | 932          | (1)                 |

| DDR_PHY_CLK (DDRPHY divider) | PHY_ROOT_CLK (CLKOUT_M2)   | 233          | 2 (1)           | 233          | 2 (1)           | 466          | 2 (1)               |

| EMIF_FCLK (DDRPHY divider)   | DDR_PHY_CLK                | 116.5        | 2 (1)           | 116.5        | 2 (1)           | 233          | 2 (1)               |

| EMIF_DLL_FCLK                | DLL_X2_CLK                 | 116.5        | 2               | 116.5        | 2               | 116.5        | 2                   |

| GPMC_CLK                     | L3_ICLK                    | 58.25        | 2 (1)           | 58.25        | 2 (1)           | 58.25        | 4 (1)               |

This ratio is configurable by software programming. For more information, see the OMAP4470 TRM.

OPP119 operating point corresponds to the Overdrive mode.

The DPLL ratios documented in this table are recommended ratios. Other values may apply.

Table 2-7: Core Clocks AC Performances – LOW Power - From DPLL CORE (3)

|                              |                               | OP                    | P50                | OP                    | P100               | OPP                   | 2119 <sup>(2)</sup> |

|------------------------------|-------------------------------|-----------------------|--------------------|-----------------------|--------------------|-----------------------|---------------------|

| Description                  | Source Clock                  | Max<br>Freq.<br>(MHz) | Ratio              | Max<br>Freq.<br>(MHz) | Ratio              | Max<br>Freq.<br>(MHz) | Ratio               |

| DPLL_CORE Locked Frequency   | -                             | 1600                  | -                  | 1600                  | -                  | 1600                  | -                   |

| CORE_X2_CLK<br>(CLKOUTX2_M5) | DPLL_CORE Locked<br>Frequency | 200                   | (M5 =<br>8)        | 400                   | (M5 =<br>4)        | 400                   | (M5 = 4)            |

| DLL_X2_CLK<br>(CLKOUTX2_M4)  | DPLL_CORE Locked<br>Frequency | 200                   | (M4 =<br>8)<br>(1) | 200                   | (M4 =<br>8)<br>(1) | 200                   | (M4 = 8)            |

| CORE_CLK                     | CORE_X2_CLK                   | 200                   | 1 (1)              | 400                   | 1 (1)              | 400                   | 1 (1)               |

| L3_ICLK                      | CORE_CLK                      | 100                   | 2 (1)              | 200                   | 2 (1)              | 200                   | 2 (1)               |

| L4_ICLK                      | L3_ICLK                       | 50                    | 2 (1)              | 100                   | 2 (1)              | 100                   | 2 (1)               |

| PHY_ROOT_CLK<br>(CLKOUT_M2)  | DPLL_CORE Locked<br>Frequency | 400                   | 2 * (M2<br>= 2)    | 800                   | 2 * (M2<br>= 1)    | 800                   | 2 * (M2<br>= 1)     |

| DDR_PHY_CLK (DDRPHY divider) | PHY_ROOT_CLK<br>(CLKOUT_M2)   | 200                   | 2 (1)              | 400                   | 2 (1)              | 400                   | 2 (1)               |

| EMIF_FCLK (DDRPHY divider)   | DDR_PHY_CLK                   | 100                   | 2 (1)              | 200                   | 2 (1)              | 200                   | 2 (1)               |

| EMIF_DLL_FCLK                | DLL_X2_CLK                    | 100                   | 2                  | 100                   | 2                  | 100                   | 2                   |

| GPMC_CLK                     | L3_ICLK                       | 50                    | 2 (1)              | 100                   | 2 (1)              | 100                   | 2 (1)               |

<sup>(1)</sup> This ratio is configurable by software programming. For more information, see the OMAP4470 TRM.(2) OPP119 operating point corresponds to the Overdrive mode.(3) The DPLL ratios documented in this table are recommended ratios. Other values may apply.

# 2.4 **Graphic Accelerator Clocks**

Table 2-8 and Table 2-9 show the recommended  $V_{DD3}$  (corresponding to vdd\_core, Core and Graphic accelerator voltage) standard graphic accelerator clocks speed characteristics vs  $V_{DD3}$ .

Table 2-8: Graphic Accelerator Clocks – HIGH Performances (3)

|                              |                              | ОР           | P50      | OPP100       |          | OPP          | 119 <sup>(2)</sup> |

|------------------------------|------------------------------|--------------|----------|--------------|----------|--------------|--------------------|

|                              |                              | Max<br>Freq. |          | Max<br>Freq. |          | Max<br>Freq. |                    |

| Description                  | Source Clock                 | (MHz)        | Ratio    | (MHz)        | Ratio    | (MHz)        | Ratio              |

| SGX544-SC (3D graphic accel  | erator)                      |              |          |              |          |              |                    |

| DPLL_PER Locked<br>Frequency | -                            | 1536         | -        | 1536         |          | 1536         | -                  |

|                              | DPLL_PER Locked<br>Frequency |              | (M7 = 8) |              | (M7 = 5) |              | (M7 = 4)           |

| PER_SGX_FCLK                 | (CLKOUTX2_M7)                | 192          | (1)      | 307          | (1)      | 384          | (1)                |

| SGX_FCLK                     | PER_SGX_FCLK                 | 192          | 1        | 307          | 1        | 384          | 1                  |

| BB2D (GC320 – 2D graphic ac  | ccelerator)                  |              |          |              |          |              |                    |

| DPLL_PER Locked Frequency    | -                            | 1536         | -        | 1536         | -        | 1536         | -                  |

|                              | DPLL_PER Locked<br>Frequency |              | (M7 = 8) |              | (M7 = 5) |              | (M7 = 4)           |

| PER_BB2D_FCLK                | (CLKOUTX2_M6)                | 192          | (1)      | 307          | (1)      | 384          | (1)                |

| BB2D_FCLK                    | PER_BB2D_FCLK                | 192          | 1        | 307          | 1        | 384          | 1                  |

<sup>(1)</sup> This ratio is configurable by software programming. For more information, see the OMAP4470 TRM.

<sup>(2)</sup> OPP119 operating point corresponds to the Overdrive mode.

<sup>(3)</sup> The DPLL ratios documented in this table are recommended ratios. Other values may apply.

Table 2-9: Graphic Accelerator Clocks – LOW Power (3)

|                           |                                         | OPP50                 |           | OPP100                |          | OPP119 (2)            |          |

|---------------------------|-----------------------------------------|-----------------------|-----------|-----------------------|----------|-----------------------|----------|

| Description               | Source Clock                            | Max<br>Freq.<br>(MHz) | Ratio     | Max<br>Freq.<br>(MHz) | Ratio    | Max<br>Freq.<br>(MHz) | Ratio    |

| SGX3D                     |                                         |                       |           |                       |          |                       |          |

| DPLL_PER Locked Frequency | -                                       | 1536                  | -         | 1536                  | -        | 1536                  | -        |

| PER_SGX_FCLK              | DPLL_PER Locked Frequency (CLKOUTX2_M7) | 153.6                 | (M7 = 10) | 307.2                 | (M7 = 5) | 384                   | (M7 = 4) |

| SGX_FCLK                  | PER_SGX_FCLK                            | 153.6                 | 1         | 307.2                 | 1        | 384                   | 1        |

| BB2D (GC320)              | BB2D (GC320)                            |                       |           |                       |          |                       |          |

| DPLL_PER Locked Frequency | -                                       | 1536                  | -         | 1536                  | -        | 1536                  | -        |

| PER_BB2D_FCLK             | DPLL_PER Locked Frequency (CLKOUTX2_M6) | 153.6                 | (M7 = 10) | 307.2                 | (M7 = 5) | 384                   | (M7 = 4) |

| BB2D_FCLK                 | PER_BB2D_FCLK                           | 153.6                 | 1         | 307.2                 | 1        | 384                   | 1        |

- (1) This ratio is configurable by software programming. For more information, see the OMAP4470 TRM.

- (2) OPP119 operating point corresponds to the Overdrive mode.

- (3) The DPLL ratios documented in this table are recommended ratios. Other values may apply.

#### **CAUTION**

During CORE DVFS sequencing to a higher OPP, please make sure to increase the voltage prior to the clocks frequencies.

During CORE DVFS sequencing to a lower OPP, please make sure to decrease the clocks frequencies prior to the voltage.

Not respecting this CORE DVFS sequencing may lead to internal timing violations.

#### **CAUTION**

When using CORE OPP100 (or OPP119) and thus setting related CORE voltage, it is highly recommended to set also CORE clocks frequencies to their maximum allowed values for enabling best throughputs on OMAP interconnect and DDR.

Using CORE OPP50 maximum allowed clock frequencies while CORE OPP100 (or OPP119) voltage is required, may lead to random system lock-up depending on the application's throughput requirements (OMAP interconnect and DDR).

Same issues may happen in case CORE OPP100 is used while CORE OPP119 is required.

#### 3 OPP DEPENDENCIES

#### **CAUTION**

The OPP dependencies apply only when both voltage domains are in ON state. That is:

- Any module in the domain may be powered, clocked and active

- SMPS is in active mode, delivering the voltage corresponding to current OPP

For more information on the Voltage Domain definitions, see the Power, Reset and Clock Management / Voltage Management Functional Description section in the OMAP4470 TRM

Reminder: for an OPP, the frequency corresponds to the maximum frequency allowed at a voltage (this voltage corresponds to the minimum voltage level required on a domain).

The dependencies defined in the tables below apply to the minimum voltages, the frequencies do not matter.

The following rules must be respected on OPPs between the three voltage domains:

- If one of the MPU voltage domain or IVA voltage domain is at OPP100 or above (i.e. OPPTB, OPPNT, OPPNTSB), then the CORE voltage domain must be set to OPP100 or above (i.e. OPP119).

- 2) The MPU voltage domain and IVA voltage domain must be both at OPP50 for having the CORE voltage domain at OPP50.

- 3) If the MPU voltage domain is at OPPTB or above (i.e. OPPNT, OPPNTSB), then IVA voltage domain must be at least at OPP100 (i.e. OPP100, OPPTB, OPPNT, OPPNTSB).

Table 3-1 shows the acceptable MPU and IVA voltage domain OPPs according to the CORE voltage domain OPP.

Table 3-1: OPP Dependencies (CORE vs IVA / MPU)

| CORE voltage domain OPP            | OPP50 | OPP100, OPP119                          |  |

|------------------------------------|-------|-----------------------------------------|--|

| Acceptable MPU voltage domain OPPs | OPP50 | OPP50, OPP100, OPPTB, OPPNT,<br>OPPNTSB |  |

| Acceptable IVA voltage domain OPPs | OPP50 | OPP50, OPP100, OPPTB, OPPNT,<br>OPPNTSB |  |

Table 3-2 shows the acceptable IVA voltage domain OPPs according to the MPU voltage domain OPP.

Table 3-2: OPP Dependencies (MPU vs IVA)

| rable of E. Of the Deportation of the 1774 |                                            |                               |  |  |  |  |

|--------------------------------------------|--------------------------------------------|-------------------------------|--|--|--|--|

| MPU voltage domain OPP                     | OPP50, OPP100                              | OPPTB, OPPNT, OPPNTSB         |  |  |  |  |

| Acceptable IVA voltage domain OPPs         | OPP50, OPP100,<br>OPPTB, OPPNT,<br>OPPNTSB | OPP100, OPPTB, OPPNT, OPPNTSB |  |  |  |  |

# 4 MAXIMUM FREQUENCY BY INTERFACE

The following table summarizes the maximum frequencies supported by OMAP4470 interfaces, and by OPPs.

**Table 4-1. Maximum Frequency By Interface**

|                                                                      |                                         |                                                                                  | CORE Voltage Domain |              |             |  |

|----------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|---------------------|--------------|-------------|--|

| Interfaces                                                           | Modes                                   | External I/O Clocks                                                              | OPP119 (MHz)        | OPP100 (MHz) | OPP50 (MHz) |  |

| General-Purpose Memory Controller (GPMC)                             |                                         |                                                                                  |                     |              |             |  |

|                                                                      | 100MHZ                                  | gpmc_clk                                                                         | 100                 | 100          | 50          |  |

| GPMC/NOR Flash Interface—Synchronous Mode                            | 66MHZ                                   | gpmc_clk                                                                         | 66                  | 66           | 33          |  |

|                                                                      | 58MHZ                                   | gpmc_clk                                                                         | 58.25               | 58.25        | 58.25       |  |

| External Memory Interface (EMIF)                                     | <u> </u>                                |                                                                                  |                     |              |             |  |

| EMIF—LPDDR SDRAM                                                     | DDR mode – 466MHz                       | lpddr2x_ck,<br>lpddr2x_nck (clocks)<br>lpddr2x_dqs,<br>lpddr2x_ndqs<br>(strobes) | 466                 | 233          | 233         |  |

|                                                                      | DDR mode – 400MHz                       | lpddr2x_ck,<br>lpddr2x_nck (clocks)<br>lpddr2x_dqs,<br>lpddr2x_ndqs<br>(strobes) | 400                 | 400          | 200         |  |

| Camera                                                               |                                         |                                                                                  |                     |              |             |  |

| CSI21 and CSI22 - High-Speed Mode                                    | Up to 3 Data Lanes                      | One pair of lanes                                                                | 500                 | 500          | 400         |  |

| CSIZ1 and CSIZZ - night-speed wode                                   | 4 data lanes                            | One pair of lanes                                                                | 412                 | 412          | 400         |  |

|                                                                      | CCP2 - Class 0                          | One pair of lanes                                                                | 208                 | 208          | 208         |  |

| Camera Serial Interface (CCP2—CSI22)                                 | CCP2 - Class 1                          | One pair of lanes                                                                | 208                 | 208          | 208         |  |

|                                                                      | CCP2 - Class 2                          | One pair of lanes                                                                | 325                 | 325          | 325         |  |

| Parallel Camera Interface (CPI)                                      | Video and Graphics Digitizer 1.8-V Mode | cam2_pclk                                                                        | 148.5               | 148.5        | NA          |  |

| Display                                                              | •                                       |                                                                                  |                     |              |             |  |

| DSS—Display Controller (DISPC)                                       | QXGA SDR Mode                           | dispc2_pclk                                                                      | 170                 | 170          | NA          |  |

| DSI1 and DSI2                                                        | Up To 3 Data Lanes                      | One pair of lanes                                                                | 450                 | 450          | 450         |  |

| DSI1                                                                 | 4 Data Lanes                            | One pair of lanes                                                                | 412                 | 412          | 412         |  |

| McBSP                                                                |                                         |                                                                                  |                     |              |             |  |

| McBSP1 and McBSP2—I2S/PCM Full and Half Cycle—<br>Master Mode—24 MHz | Master Mode                             | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 24.57               | 24.57        | 12.28       |  |

| McBSP1 and McBSP2—I2S/PCM Full and Half Cycle—<br>Slave Mode—12 MHz  | Slave Mode                              | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 12.288              | 12.288       | 6.144       |  |

| McBSP1, McBSP2, and McBSP3 Set#1—                                    | Master Mode                             | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 12.288              | 12.288       | 6.144       |  |

| TDM / Half-Cycle - 12MHz, 5-pF Load Capacitance                      | Slave Mode                              | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 12.288              | 12.288       | 6.144       |  |

| McBSP1, McBSP2, and McBSP3 Set#1—                                    | Master Mode                             | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 6.144               | 6.144        | 3.072       |  |

| TDM / Half-Cycle - 6MHz, 40-pF Load Capacitance                      | Slave Mode                              | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 6.144               | 6.144        | 3.072       |  |

| McBSP3—I2S/PCM Full and Half Cycle—<br>Master Mode—24 MHz            | Master Mode                             | x=[1,2,3]<br>abe_mcbspx_clk,<br>x=[1,2,3]                                        | 24.57               | 24.57        | 12.28       |  |

| McBSP3—I2S/PCM Full and Half Cycle—<br>Slave Mode—12 MHz             | Slave Mode                              | abe_mcbspx_clk,<br>x=[1,2,3]                                                     | 12.288              | 12.288       | 6.144       |  |

| McBSP4—I2S/PCM—Full Cycle—<br>48-MHz Master Mode                     | Master Mode                             | mcbsp4_clk                                                                       | 48                  | 48           | 24          |  |

| McBSP4—I2S/PCM—Full Cycle—<br>24-MHz Slave Mode                      | Slave Mode                              | mcbsp4_clk                                                                       | 24                  | 24           | 12          |  |

OMAP is a trademark of Texas Instruments Incorporated.

page: 22

# OMAP4470 ES1.0 DM Operating Condition Addendum Public Version 1.0 - SWPU325

|                                        |                                 |                                             | CORE Voltage Domain |              |             |

|----------------------------------------|---------------------------------|---------------------------------------------|---------------------|--------------|-------------|

| Interfaces                             | Modes                           | External I/O Clocks                         | OPP119 (MHz)        | OPP100 (MHz) | OPP50 (MHz) |

| McBSP4—I2S/PCM—Half-Cycle—             | Master Mode                     | mcbsp4_clk                                  | 24                  | 24           | 12          |

| 24-MHz Master and 12-MHz Slave         | Slave Mode                      | mcbsp4_clk                                  | 12                  | 12           | 6           |

| McASP                                  |                                 | abe_mcasp_ahclkx /<br>abe_mcasp_aclkx       | 24.57               | 24.57        | 24.57       |

| McSPI                                  |                                 |                                             |                     | •            |             |

| McSPI1, McSPI2, McSPI3 and McSPI4      | Slave Mode                      | mcspix_clkx,<br>x=[1,2,3,4]                 | 16                  | 16           | 8           |

| McSPI1 and McSPI2—Master Mode          | Master - 24-MHz Frequency Clock | mcspix_clkx,<br>x=[1,2,3,4]                 | 24                  | 24           | 24          |

| McSPI2, McSPI3, and McSPI4—Master Mode | Master - 48-MHz Frequency Clock | mcspix_clkx,<br>x=[1,2,3,4]                 | 48                  | 48           | 48          |

| DMIC                                   | Master/Receive Mode             | abe_dmic_clk[3:1]                           | 3.84                | 3.84         | 3.84        |

| МсРDМ                                  |                                 | abe_clks /<br>abe_pdm_lb_clk                | 19.2                | 19.2         | 19.2        |

| ABE SlimBus1, SlimBus2                 | SLIMBUS SDR 24.6 MHz            | slimbusx_clock,                             | 24.57               | 24.57        | 12.28       |

| ABE SlimBus1, SlimBus2                 | SLIMBUS SDR 19.2 MHz            | x=[1,2]<br>slimbusx_clock,                  | 19.2                | 19.2         | 9.6         |

| High-Speed Synchronous Interface       |                                 | x=[1,2]                                     |                     |              |             |

|                                        | Transmit Mode—1.2V              | hsi1_acdata,                                | 192                 | 192          | 96          |

|                                        | Receive Mode—1.2V               | hsi1_acflag hsi1_cadata,                    | 225                 | 225          | 112         |

| High-Speed Synchronous Interface 1     | Transmit Mode—1.8V              | hsi1_caflag<br>hsi1_acdata,                 | 192                 | 192          | 96          |

|                                        | Receive Mode—1.8V               | hsi1_acflag<br>hsi1_cadata,                 | 225                 | 225          | 112         |

| High-Speed Synchronous Interface 2     | Transmit Mode—1.2V              | hsi1_caflag<br>hsi2_acdata,                 | 192                 | 192          | 96          |

|                                        | Receive Mode—1.2V               | hsi2_acflag<br>hsi2_cadata,                 | 225                 | 225          | 112         |

|                                        |                                 | hsi2_caflag<br>hsi2_acdata,                 |                     |              |             |

|                                        | Transmit Mode—1.8V              | hsi2_acflag<br>hsi2_cadata,                 | 192                 | 192          | 96          |

|                                        | Receive Mode—1.8V               | hsi2_caflag                                 | 225                 | 225          | 112         |

| USB                                    | ULPI SDR—Slave Mode—1.8V        | uahaQ ulaiahu alle                          | 60                  | 60           | NA          |

| Universal Serial Bus (USB)—USBA0       | HSIC DDR Transmit Mode—1.2V     | usba0_ulpiphy_clk usbb1_hsic_strobe         | 240                 | 240          | NA<br>NA    |

|                                        | HSIC DDR Receive Mode—1.2V      | usbb1_hsic_strobe                           | 240                 | 240          | NA NA       |

| Universal Serial Bus (USB)—USBB1       | ULPI TLL Mode—Master Mode—1.8V  | usbb1_ulpiphy_clk                           | 60                  | 60           | 60          |

|                                        | ULPI SDR Mode—Slave Mode—1.8V   | usbb1_ulpiphy_clk                           | 60                  | 60           | NA NA       |

|                                        | HSIC DDR Transmit Mode—1.2V     | usbb2_hsic_strobe                           | 240                 | 240          | NA          |

|                                        | HSIC DDR Receive Mode—1.2V      | usbb2_hsic_strobe                           | 240                 | 240          | NA          |

| Universal Serial Bus (USB)—USBB2       | ULPI TLL Mode—Master Mode       | usbb2_ulpitll_clk                           | 60                  | 60           | 60          |

|                                        | ULPI SDR Mode—Slave Mode        | usbb2_ulpiphy_clk                           | 60                  | 60           | NA          |

| I2C & SmartReflex                      |                                 |                                             |                     |              |             |

|                                        | Standard Mode I2C & SR          | i2cx_scl,<br>v=[1 2 3 4 5]                  | 0.1                 | 0.1          | 0.1         |

|                                        | Fast Mode I2C & SR              | x=[1,2,3,4,5]<br>i2cx_scl,<br>y=[1,2,3,4,5] | 0.4                 | 0.4          | 0.4         |

|                                        | High Speed I2C                  | x=[1,2,3,4,5]<br>i2cx_scl,<br>x=[1,2,3,4]   | 3.4                 | 3.4          | 3.4         |

|                                        | High Speed SR                   | x=[1,2,3,4]<br>i2cx_scl,                    | 2.13                | 2.13         | 2.13        |

| SDMMC                                  | V -11-11-1                      | x=[5]                                       |                     | 1            |             |

|                                        | SD Identification Mode          | sdmmc1_clk                                  | 0.4                 | 0.4          | 0.4         |

|                                        | (1.8V IO) Standard SD Mode      | sdmmc1_clk                                  | 24                  | 24           | 24          |

|                                        | (3.3V IO) Standard SD Mode      | sdmmc1_clk                                  | 24                  | 24           | 24          |

| MMC/SD/SDIO 1 Interface                | High-Speed SD Mode – SR25       | sdmmc1_clk                                  | 48                  | 48           | 48          |

|                                        | High-Speed SD Mode – SR50       | sdmmc1_clk                                  | 64                  | 64           | 32          |

|                                        | High-Speed SD Mode-DDR50        | sdmmc1_clk                                  | 48                  | 48           | 24          |

OMAP is a trademark of Texas Instruments Incorporated.

page: 23

All other trademarks are the property of their respective owners.

# OMAP4470 ES1.0 DM Operating Condition Addendum Public Version 1.0 - SWPU325

|                                            |                              |                          | CORE Voltage Domain |              |             |  |

|--------------------------------------------|------------------------------|--------------------------|---------------------|--------------|-------------|--|

| Interfaces                                 | Modes                        | External I/O Clocks      | OPP119 (MHz)        | OPP100 (MHz) | OPP50 (MHz) |  |

|                                            | Standard SDR JC64 Mode       | sdmmc2_clk               | 24                  | 24           | 24          |  |

| MMC/SD/SDIO 2 Interface                    | High-Speed SDR JC64 Mode     | sdmmc2_clk               | 48                  | 48           | 48          |  |

|                                            | High-Speed DDR JC64 Mode     | sdmmc2_clk               | 48                  | 48           | 48          |  |

| MMC/SD/SDIO 3, 4, and 5 Interfaces         | High-Speed SDIO Mode         | sdmmcx_clk,<br>x=[3,4,5] | 48                  | 48           | 48          |  |

| Digital Processing Manager Interface (DPM) |                              |                          |                     |              |             |  |

| Trace Port Interface Unit (TPIU)           | TPIU PLL DDR Mode – 160 MHz  | atpiu_clk                | 160                 | 160          | 160         |  |

|                                            | Lauterbach DDR Transmit Mode | astm_clk                 | 100                 | 100          | 100         |  |

| System Trace Module Interface (STM)        | MIPI DDR Transmit Mode       | astm_clk                 | 100                 | 100          | 100         |  |

|                                            | MIPI SDR Transmit Mode       | astm_clk                 | 100                 | 100          | 100         |  |

| JTAG                                       |                              |                          |                     |              |             |  |

| JTAG                                       | Free-Running Clock Mode      | jtag_tck /<br>jtag_rtck  | 20                  | 20           | 15          |  |

| JIAG                                       | Adaptive Clock Mode          | jtag_tck /<br>jtag_rtck  | 20                  | 20           | 15          |  |

| CJTAG                                      | For MMC PADs                 | jtag_tck                 | 17.5                | 17.5         | 14          |  |

| WING                                       | For JTAG PADs                | jtag_tck                 | 20                  | 20           | 19          |  |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>