### ANO69

# Low Cost, Long Range One Way Audio Communications at 900 MHz

**By Michael Burns**

### Keywords

- CC1100

- CC1100E (955 MHz)

- CC1101

- CC1150

- Audio

- MSP430

- Frequency Diversity

- Forward Error Correction (FEC)

- FCC 15.247 Compliance

### Introduction

This design implements a one way audio link, based on the Texas Instruments CC1150 (transmit only), CC1101 (transmit/receive), and the MSP430F2232 microcontroller. The system consists of a 'transmitter' card and a 'receiver' card, and operates in the 900 MHz band (868 - 928 MHz). A power amplifier is included on the transmitter card, to increase the power output to +20 dBm while maintaining acceptable harmonic suppression. The receiver card contains a Low Noise Amplifier to increase the receiver sensitivity.

Note that the design could also be used at 955 MHz by substituting a CC1100E for the CC1150 on the transmitter card and for the CC1101 on the receiver card. Some modification to the component values in the PA matching network may also prove necessary.

The goals for this design were low cost, and long range. To this end, an external CODEC (COder-DECoder) is not used.

The MSP430F2232s 10 bit ADC is used to

sample audio data and Timer A is used in PWM (Pulse Width Modulation) mode to recover the audio from the digital data. Audio data is sent in 'packets'; that is, 36 ('single Tx' mode) or 44 ('double Tx' mode) ADC samples are collected and sent in a single packet every 4.5 ('single Tx' mode) or 5.5 ('double Tx' mode) msecs.

Two transmission techniques will be described. In 'single Tx' mode, each packet is sent only once. In 'double Tx' mode, each packet is sent twice, at two different frequencies. 'Single Tx' mode allows for the use of a lower data rate (150 kbps) or for the use of Forward Error Correction (FEC) at a higher data rate (300 kbps). It is also possible to increase the audio sample rate from 8 kHz to 12 kHz in 'single Tx' mode. 'Double Tx' offers increased robustness, but requires the use of a higher data rate (300 kbps) and reduced output power due to FCC 15.247 restrictions. Project collateral discussed in this application note can be downloaded the following from URL: http://www.ti.com/lit/zip/SWRA237.

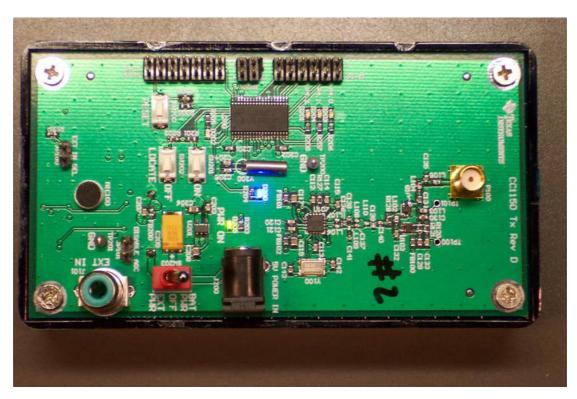

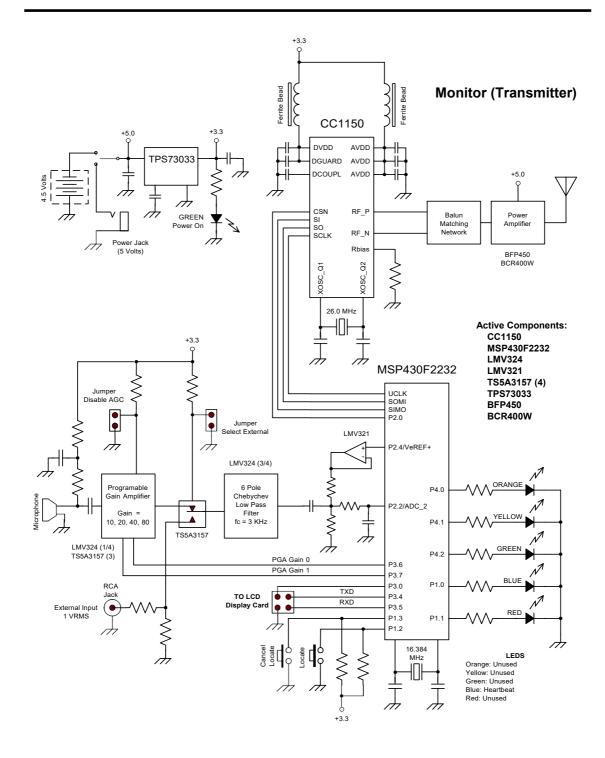

Figure 1 – Transmitter

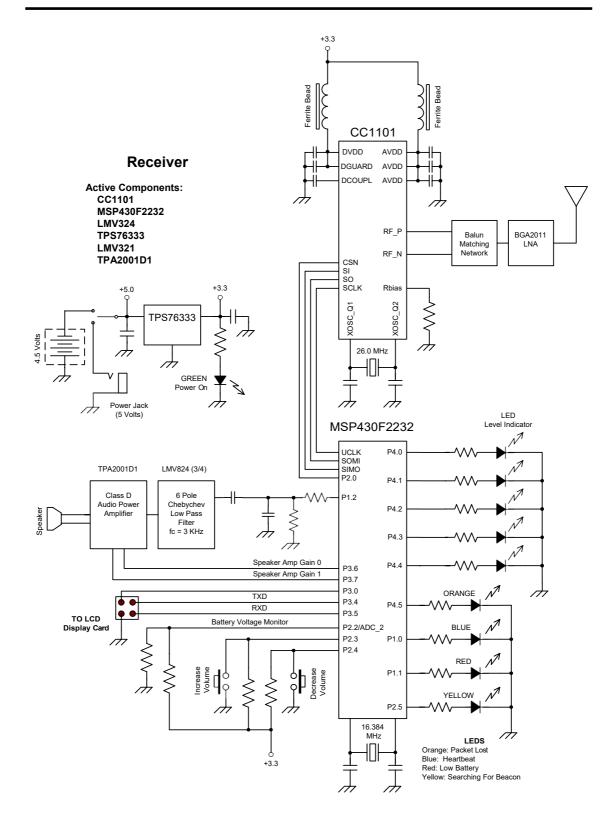

Figure 2 - Receiver

#### Hardware Description - Transmitter

A CC1150 low power RF transmitter is used, along with a discrete power amplifier using a BFP450 NPN silicon RF transistor and a BCR400W Active Bias Controller. This amplifier is capable of producing up to +20 dBm of output power while maintaining harmonic levels more than 50 dB lower than the fundamental. The microcontroller is a MSP430F2232, operating at 16.384 MHz. The MSP430F2232 includes a built-in 10 bit ADC. The audio path includes a Programmable Gain Amplifier with gains of 10, 20, 40, and 80, followed by a six pole Chebychev low pass filter with a cutoff frequency of 3 KHz. Five LEDs are contained on the card, including a 'heartbeat' indicator, along with 'Locate' and 'Cancel Locate' buttons.

Refer to schematic, Figure 12.

#### Hardware Description - Receiver

A CC1101 low power RF transceiver is used, along with a discrete low noise RF amplifier using a BGA2011 NPN RF transistor. A MSP430F2232 microcontroller operating at 16.384 MHz is used. The MSP430F2232 is capable of producing a Pulse Width Modulated audio signal using a built in timer, eliminating the requirement of an external DAC. This PWM timer is driven at the full MCU clock frequency (16.384 MHz), twice that required to convert the 10 bit ADC samples into pulses of the required length. This doubles the frequency of the idle tone from 8 kHz to 16 kHz, making it much easier to remove it from the audio via filtering. The audio path includes a six pole Chebychev low pass filter with a cut-off frequency of 3 KHz and a TPA2001D1 One Watt Filter-less Mono Class-D Audio Power Amplifier. A five LED 'bar graph' level indicator is included, along with 'increase volume' and 'decrease volume' push buttons. This card can be powered by three 1.2 volt NiCad batteries or 3 AA alkaline batteries. Battery voltage is monitored using the 10 Bit ADC built into the MSP430F2232. A blue 'heartbeat' LED, an orange 'packet error' LED, and a red 'low battery' LED are also included.

Included on both the transmitter and receiver cards is a 2 wire UART interface, intended to drive a separate 4 line by 20 character LCD display card. This display provides status information such as RSSI (Received Signal Strength), and the number of packet errors and lost packets that have occurred.

Refer to schematic, Figure 13.

#### Software Description – Single Tx mode

#### Transmitter

Audio is sampled via the MSP430F2232's 10 bit ADC at an 8 kHz rate (i.e., every 125 usec). Every 36 ADC samples (4.5 msec), the 36 ten bit audio samples are packed into 45 bytes, which, together with a status byte, are transmitted to the receiver. One bit of the 'status' byte is used to signal to the receiver to sound the 'locate' tone. The 'locate' tone is described in the 'Receiver' section, below. Since it takes more than 125 usec to pack the data, two buffers are required; the 'active' buffer is used to hold sampled ADC values in 'real time', while TX buffer data is being built from the 'inactive' buffer.

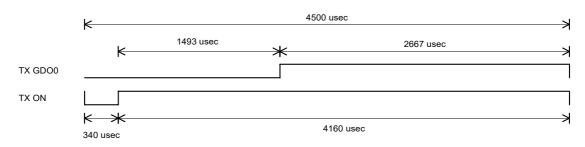

Refer to Figure 3, below. 'GDO0' is an internally generated signal available at pin 2 of the CC1150. GDO0 goes high following the transmission of the SYNC bytes, and goes low

following the transmission of the CRC bytes. 'TX ON' is generated in software. 'TX ON' goes high when the transmitter is enabled and goes low simultaneously with GDO0.

#### Figure 3 – Transmitter Timing (150 kbps, FEC disabled)

Note that there is a 1493 usec delay from the time that the transmitter is turned on until the SYNC word has been sent; approximately 810 usec of this is taken up by the PLL calibration procedure, which is performed prior to every transmission. The preamble and sync bytes take 427 usec to transmit.

#### Receiver

Data received from the transmitter is 'played back' at the same rate at which it was sampled, i.e., 8 kHz. A data packet is expected every 4.5 milliseconds, which must be unpacked (five bytes into four 10 bit values). The MSP430F2232's 'Timer A' is used to convert 10 bit audio samples to PWM (Pulse Width Modulated) signals. Again, it takes much longer than 125 usec to 'unpack' the audio data, so two buffers are required. The receiver must also recognize when the 'locate' button is activated on the Monitor, and substitute a 444 Hz tone pattern for the ADC sample data. A frequency of 444.4 Hz was chosen because an integer number of cycles (2) fit into 36 samples.

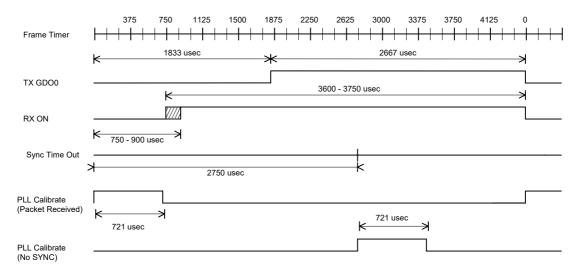

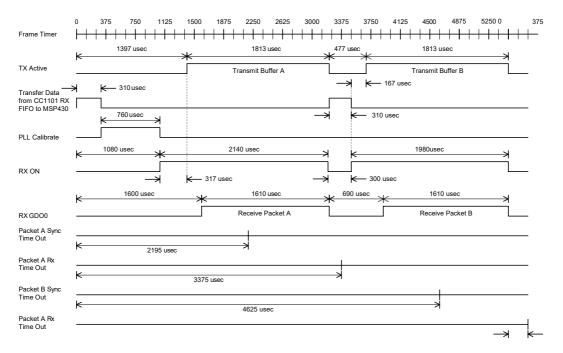

#### Figure 4 – Receiver Timing ('Paired' Mode, 150 kbps)

The receiver operates in two modes: 'paired' and 'waiting for beacon'. In 'waiting for beacon' mode, the receiver is tuned to the first entry in the 'frequency hopping' table, the PLL calibrated (using automatic calibration mode), and turned on for a maximum period of 125 msec. Once the beacon is detected, the mode is changed to 'paired'. If the beacon is not detected in the 125 msec period, the PLL is recalibrated and the process repeated indefinitely.

In 'paired' mode, Timer B of the MSP430F2232 is used as a 'frame timer'. It is reset and started once a packet is received (GDO0 goes low), and will automatically reset after 4500 usec. The receiver is tuned to the next channel and PLL calibration initiated immediately following the reception of a 'good' packet. If a packet is successfully received, the data is unpacked and transferred to the inactive audio data buffer. If a packet is 'lost' or contains errors, the inactive buffer is marked as 'unusable' - essentially, all values in the buffer are replaced with 'zeros' during playback. This will mute the audio for 4.5 msec.

In the diagram above, note that the receiver will not be turned on until calibration is complete, and until the frame timer has reached a value of between 750 and 900 usec (relative to the end of the last successfully received packet). If SYNC word is not detected once the frame timer has reached a value of 2750 usec, the receiver is turned off, any data in the receiver's FIFO buffer flushed, the receiver is tuned to the next channel, and PLL calibration initiated.

#### Software Description – Double Tx mode

#### Transmitter

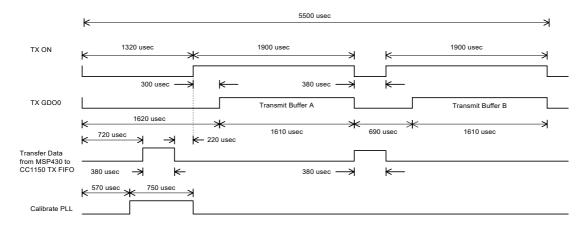

As in single TX mode, audio is sampled via the MSP430F2232's 10 bit ADC at an 8 kHz rate (i.e., every 125 usec). Every 44 ADC samples (5.5 msec), the 44 ten bit audio samples are packed into 55 bytes, and moved into a TX buffer, e.g. Tx Buffer A. The transmitter is tuned to the current channel, and data is transmitted from both Tx Buffer A and Tx Buffer B. The 'current channel' index is then incremented, so that the next transmission will take place on a different frequency. During transmission, ADC samples will continue to be collected and placed in Tx Buffer B. Thus, every ADC sample will be transmitted twice, at two different frequencies.

#### Figure 5 – Transmitter Timing, (300 kbps, double TX)

Note that 380 usec is required to transfer data form the MSP430s RAM into the CC1150s TX FIFO. However, this time is 'hidden', in that the transfer is done simultaneously with PLL calibration (750 usec).

#### Receiver

Two data packets are expected every 5.5 milliseconds. The first packet to be received in the 5.5 millisecond time slot ('Packet A') is the second transmission of the previous ADC samples (i.e. Transmit Buffer A). The second packet is the first transmission of the current ADC samples (i.e. Transmit Buffer B). Once both transmissions of a packet are received, a decision is made as to which transmission is to be used for playback, based upon the status of each packet. A packet is not considered to be 'lost' unless both transmissions of the packet were lost (no SYNC word was detected). Similarly, a packet error is considered to have

occurred only if both transmissions of the packet contained errors or if only one packet was received and it contained a packet error. Packet errors include CRC (Cyclic Redundancy Check), and address or packet length mismatch.

#### Figure 6 – Receiver Timing, (300 kbps, double TX)

The timing diagram (above) reveals several points of interest. Note that 'TX Active' in this diagram differs from 'TX GDO0' in the previous figure because it includes both the SYNC and Preamble fields (8 bytes in total). Since the receiver must be active during both the SYNC and Preamble fields, this more accurately represents the periods of time during which the receiver must be on. It takes approximately 310 usec to transfer data to and from the MSP430F2232 and the CC1101\CC150 FIFO; it takes approximately 760 usec to calibrate the frequency synthesizer of the CC1101.

As in single TX mode, the receiver must also recognize when the 'locate' button is activated on the Monitor, and substitute a 363 Hz tone pattern for the ADC sample data. A frequency of 363 Hz was chosen because an integer number of cycles (2) fit into 44 samples.

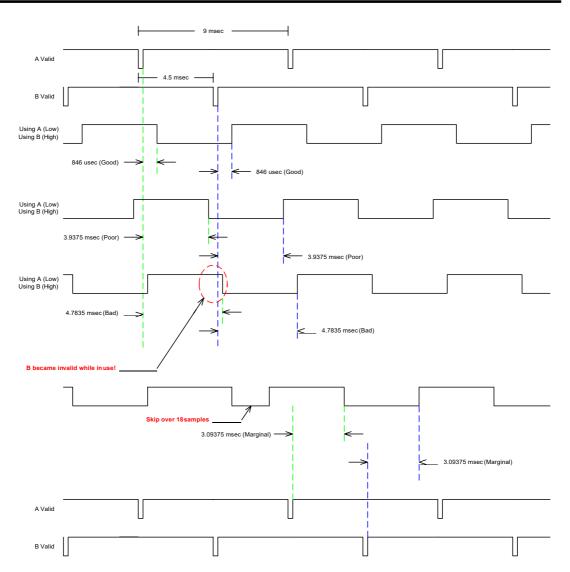

#### Synchronization

An additional complication can arise due to the fact that the oscillators on the transmitter and receiver are not at precisely the same frequency. This causes the received packet to occasionally arrive too soon or too late; when the software detects that this will happen, a few of the samples (18) are skipped in order to resynchronize the receiver to the transmitter. See Figure 5. In this figure, 'A Valid' indicates that data in the 'A' buffer is valid; similarly, 'B Valid' indicates that data in the 'B' buffer is valid. A buffer becomes 'invalid' while data is being moved from the RX buffer and unpacked into Buffer A or buffer B – about 200 usec. 'Using A' and 'Using B' indicate that the receiver is currently 'playing back' data in the A or B buffers, respectively. In the first case ('Good'), buffer A becomes valid 846 usec before it is used. In the second case ('Poor'), the receiver's oscillator has drifted relative to the transmitter's, such that buffer A is received 3.9375 msec before it is used. In the third case ('Bad'), buffer A is received 4.7835 msec before it is used. Notice that buffer B now becomes invalid while it is being used; a 'Bad' situation indeed. To correct for this, the software will 'skip ahead' 18 samples to reposition the 'valid' and 'using' timings.

#### Figure 7 – Receiver Playback Timing

If the status byte indicates that the user has depressed the 'locate' button, the receiver's audio buffer is filled with values that generate a 444 Hz tone. Additional, all segments of the LED light bar are flashed at 250 msec rate.

#### FCC 15.247 Compliance

Basically, there are two approaches to achieving FCC compliance in the 902 – 928 MHz ISM band:

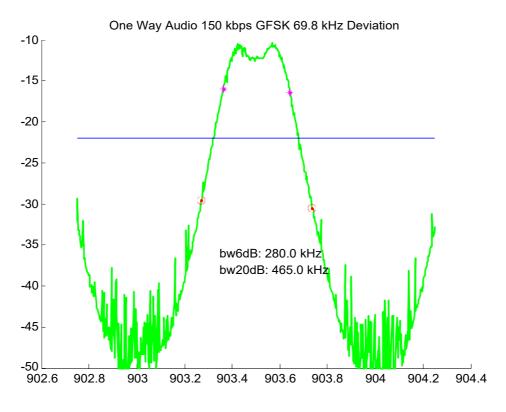

Frequency hopping system: If the 6 dB bandwidth exceeds 250kHz, at least 25 channels must be used, having a duration of less then 0.4 seconds in a 10 second period, and a maximum output power of 250 mW. The maximum 20 dB bandwidth is 500 kHz. Practically (with the CC1101, CC1150, and CC1110), this can be achieved using GFSK modulation at a data rate of 175 kbps or less and a deviation of 76.2 kHz or less. For this application, a data rate of 150 kbps and a deviation of 69.8 kHz are adequate. Refer to the spectrum plot, Figure 8.

Figure 8 – RF Spectrum using GFSK modulation at 150 kbps, 69.8 kHz deviation

Note that for the spectrum plot above, the CC1150 TX card was set to transmit at frequencies both 1 MHz below (channel 0, 902.5 MHZ) and 1 MHz above (channel 8, 904.5 MHz) the analyzer's center frequency (channel 4, 903.5 MHz). This results in 'spikes' in the 'tails' of the distribution.

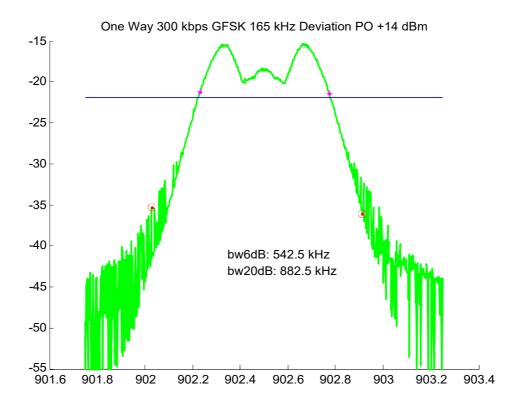

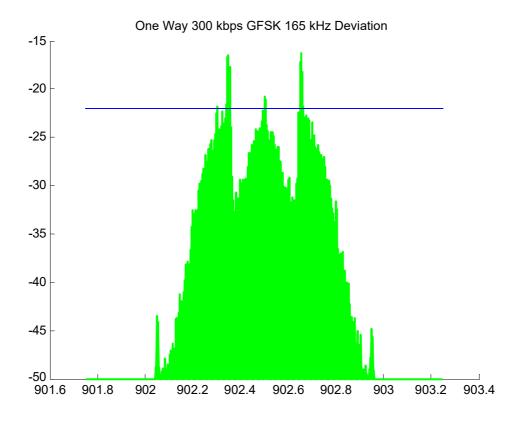

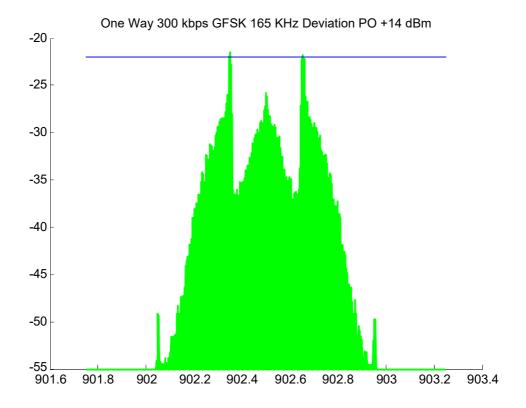

2) Digital modulation system: Such systems must have a minimum 6 dB bandwidth of 500 kHz, and a maximum output power of 1 W. An additional requirement is that the peak power spectral density shall not exceed 8 dBm in any 3 kHz band. With the CC1101, CC1150, and CC1110, this can be achieved by using GFSK modulation at a data rate of 300 kbps and a deviation setting of 165 kHz. Refer to the spectrum plot, Figure 9.

#### Figure 9 – RF Spectrum using GFSK modulation at 300 kbps, 165 kHz deviation

When frequency agility ('double TX') is implemented, a minimum data rate of 300 kbps is required. To meet FCC 15.247 specifications, the only choice is to qualify as a 'digital modulation system', using GFSK modulation as shown above.

Recall the FCC restriction that "The peak power spectral density in any 3 kHz bandwidth shall not exceed +8 dBm". With the power output set to the full +20 dBm, this restriction is clearly violated. See Figure 10.

Note: In these plots, the vertical scale (dBm) needs an explanation. A 30 dB attenuator was used at the input of the spectrum analyzer, to avoid overloading the mixer. The blue line (-22 dBm) therefore represent a +8 dBm signal, the FCC limit for a spread spectrum device. The horizontal scale is in MHz.

## Figure 10 – RF Spectrum using GFSK modulation at 300 kbps, 165 kHz deviation +20 dBm Output Power Level

By reducing the output power to +14 dBm, we can meet the FCC restriction:

### Figure 11 – RF Spectrum using GFSK modulation at 300 kbps, 165 kHz deviation +14 dBm Output Power Level

If frequency agility is not employed ('single TX'), a data rate of 150 kbps is adequate, and the frequency hopping table must include a minimum of 25 channels. This will allow the full output power (+20 dBm) to be used, and the range substantially increased.

#### **Frequency Hopping**

Although frequency hopping is implemented in both 'single Tx' and 'double Tx' modes, the number of channels in the frequency hopping table differs. In 'single Tx' mode, the hopping table contains 25 channels, spaced 1 MHz apart, and arranged in a pseudo random sequence. In 'double Tx mode, frequency hopping is not required, but is done none the less, to reduce the likelihood of interference from other devices. A set of four channels (frequencies) is used, on a rotating basis (every transmission is on a different channel). As written, the four channels used are 0, 20, 40, and 60. The base frequency is set to 902.5 MHz and the channel spacing to 250 kHz, so channels 0, 20, 40, and 60 correspond to frequencies of 902.5, 907.5, 912.5, and 917.5 MHz.

When first turned on and after 10 consecutive packets have been lost, the receiver goes into a 'waiting for beacon' mode, continuously listening on the first channel in the 'frequency hopping table' (channel 20 in 'single Tx' mode, channel 0 in 'double Tx' mode).

#### Specifications

Frequency Range: 868 to 928 MHz, 256 channels Transmitter Power: +20 dBm (100 mW) maximum Data Rate: 150 kbps, FEC disabled, frequency diversity disabled

300 kbps, FEC enabled, frequency diversity disabled 300 kbps, FEC disabled, frequency diversity enabled

Modulation:

150 kbps: GFSK (Gaussian Frequency Shift Keying) 300 kbps: GFSK (Gaussian Frequency Shift Keying) Audio Sample Rate: 8 kHz (12 kHz possible) ADC/PWM resolution: 10 Power Consumption – Receiver Card (excluding LEDs):

Searching for Beacon – 41 mA (135 mW)

• "Paired' – 33 mA (109 mW)

Power Consumption – Receiver Card (including LEDs):

- Searching for Beacon 61 mA (201 mW)

- "Paired' 50 mA (165 mW)

- Expected Battery Life (3 Alkaline 'AA' cells): Approximately 32 hours

Note: The green 'power on' LED and orange 'Lost Packet' LED consume approximately 8 mA each; the blue 'Heartbeat' LED has an average power consumption of approximately 4 mA.

Power Consumption – Transmitter Card

- Excluding LEDs 110 mA (550 mW, Vsupply = 5.0 Volts)

- Including LEDs 123 mA (615 mW, Vsupply = 5.0 Volts)

- Expected Battery Life (3 Alkaline 'AA' cells): Approximately 12 hours

#### Features

- Frequency Hopping: 25 channels pseudo randomly sequenced channels in 'single Tx' mode, 4 channels in 'double Tx' mode.

- Automatic Gain Control (Monitor/Transmitter): A software controlled AGC is implemented. The microphone preamplifier has four discrete gain settings of approximately 10, 20, 40, and 80 (20, 26, 32, and 38 dB), selectable via two control lines. The VGA gain is increased by 6 dB (2 times) whenever the MSP430's ADC reads less than 180 codes (approximately 440 millivolts peak). The VGA gain is decreased by 6 dB (.5 times) whenever the MSP430's ADC reads more than 450 codes (approximately 1098 millivolts peak).

- Manual Volume Control (Receiver): The receiver card uses a Texas Instruments TPA2001 filter-less class-D audio power amplifier, which features programmable gains of 6, 12, 18, and 23.5 dB. Gain is controlled via two push button switches ('volume up' and 'volume down'), located on the receiver card.

- Sound Level Indicator (Receiver): Five LEDs are arranged to serve as a level indicator. Each LED (segment) will light for approximately 45 milliseconds (programmable) when the received ADC codes exceed the following values:

Segment 1: 600 (approximately 215 millivoltspeak) Segment 2: 675 (approximately 398 millivoltspeak) Segment 3: 750 (approximately 581 millivoltspeak) Segment 4: 825 (approximately 764 millivoltspeak) Segment 5: 900 (approximately 947 millivoltspeak)

• Locate: Two push buttons ('Locate' and 'Cancel Locate') are located on the Monitor card. When activated, the 'locate' function will sound a 444 Hz tone at the receiver and blink all segments of the sound level indicator, at a 250 millisecond rate.

#### **Design Alternatives**

The design described herein was optimized for low receiver power consumption and telephone quality audio. Other optimizations are, of course, possible. For example, by changing the MSP430s crystal frequency from 16.384 MHz to 12.288 MHz and the cut-off

frequency of the anti-aliasing (Transmitter) and PWM (Receiver) filters from 3000 Hz to 4500 Hz, it is possible to increase the audio bandwidth to 4500 Hz and the sample rate to 12 kHz. One design goal that was particularly difficult to achieve was the ability to walk with the receiver in hand without impacting audio quality. The use of FEC (Forward Error Correction) somewhat improves 'walking performance' by reducing the number of CRC errors. However, FEC is a 'double rate' code – that is, redundant information is sent such that the packet can be reconstructed at the receiving end. This requires that the effective data rate be increased from 150 kbps to 300 kbps, and the receiver's sensitivity. As a result, although the number of CRC errors is reduced, the number of lost packets (SYNC not detected, address or length miss-match) increases.

One observation is that errors generally occur in bursts and primarily on only one channel. This led to the development of 'double TX' software, wherein each packet is sent twice, at a different frequency, a technique labelled 'frequency diversity' in some literature. This technique has shown significant improvements to both range and 'walking performance'. However, due to FCC restrictions, the output power in this mode must be reduced to approximately +14 dBm.

#### Conclusion

This document describes a set of cards and software that demonstrate telephone quality audio over a 900 MHz one way link, using the CC1101, CC1150, and MSP430F2232. Several software alternatives are discussed, including a single transmission of audio samples ('single Tx') and frequency diversity ('double Tx'; each ADC sample is transmitted twice, at different frequencies).

Figure 12 – Transmitter

### References

#### General references

- [1] CC1101 Data Sheet (Rev. B) (<u>swrs061b.pdf</u>)

- [2] CC1150 Single-Chip Low Cost Low Power RF-Transmitter (<u>swrs037.pdf</u>)

- [3] Design Note DN006 'CC11xx Settings for FCC 15.247 Solutions' (swra123a.pdf)

- [4] MSP430F2232 Mixed Signal Microcontroller (Rev. B) (<u>slas504b.pdf</u>)

- [5] BFP450 NPN Silicon RF Transistor(BFP450)

- [6] BCR400W Active Bias Controller (BCR400W)

- [7] BGA2011 900 MHz MMIC Low Noise Amplifier (<u>BGA2011</u>)

- [8] TPA2001 One Watt Filter-less Mono Class D Amplifier(<u>TPA2001</u>)

- [9] LMV324 Low-Voltage Rail-to-Rail Output Operational Amplifier (LMV324)

- [10] TPS73033 Low Noise High PSRR RF Low Drop Out Regulator (TPS73033)

- [11] TPS76333 Low Power Low Dropout Linear Regulator (TPS76333)

### **Document History**

| Revision | Date          | Description/Changes |

|----------|---------------|---------------------|

| SWRA237A | 13 Nov 2008   | Initial release     |

| SWRA237B | 23 March 2009 | Include CC1100E     |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated