# **ERRATA NOTES**

# CC2550

# **Table Of Contents**

| 1 | PLL LOCK DETECTOR OUTPUT                          | 2 |

|---|---------------------------------------------------|---|

| 2 | SPI READ SYNCHRONIZATION ISSUE                    | 3 |

| 3 | EXTRA BYTE TRANSMITTED IN TX                      | 6 |

| 4 | 2-FSK MODULATION DATA RATE IS LIMITED TO 250 KBPS | 7 |

| 5 | DOCUMENT HISTORY                                  | Q |

# 1 PLL Lock Detector Output

## 1.1 Description and Reason for the Problem

The PLL lock detector output is not 100% reliable and might toggle even if the PLL is in lock. The PLL is in lock if the lock detector output has a positive transition or is constantly logic high. The PLL is not in lock if the lock detector output is constantly logic low. It is not recommended to check for PLL lock by reading PKTSTATUS[0] with IOCFG0.GDO0\_CFG=0x0A.

### 1.2 Suggested Workaround

PLL lock can be checked reliably as follows:

1) Program register IOCFG0.GDO0\_CFG=0x0A and use the lock detector output available on the GDO0 pin as an interrupt for the MCU. A positive transition on the GDO0 pin means that the PLL is in lock. It is important to disable for interrupt when waking the chip from SLEEP state as the wake-up might cause the GDO0 pin to toggle when it is programmed to output the lock detector.

O

2) Read register FSCAL1. The PLL is in lock if the register content is different from 0x3F.

#### 1.3 Batches Affected

This errata note applies to all batches and revisions of the chip.

Page 2 of 8

# 2 SPI Read Synchronization Issue

A bug affecting the synchronization mechanism between the SPI clock domain (using a user supplied SCLK) and the internal 26MHz clock domain (XCLK in this document) will sometimes result in incorrect read values for register fields that are continuously updated. The frequency with which this occurs is very low and guidelines for application design to avoid this issue are given in this chapter. The issue does **not** affect writes to registers or the TX FIFO at any time.

### 2.1 Symptoms

When reading multi-bit register fields that are updated by the radio hardware such as the MARCSTATE or TXBYTES registers over the SPI interface, occasionally nonsensical or erroneous values will be read.

For example, in an application that sends packets longer than the 64 byte TX FIFO, the TX FIFO must be topped up with additional data during packet transmission. Assuming this is done by initially transferring 64 bytes to the TX FIFO, starting transmission, and then continuously polling TXBYTES to see when space for additional bytes is available, and then transferring the required number of bytes until the end of the packet. In this case the expected sequence of values read from TXBYTES would be:

```

64, 64, ..., 63, (write byte), 64, 64, ..., 63, (write byte), 64, ...

```

Due to the SPI synchronization issue the following might (infrequently) be seen instead:

The erroneous value read is highlighted in red. The register read is changing from the value 64 (01000000b) to the value 63 (00111111b) on the XCLK clock at the same time that its value is latched into the SPI output shift register on the SCLK clock. If the two clock edges occur sufficiently close in time, the improper synchronization mechanism will latch some bit values from the previous register value and some bits from the next register value, resulting in the erroneous value 89 (01011001b).

### 2.2 Description

During an SPI read transaction, the SPI output register latches the read value on the last falling edge of SCLK during an SPI address byte. For a burst read operation, subsequent register values are latched on the falling edge of SCLK in the last bit of each previous data byte.

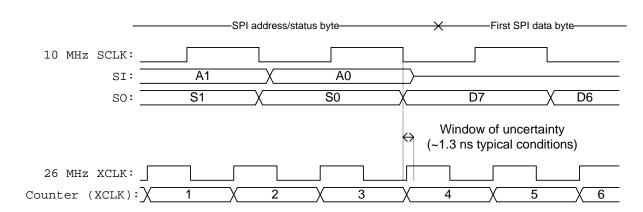

Due to this synchronization issue, if the register being read changes value (synchronously with XCLK) during a certain period of time after this falling edge of SCLK then some of the bits in the read value will come from the previous value and some from the next value. This so-called window of uncertainty is about 1.3 ns for typical conditions and increases to about 2.0 ns for worst-case conditions (1.8 V VDD, 85 °C).

Figure 1: Window of Uncertainty (drawing not to scale)

Figure 1 shows a timing diagram of an SPI read that fails when reading a fictitious counter being updated internally each **XCLK**. Since the counter update from value 3 (011b) to 4 (100b) within the window of uncertainty, the read value could be any one of 0-7 (000b, 001b, 010b, 011b, 100b, 101b, 110b, 111b) depending on exactly when the positive edge of **XCLK** falls within the window of uncertainty.

### 2.2.1 What Kinds of Register Fields Are Affected?

This issue does **not** affect:

- Reading of the static configuration registers (registers 0x00-0x2F)

- Reading static status registers (PARTNUM, VERSION) or FS calibration (VCO\_VC\_DAC)

- Single-bit fields (all fields in PKTSTATUS, TXBYTES.TXFIFO\_UNDERFLOW)

This issue **does** affect:

- The SPI status byte (shifted out while the host MCU supplies the address byte) fields STATE and FIFO\_BYTES\_AVAILABLE.

- Reading MARCSTATE at any other time than when the device is inactive (IDLE).

- Reading TXBYTES while transmitting a packet.

#### 2.2.2 How Often Does the Issue Corrupt Read Values?

The probability of reading a corrupt value is given by the frequency with which the read value changes,  $f_c$ , and the length of window of uncertainty,  $T_{WU}$  (typically 1.3 ns). The probability that the two events overlap, and thus that the read value is potentially corrupted, is given by:

$$P_{corrupt} = \frac{T_{WU}}{T_c} = T_{WU} f_c$$

In the example given in section 2.1, the probability of any single read from TXBYTES being corrupt, assuming the maximum datarate is used, is approximately  $P_{corrupt} = T_{WU} \, f_c = 1.3 \, \mathrm{ns} \cdot \left(500 \, \mathrm{kbps} \, / \, 8b\right) \approx 80 \, \mathrm{ppm}$  or less than once every 10000 reads. In many situations the underlying received packet failure rate in the communication system is so much higher that any packet transmission/reception failure attributable to the issue described here will be negligible.

### 2.3 Suggested Workaround

In a typical radio system a packet error rate of at least 1 % should be tolerated in order to ensure robustness. In light of this, the negligible contribution to the number of packets lost due to, for example, occasionally reading incorrect FIFO byte count values or the wrong radio state from MARCSTATE, can probably be ignored in most applications. However, care should be taken to ensure that reading an incorrect value does not jeopardize an application. Examples of commonsense things to do include:

- For packets longer than the TX FIFO, configure the device to signal on a GDO pin when there is enough room to fill up with a new block of data (using the TXFIFO\_THR threshold). If polling TXBYTES is necessary due to pin constraints, read TXBYTES repeatedly until the same value is returned twice in succession such a value can always be trusted.

- Do not rely on the internal radio state machine through transient states (e.g. CALIBRATE SETTLING TX IDLE). It is, however, perfectly safe to poll for the end of transmission by waiting for MARCSTATE=IDLE.

- Avoid using the SPI status byte STATE and FIFO\_BYTES\_AVAILABLE fields during packet transmission.

If it is important to **ensure** that read values are not corrupted, reading of one of the affected registers should be done repeatedly until the same value is read twice in succession. If the rate at which the register is read is guaranteed to be at least twice as fast as the expected register update rate, then an upper bound on the number of required reads is four and the average number of reads slightly more than two.

The same method can be used to ensure that the SPI status byte fields that provide simplified radio FSM state and saturated FIFO byte count are correct. This only makes sense when polling the status byte with SNOP as the address.

#### 2.4 Batches Affected

This errata note applies to all batches and revisions of the chip.

# 3 Extra Byte Transmitted in TX

### 3.1 Description and Reason for the Problem

If one abort a transmission (exits TX mode) during the transmission of the first half of any byte, there will be a repetition of the first byte of the next transmission. This issues is caused by a state machine controlling the mod\_rd\_data signal in the modulator. This signal asserts at the start of transmission of each full byte, then deasserts after half the byte has been transmitted. If transmittion is aborted after a byte has started but before half the byte is transmitted this signal remains asserted and the first byte in the next transmission will be repeated.

### 3.2 Suggested Workaround

As long as the packet handling features of the CC2500 are used, this will not be a problem since the chip will always exit TX mode after the transmission of the last bit in the last byte of the packet. If, however, one disables the packet handling features (MDMCFG2.SYNC\_MODE=0) and wants to exit TX mode manually by strobing IDLE, one should make sure that the IDLE strobe is being issued after clocking out 12 dummy bits (8 dummy bits are necessary due to the TX latency, but since this would mean that transmission is aborted within the first half of a byte, 4 extra bits are added).

#### 3.3 Batches Affected

This errata note applies to all batches and revisions of the chip.

# 4 2-FSK Modulation Data Rate is Limited to 250 kbps

## 4.1 Description and Reason for the Problem

The CC2550 can not modulate with 2-FSK at 500 kbps. Maximum supported rate is 250 kbps.

# 4.2 Suggested Workaround

Use 2-FSK modulation at 250 kbps or change device to CC2500 which supports 500 kbps 2-FSK modulation.

### 4.3 Batches Affected

This errata note applies to all batches and revisions of the chip.

# 5 Document History

| Revision | Date       | Description/Changes                                                                                                                                                                                                                                                                                           |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWRZ011C | 2013-02-20 | Added Chapter 4 restriction on 2-FSK data rate                                                                                                                                                                                                                                                                |

| SWRZ011B | 2007-11-29 | Chapter 3.2: "bytes" changed to "bits"                                                                                                                                                                                                                                                                        |

| SWRZ011A | 2007-10-18 | Removed chapter on reduced link performance at certain frequencies. Reduced link performance is related to the CC2500 receiver and not the CC2500 transmitter.  Added Chapter 3 with info related to the transmission of an extra byte in TX. Chapter 1 is updated with more detailed workaround information. |

| 1.0      | 2006-05-22 | First edition                                                                                                                                                                                                                                                                                                 |

## **TEXAS INSTRUMENTS NORWAY**

Tel. +47-22958544

Fax +47-22958546

www.ti.com

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID <u>www.ti-rfid.com</u>

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>