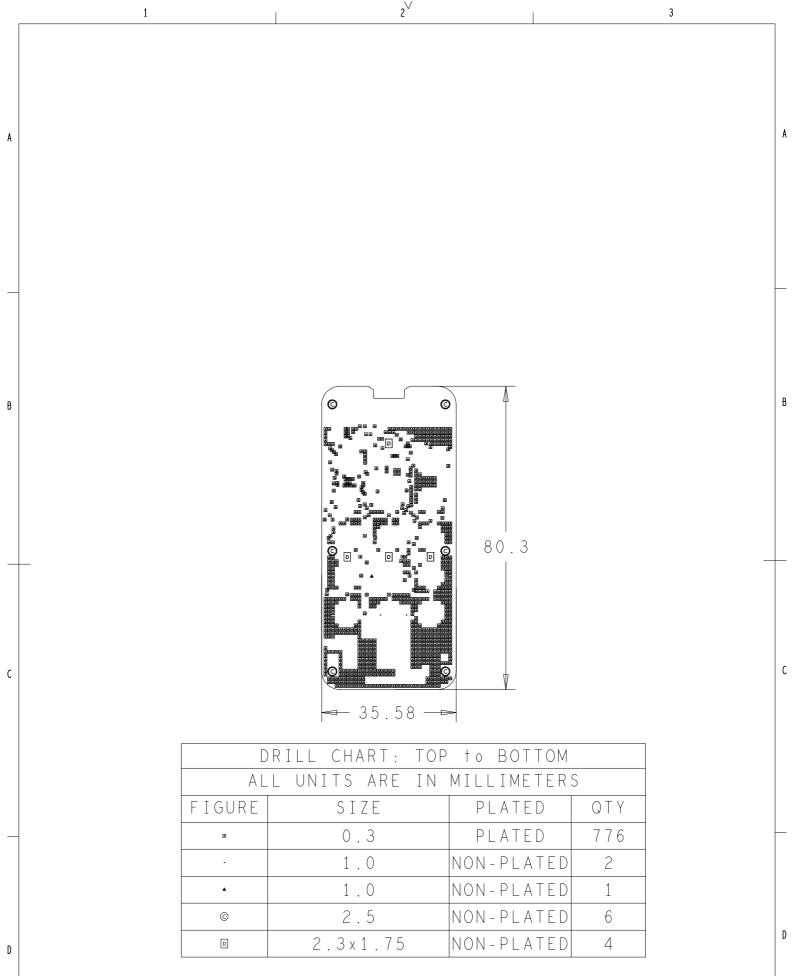

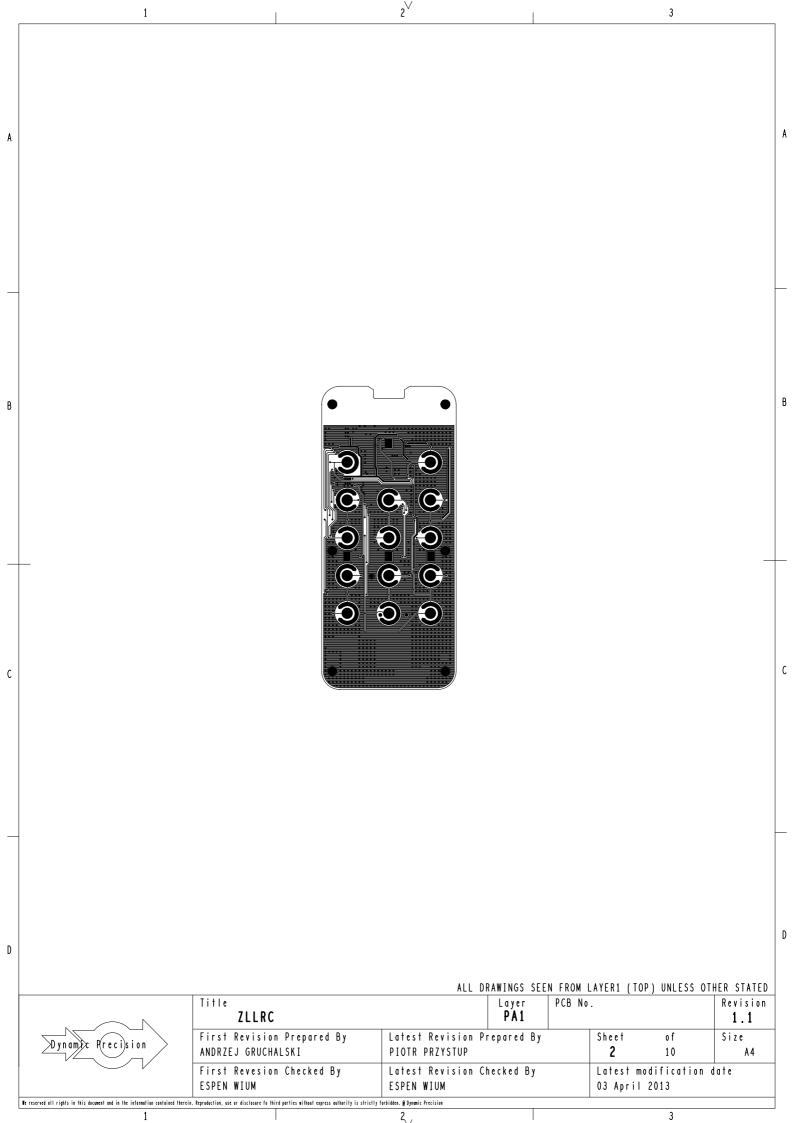

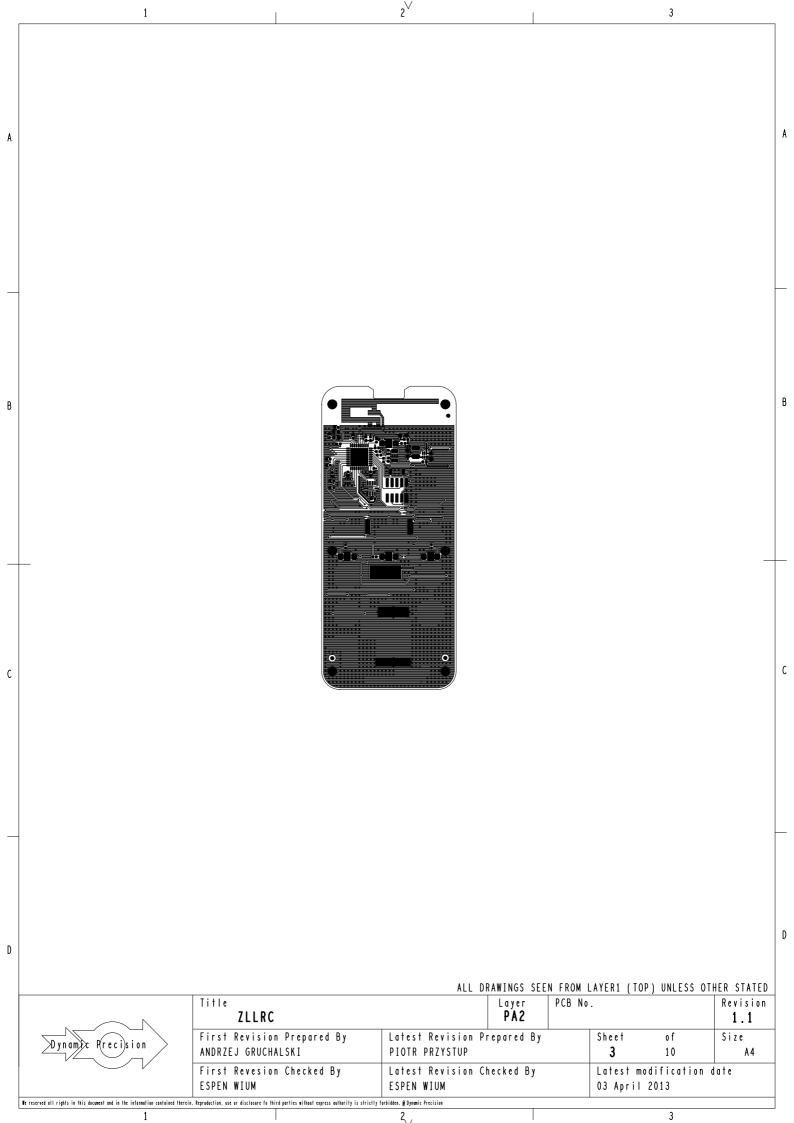

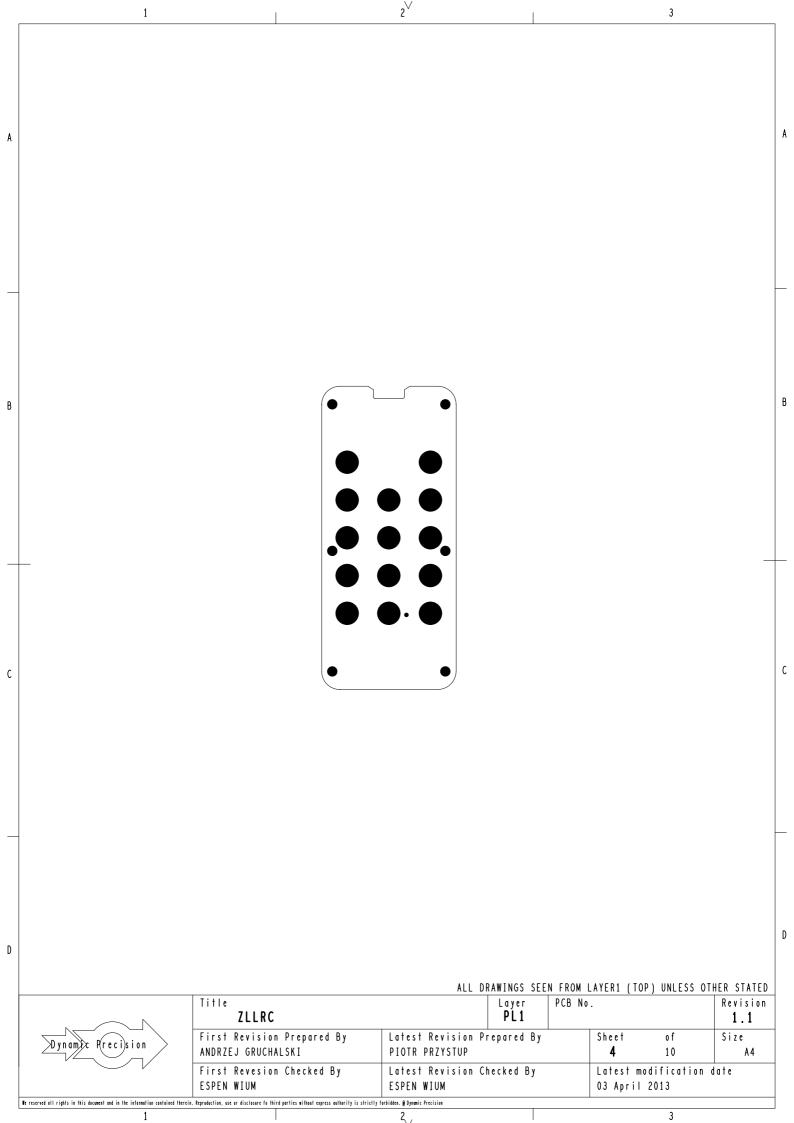

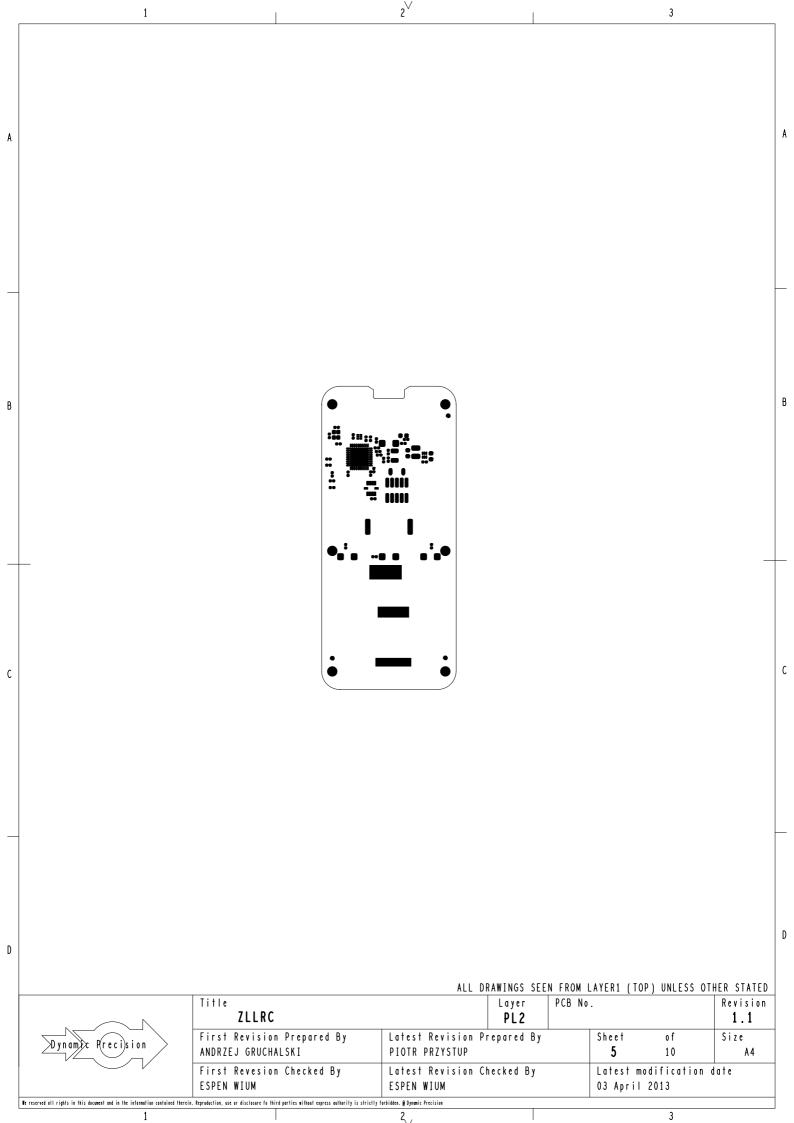

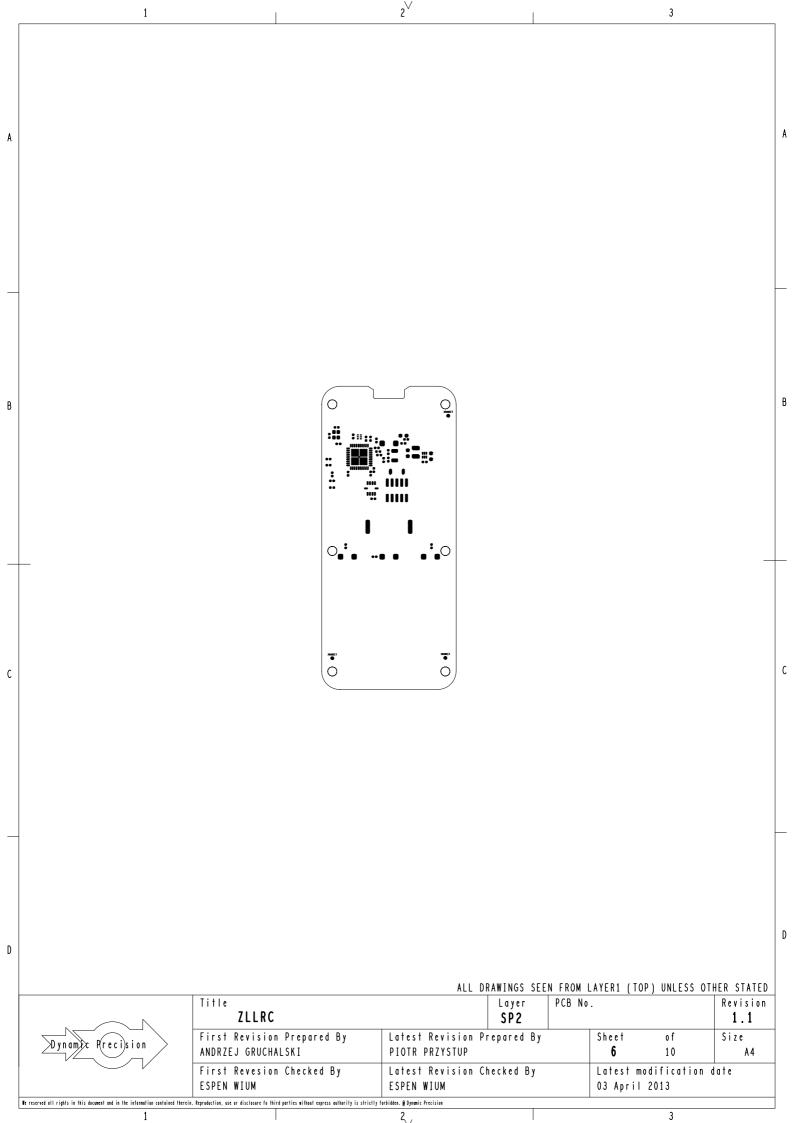

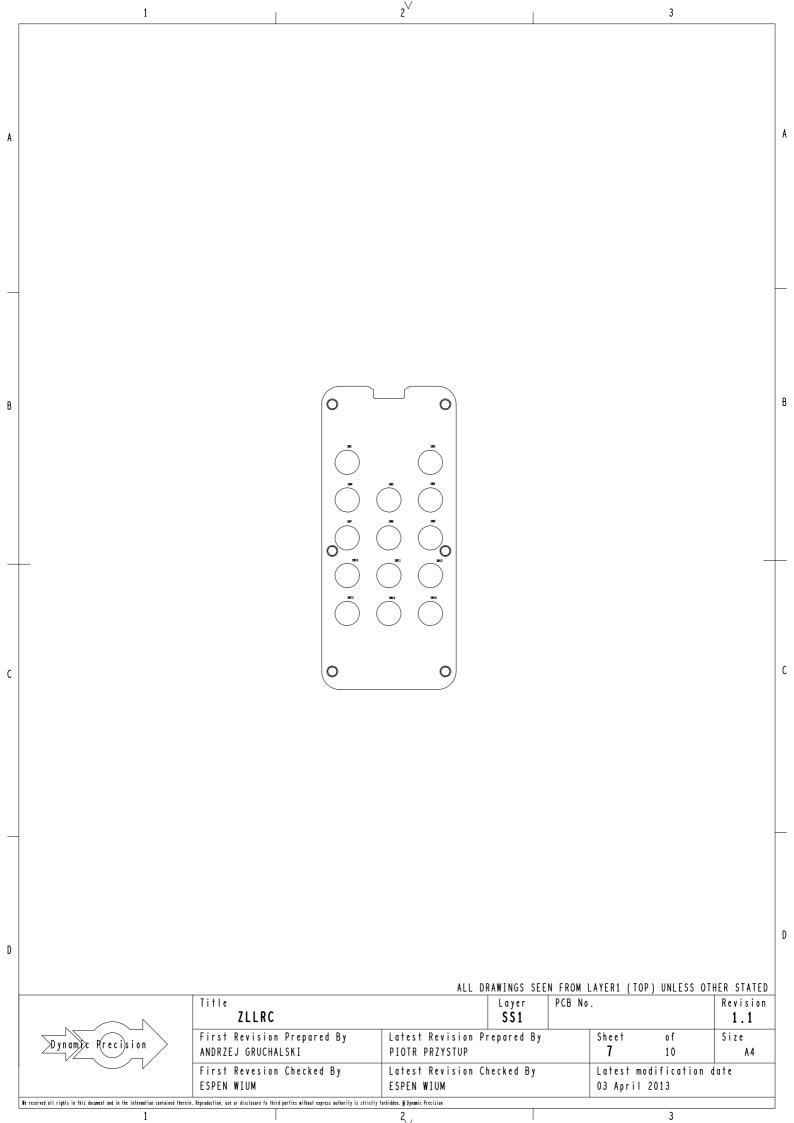

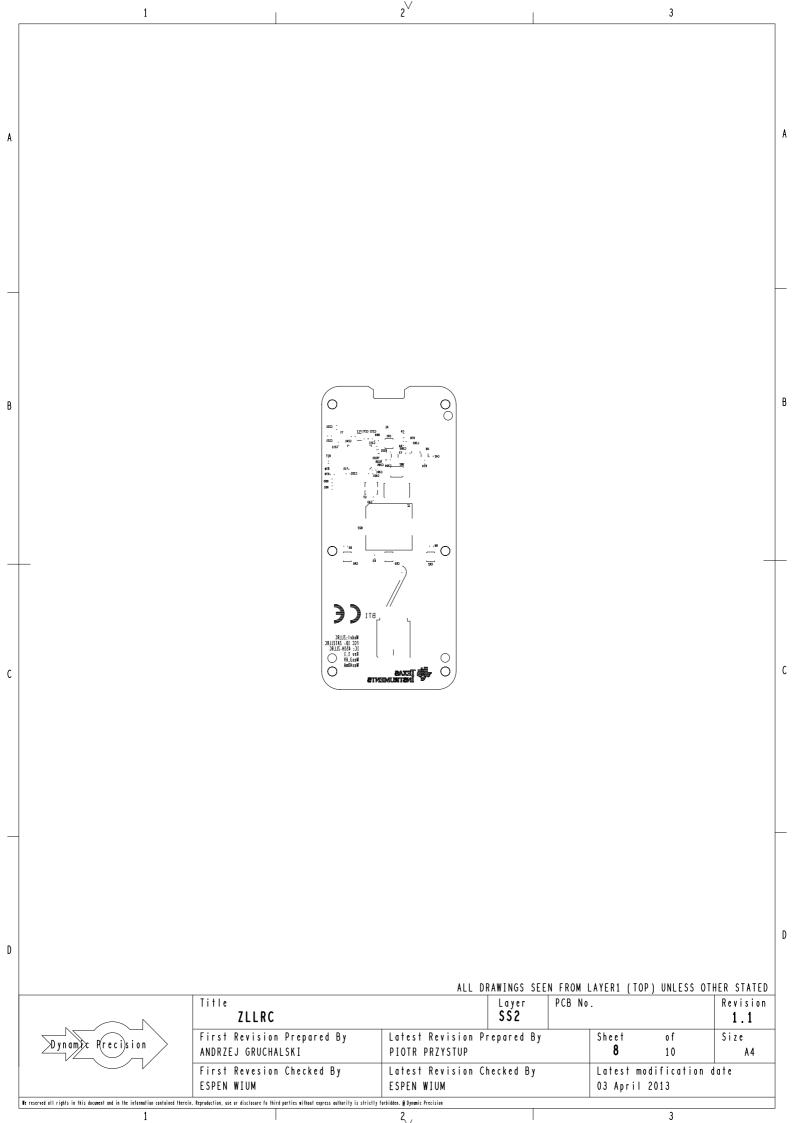

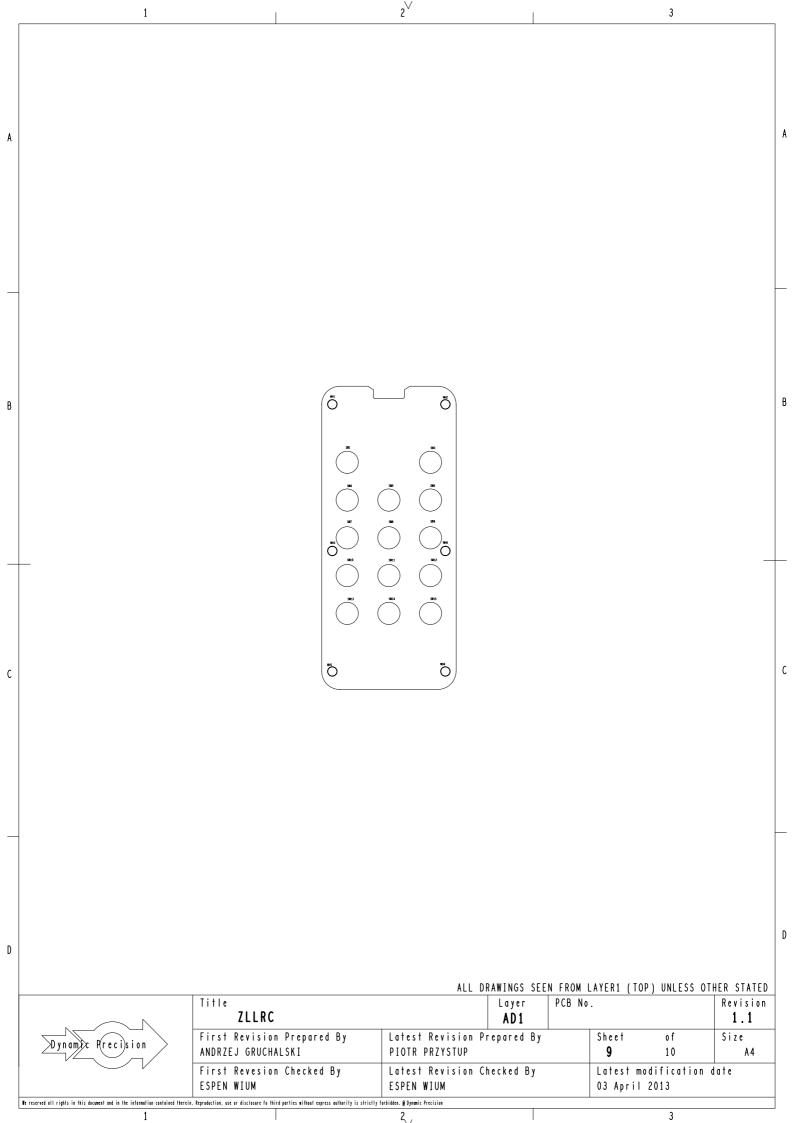

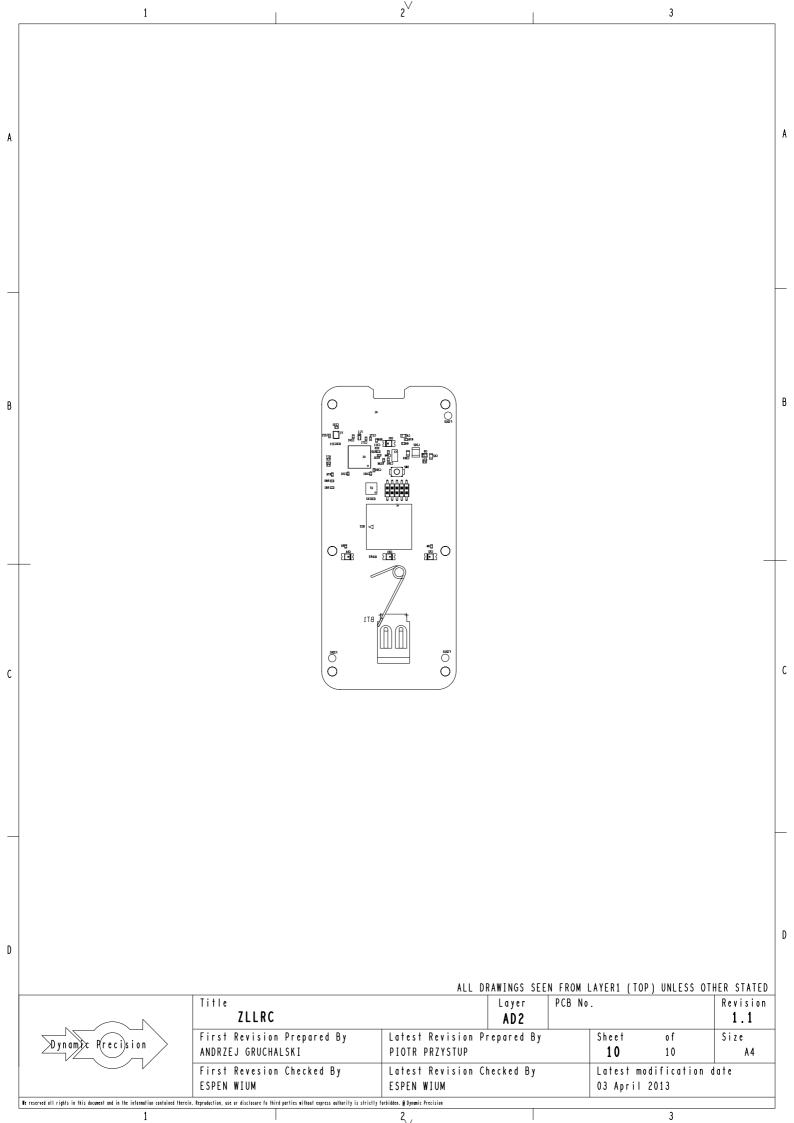

## ALL DRAWINGS SEEN FROM LAYER1 (TOP) UNLESS OTHER STATED

| ALL DRAWINGS SEEN FROM LATERI (TOP) UNLESS DIFFER STATED                                                                                |                                                  |                                        |             |                           |          |                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|-------------|---------------------------|----------|------------------------|

|                                                                                                                                         | Title<br>ZLLRC                                   |                                        | ayer<br>DRM | PCB No.                   |          | Revision<br><b>1.1</b> |

|                                                                                                                                         | First Revision Prepared By<br>ANDRZEJ GRUCHALSKI | Latest Revision Prep<br>PIOTR PRZYSTUP | ared By     | Sheet<br>1                | of<br>10 | Size<br>A4             |

|                                                                                                                                         | First Revesion Checked By<br>ESPEN WIUM          | Latest Revision Chec<br>ESPEN WIUM     | ked By      | Latest mod<br>03 April 21 |          | ate                    |

| in contained Herein, Agreduction, use er disclosure fo Ihird parties nithout express outherity is strictly forbides. & Dynaic Precision |                                                  |                                        |             |                           |          |                        |

ζ,

≫Dynam)≿c P(rec

We reserved all rights in this document and in the information

3

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated