# TI Designs: TIDA-00893 Isolated CAN With Integrated Power Reference Design

TEXAS INSTRUMENTS

### Description

This reference design provides a compact solution capable of generating isolated DC power while supporting isolated CAN communication. This isolated CAN reference design consists of a reinforced digital isolator with integrated power combined with a CAN transceiver and is designed to reduce emissions.

#### Resources

TIDA-00893 TCAN1042-Q1 ISOW7841 Design Folder Product Folder Product Folder

ASK Our E2E™ Experts

#### Features

- > ±8 kV Across Barrier, ±16 kV Same-Side IEC 61000-4-2 ESD Protection

- ±4-kV EFT Burst Tolerant Even at Optimized Size

- Industry-Leading Common-Mode Transient Immunity (CMTI): ±100 kV/µs (Minimum)

- Single Power Supply Solution

- No Separate Supply Required to Power Side 2 Components

- V<sub>ISO</sub> of ISOW7841 Can Source Load up to 130 mA

- Can Support 3-V and 5-V CAN Applications

- Reduced BOM Cost Solution Eliminates Need for Separate Transformer

- Simpler Design

- Fast Loop Delays

- Extendable to Other CAN or CAN FD Transceivers

- PCB Design Creates a Stitching Capacitor Across

Isolation Barrier for Improved Emissions

#### Applications

- PLC, PAC, DCS Communication Modules

- Grid Communication Modules

- Industrial Automation

- High-Voltage System Communication Modules

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

This reference design combines both data and power isolation along with a Controller Area Network (CAN) communication interface to provide a robust, low-cost, small-footprint solution that customers can directly place on their designs. This design combines a high-performance reinforced digital isolator with an integrated high-efficiency, low-emissions DC/DC converter (ISOW7841), and a robust automotive fault protected CAN flexible data rate (CAN FD) transceiver (TCAN1042HG-Q1).

This reference design does not require any additional components to generate the isolated power, making the isolation solution less than a quarter of the size of all existing solutions by using a discrete transformer to generate the required isolated power. This reference design takes a single power supply input between 3 V and 5.5 V and digital signals referred to the input supply level on side 1 of the board. The ISOW7841 generates an isolated power supply using an integrated DC/DC converter, which is used to power the CAN transceiver on side 2 of the board. The side 1 signals are isolated and connected to the CAN transceiver, which converts the single-ended digital signals into the differential CAN format.

PLCs and grid communication systems have been an integral part of factory automation and industrial process control using digital and analog I/O modules to interface to sensors, actuators, and other equipment. Analog inputs for the PLC system include temperature sensors, transmitters, and current and voltage sensors. Examples of common digital inputs include push-buttons, proximity switches, photo sensors, pressure switches, and more that need to be either group isolated or isolated per channel. Because PLCs are expected to work in harsh industrial environments, sensor signals are converted into the digital domain and coupled to the control domain through a digital isolator. Power for the sensors and switches is also isolated from the back plane side with an isolated DC/DC converter. The isolated CAN reference design can significantly reduce the required component mounting area on the PCB and bring down the BOM cost by eliminating the requirement for discrete transformers.

### 1.1 Key System Specifications

| FEATURE                | PARAMETER          | SPECIFICATION                 |

|------------------------|--------------------|-------------------------------|

| Input supply           | Input voltage      | 5 V                           |

| Isolated output supply | Output voltage     | 3.3 V or 5 V                  |

|                        | Output current     | 75 mA (3.3 V <sub>IN</sub> )  |

|                        |                    | 130 mA (5 V <sub>IN</sub> )   |

| Communication          | Max data rate      | 5 Mbps (CAN FD communication) |

| Isolation              | Clearance          | > 3 mm                        |

|                        | Surge              | 4 kV                          |

|                        | Working voltage    | 300 V <sub>RMS</sub>          |

|                        | CMTI               | > 100 kV/µs                   |

| EMI or EMC             | ESD                | 6 kV (across barrier)         |

|                        |                    | 16 kV (across CAN lines)      |

|                        | EFT                | 2 kV (Class A)                |

|                        | Radiated emissions | CISPR22 (Class B)             |

|                        | Radiated immunity  | 10 V/m                        |

#### **Table 1. Key System Specifications**

# 2 System Overview

### 2.1 Block Diagram

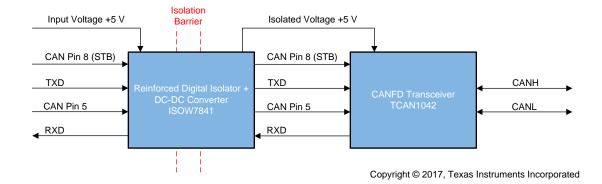

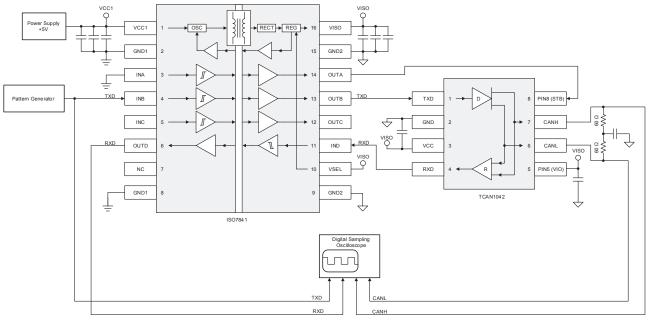

Figure 1. TIDA-00893 Block Diagram

Figure 1 shows the high-level block diagram of this reference design, which can be broken down to two main sections: the isolation block (ISOW7841) and the interface block (TCAN1042HG-Q1).

The isolated CAN reference design works on a single input of  $3 \vee to 5.5 \vee$ . The integrated power supply can produce an isolated output voltage of  $3.3 \vee (for any input)$  or  $5 \vee (for \vee CC1 \ge 5 \vee)$ , which can be used to power up the CAN interface block. Most CAN transceivers including the TCAN1042HG-Q1 use a 5-V supply; some CAN transceivers use a 3.3- $\vee$  supply that can be supported by this reference design. Digital signals from a source such as a microcontroller (MCU) are connected on one side of the board to the ISOW7841 digital isolator, and the differential CAN lines that communicate with the field side of the system are connected to the other.

### 2.2 Highlighted Products

This reference design features the following devices from Texas Instruments.

#### 2.2.1 ISOW7841

The ISOW7841 is a high-performance, quad-channel, reinforced digital isolator with an integrated, highefficiency power converter. The integrated DC/DC converter provides up to 650 mW of isolated power at high efficiency, can be configured for various input and output voltage configurations, and eliminates the need for a separate isolated power supply in isolated designs with space constraints.

The ISOW7841 device provides high electromagnetic immunity and low emissions while isolating CMOS or LVCMOS digital signals with an isolation channel that has a logic input and output buffer separated by a silicon dioxide (SiO<sub>2</sub>) insulation barrier. Power isolation uses on-chip transformers separated by insulation material that is a thin film polymer. Unwanted noise currents are prevented from entering the data bus, other circuits, or the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISOW7841 has been significantly enhanced to ease system-level electrostatic discharge (ESD), electrical fast transient (EFT), surge, and emissions standard compliance. The high efficiency of the power converter allows operation at a higher ambient temperature. The ISOW7841 is available in a 16-pin SOIC wide-body (DWE) package.

Key features of the ISOW7841 isolator include the following:

- Integrated, high-efficiency DC/DC converter with on-chip transformer

- Wide input supply range: 3 V to 5.5 V

- Regulated 3.3-V or 5-V output

- Up to 650-mW output power

- 130-mA load current (5 V to 5 V or 5 V to 3.3 V)

- 70-mA load current (3.3 V to 3.3 V)

- Soft start to limit inrush current

- · Overload and short-circuit protection

- Thermal shutdown

- Signaling rate up to 100 Mbps

- Low prop-delay: 13 ns typical (5-V supply)

- High CMTI: ±100 kV/µs (min)

- Robust electromagnetic compatibility (EMC):

- System-level ESD, EFT, and surge immunity

- Low radiated emissions

- Safety-related certifications:

- 7071-V<sub>PK</sub> Reinforced Isolation per DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

- 5000-V<sub>RMS</sub> Isolation for 1 Minute per UL 1577

- CSA Component Acceptance Notice 5A, IEC 60950-1 and IEC 60601-1 End Equipment Standards

- CQC Approval per GB4943.1-2011

- TUV Certification according to EN 60950-1 and EN 61010-1

- All agency certifications are planned

- Extended temperature range: -40°C to +125°C

### 2.2.2 TCAN1042HGV-Q1

The TCAN1042HG-Q1 transceiver meets the ISO 11898-2 (2016) high-speed CAN physical layer standard. This transceiver is designed for data rates in excess of 1 Mbps for CAN FD with an enhanced timing margin for higher data rates in long and highly-loaded networks. The TCAN1042 provides many protection features including undervoltage protection (UVLO) on the supply pins, ±70-V bus fault protection, both driver and receiver dominant state timeouts (TXD DTO, RXD DTO), and thermal shutdown protection (TSD). The CANH and CANL bus pins also have robust integrated ESD protection against HBM, CDM, IEC 61000-4-2, and ISO 7637 standards. Without requiring external protection components, the TCAN1042HG-Q1 tolerates ±8-kV IEC 61000-4-2 ESD, ±16-kV HBM ESD, and ±4-kV IEC 6100-4-4 EFT levels.

System Overview

Key features of the TCAN1042HGV-Q1 transceiver include the following:

- AEC Q100: qualified for automotive applications

- Meets the ISO 11898-2:2016 physical layer update

- Meets the released ISO 11898-2:2007 and ISO 11898-2:2003 physical layer standards

- "Turbo" CAN:

- Supports 5-Mbps CAN FD

- Short and symmetrical propagation delay times and fast loop times for enhanced timing margin

- Higher data rates in loaded CAN networks

- Input and output voltage range supports 3.3-V and 5-V MCUs

- Ideal passive behavior when unpowered:

- Bus and logic terminals are high impedance (no load)

- Power-up and power-down glitch free operation on bus and RXD output pins

- Protection features:

- HBM ESD protection: ±16 kV

- IEC ESD protection: up to ±15 kV

- Bus fault protection: ±70 V

- UVLO on V<sub>cc</sub> and V<sub>IO</sub> (V variants only) supply terminals

- Driver dominant timeout (TXD DTO) with data rates down to 10 kbps

- Thermal shutdown protection (TSD)

- Receiver common-mode input voltage: ±30 V

- Typical loop delay: 100 ns

- Junction temperatures: -55°C to +150°C

### 2.3 System Design Theory

#### 2.3.1 Isolation

Noise can seriously affect the integrity of data transfer in most industrial interface systems. Including galvanic isolation in the interface circuit is a proven method for improving the communication performance and protecting the low-voltage (LV) MCU side from the high-voltage (HV) side exposed to stresses like ESD, EFT, and surge.

Ground loops and electrical line surges can cause many forms of radiated and common-mode noise with unwanted current and voltage on the cable bus connecting multiple systems resulting in severe problems. Ground loops occur when there are multiple paths in the system for current to flow to ground. These paths have different impedance and can pick up additional current through electromagnetic induction, creating a potential difference for current to flow and cause bit errors or damage components. Electrical surges can be caused by many sources typically coupled onto long cables through induction. Industrial environments have many sources of surge, such as electric motors that cause rapid changes in the ground potential while operating and force current to flow on system cables to equalize the changing ground potential.

Other HV stress sources include ESD and lightning strikes (surge) that can result in thousands of volts of potential on the line. A remote node may receive a 5-V switching signal superimposed on a HV level with respect to the local ground. These uncontrolled voltages and currents can corrupt the signal and be catastrophic to the device and system, causing damage or destruction of the components connected to the bus and resulting in system failure. CAN systems that connect multiple systems in automotive and industrial environments are especially susceptible to these events.

Isolating the CAN system devices from each of the systems connected to the bus prevents ground loops and electrical surges from destroying circuits. Isolation prevents ground loops because each system and CAN circuit connected to a CAN cable bus has a separate and isolated ground. By referencing each CAN circuit only to one ground, ground loops are eliminated. Isolation also allows the reference voltage levels of the CAN circuit to rise and fall with any surges that appear on the cable line. Isolation allows the circuit voltage reference to move with surges, rather than being clamped to a fixed ground, preventing devices from being damaged or destroyed. To accomplish system isolation, both the CAN signal lines and power supplies must be isolated.

#### 2.3.2 CAN Communication

CAN is an International Standardization Organization (ISO) defined serial communications bus originally developed for the automotive industry to replace complex wiring harnesses with a two-wire bus. The specification calls for high immunity to electrical interference and the ability to self-diagnose and repair data errors. These features have made CAN popular in a variety of industries including building automation, process control automation, elevators, construction equipment, robotics, medical, and manufacturing among many others.

The following key features make CAN ideal for use in industrial and instrumentation applications:

- · Established standard and standardized plug-n-play products

- · Fault tolerant, very-high short-circuit protection

- Self-diagnosing error repair, every bit checked five times for errors

- Robust interface for harsh electrical environments

- Wide common-mode operating range tolerant of ground potential differences

- Multi-master message broadcast system where all nodes receive all messages

- Message priority identifier with lossless bit-wise arbitration system to ensure the highest priority message is transmitted first and no message is lost

### 3 Hardware, Testing Requirements, and Test Results

### 3.1 Hardware

#### 3.1.1 Board Description

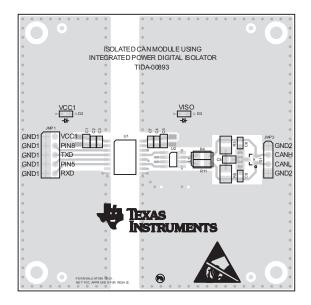

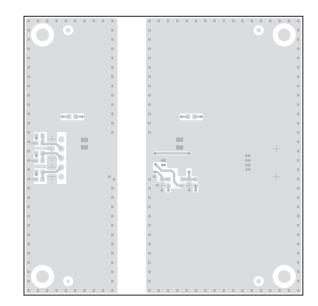

Figure 2 shows the size of the reference design that has been optimized for low radiated emissions with the component mounting area on the board marked in red. Traditional solutions that do not integrate power isolation into the same digital isolation device require transformers, transformer drivers, and rectifiers to isolate the power from one side of the isolation barrier to the other. These additions take up much more space on a PCB than the integrated solution shown with the ISOW7841. The board for this reference design measures 3 by 3 inches, while the component mounting requires less than 0.5 by 2 inches of area. This board has been separated into two sides for isolation. Side 1 is the system side connected to power input VCC1 and GND1 planes. Side 2 is connected to the isolated output voltage ( $V_{ISO}$ ) and GND2 planes and contains the TCAN1042 transceiver.

Figure 2. Component Mounting Area

The transformers used in non-integrated solutions are typically high-inductance magnetic-core transformers with low switching frequencies and are fairly large in size. By scaling the power isolation components into a single device, chip-scale transformers are used to keep small area solutions possible. These small transformers use much fewer turns than the external transformers, reducing the series resistance. As a result, a higher-frequency DC/DC converter is needed to drive the transformer at several tens of megahertz or more.

Because the primary and secondary windings of these small transformers are close together inside the device package, and typically do not use magnetic cores, a parasitic capacitance forms between the two coils of the transformer, which could be fairly large. This capacitance allows a path for the fast transients in the DC/DC converter to couple through to the other side, creating common-mode current between the two sides. However, because the two sides of the ISOW7841 device are completely isolated, the current forms a path through parasitic capacitance on the board itself creating a large current loop and radiated emissions.

The power converter used to drive the transformer has a duty cycle and high-current draw from the  $V_{cc}$  input supply during the active portion of the cycle. The low-frequency content of the current is somewhat proportional to the closed-loop regulation bandwidth of the DC/DC converter while the higher frequency content is a result of the switching frequency and harmonics. Therefore, the common-mode current is composed of several different components of varying frequency that need to be addressed.

One of the methods used in this reference design to address this common-mode current is to include a bank of three different valued capacitors at both the input and output voltage pins. This bank helps filter out this frequency content and prevent it from propagating through the power routing. The smallest valued capacitor, 100 nF, is placed closest to the ISOW7841 pins, followed by the  $1-\mu$ F capacitors and then the  $10-\mu$ F capacitors, making the area of the power to ground loops as small as possible.

#### Figure 3. Decoupling Capacitor Banks

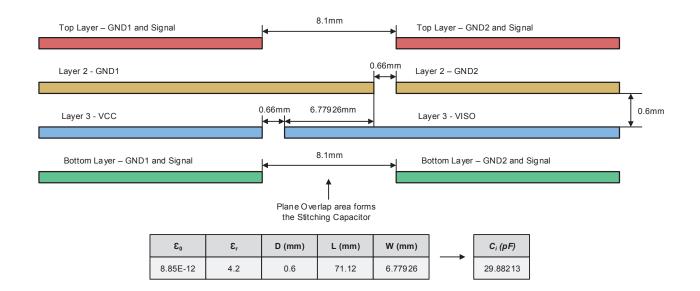

Secondly, this board is a four-layer design and uses the internal layer three for power. Layer two is used for ground along with the majority of the top and bottom layer not used for component placement and signal routing. Stitching vias are placed along the edges of the board and along the isolation channel to form a Faraday cage around any noise on the internal power planes, which can contribute to the radiated emission profile.

Despite all the efforts to filter and contain the transient noise on either side of the isolation channel, there is still some common-mode current that flows through the board parasitic capacitance between the two sides. A capacitor can be added between the GND pins on each side of the isolator, but that capacitor must be a high-voltage capacitor rated to handle the isolation voltage needs. This capacitor also comes with some inductance from the leads and limit the maximum effective frequency range.

Instead of increasing the BOM cost and limiting the maximum effective frequency by adding one of these capacitors to this reference design, a low-inductance capacitor is created in the PCB layout by overlapping the internal PCB layers within the isolation channel region.

The side 1 GND plane on layer two of the board (see Figure 23), and connected to pin 8 of the ISOW7841, is extended most of the way into the channel, leaving approximately 0.66 mm of gap between it and the side 2 GND plane. The side 2 VISO plane on layer three (see Figure 24) is likewise extended into the isolation channel region, leaving approximately 0.66 mm of gap between VCC on side 1 of the isolation device.

The thickness of the FR-4 dielectric material between the GND1 and VISO planes is 0.6 mm. This material creates a parallel plate stitching capacitance across the isolation region and creates a lower inductance path for the high-frequency switching transients to flow, thereby reducing the amount of radiated emissions.

The capacitance of the stitching capacitor C<sub>i</sub> can be calculated with Equation 1:

$$C_i = \varepsilon_0 \times \varepsilon_r \times \frac{A}{d}$$

where:

- $\mathcal{E}_0$  is the absolute permittivity of air (8.854 pF/m)

- E<sub>r</sub> is the relative permittivity of the dielectric (4.2 for FR-4)

- A is the overlapping area

- d is the distance between GND and  $V_{cc}$  layers

#### Figure 4. Isolation Channel With Embedded High-Frequency Stitching Capacitor

While creating a stitching capacitance inside the isolation channel improves the radiated emissions, it also brings the power and ground planes from the two sides closer together. The standards for systems with reinforced isolation require a minimum spacing between the two sides to maintain sufficient isolation for the application given the dielectric strength of the board material insulation.

The IEC 66010-1 standard mandates that a reinforced isolated system withstand a 5-second test of 3510 V<sub>RMS</sub> and a surge or impulse test of 6400 V<sub>PK</sub> for mains voltage between 300 V<sub>RMS</sub> and 600 V<sub>RMS</sub>. The minimum spacing of 0.6 mm is needed for systems that require between 300 V<sub>RMS</sub> and 600 V<sub>RMS</sub>, but that spacing can be reduced to 0.4-mm if less than 300 V<sub>RMS</sub> of isolation is needed. A minimum spacing of 0.6-mm is used in this reference design to provide isolation up to 600 V<sub>RMS</sub> using FR-4 with a dielectric strength of 20 kV/mm.

(1)

Hardware, Testing Requirements, and Test Results

www.ti.com

Because the breakdown voltage of air is different than that of the FR-4, the power and ground planes are kept away from the edges of the board by more than 0.6 mm to ensure that there is not excessive field stress that could cause an air breakdown along the edge of the board. Sharp corners on the planes also increase the electric field intensity. To reduce the risk of a breakdown occurring between the planes during a high-voltage pulse, all corners of the planes are mitered at 45° to help spread out the charge density and ensure there are no 90° sharp corners that could lead to a breakdown.

It is also common practice to use a common-mode choke on the CAN bus pins to remove any noise coming into the node from the CAN bus and to prevent any noise generated in the node from entering the bus. The TCAN1042 CAN FD transceiver already has excellent emissions performance and does not require a common-mode choke to pass IEC TS 62228; adding one improves the performance even more.

Furthermore, because a high-frequency DC/DC converter is used in the power isolation, a small amount of the common-mode noise can filter into the power supply of the TCAN1042 and find its way into the CAN bus. Using a choke prevents this from occurring. If a common-mode choke is not needed, remove and replace the choke with two low-valued resistors such as 0  $\Omega$ .

There is also a placeholder on the board for an external TVS diode to help achieve greater ESD protection than what the TCAN1042 can provide. Loading capacitors are also added to each CAN line that can be populated to help mimic the capacitive load of the cabling on a CAN bus in a lab environment along with pullup and pulldown resistors on the digital signals connector for convenience of the user. Because all of these components are not required for a real system, it is left up to the user to configure them per his or her requirements.

#### 3.1.2 Connector Description

There are only two connectors on this board: one for the power and digital interface side, and the other for the CAN bus side.

The connector on the left side of the board is for the power and digital signals. Connect a 5-V DC power supply between the VCC and GND1 pins. All the other signals are labeled according to their function and have a GND1 pin next to each one to provide easy access to a scope probe GND reference or that of a cable coming from an MCU or signal generator.

Pins 5 and 8 vary in function among CAN transceivers. The TCAN1042 used in this reference design uses pin 8 for a standby mode control, and pin 5 as a VIO supply pin that could be either 5 V or 3.3 V depending on the signal level of the MCU connected to it. The ISOW7841 is capable of supplying an isolated 5 V or 3.3 V on the VISO pin. However, the isolator can not supply both a 5-V VCC rail and 3.3-V VIO rail at the same time.

Therefore, for this reference design, the same 5-V supply level is used for VIO. This pin is isolated from the connector with an uninstalled resistor because this is not a digital signal. Other transceivers could use this pin as a fault indicator pin. If one of those transceivers are evaluated with the ISO7841 instead of the TCAN1042, this signal is available on the connector by populating this resistor with a 0- $\Omega$  resistor.

The connector on the right side of the board has the CANH and CANL bus pins along with a GND2 pin next to each one as an easy reference for a ground reference pin of a scope probe.

Figure 5. Board Connectors

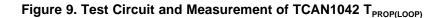

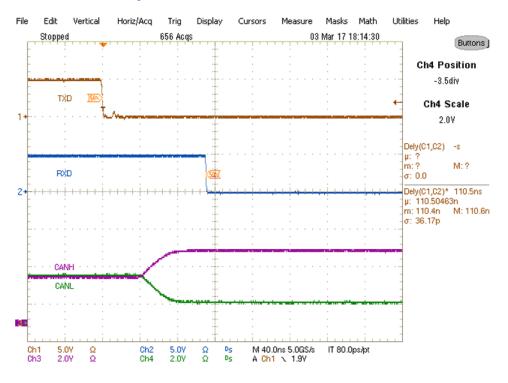

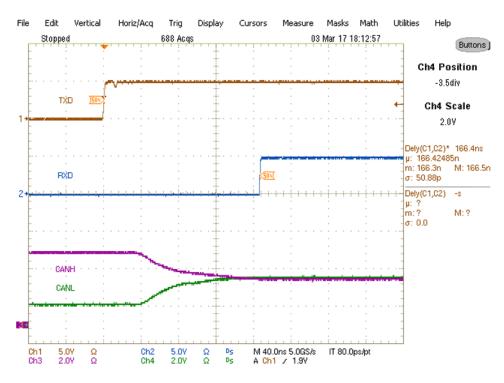

# 3.2 Testing Results—Waveforms and T<sub>PROP(LOOP)</sub> Measurements

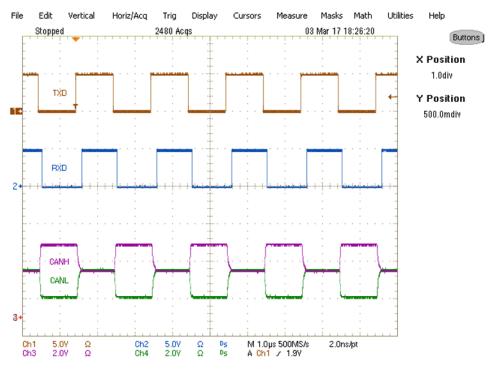

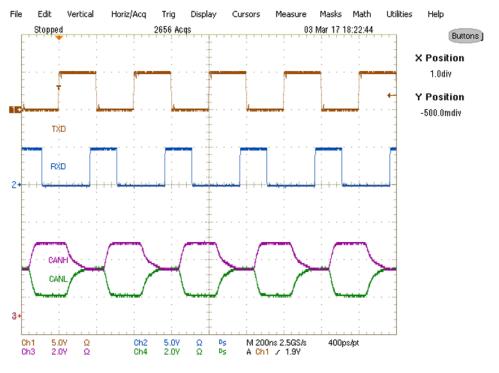

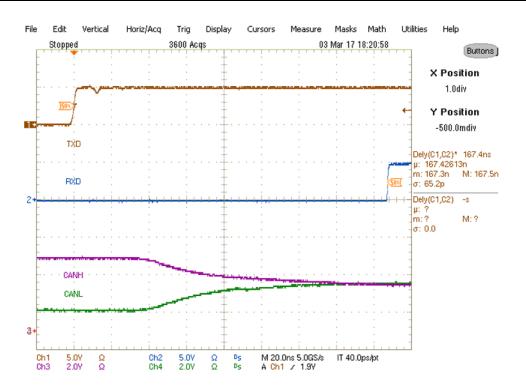

The TCAN1042 transceiver can support both classical CAN applications with data rates up to 1 Mbps and CAN FD applications with data rates up to 5 Mbps. Waveform symmetry is critical in maintaining low common-mode noise and radiated emissions. Therefore, waveforms of the CANH, CANL, TXD, and RXD are captured on a scope at both 1- and 5-Mbps data rates using a square wave input signal from a pattern generator to mimic the maximum data rates of the CAN and CAN FD protocols.

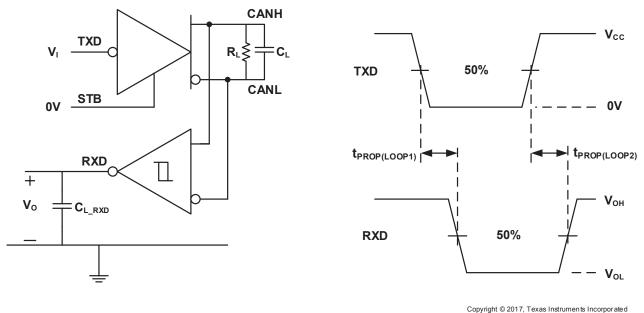

During the arbitration phase of the CAN protocol, the propagation delay of the transceiver and the delay between the nodes is important. To ensure that the node with the highest priority message gains control of the bus, the MCU monitors the data coming into its RXD pin and compares it with the data it is transmitting on its TXD pin. If the MCU transmits a recessive bit on the TXD pin yet detects a dominant bit on the RXD pin, the MCU loses arbitration to a node with a higher priority message and stop transmitting, thereby yielding the bus to the other node. This arbitration must be completed in 255 ns, which is about 25% of the bit period for a 1-Mbps data bit and the maximum allowable loop delay for a signal propagating between the TXD pin and the RXD pin of the transceiver.

Adding isolation between the MCU and the transceiver increases the loop time, can impact the arbitration, and cause bit collisions between two nodes. Having fast transceiver loop delays allows the MCU to perform arbitration quickly, giving a performance margin to the overall system. These delays also allow for margin when adding the additional delay from an isolation device while maintaining the required timing.

Copyright © 2017, Texas Instruments Incorporated

Figure 7 shows the TXD, RXD, CANH, and CANL signal waveforms with a repeating one-zero data pattern running at 1 Mbps. Figure 8 shows the same signals with the data pattern running at 5 Mbps.

Figure 7. CAN Waveforms With 1 Mbps of Data

Figure 8. CAN Waveforms With 5 Mbps of Data

Figure 9 shows the test circuit and measurement definition of the TCAN1042  $T_{PROP(LOOP)}$ .

Copyright © 2017, Texas Instruments Incorporate

The following figures show the measured  $T_{PROP(LOOP)}$  delays of the TCAN1042 with the additional delay of the ISOW7841, as shown in Figure 6.

Figure 10. T<sub>PROP(LOOP1)</sub> Delay Measured With 1 Mbps of Data

Figure 11. T PROP(LOOP2) Delay Measured With 1 Mbps of Data

Because the  $T_{PROP(LOOP)}$  delay times are fixed, they are not expected to change with the data rate, as shown in the following figures with the data pattern increased to 5 Mbps.

Figure 12. T<sub>PROP(LOOP1)</sub> Delay Measured With 5 Mbps of Data

| DATA RATE (Mbps) | T <sub>PROP(LOOP1)</sub> (ns) | T <sub>PROP(LOOP2)</sub> (ns) |

|------------------|-------------------------------|-------------------------------|

| 1                | 110.5                         | 166.4                         |

| 5                | 110.6                         | 167.4                         |

Table 2. T<sub>PROP(LOOP)</sub> Measurement Summary

### 3.3 Testing and Results—Conducted Emissions

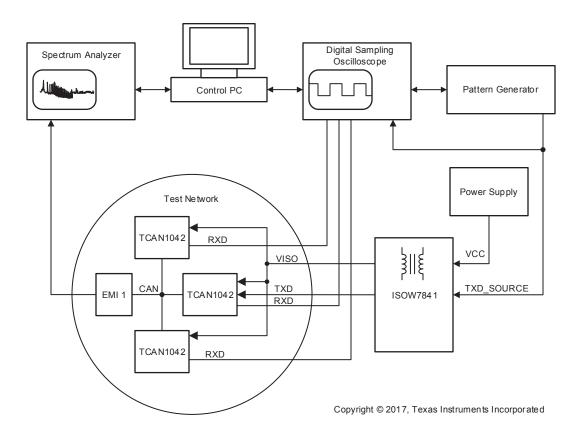

Both conducted and radiated emissions concern system designers. The conducted emissions are measured according to the IEC TS 62228 standard using the Zwickau CAN HS EMI/EMS V3.6a BK01/BK13 test circuit board. This board measures the emissions on the CAN bus with three TCAN1042 transceivers or nodes populated, but it does not have provision for the ISOW7841 digital isolator with integrated power. Therefore, to accommodate testing of the conducted emissions, the TCAN1042 is removed from the design board, and the TXD, RXD, VISO, and GND pins of the ISOW7841 are connected to the TCAN1042 device under test on the test circuit board. The conducted emissions test setup is shown in Figure 14.

Figure 14. Conducted Emissions Test Setup

It is important to establish a baseline noise floor for the test setup to use as a comparison when evaluating the cumulative effects of the system under test. Figure 15 shows the baseline noise floor of the test setup without the TCAN1042 and ISOW7841 devices.

Figure 15. Noise Floor Measurement of Conducted Emissions Test Equipment

Figure 16 shows the design is capable of passing the conducted emissions test standard with the use of a common-mode choke.

Figure 16. Common-Mode Choke Measurement of Conducted Emissions Test Equipment

### 3.4 Testing and Results—Radiated Emissions

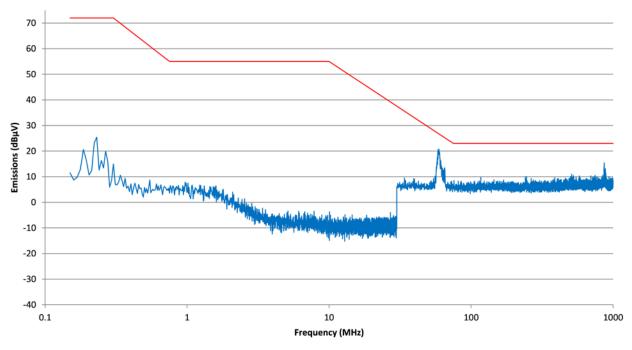

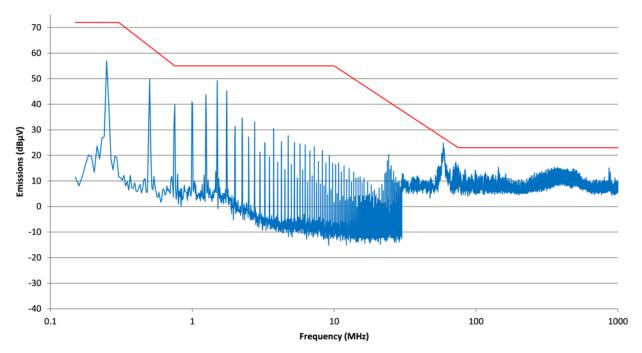

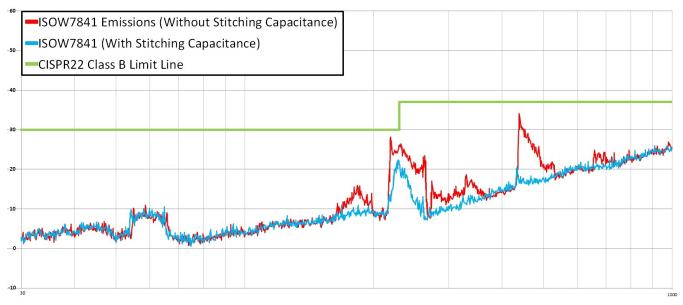

Radiated emissions are measured on the ISOW7841 using two different boards against the CISPR 22 Class B limit. One board implements the stitching capacitance PCB layout technique duplicated in this reference design. The other board does not include the stitching capacitance technique and instead implements a traditional isolation channel under the device. Measuring the radiated emissions in this manner allows for a direct comparison on the improvement as a result of implementing the stitching capacitance.

Figure 17 shows the radiated emissions measurements with and without stitching capacitance. While both tests pass the CISPR 22 Class B test limit, it is easy to see the filtering effect the stitching capacitor has on the higher frequency noise generated by the isolated transformer inside the ISOW7841 and the additional margin that can be gained by implementing it into a design.

Figure 17. Radiated Emissions Measurements With and Without Stitching Capacitance

TEXAS INSTRUMENTS

www.ti.com

Design Files

### 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-00893.

### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00893.

### 4.3 PCB Layout Recommendations

The PCB layout shown in this reference design is a good example of how to reduce radiated emissions from the integrated power transformer without adding additional cost to the BOM by creating a stitching capacitor across the isolation barrier using the PCB power and ground layers.

A capacitance of 30 pF is targeted for this reference design with isolation up to 600  $V_{RMS}$ . Adjustments to this basic layout format can be made to accommodate different levels of isolation and capacitance using Equation 1. Placing several capacitors of different values across the power and ground pins of both sides of the ISOW7841 device is also recommended as a filter for unwanted power noise being emitted into the system and for improved device performance.

This reference design also demonstrates how to improve the isolation performance during a high-voltage pulse and reduce the risk of a breakdown occurring between the planes of the PCB. It is recommended to remove 90° and sharp corners on the power and ground planes. All corners in this design have been mitered at 45° to reduce the electric field intensity at these locations during high-voltage pulses.

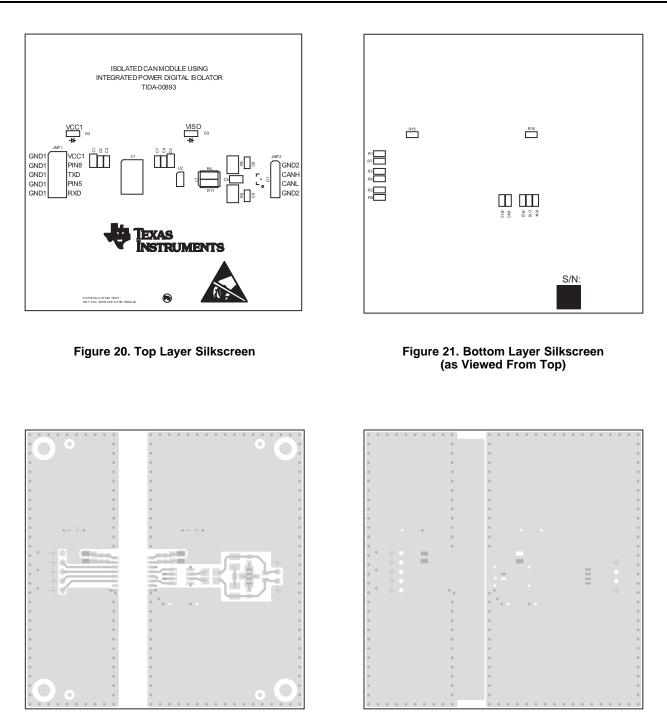

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00893.

Figure 18. Top Layer With Silkscreen

Figure 19. Bottom Layer With Silkscreen (as Viewed From Top)

#### Figure 22. Top Layer

Figure 23. Layer 2 Ground

Figure 24. Layer 3 Power

Figure 25. Bottom Layer (as Viewed From Top)

### 4.4 Cadence Project

To download the Cadence project files, see the design files at TIDA-00893.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00893.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00893.

### 5 Related Documentation

- 1. Texas Instruments, TCAN1042-Q1 Automotive Fault Protected CAN Transceiver with CAN FD Data Sheet

- 2. Texas Instruments, ISOW784x High-Performance, 5000-VRMS Reinforced Quad-Channel Digital Isolators With Integrated High-Efficiency, Low-Emissions DC-DC Converter Data Sheet

- 3. Texas Instruments, TIDA-00892 Isolated RS-485 With Integrated Signal and Power Reference Design

- 4. Texas Instruments, TIDA-01230 Isolated RS-232 With Integrated Signal and Power Reference Design

### 5.1 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 6 About the Author

**JONATHAN NERGER** is an applications engineer at Texas Instruments supporting transceiver interface products used in standards such as CAN, LIN, RS-485, RS-232, IO-Link, and I<sup>2</sup>C. Jonathan is responsible for developing EVMs, reference design solutions, and for customer support through direct contact and creating technical content such as application notes, datasheets, white papers, and videos and silicon characterization. Jonathan brings to this role experience in other differential signaling standards such as PECL, LVDS, MLVDS, HDMI, DisplayPort, high-speed SERDES, and optical transceiver applications. Jonathan earned his bachelors of science in electrical engineering (BSEE) from Southern Methodist University (SMU).

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated