# TI Designs: TIDA-01385 Energy Harvesting From Current Transformer With Supercapacitor for Fault Indicator Reference Design

# Texas Instruments

# Description

The TIDA-01385 design introduces a circuit to harvest energy from a current transformer for the system load of a fault indicator while storing the extra energy in a 2.7-V supercapacitor. A primary Li/SOCI2 battery is used as backup power to extend the operating time of the fault indicator after the power grid fails. With an input current from 3 mA to 2 A, this TI Design provides a stable 3.6 V to the system load within 2 seconds after the current transformer is connected.

## Resources

| TIDA-01385 |  |

|------------|--|

| TPS61021A  |  |

| TLV3492    |  |

| ATL431A    |  |

| CSD13202Q2 |  |

| CSD25310Q2 |  |

| TIDA-00998 |  |

TI E2E<sup>™</sup> Community Product Folder Product Folder Product Folder Product Folder Product Folder Design Folder

Design Folder

# ASK Our E2E Experts

# Features

- Harvests Energy From Current Transformer

- Automatic Charging Supercapacitor With Extra Energy

- Provides Stable Output Voltage Within 2 Seconds

- Supercapacitor Full Charged Protection

- Ultra-low Input Boost Converter for Using Maximum Supercapacitor Stored Energy

# Applications

Fault Indicators

Energy Harvesting From Current Transformer With Supercapacitor for Fault Indicator Reference Design

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

A fault indicator is a device used in electric power distribution networks to detect and indicate fault conditions. The fault indicators reduce operating costs and service interruptions by providing information on the section of the network that has failed. To quickly identify the fault type and location, the latest fault indicator is required to record the operating data of the power networks, which is sent to the data concentrator with low-power wireless communication when necessary.

The power supply for the fault indicator is an energy harvesting device with the primary battery as backup. The energy harvesting devices could be the current transformer (CT) or solar cell. Because the energy from a CT varies with the current through the power lines or from solar cell changes with sunlight condition, an energy buffer such as a supercapacitor or rechargeable battery is required to provide stable power supply. The primary battery should be long shelf life (>10 year) lithium or lithium-ion based cells, such as a Li/SOCI2 battery, considering the long lifetime of the fault indicator.

This reference design introduces a circuit to harvest energy from a CT to charge a supercapacitor and provide stable power for the system load. The backup primary battery is the Li/SOCl2. For another reference design about energy harvesting in this application field, see the TIDA-00998 design.

# 1.1 Key System Specifications

Table 1 summarizes the key specifications for the TIDA-01385 design. The supercapacitor capacity can be selected based on real requirement without impacting the performance of the reference design.

| PARAMETER                   | DESCRIPTION                                                |  |

|-----------------------------|------------------------------------------------------------|--|

| CT input current            | CT secondary peak current range of 3 mA to 2 A             |  |

| Supercapacitor backup time  | 100 seconds with a 10-F capacitance and 50-mA load current |  |

| Output voltage              | 3.6 V when powered from the CT and supercapacitor          |  |

|                             | 3 to 3.3 V when powered from the primary battery           |  |

| Output voltage startup time | 2 seconds (typical)                                        |  |

### **Table 1. Key System Specifications**

# 2 System Overview

### 2.1 Block Diagram

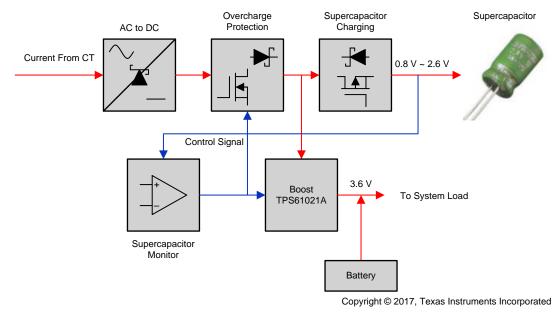

The block diagram of the TIDA-01385 is shown in Figure 1. The power input is from the secondary side of the CT. The maximum input current of the CT should be lower than 2 A. The minimum input current depends on the system load requirement. Normally it should be higher than 3 mA.

The function of the each block is as follows:

- The AC to DC is a full-bridge rectifier, transferring the AC input current into DC current.

- The overcharge protection circuit shorts the current from the CT to ground when the supercapacitor is fully charged. The circuit becomes inactive and the current charges the supercapacitor again if the supercapacitor voltage is lower than a voltage threshold.

- The supercapacitor charging circuit charges the supercapacitor only when the input voltage is higher than 1.6 V, which is high enough for the operation of the TPS61021A. So all the energy from the CT can be used for the system load even if the supercapacitor voltage is zero.

- The supercapacitor monitor circuit controls the protection circuit to prevent the supercapacitor from overcharge.

- The boost converter TPS61021A boosts the low input voltage to 3.6 V for the system load. The 3.6-V voltage can prevent the battery from discharge during normal operating condition.

- The battery is a Li/SOCI2 battery and connected to a 3.6-V power rail through a Schottky diode in series. The battery can support system load when the power grid fails and the supercapacitor is out of charge.

Figure 1. Block Diagram of TIDA-01385

System Overview

### 2.2 Highlighted Products

The reference design features the TPS61021A, TLV3492, ATL431, CSD13202Q2, and CSD25310Q2. The following subsections briefly summarize the key performance of each device. To find more details about each device, see their respective datasheets at TL.com.

# 2.2.1 TPS61021A

The TPS61021A is an ultra-low input voltage device. The device can operate with an input voltage between 0.5 and 4.4 V after it finishes startup from a 0.9-V input voltage. The wide input voltage range makes it suitable in the application that is powered by the signal-cell supercapacitor. Other key features of this device include:

- 17-µA typical quiescent current

- PFM operation mode at light load

- Output overvoltage protection

- Output short-circuit protection

- 2-mm×2-mm WSON package

- True disconnection between input and output during shutdown

## 2.2.2 TLV3492

The TLV3492 is a 1.8-V, nano-power, dual push-pull comparator. The small power consumption helps to minimize the power loss of the reference design. The push-pull output can reduce the external components to drive the MOSFET. Other key features of this device include:

- Very low supply current: 0.8 µA (typical)

- Input common-mode range: 200-mV beyond supply rails

- Supply voltage: 1.8 to 5.5 V

- High speed: 6 µs

- Push-pull CMOS output stage

# 2.2.3 ATL431

The ATL431 is an adjustable, three-terminal shunt regulator with low quiescent current. The device is offered in two grades, with initial tolerances (at 25°C) of 0.5%, 1%, for the B and A grade, respectively. The reference design selects the grade device ATL431A. Other key features of this device include:

- Adjustable regulated output: 2.5 to 36 V

- Very-low operating current

- Internally compensated for stability

- Extended cathode current range: 35 µA to 100 mA

# 2.2.4 CSD13202Q2 and CSD25310Q2

The CSD13202Q2 is a 12-V N-Channel power MOSFET. Its continue drain current is up to 14 A. Its gateto-source threshold voltage is typically 0.8 V and the drain-to-source on-resistance is only 9.1 mR at a 2.5-V driving voltage.

The CSD25310Q2 is a 20-V P-Channel power MOSFET. The gate-to-source threshold voltage of this device is typically 0.85 V. The drain-to-source on-resistance is 27 mR at a 2.5-V driving voltage. The device has low thermal resistance and up to 150°C maximum operating junction temperature.

### System Overview

# 2.3 System Design Theory

The entire schematic of the TIDA-01385 can be found in the TIDA-01385 design folder. The following subsections explain the behavior of each subcircuit.

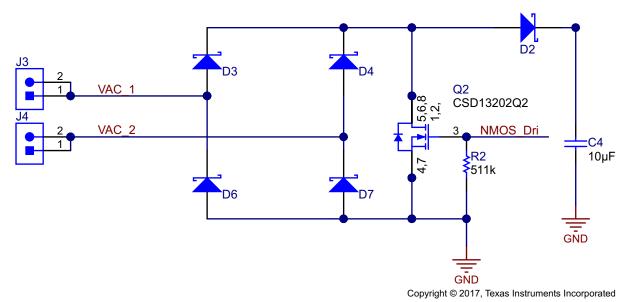

## 2.3.1 Rectifier and Overcharge Protection

The circuit shown in Figure 2 is used for rectifying the AC to input DC voltage and protecting the supercapacitor from overcharge. The full-bridge rectifier is composed of four Schottky diodes. The current capability of the Schottky diodes should be higher than maximum input current, which is 2 A in this reference design. The maximum voltage rating of diode must be higher than 5 V.

The N-type MOSFET Q2 is used to protect the supercapacitor from overcharging. When supercapacitor voltage is lower than setting limit 2.6 V, the Q2 opens, so the current flows through the D2 to power the system load and charge the supercapacitor. After the supercapacitor voltage reach 2.6 V, the Q2 turns on to short the input current into ground. When the supercapacitor is discharged to a setting value of 2.4 V by the load, Q2 opens again.

Figure 2. Rectifier and Overcharge Protection

(1)

#### System Overview

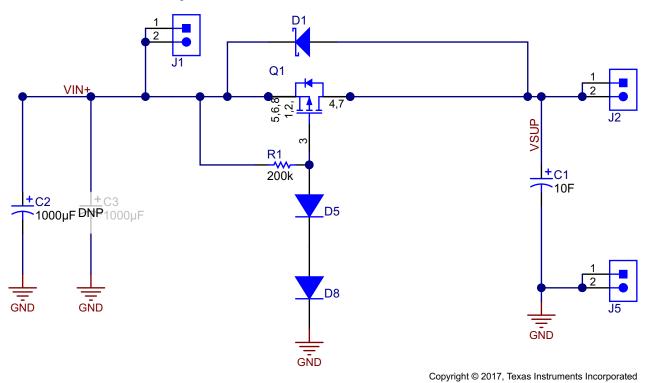

#### 2.3.2 Supercapacitor Charging

The supercapacitor charging circuit is shown in Figure 3. The function of the circuit is limiting the charging current according to the input voltage VIN+. The minimum voltage to charge the supercapacitor is defined by Equation 1:

$V_{IN + MIN} = V_{GS}$  th  $+ 2 \times V_{D}$

Where:

6

- $V_{GS th}$  is the gate-to-source threshold voltage of the P-FET Q1

- $V_{D}$  is the forward voltage of the D5 and D8

Figure 3. Schematic of Supercapacitor Charging Circuit

$V_{GS\_th}$  increases with the current flowing through the MOSFET channel (I\_{DS}). V\_{GS\\_th} is 0.8 V when the P-FET starts to conduct and is approximately 1.3 V when I\_{DS} is 2 A. V\_D also increases with the forward current. V<sub>D</sub> is approximately 0.4 V if several microamps flow through it. Therefore, the minimum voltage to charge the supercapacitor V<sub>IN+ MIN</sub> is 1.6 V. No current flows through Q1 if VIN+ is lower than 1.6 V.

When input current is 2 A, V<sub>GS\_th</sub> will be approximately 1.3 V, so the VIN+ is 2.1 V even the supercapacitor is 0 V. The power loss in Q1 could reach 4 W at this condition. In the PCB layout, make sure the junction temperature of Q1 is not higher than 150°C for this short period.

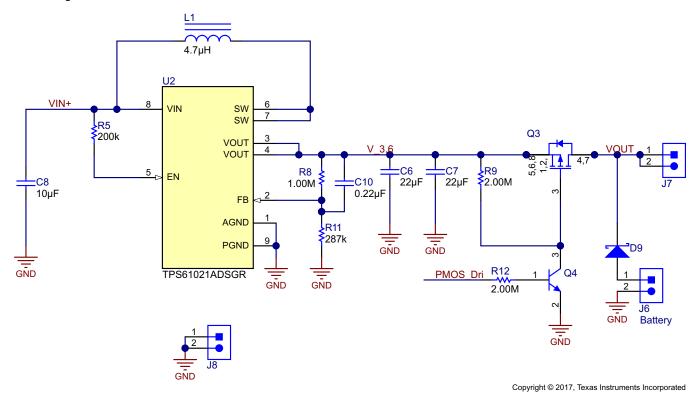

# 2.3.3 Boost Converter Solution

The schematic of the boost converter solution TPS61021A is shown in Figure 4. Most of the external components are selected based on the suggestion in the datasheet. The feed-forward capacitor C10 can help to extend the startup time of the boost converter. Long startup time reduces the inrush input current. This helps the reference design start up easily when the input current from the CT is weak. However, the feed-forward capacitor impacts the stability of the TPS61021A, so the system load current should be not higher than 50 mA.

Figure 4. Schematic of Boost Converter Solution

The P-type MOSFET Q3 and NPN transistor Q4 in Figure 4 closes only when the output voltage of the TPS61021A is higher than 3.3 V. This function is designed to prevent the system loads from operating at a low-voltage condition. Some system loads may consume large current when the voltage is closed to their minimum operating voltage. The large current requirement could cause the startup of the circuit to fail if the input current of the CT is weak. Depending on the performance in real applications, this function can be removed.

The 3.6-V primary battery is connected VOUT rail through a Schottky diode. No current flows out of the battery when the boost converter is working. After the power lines fail and the supercapacitor is out of charge, the Schottky diode starts to conduct and maintain the VOUT voltage at 3.3 V to about 3 V, which is related to the load condition. The Schottky diode can be replaced by a power multiplexer such as TPS211xA family devices for better performance. See Section 3.2 of the TIDA-00998 design guide for more information (TIDUCL5).

### 2.3.4 Supercapacitor Protection Circuit

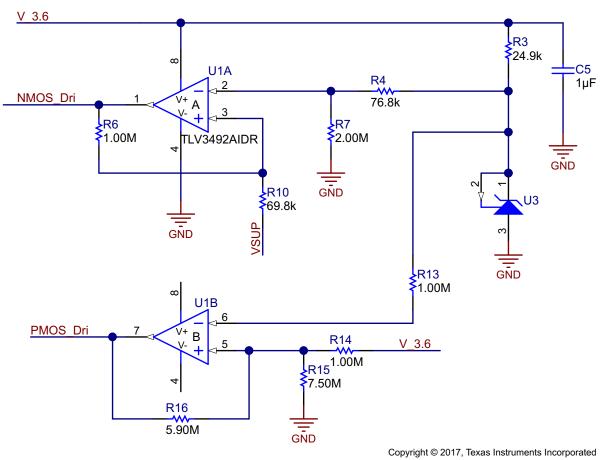

Figure 5 shows the schematic for the supercapacitor protection and system load starting voltage. U3 is a shunt regulator with low quiescent current that provides a 2.5-V reference voltage. U1A is used to drive the Q2 and control the supercapacitor voltage. U1B is used to control the voltage to turn on Q3.

Figure 5. Schematic of Supercapacitor Protection Circuit

The overcharge protection voltage is set by Equation 2, and the recharging voltage is set by Equation 3:  $R_7 = R_7 = R_6 + R_{10}$

$$V_{SUP_{-}OV} = 2.5 \times \frac{1}{R_{4} + R_{7}} \times \frac{1}{R_{6}}$$

$$V_{SUP_{-}OV} = \left(2.5 \times \frac{R_{7}}{R_{4} + R_{7}} - 3.6 \times \frac{R_{10}}{R_{6} + R_{10}}\right) \times \frac{R_{6} + R_{10}}{R_{6}}$$

(2)

(3)

In the U1B circuit of Figure 5, R15 is added to make sure the positive input voltage is lower than the negative input voltage at the beginning of V\_3.6 startup. As defined by Equation 4 and Equation 5, U1B outputs high voltage if the V\_3.6 voltage is higher than V\_3.6\_H; U1B outputs low voltage if the V\_3.6 voltage is lower than V\_3.6\_L.

$$V_{3.6} = 2.5 \times \left( \frac{R_{15} \times R_{16}}{R_{15} + R_{16}} + R_{14} \right) \div \frac{R_{15} \times R_{16}}{R_{15} + R_{16}}$$

(4)

$$V_{3.6}L = 2.5 \times \left(\frac{R_{14} \times R_{16}}{R_{14} + R_{16}} + R_{15}\right) \div R_{15}$$

(5)

# **3 Getting Started Hardware**

The functions of the connectors are described in Table 2.

### **Table 2. Function of Connectors**

| CONNECTORS | DESCRIPTION                                                                  |

|------------|------------------------------------------------------------------------------|

| J1         | Input voltage of the boost converter and the supercapacitor charging circuit |

| J2         | Supercapacitor voltage                                                       |

| J3, J4     | CT input                                                                     |

| J5, J8     | Ground of the supercapacitor                                                 |

| J6         | Primary battery                                                              |

| J7         | Reference design output                                                      |

To demonstrate the energy harvest and the supercapacitor charging circuit function, the primary battery is not attached during the following bench test. Connect J3 and J4 to the secondary side of the CT or simulation current source. Connect the J7 and J8 to the system load. The circuit starts to operate if there is current flowing into J3 and J4.

### 4 Testing and Results

### 4.1 Startup With Supercapacitor Out of Charge

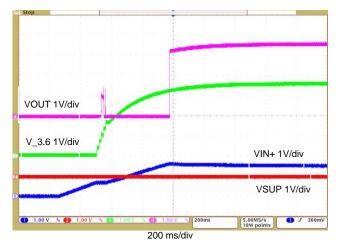

Using a DC current source to simulate the CT and the rectifier, the startup waveform is shown in Figure 6 when the average input current is 3 mA. The supercapacitor voltage is zero, so the reference design is powered by the energy from the CT. The TPS61021 starts operating when the VIN+ reaches 0.9 V. The output voltage of the TPS61021A V\_3.6 ramps up to 3.6 V within one second. The Q3 closes as V\_3.6 reaches 3.3 V, so the VOUT ramps up to 3.3 V quickly and then follows the V\_3.6. At the beginning, VOUT rushes to 1 V for a short period because Q3 conducts when the power for the comparator is not ready. After VOUT is stable at 3.6 V, VIN+ also becomes stable at approximately 1.6 V. This voltage is the minimum amount to charge the supercapacitor.

Figure 6. Startup With 3-mA Input Current and 4-k $\Omega$  Load

### 4.2 Supercapacitor Overvoltage Protection

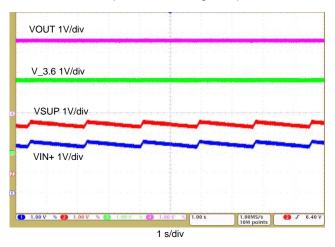

The supercapacitor overcharge voltage and the recover voltage can be simply measured by removing the supercapacitor or applying a large charging and discharging current to the reference design. When the supercapacitor is removed and the input current is 3 mA, the stable waveform is shown in Figure 7. The supercapacitor stops charging when the VSUP reaches 2.6 V. The VSUP starts charging again when the voltage falls below 2.4 V. The VOUT keeps stable during this period.

Figure 7. Overcharge Protection Measurement With 3-mA Input Current

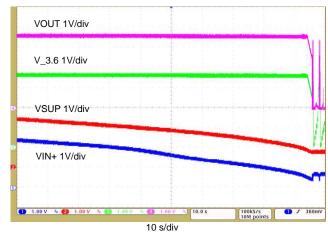

At a 2-A input current condition, the operating waveform is shown in Figure 8. The VSUP slowly drop down to 2.4 V by the 50-mA load, then the 10-F supercapacitor starts charging. The VSUP ramps up quickly because of the large input current. When VSUP reaches 2.6 V, the supercapacitor stops charging. As a result, VSUP decreases toward 2.4 V again. VOUT keeps stable during this period.

|                              | 0 -       | /div       | TUM points            |                 |

|------------------------------|-----------|------------|-----------------------|-----------------|

| 1.00 V 😼 🔁 1.00 V 👒 🌍 1.00 V | • () 1.00 | V V 2.00 s | 500kS/s<br>10M points | <b>2</b> 5 6.40 |

|                              |           |            |                       |                 |

|                              |           |            |                       |                 |

|                              |           |            |                       |                 |

| VIN+ 1V/div                  |           |            |                       |                 |

|                              |           |            |                       |                 |

|                              | 1000      |            |                       |                 |

| VSUP 1V/div                  |           |            |                       |                 |

|                              |           |            |                       |                 |

|                              |           |            |                       |                 |

|                              |           |            |                       |                 |

| V_3.6 1V/div                 |           |            |                       |                 |

|                              |           |            |                       |                 |

| OUT 1V/div                   |           |            |                       |                 |

|                              |           |            |                       |                 |

Figure 8. Overcharge Protection Measurement With 2-A Input Current

# 4.3 Supercapacitor Charging and Discharging

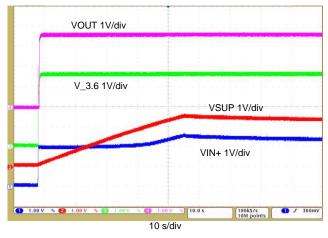

Figure 9 shows the waveform that supercapacitor voltage ramps from 0 to 2.6 V with a 500-mA input current. The supercapacitor voltage stops charging if the voltage reaches 2.6 V. The output voltage keeps stable during the charging period.

Figure 9. Supercapacitor Charging With 500-mA Input Current

Testing and Results

www.ti.com

Figure 10 shows the discharge waveform of the supercapacitor by a 50-mA load at the VOUT after the CT input is removed. The minimum supercapacitor voltage is 0.8 V, at which condition VOUT becomes out of regulation.

Figure 10. Supercapacitor Discharge Waveform With 50-mA Load

# 5 Design Files

# 5.1 Schematics

To download the schematics, see the design files at TIDA-01385.

# 5.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01385.

# 5.3 Layout Prints

To download the layer plots, see the design files at TIDA-01385.

# 5.4 Altium Project

To download the Altium project files, see the design files at TIDA-01385.

# 5.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01385.

# 5.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01385.

# 6 Related Documentation

This design guide did not use any related documentation.

# 6.1 Trademarks

All trademarks are the property of their respective owners.

# 7 About the Author

**JASPER LI** is a power application engineer for the Texas Instruments Boost Converter Solution Group. In this role, he supports worldwide customers, writes application notes, and develops reference designs. Since 2013 his focus has been on ultra-low-power applications. Jasper received his master's degree in power electronics in 2013 at Zhejiang University in China.

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated