# Design Guide: TIDA-01040 **Battery Tester Reference Design for High Current** Applications

# **TEXAS INSTRUMENTS**

# Description

Li-Ion battery formation and electrical testing require accurate voltage and current control, usually to better than ±0.05% over the specified temperature range. This reference design proposes a solution for highcurrent (up to 50 A) battery tester applications supporting input (bus) voltages from 8 V-16 V and output load (battery) voltages from 0 V-5 V. The design utilizes TI's integrated multi-phase bidirectional controller, LM5170, combined with TI's high precision data converters and instrumentation amplifiers to achieve charge and discharge accuracies of 0.01% full scale. To maximize battery capacity and minimize battery formation time, the design uses highly-accurate constant current (CC) and constant voltage (CV) calibration loops with a simplified interface. All key design theories are described guiding users through the part selection process and optimization. Finally, schematic, board layout, hardware testing, and results are also presented.

### Resources

TI E2E

| TIDA-01040                                 | Design Folder  |

|--------------------------------------------|----------------|

| LM5170-Q1, LM2664, TPS709                  | Product Folder |

| LM5118                                     | Product Folder |

| INA188                                     | Product Folder |

| DAC80004                                   | Product Folder |

| ADS131A04                                  | Product Folder |

| TLV07, OPA2227, OPA827, THS4561,<br>LM6142 | Product Folder |

|                                            |                |

Community

ASK Our E2E<sup>™</sup> Experts

#### **Features**

- Battery test subsystem with calibration control achieving 0.01% full scale current control accuracy

- Supports up to 50-A applications with an input voltage (bus) from 8 V-16 V and output load (battery) from 0 V-4.5 V (5 V max)

- LM5170 bidirectional buck, boost controller

- Programmable high-precision reference supplied by DAC80004

- Voltage and current monitoring provided by the ADS131A04 24 bit delta-sigma

- User-friendly control interface ٠

#### Applications

Battery test equipment

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Demand for Li-Ion batteries continues to grow at an exponential pace. Battery formation and testing is an important manufacturing step to maximize battery life and storage capacity requiring multiple charge and discharge cycles. During these cycles, battery current and voltage must be precisely controlled. The TIDA-01040 reference design provides an easy-to-design solution utilizing high accuracy constant current (CC) and constant voltage (CV) calibration loops to achieve up to 0.01% full scale charge and discharge current control accuracy. This solution supports charge and discharge rates of up to 50 A and provides a high-precision DAC and ADC to regulate and monitor the battery voltage and current . Furthermore, the flexible solution provides an option for additional higher current and multi-phase applications.

# 1.1 Li-lon Formation

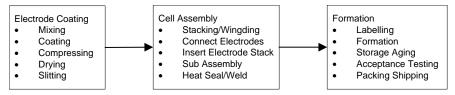

The Li-Ion battery manufacturing process includes electrode production, stack and jelly-roll construction, cell assembly and end-of-line conditioning. Figure 1 shows a simplified Li-Ion battery manufacturing process. Formation and testing at the end-of-line conditioning step are the process bottlenecks, limiting throughput. To maximize battery life, quality and performance, battery test equipment must possess accurate voltage and current control, often better than ±0.05%, over the specified temperature range.

Figure 1. Simplified Li-Ion Battery Manufacturing Process

Some battery test equipment has adopted linear regulators to easily meet the accuracy requirements of formation and testing of batteries used in portable equipment, while compromising on efficiency. On larger batteries, this approach will have challenges with heat management and efficiency. Switching regulators have been widely used in battery test equipment for their better performance in efficiency and heating management.

# 1.2 Li-lon Battery Formation Profile

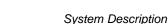

Figure 2 shows the typical Li-Ion battery formation profile which is similar to the battery charging profile. This process can be divided into three phases: initial process, CC, and CV. At first, a small *initial* charge of around 10% of the full-charge current is applied. This prevents the cell from overheating until such a time that it is able to accept the full current of the constant-current phase. In reality, this phase is rarely needed because most modern mobile devices are designed to shut down while there is still some charge left because deep discharge, like overcharging, can damage the cell.

Figure 2. Regular Li-Ion Battery Formation Profile

Then, the battery is typically charged at a CC of 0.5 A. (typical) or less until the battery voltage reaches 4.1 or 4.2 V (depending on the exact electrochemistry). When the battery voltage reaches 4.1 or 4.2 V (typical), the charger switches to a *constant voltage* phase to eliminate overcharging. Superior battery test equipment manages the transition from CC to CV smoothly to ensure maximum capacity is reached without risking damage to the battery. At higher charge current, the transition between CC and CV occurs earlier, because the cell voltage is higher due to the voltage drop across the internal resistance of the cell, and therefore the CV voltage is reached sooner.

# 1.3 Key System Specifications

| Table 1. | Key | System | Specifications |

|----------|-----|--------|----------------|

|----------|-----|--------|----------------|

| PARAMETER                   | SPECIFICATIONS | DETAILS                                                      |

|-----------------------------|----------------|--------------------------------------------------------------|

| V <sub>battery_min</sub>    | 0 V            | Battery-port minimum operating voltage                       |

| V <sub>battery_normal</sub> | 4.2 V          | Battery-port normal operating voltage                        |

| V <sub>battery_max</sub>    | 5 V            | Battery-port maximum operating voltage                       |

| V <sub>bus_min</sub>        | 8 V            | Bus-port minimum operating voltage                           |

| V <sub>bus_normal</sub>     | 12 V           | Bus-port normal operating voltage                            |

| V <sub>bus_max</sub>        | 16 V           | Bus-port normal operating voltage                            |

| F <sub>sw</sub>             | 100 kHz        | Switching frequency                                          |

| I <sub>max</sub>            | 25 A           | Maximum DC current per phase, bidirectional                  |

| I <sub>Total_max</sub>      | 50 A           | Total maximum DC current at battery-port                     |

| Current control accuracy    | 0.01%          | Full-scale current control accuracy for charge and discharge |

### 2 System Overview

# 2.1 Block Diagram

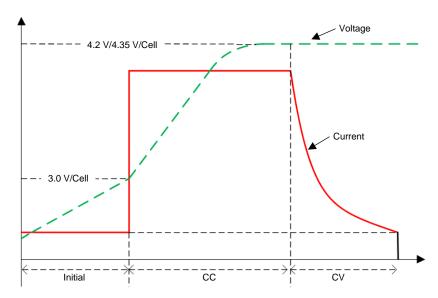

Figure 3. TIDA-01040 Block Diagram

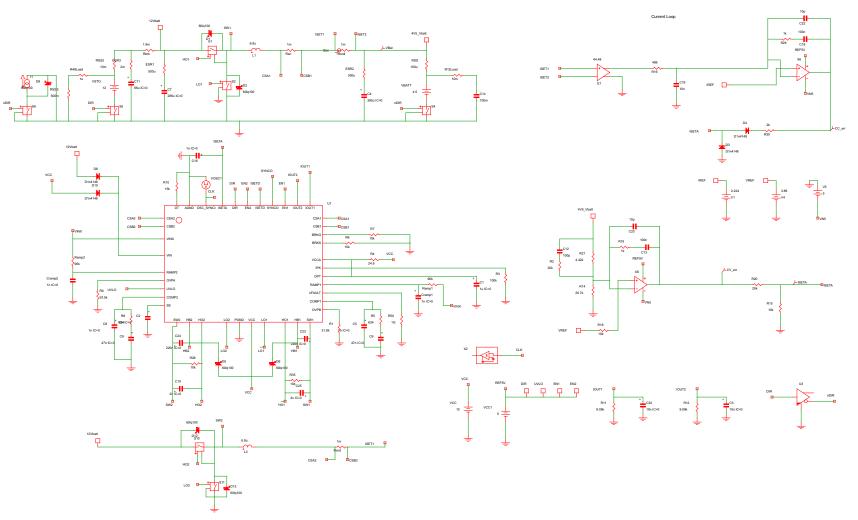

In this reference design, LM5170 is a buck-boost controller which charges or discharges the battery depending on the "DIR" setting. The high precision current sense amplifier monitors the charging or discharging current. SN74LV4053 is a 2-channel CMOS analog multiplexer/demultiplexer which converts the bidirectional signal into a single directional signal. The INA188 device is high-precision instrumentation amplifier which amplifies the cross voltage of the high-precision current sensor with low noise. TLV07 is an error amplifier that compares the battery voltage or bus voltage with the reference control signal. "EN1" and "DIR" signals enable the calibration of the bus voltage in boost mode or the battery voltage in buck mode. Two OPA827 devices operate as buffers between the main control system and data acquisition system. THS4561 is a differential amplifier which converts the single ended measurement signals to differential signals. ADS131A04 is a four-channel, 24-bit delta-sigma ADC which monitors the current and voltage of the battery. DAC80004 is a four-channel, 16-bit high precision DAC that provides reference control signals to the CC and CV control with a two-channel amplifier OPA2277. There is also an onboard TIVA processor that communicates between the ADS131A04 device and the PC.

#### System Overview

# 2.2 Highlighted Products

# 2.2.1 LM5170-Q1 Multiphase Bidirectional Current Controller

The LM5170-Q1 device is a dual-channel, bidirectional, multiphase controller that supports high-current battery test applications up to 200 A using eight phases. It can regulate the average current flowing between the high- and low-voltage ports in the direction designated by the DIR input signal.

Other important features include:

- 5-A peak half-bridge gate drivers which enables the ability to drive high currents

- Programmable oscillator frequency which allows the user to choose the FET switching frequency

- MOSFET failure detect at start-up and circuit breaker control which provides security to the system

### 2.2.2 INA828 Precision Instrumentation Amplifier

The INA828 device is a precision instrumentation amplifier with integrated resistor networks for sensing and data acquisition systems. This device measures and amplifies a differential voltage that represents output current which acts as feedback to regulate current. The INA828 device uses super-beta input transistors which allows for lower input bias current and current noise while also improving input offset voltage and offset drift.

Other important features include:

- Gain drift: 50 ppm/°C (G > 1) which limits the variation of calibration at high temperatures

- Bandwidth: 2 MHz (G = 1), 260 kHz (G = 100) which allows for fast transients

- Inputs protected up to ±40 V which provides protection to the device

- Power-supply rejection: 100 dB, minimum (G = 1) which limits the noise observed on the signal chain

#### Alternatives:

The INA828 device offers lower noise than its predecessor, the INA188 device, but has a narrower bandwidth than the INA821. The INA828 device is pin-to-pin compatible with the SOIC package of the INA188 device.

|                        | INA828   | INA821               | INA188                | INA819               |

|------------------------|----------|----------------------|-----------------------|----------------------|

| Quiescent current      | 0.6 mA   | 0.6 mA               | 1.4 mA                | 350 µA               |

| Noise density at 1 kHz | 7 nV/√Hz | 7 nV/√ <del>Hz</del> | 12 nV/√ <del>Hz</del> | 8 nV/√ <del>Hz</del> |

| Gain error (±)         | 0.15%    | 0.15%                | 0.50%                 | 0.005%               |

| Bandwidth at G = 1     | 2 MHz    | 4.7 MHz              | 0.6 MHz               | 2 MHz                |

#### Table 2. INA828 Alternatives

# 2.2.3 DAC80004 16-bit DAC With 1 LSB INL/DNL

The DAC80004 device is low-power, quad-channel, 16-bit digital-to-analog (DAC) converter. Hexadecimal values are written to the DAC using a computer which produces voltages at two channels. These voltages set the battery voltage charge and discharge rate. The four channels of the DAC80004 are used for the generation of high accuracy, user-defined voltage references.

Other important features include:

- True 16-bit performance: 1 LSB INL/DNL (maximum) which ensures accurate references for current and voltage

- Output buffer with rail-to-rail operation which provides clean references for current and voltage

- 50 MHz, 4- or 3-wire SPI-compatible which allows for simplified user interface

### Alternatives:

The DAC80508 device is an eight channel DAC from the same family as the DAC80004.

|               | DAC80004        | DAC80508        |

|---------------|-----------------|-----------------|

| INL/DNL       | 1 LSB (maximum) | 1 LSB (maximum) |

| # of channels | 4               | 8               |

| Glitch energy | 1 nV-s          | 4 nV-s          |

#### Table 3. DAC80004 Alternatives

### 2.2.4 ADS131A04 24-bit, 128-kSPS, 4-Channel, Simultaneous-Sampling Delta-Sigma ADC

The ADS131A04 device uses four channels to simultaneously and continuously sample voltage or current measurements. The ADC is the front-end of the battery tester and interface with a computer to display voltage and current values in TI's EvaluaTlon software. The ADS131A04 device is well equipped for measuring current and voltage signals due to it being a simultaneous sampling 4-channel converter, with a flexible SPI and data integrity to check and correct single-bit errors during data transmission.

Other important features include:

- Single-channel accuracy: Better than 0.01% at 10,000:1 dynamic range which enables high accuracy data acquisition

- Effective resolution: 20.6 bits at 8 kSPS which allows for high accuracy data acquisition

- Low-drift internal voltage reference: 6 ppm/°C which limits the effects that temperature has on the data acquisition

- Multiple SPI data modes which allows for a simplified user interface

Alternatives:

The ADS131E08 and ADS131E04 devices, predecessors to the ADS131A04, have a lower data rate but implement integrated buffer amplifiers.

|                         | ADS131A04 | ADS131E08 | ADS131E04 |

|-------------------------|-----------|-----------|-----------|

| Data rates<br>(maximum) | 128 kSPS  | 64 kSPS   | 64 kSPS   |

| # of Channels           | 4         | 8         | 4         |

| SNR                     | 115 dB    | 107 dB    | 107 dB    |

### Table 4. ADS131A04 Alternatives

# 2.2.5 Other Highlighted Products

In addition to the key products highlighted in the previous sections, this reference design also showcases the following TI devices:

System Overview

- OPA2277 precision op amp; DAC driver buffer

- OPA827 precision op amp; ADC current and voltage measurement buffers

- TPS709 LDO regulators; 5-V DAQ and control power rails

- TLV07 36-V precision, rail-to-rail output, op amp; CC control amplifier

- THS4561 low-power, 70-MHz, high-supply range, fully differential amplifier; differential signal input for ADC

- LM2664 switched capacitor voltage converter; -5-V power rail

- LM7705 low-noise negative bias generator; -0.2 power rail

- LM5118 non-synchronous buck-boost controller; 10-V power rail

- LM6142 rail-to-rail I/O op amp; CV control amplifier

- SN74LVC1G04 single inverter; boost control logic

- SN74LV1T32 2-input positive OR gate; boost control logic

- SN74LV1T00 2-input positive NAND gate; buck control logic

# 2.3 System Design Theory

#### 2.3.1 Constant Current Control Design

For CC control, a high precision current sensor with low inductance and temperature coefficient is necessary. The WSL2726 and WSLP2726 serial resistors are welded constructions of power metal strips which are ideal for current sensing with 1% tolerance, maximum 75 ppm/°C temperature coefficient, 0.5-nH to 5-nH inductance and less than 20-dB element TCR. See WSL2726 and WSLP2726 for detailed parameters.

A mux is used to manage the bidirectional current when charging or discharging. This design uses the SN74LV4053A, a triple 2-channel analog multiplexer/demultiplexer.

The next stage of the CC control loop chain is a zero-drift instrumentation amplifier INA188. This stage amplifies the current signal across the current sensor with low noise and low output impedance.

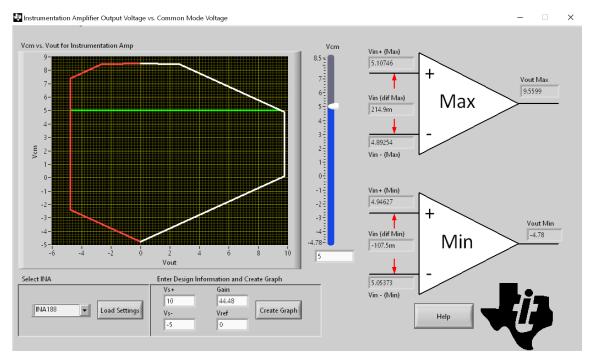

For the instrumentation amplifier, the common-mode voltage affects the input and output range limitation. The *Vcm vs Vout Calculator for Instrumentation Amplifier* design tool enables designers to easily determine the input common-mode and output swing limitations of the chosen instrumentation amplifier to ensure dynamic range and minimize prototyping time.

Figure 4. Vcm vs Vout Calculator for INA188

Figure 4 highlights the calculation results of the INA188 input and output range for this reference design. In this case, the maximum common mode voltage is the same as the maximum voltage on the battery side, so its maximum value is 5 V. When the INA188 is powered by 10 V and –5 V, and the gain is configured at 44.48, the calculation results show the input range is from –107.5 mV to 214.9 mV. It fits within the current signal range ( $\pm$ 50 A × 1 m $\Omega$  =  $\pm$ 50 mV).

The CC control loop needs a high-precision error amplifier to calibrate to the target signal. TLV07 is a low-noise, precision operational amplifier whose maximum offset voltage is less than  $\pm 100 \ \mu$ V and has a 1-MHz bandwidth.

Due to the high current of this application, the high temperature will have an effect on the performance of this board. The input offset voltage drift is a key parameter to consider when choosing the amplifier. The input offset voltage drift of the TLV07 device is only 0.9  $\mu$ V/°C. The maximum input offset voltage at 125°C is: 0.9  $\mu$ V × 125 = 112.5  $\mu$ V. In the worst-case 50-A application, this input offset voltage will cause an error of 112.5  $\mu$ V / (50 A × 0.001 × 44.48) × 100% = 0.005058% on the control loop. This error is less than the 0.01% demanded accuracy, so the TLV07 device is a suitable amplifier.

9

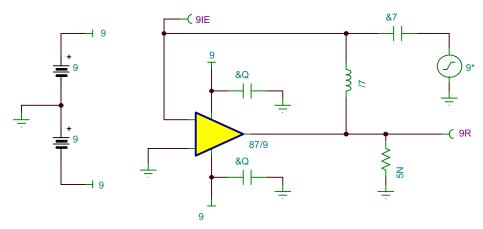

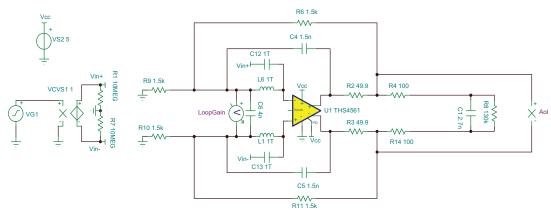

Figure 5. TLV07 TINA-TI Stability Schematic

Figure 5 highlights the schematic used to test the stability of the TLV07 device. The TINA-TI schematic in Figure 5 features a 1TF capacitor and 1TH inductor for simulation purposes. This is used to break the feedback loop as the capacitor will be an open at DC while the inductor is a short. At high frequencies, the inductor will be an open and the capacitor will be a short. The load the TLV07 device experiences at the next stage of the system was also added on the right side of the schematic. This allows for the proper simulation of the stability of the circuit.

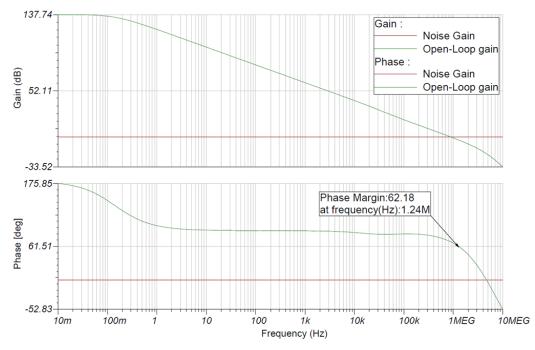

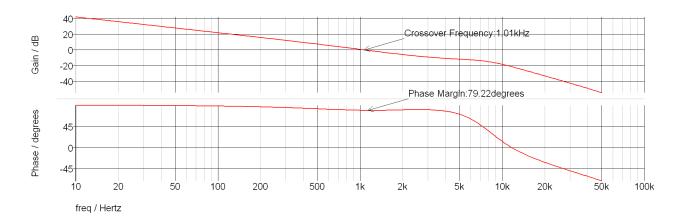

Figure 6. TLV07 TINA-TI Stability Simulation Results

Figure 6 highlights the results from the TLV07 stability simulation including a phase margin of > 62°, which implies stability. It is also important to consider the rate of closure between the loop gain and loaded open-loop gain curves. The loaded open-loop gain curve is decreasing at -20 dB per decade at the point of intersection with the noise gain curve. The noise gain curve is flat, meaning it is at 0 dB per decade. The rate of closure is thus 20 dB per decade. For a circuit to be considered stable, the rate of closure has to be less than 40 dB per decade. For more information about amplifier stability, see *TI's Precision Labs - Op Amps*.

To verify the power stage and control stability, this reference design has adopted SIMetrix®/SIMPLIS® to build simulation modes to verify the control performance.

System Overview

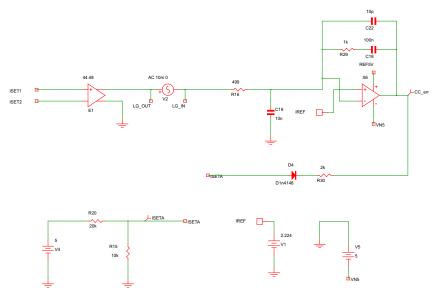

Figure 7 shows the CC control simulation schematic. To keep the system working in CC control mode, V4 provides a DC voltage for D4 to conduct all the time. ISET1 and ISET2 capture the differential voltage across the current sense resistor, E1 is an ideal differential amplifier to output a single-ended signal, R16 and C19 create a low pass filter, and X6 is the error amplifier used to calibrate the current signal to the reference signal.

Figure 7. Constant Current Control Simulation Schematic

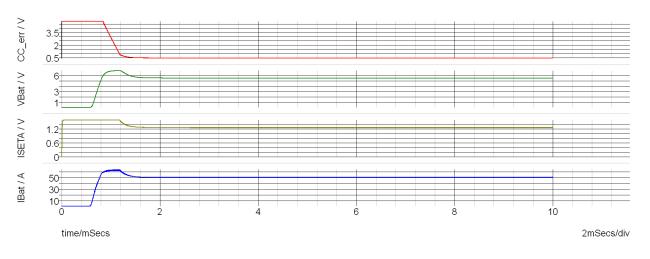

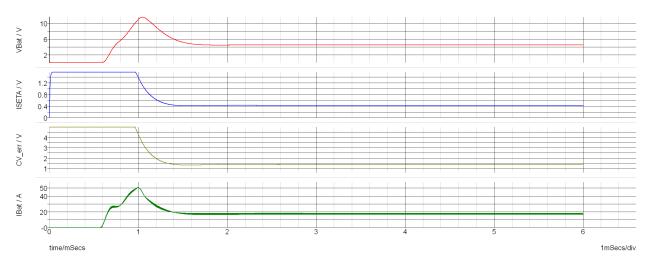

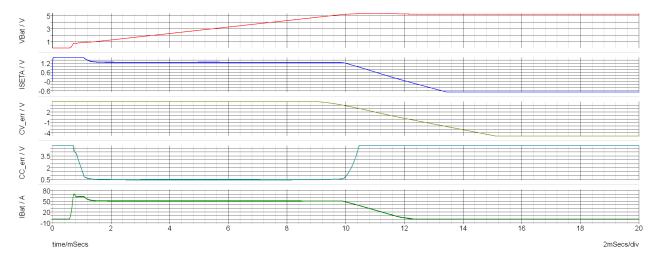

Figure 8 shows the transient simulation result. The "ISETA" pin is clamped to 1.67 V by V4 after power on. With the increase of current, the output of error amplifier X6 decreases, and the CC control circuit takes the control of the system. The final steady current is 50 A, in line with design parameters.

# Figure 8. Constant Current Control Transient Simulation Results

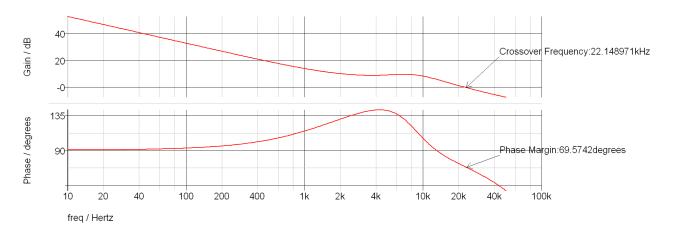

Figure 9 shows the small signal performance of this CC control subsystem. The gain crossover frequency is 22.15 kHz, and the phase margin is 69.57° which means this control circuit is stable and can provide enough bandwidth.

# 2.3.2 Constant Voltage Control Design

For CV control, the bus voltage at boost mode needs to be monitored, so logic control is used to enable the bus side at boost mode or battery side at buck mode. The buck-boost controller uses the "DIR" command pin to set the work mode. This reference design uses the SN74LV1T00 and SN74LV1T32 devices to enable the different voltage sides.

The LM6142 device is dual high-speed and low-power amplifier that is used for calibrating the battery or bus voltage with the reference control signal. The input offset drift is  $3 \mu$ V/°C. At the worst case, 5-V output voltage and 125°C, this drift will case  $3 \mu$ V × 125 / (5 V × 26.7 / 31.12) × 100% = 0.008741157% accuracy error, which can meet the demand of 0.01% accuracy.

System Overview

www.ti.com

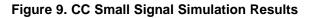

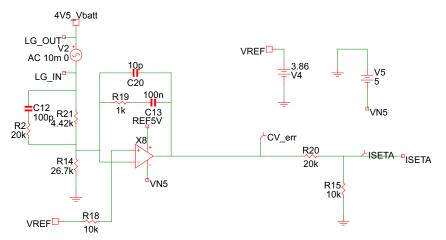

For CV control simulation, remove the current control subsystem. Figure 10 shows the CV control schematic. R20 and R15 determine the maximum DC current of the system, C12, R2, C20, R19, and C13 consist of a type III compensator to provide enough bandwidth and phase margin. See *Demystifying Type II and Type III Compensators Using Opamp and OTA for DC/DC Converters* for design theory details.

Figure 10. Constant Voltage Control Simulation Schematic

Figure 11 shows the transient performance of this subsystem. The final battery voltage is controlled by the reference voltage, as expected.

Figure 11. Constant Voltage Control Transient Simulation Results

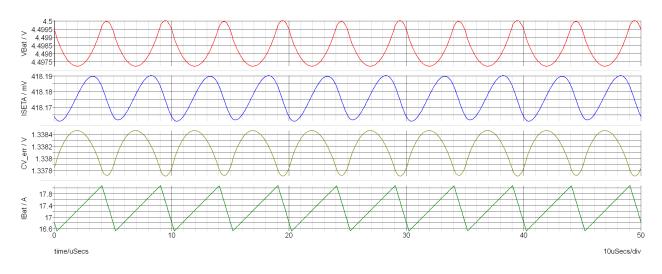

Figure 12 and Figure 13 show the steady state and small signal performance under CV control. The gain crossover frequency is 1.01 kHz, and the phase margin is 79.22°, which means the CV control loop is steady.

Figure 12. CV Steady State Simulation Results

#### System Overview

Figure 13. CV Small Signal Simulation Results

# 2.3.3 System Simulation

Figure 14 shows the whole system simulation schematic. CC control and CV control are connected together with R20, R15, D4 and R30. A battery is simulated with the R12Load and C14.

Figure 14. TIDA01040 System Simulation Schematic

#### System Overview

www.ti.com

Figure 15 shows the transient performance of this system. After power on, due to the low voltage at this time, the CV loop outputs high voltage. It provides enough DC voltage for D4 to conduct, and the CC control loop starts taking control of the whole system at about 2 ms. The current keeps a constant 50 A and the battery voltage increases with time. At about 9 ms, the battery voltage reaches near 4.5 V. After this time, the CV control error amplifier decreases the output voltage and it gets the control of the system. The battery current then decreases and the battery voltage keeps steady after the switch from CC control to CV control.

Figure 15. TIDA01040 System Transient Simulation Results

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Hardware Design

# 3.1.1 Power Bias

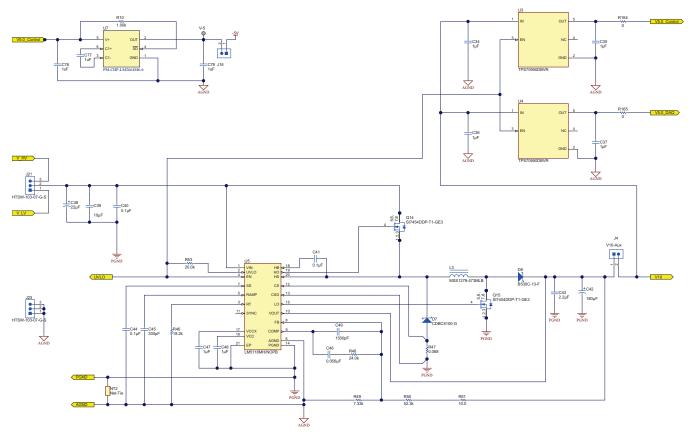

Figure 16 shows the power bias subsystem which supports power for the whole system whether in charge or discharge mode. LM5170 needs a bias voltage of about 10 V, and the amplifiers need ±5 V to calibrate the control signal. The LM5118 device is a wide input, current mode nonsynchronous buck-boost controller which connects to the high- or low-voltage side manually depending on the mode. This is able to provide 10 V for the LM5170 device, LDOs, and switched capacitor voltage converter. In this reference design, U3 and U4 are used to provide isolated 5.0 V to the control subsystem and DAQ subsystem.

Figure 16. Power Bias Subsystem

#### 3.1.2 Main Power Convert Stage

Figure 17 shows the power stage. The power stage can be set to buck or boost mode using the LM5170 device. The two same power stages were connected in parallel to work in higher current applications, as with the parallel MOSFETs. R21, R16, and R22 are high-power current sensing resistors whose temperature coefficients are ±75 ppm/°C. R21 and R22 are used to monitor the current per channel to balance the safety current, while R16 was used to detect the total two phase current to the CC control loop and ADC. The parallel input and output capacitors provide low ESR with enough capacitance. The detailed design guide is found in *LM5170-Q1 Multiphase Bidirectional Current Controller*. This proposed solution can support higher power or current by employing larger inductors, high power MOSFETs, and smaller current sense resistors.

Figure 17. Main Power Convert Stage Subsystem

# 3.1.3 LM5170 Subsystem

Figure 18 shows the LM5170 control schematic. See the *LM5170-Q1 EVM User Guide* and *LM5170-Q1 Multiphase Bidirectional Current Controller Data Sheet* for the detailed design guide. The DIR pin can be used to choose either buck or boost mode. The FB pin delivers the control signal from the CC and CV control loops to the LM5170 device. The SYNCOUT pin, OPT pin, and SYNCIN pin can be used for further multiphase applications.

Figure 18. LM5170 Subsystem

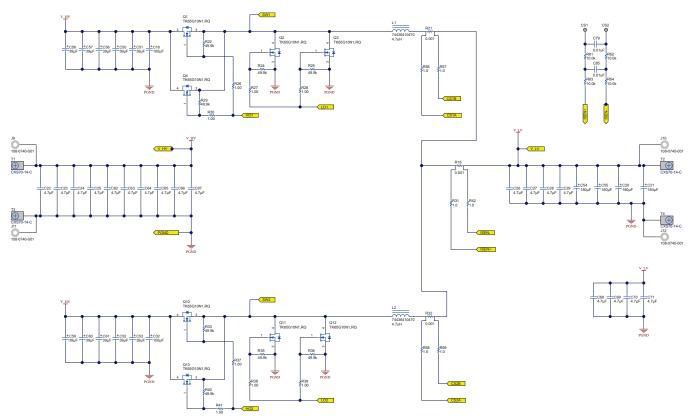

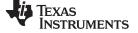

#### 3.1.4 CC Calibration Subsystem

Figure 19 shows the CC calibration subsystem. The SN74LV4053 device converts the bidirectional current to one direction to be used in the CC control loop. When the DIR pin is high, the whole system works in buck mode. The current flows from "ISEN+" to "1-COM" to "1Y1" to "INA188" to "2Y1" to "2-COM" to "ISEN-". Otherwise in boost mode, the current flows from "ISEN-" to "2-COM" to "2Y0" to "INA188" to "1Y0" to "1-COM" to "ISEN+". INA188 is a zero-drift, rail-to-rail-out instrumentation amplifier, that converts the voltage from the current sensing resistor to a proper value. The gain of the CC control loop is  $(1 + 2 \times 25 \text{ k}\Omega / \text{R70}) = 44.48$ . R71 and C110 form a low-pass filter which can filter significant switching noise from the MOSFETs. The output signal from the filter is compared with the current reference signal through an error amplifier with compensation. At power up, the battery voltage is very low. The CV calibration loop outputs a high voltage to the FB pin. At this time, D3 starts to conduct and the CC calibration loop takes control of the whole system.

Figure 19. CC Calibration Subsystem

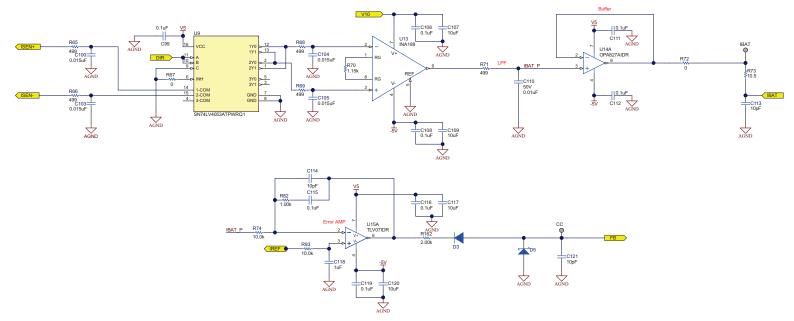

### 3.1.5 CV Calibration Subsystem

Figure 20 shows the battery-side CV calibration subsystem. It needs to monitor the battery side in buck mode and the bus side in boost mode. The logic components U10, U11, and U12 are controlled by the EN1 and DIR signal from the LM5170 device. U2 is a dual-channel high-speed rail-to-rail amplifier which acts as an error amplifier to calibrate the terminal voltage to the reference voltage. When the system works in buck mode, with the increase of the battery voltage, the CV calibration loop starts taking control of the whole system to keep the battery voltage equal to the VREF voltage. Q16 is opened by the startup command (EN and DIR), which allows the VREF signal to rise up slowly. Adjust R84 and C90 values to set the REF ramp up rate which affects the inrush current after power on.

Figure 20. CV Calibration Subsystem

Hardware, Software, Testing Requirements, and Test Results

www.ti.com

Figure 21 shows the system soft start waveform with R84 = 1 M $\Omega$ , C90 = 10  $\mu$ F, and the current setting = 10 A. This result shows that the reference voltage ramps up slowly causing the "ISETA" signal to ramp up slowly as well. This soft start circuit has sharply decreased the inrush current at power on.

Figure 21. Soft Start Waveform

There is another software method to achieve this soft start performance: increasing the voltage reference signal slowly at power on instead of giving the final reference voltage immediately.

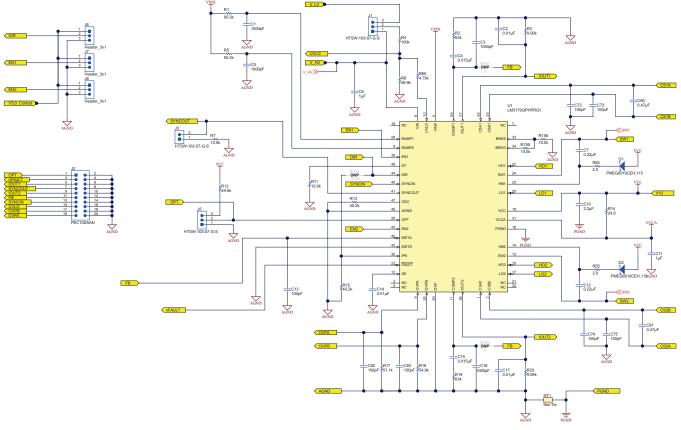

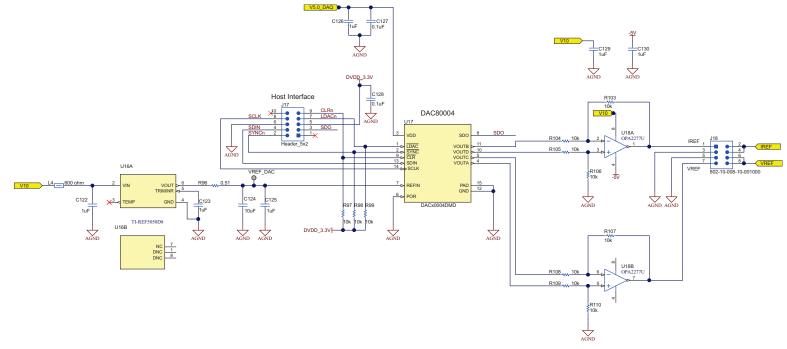

#### 3.1.6 DAC Subsystem

Figure 22 shows the DAC subsystem, which provides the reference signals for the CC and CV calibration subsystem. The DAC80004 device is a high-accuracy, low power 16-bit DAC. It can be controlled through the USB2ANY interface. The REF5050 device has great noise performance which provides a 5-V reference voltage for DAC. The OPA2277 device is a high-precision, low-noise amplifier which works as a buffer and changes the output range of the DAC subsystem.

In this schematic, all four channels are connected to the amplifiers to be used to calibrate the offset voltage of the amplifier to achieve better calibration performance. In real applications, only two channels can be used to provide voltage and current reference control signals.

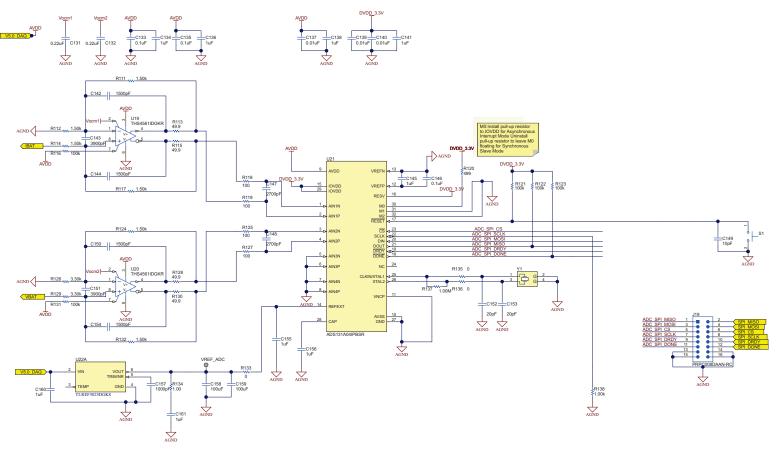

# 3.1.7 DAQ Subsystem

Figure 23 shows the DAQ subsystem that consists of the ADS131A04, THS4561, and REF5025 devices. The THS4561 device can convert the single-ended signal of the battery current and voltage to differential signals and provide suitable gain to drive the ADC. The ADS131A04 device is a 24-bit, 128-kSPS delta-sigma ADC that allows battery parameters to be viewed in the GUI. It uses an onboard MCU, TIVA4, to communicate with the GUI.

Figure 24 shows how the full driver-ADC subsystem stability simulations are performed.

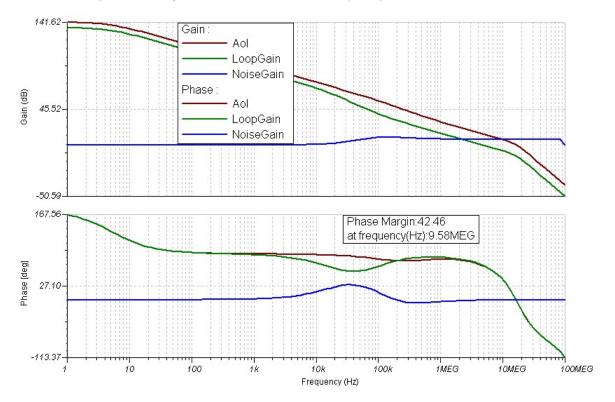

Figure 24. THS4561 Stability Simulation Schematic

Figure 25 shows the simulation results of the THS4561 stability. It shows that the crossover frequency is about 9.58 MHz, and the phase margin is about 42.46°. These are indications of a stable circuit. To learn more about amplifier stability, see *TI's Precision Labs - Op Amps*.

Figure 25. THS4561 Stability Simulation Results

#### Hardware, Software, Testing Requirements, and Test Results

www.ti.com

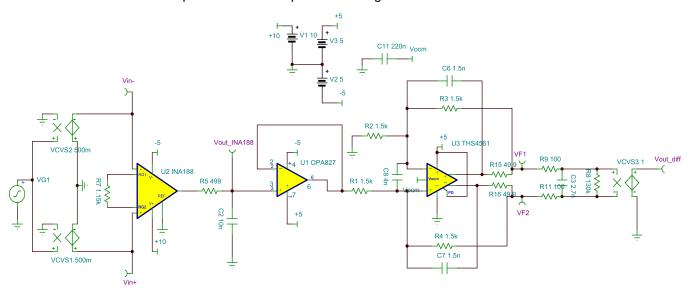

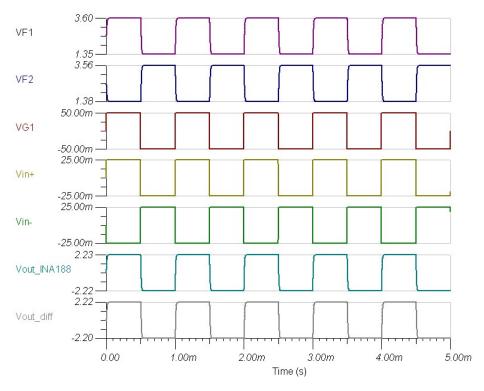

Transient response simulations are also completed for the THS4561 and INA188 stage to further ensure the proper functionality of this stage. Figure 26 shows the output of a 50-mV peak-to-peak, 1-kHz square wave that is put into the circuit. Figure 27 displays the results of the transient response of this analog front end stage. As seen, the output is a 2.2-V square wave, which corresponds to the expected gain of 44.48. There is no oscillation present on the output so this stage is considered stable.

Figure 27. TIDA-01040 AFE Transient Results

# 3.2 Software Design

# 3.2.1 DAC

This reference design uses the USB2ANY interface adapter to communicate with the DAC80004 device to generate a reference signal for current and voltage control. First, open the USB2ANY Explorer, click Select Interface to choose the SPI, then click the 3.3V ON button. Click the SPI tab above the Activity Logging section. If the SPI tab does not appear, click around the words "Activity Logging" as sometimes the tabs are hidden. Configure the GUI parameters as shown in Figure 28.

| USB2ANY Explorer v2.7.0.5 (API v2.7.0.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 🗆 ×             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Adapter connection<br>Type: USB2ANY Rev: Serial #: CA7C1B511A001A00 Firmware Version: 2.7.0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Close Device      |

| Clock Polarity       Clock Phase       CS Polarity       Bit Direction       Length <ul> <li>Inactive Low</li> <li>Trailing Edge</li> <li>Active High</li> <li>Leading Edge</li> <li>Active Low</li> <li>MSB First</li> <li>8 Bits</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Select Interfaces |

| Bit Rate     Slave Device     CS Type       100     KHz     1 $\stackrel{\circ}{\checkmark}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| MOSI Message / Data<br>Write data: 4:4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3V ON           |

| 02 F0 00 00<br>4 bytes<br>Vite/Read<br>4 bytes<br>Vite/Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.0V OFF          |

| Read data:       00 00 00 00       Load         Save       Clear Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Log Comment       |

| Activity Log:         Timestamp       Mo       R       Len       Data/Message         2018-05-14        SPI         SPI bit rate set to 100.000 kHz.         2018-05-14        INFO         Target Power: 3.3v is ON, 5.0v is OFF, Adj is OFF         2018-05-14        SPI         Target Power: 3.3v is ON, 5.0v is OFF, Adj is OFF         2018-05-14        SPI         SPI write/read count set to 4         2018-05-14        SPI         SPI bit rate set to 100.000 kHz.         2018-05-14        SPI       write/read count set to 4       2018-05-14       SPI         2018-05-14        SPI       write/read count set to 100.000 kHz.       2018-05-14       SPI         2018-05-14        SPI       write/read count set to 100.000 00       2018-05-14       A Data: 02 F0 00 00         2018-05-14        SPI       mile       Target Power: 3.3v is ON, 5.0v is OFF, Adj is OFF         2018-05-14        INFO         Target Power: 3.3v is ON, 5.0v is OFF, Adj is OFF         2018-05-14        I | <u> </u>          |

Figure 28. USB2ANY Configuration

The DAC80004 commands are found in the DACx0004, Quad 16-,14-,12-Bit, 1 LSB INL, Buffered, Voltage-Output Digital-to-Analog Converters Data Sheet.

### 3.2.2 ADC

In this reference design, the *Delta-Sigma ADC Evaluation Software* is used to communicate with the ADS131A04 device. See the *Delta-Sigma ADC EvaluaTion Software User's Manual* and *ADS131A04 Evaluation Module User's Guide* for detailed information.

After launching this software, click the *Scripts* menu, then click *Predefined* and choose *Basic startup with Datarate* @ 8kSPS as Figure 29 shows. Finally, click the *Run* button at the right side of the window.

| 🖾   & 🗉 🖽   =                                                                  | Delta-Sigma ADC EvaluaTIon Software - ADS131A04                                                             | - 0 ×                                                                  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| File Device Scripts Console                                                    |                                                                                                             | ۵                                                                      |

| € Import<br>Save Secan Predefined<br>Basic startup with Datarate @ 8kSPS [pts] | Tools Additional Data User<br>Interfaces Analysis Guide                                                     | <ul> <li>Datasheet</li> <li>E2E Forum</li> <li>Collateral -</li> </ul> |

| Basic startup 8kSPS                                                            |                                                                                                             |                                                                        |

|                                                                                | inning, reads back all the registers, sets datarate to 8kSPS and enables all the ADCs (for data collection) |                                                                        |

| UNLOCK<br>Unlock the device                                                    |                                                                                                             | 💽 Run                                                                  |

| WREG OD 02<br>Set ICLK Divider to 2                                            |                                                                                                             | 🖲 Step                                                                 |

| WREG OE 48<br>Set MODCLK Divider to 4 and OSR = 256                            |                                                                                                             | 🦳 Reset                                                                |

| WAKEUP<br>Wakeup the device                                                    |                                                                                                             |                                                                        |

| WREG OF OF<br>Enables all ADCs                                                 |                                                                                                             |                                                                        |

| <b>REGMAP</b><br>Reads back all of the user control registers                  |                                                                                                             |                                                                        |

|                                                                                |                                                                                                             |                                                                        |

| Script Editing                                                                 |                                                                                                             |                                                                        |

| Sending USB>> ID<br>ADS131A04 Mar/ 9/2016/14:32:08<br>Sending USB>> UNLOCK     |                                                                                                             | 4 111 >                                                                |

The second step is to set the register of the ADC. Figure 30 shows the setting with an external reference voltage. It also can modify clock settings and OSR settings.

| 88            | - 10             |                                                                         |              |   | Delta | -Sigr | na AD | C Ev | aluaTl     | on S  | oftw  | /are · | ADS131A04         | - 0                              | ×       |

|---------------|------------------|-------------------------------------------------------------------------|--------------|---|-------|-------|-------|------|------------|-------|-------|--------|-------------------|----------------------------------|---------|

| File          | Device           | Scripts Console                                                         |              |   |       |       |       | _    |            | _     | _     | _      |                   |                                  | ۵       |

| Save<br>Regis | Load             | Tools Additional Data<br>• Interfaces • Analysis<br>Application Clients |              |   |       |       |       |      |            |       |       |        | Use<br>Guid       | er as eze Forum                  |         |

| ADS131/       | A04 Register I   | Мар                                                                     |              |   |       |       |       |      |            |       |       |        | Register Controls |                                  | _       |

| Address       | Register Nam     | ne Current                                                              | Default      | 7 | 6     | 5     | 4 3   |      | 2 1        | C     | 4     | a.     | VNCPEN Ne         | egative Charge Pump powered down | <b></b> |

| 0x00<br>0x01  | ID_MSB<br>ID_LSB | 0x04<br>0x03                                                            | 0x00<br>0x00 | 0 | 0     | 0     | 0 0   |      | 1 0<br>0 1 |       |       |        | HRM Hig           | gh Resolution mode Y             |         |

| 0x02          | STAT_1           | 0x10                                                                    | 0x00         | 0 | 0     | 0     | 1 0   |      | 0 0        |       |       |        | VREF_4V VR        | REFP set to 2.442V Y             |         |

| 0x03<br>0x04  | STAT_P<br>STAT_N | 0x0C<br>0x0C                                                            | 0x00<br>0x00 | 0 |       |       | 0 1   |      | 1 0<br>1 0 |       |       |        | INT_REFEN Ext     | ternal reference voltage         |         |

| 0x04<br>0x05  | STAT_N<br>STAT_S | 0x00                                                                    | 0x00         | 0 |       |       | 0 0   |      | 0 0        |       |       |        | COMP_TH Hig       | gh-side = 95%, Low-side = 5%     |         |

| 0x06          | ERROR_CNT        | 0x00                                                                    | 0x00         | 0 | 0     | 0     | 0 C   |      | 0 0        | C     |       |        |                   |                                  |         |

| 0x07          | STAT_M2          | 0x01                                                                    | 0x00         | 0 | 0     | 0     | 0 0   |      | 0 0        | 1     |       |        |                   |                                  |         |

| 0x0B          | A_SYS_CFG        | 0x60                                                                    | 0x60         | 0 | 1     | 1     | 0 0   |      | 0 0        | C     |       |        |                   |                                  |         |

| 0x0C          | D_SYS_CFG        | 0x3C                                                                    | 0x3C         | 0 | 0     | 1     | 1 1   |      | 1 0        |       |       |        |                   |                                  | Ŧ       |

| 0x0D          | CLK1             | 0x08                                                                    | 80x0         | 0 | 0     |       | 0 1   |      | 0 0        |       |       |        |                   |                                  |         |

| 0x0E          | CLK2             | 0x8B                                                                    | 0x86         | 1 | 0     |       | 0 1   |      | 0 1        | 1     |       |        |                   |                                  |         |

| 0x0F          | ADC_ENA          | 0x0F                                                                    | 0x00         | 0 |       |       | 0 1   |      | 1 1        | 1     |       |        |                   |                                  |         |

| 0x11          | ADC1             | 0x00                                                                    | 0x00         | 0 |       |       | 0 0   |      | 0 0        |       |       |        |                   |                                  |         |

| 0x12          | ADC2             | 0x00                                                                    | 0x00         | 0 |       |       | 0 0   |      | 0 0        |       |       |        |                   |                                  |         |

| 0x13          | ADC3             | 0x00                                                                    | 0x00         | 0 |       |       | 0 0   |      | 0 0        |       |       |        |                   |                                  |         |

| 0x14          | ADC4             | 0x00                                                                    | 0x00         | 0 | 0     |       | 0 0   |      | 0 0        |       |       |        |                   | Refresh/Sync Write Defaults      |         |

|               |                  |                                                                         |              |   |       |       | lnac  | tive | 01         | /lodi | tying | 3      |                   | Merresily synce Write Deraults   |         |

| 🕞 Regi        | ister Decode I   | nformation                                                              |              |   |       |       |       |      |            |       |       |        |                   |                                  |         |

Figure 30. ADC Register Setting

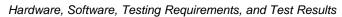

After setting the GUI and registers, the software can now capture the data: click the *Data Analysis* menu, choose "ADC0" and "ADC1", change the *Clock* and *VRef (V)*, then click the *Collect Data* button as Figure 31 shows.

| File           | Dat     | ta Analysis | Analysis Eng | ine for Deita-Sigma ADC Evalua i lon Software |           | — Ц        | ×                |

|----------------|---------|-------------|--------------|-----------------------------------------------|-----------|------------|------------------|

| Save I<br>As   | Data Lo | ad          |              |                                               |           | -          |                  |

| Data Inspector | Count   | ADC0        | ADC1         |                                               |           | ● 🗸 ADC0   | ,                |

| spe            | 0       | 785540      | 4833528      |                                               |           | _          |                  |

| talr           | 1       | 785585      | 4833521      |                                               |           | O 🗸 ADC1   |                  |

| Da             | 2       | 785694      | 4833460      |                                               |           | O ADC2     |                  |

| Time Domain    | 3       | 785350      | 4833453      |                                               |           | _          |                  |

| Dor            | 4       | 785308      | 4833441      |                                               |           | O ADC3     | 1                |

| lime           | 5       | 785038      | 4833424      |                                               |           |            |                  |

|                | 6       | 785084      | 4833431      |                                               |           |            |                  |

| Histogram      | 7       | 785061      | 4833406      |                                               |           |            |                  |

| Histo          | 8       | 785339      | 4833491      |                                               |           |            |                  |

| -              | 9       | 785498      | 4833504      |                                               |           |            |                  |

|                | 10      | 785138      | 4833436      |                                               |           |            |                  |

|                | 11      | 785444      | 4833520      |                                               |           |            |                  |

|                | 12      | 785573      | 4833503      |                                               |           | EVM Parame | ters             |

|                | 13      | 785446      | 4833443      |                                               |           | Clock (Hz) | _                |

|                | 14      | 785401      | 4833511      |                                               |           | 163840     | 000              |

|                | 15      | 785203      | 4833498      |                                               |           | VRef (V)   |                  |

|                | 16      | 785321      | 4833554      |                                               |           |            | 2.5 🜩            |

|                | 17      | 785576      | 4833543      |                                               |           |            |                  |

|                | 18      | 785326      | 4833515      |                                               |           |            |                  |

|                | 19      | 785233      | 4833443      |                                               | -         | Collect D  | ata              |

|                |         | 705//0      | 1000 100     | Hex Dat                                       | a Display |            | 48 韋<br>'samples |

Figure 31. ADC GUI Collect Data

The raw data is shown on the GUI, but the mean value of current and voltage is needed.

Figure 32. ADC GUI Data Analysis

Figure 32 shows the mean value on the bottom after analysis, but this is the full scale format. Divide by 8388607 (DEC of 0X7FFFF), and multiply by "VRef", then the real current and voltage signal is obtained as Equation 1 and Equation 2 show. This example was tested under CC control: the control current is 5 A, the battery voltage is 3.1 V.

$$ADC_{current} = \frac{ADC0_{Mean}}{8388607} \times V_{Ref} = \frac{785343.6}{8388607} \times 2.5 \quad V = 234.05 \quad mV$$

$$ADC_{voltage} = \frac{ADC1_{Mean}}{8388607} \times V_{Ref} = \frac{4833489.7}{8388607} \times 2.5 \quad V = 1.4405 \quad V$$

(1)

(2)

The expected value of channel 0 should be (Iset × Rcs × Gain\_INA188 × Gain\_ADC0) = 5 A × 1 m $\Omega$  × 44.48 × 1 = 222.4 mV, and the expected value of channel 1 should be (Vset × Gain\_ADC1) = 3.1 V × (1.5 k/3.30 k) = 1.4091 V. Those values are close to the mean value from the histograms. Due to the offset and noise of the components, refer to Section 3.3.3.4 to calibrate the ADC. The result is a more accurate value.

# 3.3 Testing and Results

# 3.3.1 Getting Started Hardware

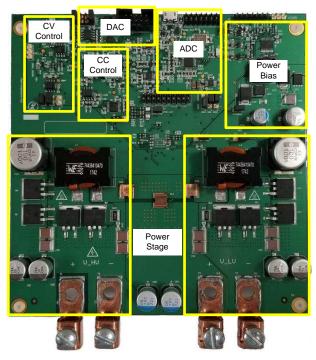

This section gives brief information to set up and run the board. Figure 33 shows the sections of the board.

Figure 33. TIDA-01040 Hardware

This system has some configuration options. Table 5 highlights the purpose of each jumper as well as the default configurations.

| HEADER | SIGNAL    | PINS        | FUNCTION DESCRIPTION                            | DEFAULT |

|--------|-----------|-------------|-------------------------------------------------|---------|

| J1     | UVLO      | (1,2)       | Enable from V_HV                                | Y       |

|        |           | (2,3)       | Enable from V_LV                                |         |

| J3     | SYNCOUT   | (1,2)       | Clock output for multiphase configuration       | Y       |

| J4     | V10-Aux   | (1,2)       | Auxiliay power                                  | Y       |

| J5     | OPT       | (1,2)       | Multiphase configuration                        |         |

|        |           | (2,3)       | No Multiphase configuration                     | Y       |

| J6     | DIR       | (1,2)       | BUCK mode                                       | Y       |

|        |           | (2,3)       | BOOST mode                                      |         |

| J7     | EN1       | (1,2)       | Onboard CH-1 enable                             |         |

|        |           | (2,3)       | Onboard CH-1 disable                            | Y       |

| J8     | EN2       | (1,2)       | Onboard CH-2 enable                             |         |

|        |           | (2,3)       | Onboard CH-2 disable                            | Y       |

| J14    | V5        | (1,2)       | Enable power supply for CC control              | Y       |

| J18    | IREF/VREF | (1,2),(7,8) | Enable DAC output signal for CC/CV control loop | Y       |

| J34    | V_HV      | (1,2)       | Enable CV control for bus voltage(V_HV)         | N       |

| J35    | V_LV      | (1,2)       | Enable CV control for battery voltage(V_LV)     | Y       |

| J37    | V5A       | (1,2)       | Enable power supply for CV control              | Y       |

#### **Table 5. Jumper Configuration**

Battery Tester Reference Design for High Current Applications 31

#### 3.3.2 Test Setup

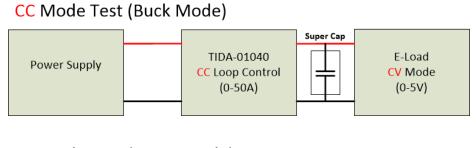

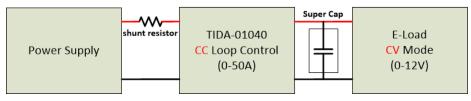

The test setup for a bidirectional charge and discharge converter requires a different setup for current and voltage control loop tests. Figure 34 shows a block diagram of the hardware setup for the TIDA-01040 current control loop test.

# CC Mode Test (Boost Mode)

Figure 34. Current Control Test Block Diagram

The power supply must be able to provide enough power in both charge and discharge mode. Configure the TIDA-01040 board to BUCK or BOOST mode through the "DIR" header (J6). Then set current and voltage control signals to control loop. Configure the electronic load to operate in CV mode whose value should be smaller than the voltage set by the DAC. The CV control loop will give enough forward voltage for D3, and the system can work in CC mode. The super capacitor is required to clamp the output voltage and simulate the battery performance.

The reason for connecting a shunt resistor in BOOST mode is for monitoring the current flow out from the battery (discharging current). In BUCK mode, it is easy to read the current flow into battery (charging current) on the electronic load.

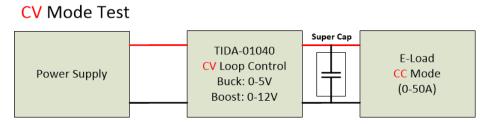

Figure 35 shows the block diagram of the hardware setup for the TIDA-01040 voltage control loop test.

Figure 35. Voltage Control Test Block Diagram

When testing the CV control performance, configure the system to work in CV mode. Configure the electronic load to operate in CC mode with a value smaller than the current value set by DAC.

#### 3.3.3 Test Results

#### 3.3.3.1 Current Control Accuracy

The current accuracy depends on the current sensing resistor, the gain, offset, and drift of the current amplifier, INA188, and TLV07 devices. These parameters vary from device to device. To achieve good current control accuracy, the total gain and the offset of the designed circuit must be calibrated. Because high temperature effects the drift of some device in the system, the relationship between the current control signal and the real output current is not linear. Three point data is used to calibrate the CC control considering the drift in a high current situation. In buck mode, the battery current is 5.479 A if the DAC current reference signal code is 3229(DEC). The battery current is 34.932 A if the DAC current reference signal code is 20522(DEC), and the battery current is 49.942 A if the DAC current reference signal code is 29360(DEC). From these three test results, the real gain and offset can be calculated as follows:

$$Gain1 = \frac{(I_{out2} - I_{out1})}{(DAC_{code2} - DAC_{code1})} = \frac{34.932 \ A - 5.479 \ A}{20522 - 3229} = 0.001700225 \ A$$

(3)

Offset1 =  $I_{out1} - Gain1 \times DAC_{code1} = 5.479 \ A - 0.001700225 \ A \times 3229 = -0.011026958 \ A$

(4)

$$Gain 2 = \frac{(I_{out3} - I_{out2})}{(DAC_{code3} - DAC_{code2})} = \frac{49.942 \text{ A} - 34.932 \text{ A}}{29360 - 20522} = 0.001704133 \text{ A}$$

(5)

$Offset2 = I_{out2} - Gain2 \times DAC_{code2} = 34.932 \quad A - 0.001704133 \quad A \times 20522 = -0.091333333 \quad A \tag{6}$

The current accuracy in boost mode can be calibrated with the same method. Using the gain and offset, the output current value can be determined and compared to the actual test output current.

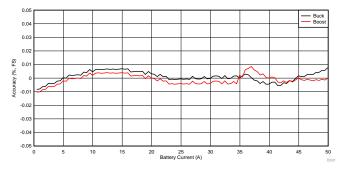

Figure 36 shows the full scale (FS) CC control accuracy of this reference design at buck (high side is 12 V, low side is 1 V) and boost (low side is 2 V, high side is 10 V) mode conditions. The output is controlled within 0.01% in the whole range.

Figure 36. CC Control Accuracy

To know the whether a change in voltage has any effect on the CC control accuracy, Table 6 shows test current under different battery voltage and different current settings. The tested data shows that the voltage setting has very little effect on the current control.

|                          | I <sub>SET</sub> |        |       |        |        |  |  |  |  |

|--------------------------|------------------|--------|-------|--------|--------|--|--|--|--|

| V <sub>Battery</sub> (V) | 10 A             | 20 A   | 30 A  | 40 A   | 50 A   |  |  |  |  |

| 0.5                      | 9.976            | 19.966 | 29.96 | 39.958 | 49.968 |  |  |  |  |

| 1                        | 9.976            | 19.966 | 29.96 | 39.958 | 49.968 |  |  |  |  |

| 1.5                      | 9.976            | 19.966 | 29.96 | 39.958 | 49.968 |  |  |  |  |

| 2                        | 9.976            | 19.966 | 29.96 | 39.958 | 49.97  |  |  |  |  |

| 2.5                      | 9.976            | 19.966 | 29.96 | 39.958 | 49.97  |  |  |  |  |

| 3                        | 9.976            | 19.966 | 29.96 | 39.958 | 49.97  |  |  |  |  |

| 3.5                      | 9.976            | 19.966 | 29.96 | 39.958 | 49.972 |  |  |  |  |

| 4                        | 9.976            | 19.966 | 29.96 | 39.958 | 49.972 |  |  |  |  |

| 4.5                      | 9.976            | 19.966 | 29.96 | 39.958 | 49.972 |  |  |  |  |

Table 6. CC Control with Different Battery Voltage

|                          | I <sub>SET</sub> |        |       |        |        |

|--------------------------|------------------|--------|-------|--------|--------|

| V <sub>Battery</sub> (V) | 10 A             | 20 A   | 30 A  | 40 A   | 50 A   |

| 5                        | 9.976            | 19.966 | 29.96 | 39.958 | 49.973 |

Table 6. CC Control with Different Battery Voltage (continued)

# 3.3.3.2 Voltage Control Accuracy

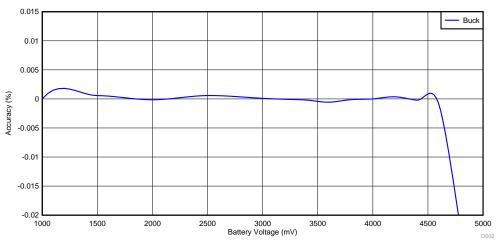

The voltage control accuracy of this system depends on the gain offset, offset of the resistor division, and the LM6142 device. This also requires calibration to achieve good voltage control accuracy. Because the voltage control subsystem is far away from the main power stage, use a simplified two points calibration method to calibrate the gain as Equation 7 and Equation 8:

$Gain = \frac{(V_{out2} - V_{out1})}{(DAC_{code2} - DAC_{code1})} = \frac{3996.49 \text{ mV} - 998.79 \text{ mV}}{44982 - 11245} = 0.088854966 \text{ mV}$ (7)

$Offset = V_{out1} - Gain \times DAC_{code1} = 998.79 \text{ mV} - 0.088854966 \text{ mV} \times 11245 = -0.3840967 \text{ mV} \tag{8}$

After calibration, the calculated output voltage can be compared with the actual test output voltage. Figure 37 shows the accuracy of CV control at buck mode (high side 12 V, output current 10 A).

Figure 37. CV Control Accuracy

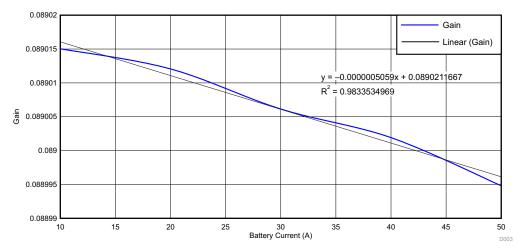

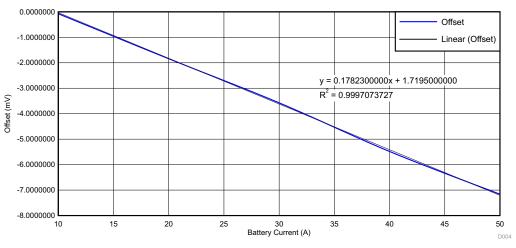

To determine whether the CV control accuracy will change with different current conditions, these conditions must be tested. Table 7 shows the different calibrated gain and offset values at different currents.

| CURRENT (A) | GAIN        | OFFSET       |

|-------------|-------------|--------------|

| 10          | 0.089015028 | -0.073989981 |

| 20          | 0.089012064 | -1.840658624 |

| 30          | 0.089006136 | -3.57399591  |

| 40          | 0.089001921 | -5.484399232 |

| 50          | 0.088994807 | -7.164402077 |

#### Figure 38 and Figure 39 show the linear relationship between gain and offset with current.

Use the equations in Figure 38 and Figure 39 to get the new gain and offset values under different currents. Table 8 shows some sample values.

| CURRENT (A) | GAIN        | OFFSET  |

|-------------|-------------|---------|

| 10          | 0.089016108 | -0.0628 |

| 20          | 0.089011049 | -1.8451 |

| 30          | 0.08900599  | -3.6274 |

| 40          | 0.089000931 | -5.4097 |

| 50          | 0.088995872 | -7.192  |

# Table 8. CV Control Updated Calibration Under Different Current

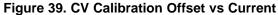

Using the updated gain and offset, obtain the updated CV control accuracy with different current as Figure 40 shows. The results show the CV control can almost maintain 0.01% accuracy within the whole battery voltage range (1.0 V–4.5 V).

Figure 40. CV Control Accuracy With Different Current

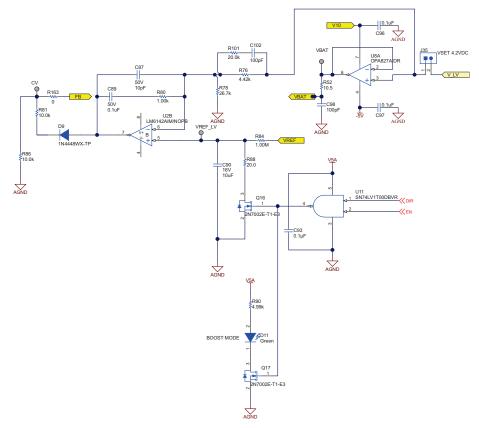

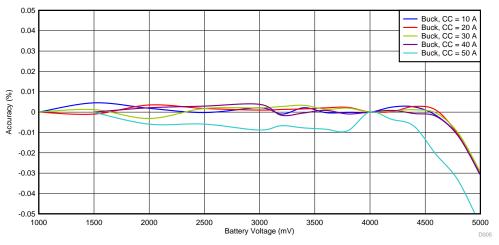

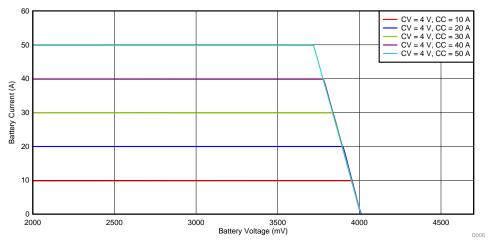

#### 3.3.3.3 CC, CV Transformation

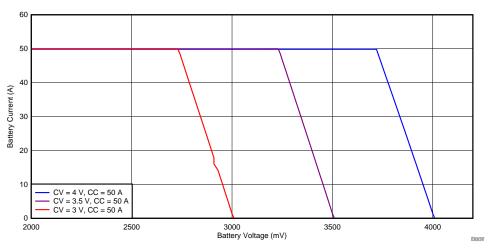

The complete battery formation profile should include both the CC control and the CV control. It is critical to understand the performance of the system when transforming from CC mode to CV mode. Figure 41 and Figure 42 show the transformation under different current and different voltage settings.

Figure 41. CC, CV Transformation Under Different Current Setting

Figure 42. CC, CV Transformation Under Different Voltage Setting

In Figure 41, with the increase in current setting, the CC control will start transforming to CV control at lower voltage. Figure 42 shows that voltage setting has less effect on the switch from CC control to CV control.

(12)

#### 3.3.3.4 ADC Calibration

Two channels are used to monitor the battery current and voltage. The accuracy of this data acquisition depends on the gain and offset of the THS4561 device and other components, so the output of the ADC should be calibrated. Use a similar method to calibrate those two channels as the previous current and voltage control loop:

ADC channel 1 calibration:

$$\begin{aligned} \text{Gain1} &= \frac{(I_{\text{out2}} - I_{\text{out1}})}{(\text{ADC}_{\text{out2}} - \text{ADC}_{\text{out1}})} = \frac{34.932 \text{ A} - 5.479 \text{ A}}{1565.7 \text{ mV} - 256.25 \text{ mV}} = 0.02249265 \text{ A / mV} \end{aligned} \tag{9} \\ \text{Offset1} &= I_{\text{out1}} - \text{Gain} \times \text{ADC}_{\text{out1}} = 5.479 \text{ A} - 0.02249265 \text{ A / mV} \times 256.25 \text{ mV} = -0.284741456 \text{ A}} \end{aligned} \tag{10} \\ \text{Gain2} &= \frac{(I_{\text{out3}} - I_{\text{out2}})}{(\text{ADC}_{\text{out3}} - \text{ADC}_{\text{out2}})} = \frac{49.942 \text{ A} - 34.932 \text{ A}}{2231.4 \text{ mV} - 1565.7 \text{ mV}} = 0.022547694 \text{ A / mV} \end{aligned} \tag{11} \\ \text{Offset2} &= I_{\text{out2}} - \text{Gain} \times \text{ADC}_{\text{out2}} = 34.932 \text{ A} - 0.0225476944 \text{ A / mV} \times 1565.7 \text{ mV} = -0.370924741 \text{ A} \end{aligned}$$

ADC channel 2 calibration:

$$Gain = \frac{(V_{out2} - V_{out1})}{(ADC_{out2} - ADC_{out1})} = \frac{4005.8 \text{ mV} - 1002.5 \text{ mV}}{1822.3 \text{ mV} - 460.5 \text{ mV}} = 2.205389925$$

(13)

Offset = V<sub>out1</sub> - Gain × ADC<sub>out1</sub> = 1002.5 mV - 2.205389225 × 460.5 mV = -13.08206051 mV (14)

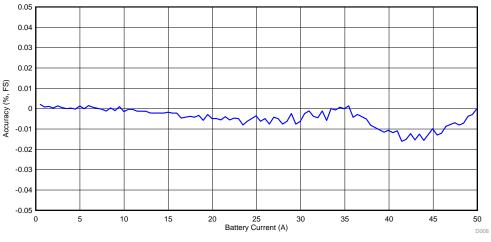

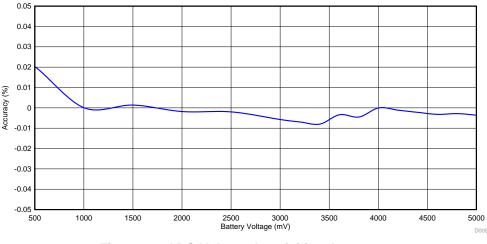

Figure 43 and Figure 44 show the accuracy of this data acquisition after calibration.

Figure 43. ADC Current Acquisition Accuracy

Figure 44. ADC Voltage Acquisition Accuracy

The results show the ADC current acquisition accuracy is excellent. Although the ADC voltage acquisition accuracy is not good in the low voltage range, battery tester applications usually are more concerned with the accuracy in the high-voltage range. In battery tester applications, engineers can refer to Section 3.3.3.1 and Section 3.3.3.2 to set the DAC to control the current and voltage after calibration. Then engineers can refer to Section 3.3.3.4 to get the real output current and voltage after calibration and adjust the DAC value to get the better performance.

Design Files

# 4 Design Files

# 4.1 Schematics

To download the schematics, see the design files at TIDA-01040.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01040.

# 4.3 PCB Layout Recommendations

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01040.

# 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-01040.

# 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01040.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01040.

# 4.7 Simulation Results

To download the simulation results, see the design files at TIDA-01040.

### 5 Software Files

To download the software files, see the design files at TIDA-01040.

# 6 Related Documentation

- 1. Texas Instruments, LM5170-Q1 Multiphase Bidirectional Current Controller Data Sheet

- 2. Texas Instruments, LM2664 Switched Capacitor Voltage Converter Data Sheet

- 3. Texas Instruments, TPS709 150-mA, 30-V, 1-µA IQ Voltage Regulators with Enable Data Sheet

- 4. Texas Instruments, LM5118 Wide Voltage Range Buck-Boost Controller Data Sheet

- 5. Texas Instruments, INA188 Precision, Zero-Drift, Rail-to-Rail Out, High-Voltage Instrumentation Amplifier Data Sheet

- 6. Texas Instruments, DACx0004, Quad 16-,14-,12-Bit, 1 LSB INL, Buffered, Voltage-Output Digital-to-Analog Converters Data Sheet

- 7. Texas Instruments, ADS131A0x 2- or 4-Chan, 24-Bit, 128-kSPS, Simultaneous-Sampling, Delta-Sigma ADC Data Sheet

- 8. Texas Instruments, TLV07 36-V Precision, Rail-to-Rail Output Operational Amplifier Data Sheet

- 9. Texas Instruments, OPAx22x High Precision, Low Noise Operational Amplifiers Data Sheet

- 10. Texas Instruments, OPA827 Low-Noise, High-Precision, JFET-Input Operational Amplifier Data Sheet

- 11. Texas Instruments, THS4561 Low-Power, High Supply Range, 70-MHz, Fully Differential Amplifier Data Sheet

- 12. Texas Instruments, LM6142/LM6144 17 MHz Rail-to-Rail Input-Output Operational Amplifiers

- 13. Texas Instruments, PMP15038 Test Results Technical Reference

# About the Author

# 6.1 Trademarks

E2E is a trademark of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. SIMetrix, SIMPLIS are registered trademarks of SIMetrix Technologies Ltd. All other trademarks are the property of their respective owners.

# 7 About the Author

**Sean Zhou** is an application engineer at Texas Instruments, where he is responsible for developing reference design solutions for the test and measurement industry. Sean has earned his master of science in electrical engineering (MSEE) degree from the Soochow University in Suzhou, China.

**Taras Dudar** is a systems design engineer and architect at Texas Instruments, where he is responsible for developing reference design solutions for the test and measurement industry. Previously, Taras designed high-speed analog SOC integrated circuits for Gbps data communications. Taras has earned his master of science in electrical engineering (MSEE) degree from the Oregon State University in Corvallis, OR.

# 8 Acknowledgement

A special thank you goes out to Youhao Xi, Ryan Andrews, Uttama Kumar Sahu, Jasper Li and Bryan Bloodworth for their support during the development of the TIDA-01040 reference design.

Page

**Revision History**

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from A Revision (September 2018) to B Revision

| • | Changed LM5170-Q1 Multiphase Bidirectional Current Controller section.                        | 5 |

|---|-----------------------------------------------------------------------------------------------|---|

| • | Deleted LM5118, TLV07, LM6142, and OPA2277 sections.                                          | 5 |

| • | Updated INA828 Precision Instrumentation Amplifier section.                                   | 5 |

| • | Updated DAC80004 16-bit DAC With 1 LSB INL/DNL section.                                       | 6 |

| • | Updated ADS131A04 24-bit, 128-kSPS, 4-Channel, Simultaneous-Sampling Delta-Sigma ADC section. | 6 |

|   | Updated Other Highlighted Products section.                                                   |   |

|   |                                                                                               |   |

#### Changes from Original (June 2018) to A Revision

#### Page

| • | Changed 'CC, CV' to 'constant current (CC) and constant voltage (CV)' | 2  |

|---|-----------------------------------------------------------------------|----|

| • | Changed wording in Section 1.1                                        | 2  |

| • | Changed '0.5 C' to '0.5 A'                                            | 3  |

| • | Changed wording throughout Section 2                                  | 4  |

| • | Changed wording throughout Section 3                                  | 17 |

| • | Changed information in Table 5                                        | 31 |

| • | Added Section 8                                                       | 41 |

|   |                                                                       |    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated