Design Guide: TIDA-020015

# 4.5-V to 65-V Input, Compact Bias Supply With Power Stage Reference Design for IGBT/SiC Gate Drivers

# **Description**

This reference design is a 4.2-W, single-channel, automotive 12-V battery input flyback bias supply for IGBT/SiC isolated gate drivers. The supply accepts a wide input range of 4.5-V to 65-V DC. The output is configurable as +15 V, -8 V or +20 V, -4 V at loads up to 180 mA for driving the IGBT/SiC MOSFET power modules. The system consists of reverse polarity protection, electric transients clamping, and overvoltage and undervoltage protection circuits. The flyback controller implements primary-side regulation with better than ±1% load and line regulation performance. The power stage design includes the dual-channel isolated gate drivers with 5.7-kV<sub>RMS</sub> reinforced isolation and designed in compact form factor of 100 mm x 62 mm. It includes isolated DC bus sensing, isolated temp sensing, logic shoot-through protection and diagnostic features.

#### Resources

| TIDA-020015 | Design Folder  |

|-------------|----------------|

| TIDA-020014 | Design Folder  |

| LM5180-Q1   | Product Folder |

| LM74700-Q1  | Product Folder |

| ISO5852S-Q1 | Product Folder |

| AMC1311-Q1  | Product Folder |

| AMC1301-Q1  | Product Folder |

ASK Our E2E™ Experts

## **Features**

- Wide-V<sub>IN</sub> flyback converter over the input voltage of 4.5-V to 65-V DC

- Output configurable as +15 V, -8 V or +20 V, -4 V at load up to 180-mA supply for Si IGBT and SiC MOSFET modules

- Protection for clamping high voltage conducted transients to safe levels for downstream circuitry

- Programmable overvoltage and undervoltage protection on supply output

- Primary side regulation with no optocoupler for extended life time and small form factor

- Power stage design includes dual channel isolated gate driver, DC bus sensing, and temp sensing for high voltage testing

## **Applications**

- Inverter and motor control

- Onboard (OBC) and wireless charger

- DC/DC converter

- Gasoline and diesel engine platform

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

## 1 System Description

This reference design is a highly-integrated, primary side regulated (PSR) flyback bias supply powering two single channel IGBT/SiC isolated gate drivers. It can be powered directly from the 12-V car battery with a wide input range of 4.5 V to 65 V DC, electric transients suppression, and provides 15-V and –8-V isolated voltage rails with 180-mA maximum output current. The integration of a MOSFET switch, elimination of feedback loop, and elimination of bias winding makes this design very compact and attractive.

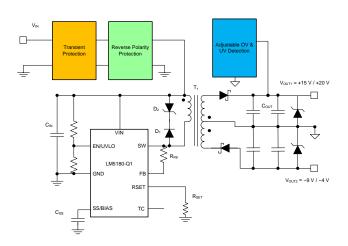

The TIDA-020015 targets at powering IGBT/SiC isolated gate drivers implemented in hybrid electric vehicle and electric vehicle (HEV/EV) systems. Figure 1 shows a traction inverter reference diagram where the position of the TIDA-020015 design is highlighted. The isolated gate drivers galvanically isolate the high-voltage power switches from the low-voltage control signals. Each isolated gate driver requires a pair of positive supply and negative supply rails to fully turn on and off the IGBT/SIC power modules.

Additionally, the TIDA-0120015 design is able to handle the 12-V battery conditions which include:

- The system maintains a constant output voltage over the full DC range of battery conditions specified in ISO 16750-2:

- Input V<sub>IN</sub> (min) down to 3.0 V, (after powered up) simulating a severe cold cranking condition.

- Input V<sub>IN</sub> (max) higher than 42 V, simulating the upper range of normal battery operation.

- The system must clamp or filter high-voltage electrical fast transients and maintain operation through them:

- These pulses include clamped load dump (up to 38 V) and other transients outlined in ISO 7637-2:2004.

- The system must properly respond to a reverse battery polarity event and shut down appropriately.

www.ti.com System Description

Figure 1. HEV, EV Traction Inverter Reference Block Diagram and the TIDA-020015 Position

System Description www.ti.com

# 1.1 Key System Specifications

Table 1 shows the key system specifications.

**Table 1. Key System Specifications**

| PARAMETER           |                              | COMMENTS                                                                                                                                                             | MIN  | TYP  | MAX  | UNIT |  |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| SYSTEM INPUT        |                              |                                                                                                                                                                      |      |      |      |      |  |

| V <sub>IN</sub>     | Input voltage                | Battery voltage range (DC)                                                                                                                                           | 4.5  | 13.5 | 65   | V    |  |

| V <sub>CLAMP+</sub> | Positive clamping voltage    | Positive input protection TVS clamping range                                                                                                                         | 60   |      | 100  | V    |  |

| P <sub>PK</sub>     | Peak pulse power dissipation | Maximum TVS power dissipation                                                                                                                                        |      | 600  |      | W    |  |

| F <sub>sw</sub>     | Switching frequency          |                                                                                                                                                                      | 10   | 350  | 350  | kHz  |  |

| OUTPUT VOL          | TAGE                         |                                                                                                                                                                      |      | *    | *    | *    |  |

| V <sub>out1</sub>   |                              | System output voltage, across load                                                                                                                                   | 13   | 15   | 17   | V    |  |

| V <sub>out2</sub>   |                              | System output voltage, across load                                                                                                                                   | -6.5 | -8   | -8.2 | V    |  |

| OUTPUT CUR          | RRENT                        |                                                                                                                                                                      |      |      |      |      |  |

| l <sub>out</sub>    |                              | Max output current. Drawing more than 180 mA is not recommended for thermal reasons. See the Section 3.2.8 testing section to see the temperature rise at full load. |      | 180  |      | mA   |  |

www.ti.com System Overview

## 2 System Overview

## 2.1 Block Diagrams

# 2.1.1 Bias Supply Block Diagram

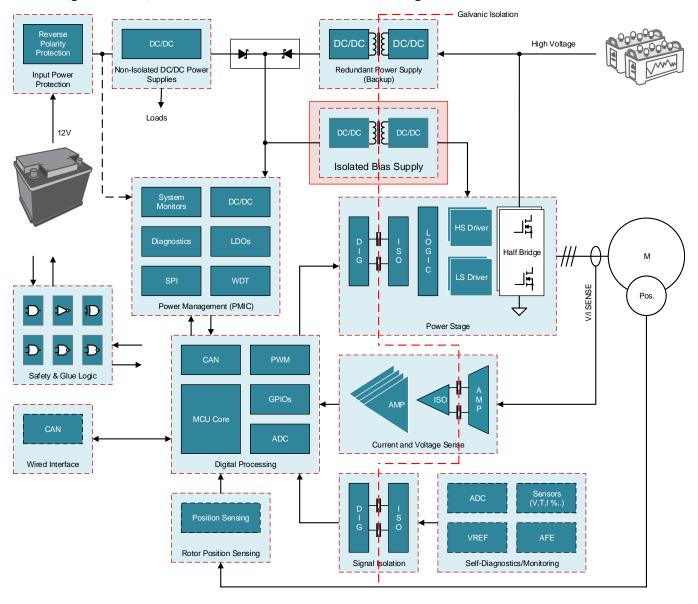

Figure 2 shows the TIDA-020015 low-voltage board block diagram. The design consists of 4 main functional elements:

- 1. The transient protection which suppresses both positive and negative battery pulses as prescribed in ISO 7637-2:2004 pulses 1, 2a, and 3a, 3b.

- 2. The reverse polarity protection to prevent reverse-biasing components, which are sensitive to polarity, like polarized capacitors and most integrated circuits.

- 3. The PSR flyback converter which has an integrated MOSFET switch and high-density design with only one component crossing the isolation barrier. The converter maintains high regulation across various loads and achieves larger than 90% peak efficiency.

- 4. The adjustable overvoltage and undervoltage detection circuit which prevents the gate-driver voltage dropping below the minimum gate voltage to properly turn on the IGBT. Operating the IGBT with a lesser gate voltage causes excessive power dissipation in the IGBT.

Figure 2. TIDA-020015 Low-Voltage Board Block Diagram

System Overview www.ti.com

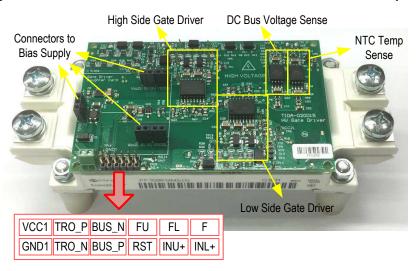

# 2.1.2 Isolated Gate-Driver Board Block Diagram

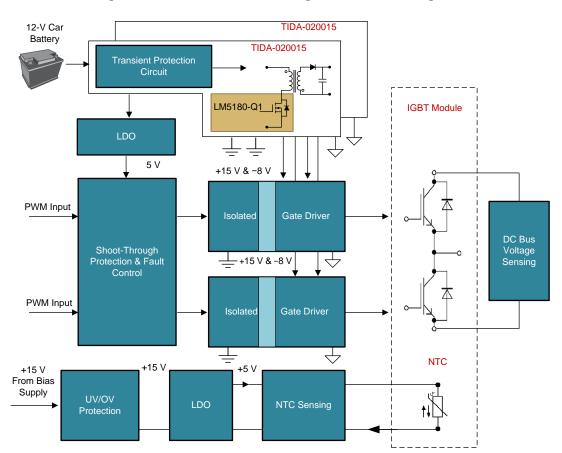

The TIDA-020015 design includes a power-stage companion board for high-voltage evaluation. It is a compact, dual-channel isolated gate-driver board providing drive, bias voltages, protection, and diagnostics needed for half-bridge SiC MOSFET and Si IGBT power modules housed in 150-mm × 62-mm × 17-mm packages. The HV board consists of the high-side and low-side isolated gate drivers, the DC bus voltage sensing, the shoot-through protection and fault control, the high-voltage input LDO, and the NTC sensing circuit. The connectors allow for plug-in connection to the gate drivers for easy evaluation. Figure 3 shows the power stage board block diagram. The features are listed as follows:

- 20-A peak split sink and source drive current from external buffer to optimize turn on and turn off switching time

- Robust noise-immune solution with CMTI > 100 V/ns

- Supports 5-kV<sub>RMS</sub>, reinforced isolation for input rail up to 1700 V

- Programmable short-circuit sensing and soft turn-off protection by the de-saturation circuit

- 2-A active Miller clamp

- · Output short-circuit clamp

- · Fault feedback with reset

- NTC temperature and DC bus voltage sensing

Figure 3. TIDA-020015 Power Stage Board Block Diagram

www.ti.com System Overview

## 2.2 Design Considerations

The TIDA-020015 reference design provides bias power to the SiC or IGBT isolated gate drivers. Gate drivers must provide sufficient drive current to ensure fast charging and discharging of the gate capacitance of the IGBT or SiC transistor, hence to reduce the switching power loss. The gates of the IGBTs are supplied with a much higher voltage than the actual gate-threshold voltages, typically 15 V to 20 V to minimize the turn-on losses. To reduce the turn-off time and the turn-off losses, a negative voltage (-4 V to -9 V) is applied at the gate. A negative voltage also prevents Miller turn on of the switch. This design provides the required drive voltages, and a 4.3-W bias power which is sufficient for most of the high-power IGBT or SiC modules.

## 2.3 Highlighted Products

The TIDA-020015 reference design features the following TI devices.

#### 2.3.1 LM5180-Q1

The LM5180-Q1 device is a primary-side regulated (PSR) flyback converter with high efficiency over a wide input voltage range of 4.5 V to 65 V. The isolated output voltage is sampled from the primary-side flyback voltage, eliminating the need for an optocoupler, voltage reference, or third winding from the transformer for output voltage regulation. The high level of integration results is a simple, reliable and high-density design with only one component crossing the isolation barrier. Boundary conduction mode (BCM) switching enables a compact magnetic solution and better than ±1% load regulation and line regulation performance. An integrated 100-V power MOSFET provides output power up to 7 W with enhanced headroom for line transients.

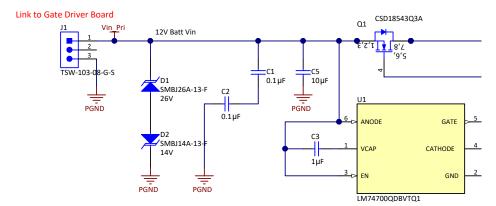

## 2.3.2 LM74700-Q1

The LM74700-Q1 is an ideal diode controller device that operates in conjunction with an external N-channel MOSFET as an ideal diode rectifier for low loss reverse polarity protection. The wide supply input range of 3 to 65 V allows control of many popular DC bus voltages. The device can withstand and protect the loads from negative supply voltages down to -65 V. With a low  $R_{DS(on)}$  external N-channel MOSFET, a very low forward voltage drop can be achieved while minimizing the amount of power dissipated in the MOSFET.

#### 2.3.3 TPS3700-Q1

The TPS3700-Q1 is a wide-supply voltage window comparator which operates over a 1.8-V to 18-V range. The device has two high-accuracy comparators with an internal 400-mV reference and two open-drain outputs rated to 18 V for overvoltage and undervoltage detection. The TPS3700-Q1 device can be used as a window comparator or as two independent voltage monitors; the monitored voltage can be set with the use of external resistors.

#### 2.3.4 ISO5852S-Q1

The ISO5852S-Q1 device is a reinforced, isolated gate driver that is capable of driving a 1200-V IGBT module with current ratings from 50 A to 200 A. The device offers:

- High isolation ratings in the industry

- 5.7 kV<sub>RMS</sub> isolation voltage

- 8000 -V<sub>pk</sub> maximum transient isolation voltage

- 2121-V<sub>pk</sub> maximum transient isolation voltage

- Split outputs

- 2.5-A peak source and 5-A peak sink currents

- 100-kV/µs minimum common-mode transient

- The device also includes the Miller clamp, soft turnoff, UVLO, DESAT detect, fault feedback, and ready-status feedback features.

System Overview www.ti.com

#### 2.3.5 AMC1301-Q1

The AMC1301 is a fully-differential, precision, isolated amplifier. The input stage of the device consists of a fully differential amplifier that drives a second-order, delta-sigma ( $\Delta\Sigma$ ) modulator. The modulator uses the internal voltage reference and clock generator to convert the analog input signal to a digital bit stream. The drivers transfer the output of the modulator across the isolation barrier that separates the high-side and low-side voltage domains.

#### 2.3.6 AMC1311-Q1

The AMC1311-Q1 is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 7 kV peak according to VDE V 0884-11 and UL1577. Used in conjunction with isolated power supplies, this isolated amplifier separates parts of the system that operate on different common-mode voltage levels and protects lower-voltage parts from damage. The high-impedance input of the AMC1311-Q1 is optimized for connection to high-voltage resistive dividers or other voltage signal sources with high output resistance.

#### 2.3.7 TPS7B8250-Q1

The TPS7B82-Q1 device is a  $40\text{-V}_{\text{IN}}$  300-mA low-dropout linear regulator with ultra-low quiescent current. This voltage regulator consumes only 3  $\mu\text{A}$  of quiescent current at light load, and is quite suitable for the automotive always on application. The device operates with a wide input-voltage range from 3 V to 40 V (45-V load dump protection).

# 2.4 System Design Theory

# 2.4.1 Reverse Polarity Protection

Reverse battery protection is required in every electronic subsystem of a vehicle, both by OEM standards, as well as ISO 16750-2, an international standard pertaining to supply quality. The goal is to prevent reverse-biasing components which are sensitive to polarity, like polarized capacitors and most integrated circuits.

Figure 4 shows the schematic of the reverse polarity protection circuit. It consists of an N-channel MOSFET (Q3) which is driven by the LM74700-Q1 smart diode controller. Traditional methods which implement a blocking diode result in large power dissipation due to the typical 400- to 700-mV forward voltage drop. The smart diode solution decreases the losses as per the  $R_{DS(on)}$  of the MOSFET. The LM74700-Q1 controller provides a gate drive for an external N-channel MOSFET and a fast response internal comparator to discharge the MOSFET gate in the event of reverse polarity. A unique advantage of this scheme is that it is not referenced to ground and thus has Zero  $I_q$ . The N-channel MOSFET is selected according to the following criteria:

- Continuous current rating higher than 10 A which is the maximum input current at minimum input voltage in this design

- The V<sub>GS</sub> threshold should be 2.5 V maximum

- Source-to-drain voltage V<sub>SD</sub> should be at least 0.48 V at 2 A

www.ti.com System Overview

Figure 4. Reverse Polarity Protection Circuit Schematic

#### 2.4.2 Electrical Transient Protection

TVS diodes are implemented on the supply input of the system to protect against both positive and negative electrical transients as prescribed in ISO 7637-2:2004 pulses 1, 2a, and 3a, 3b. OEM specifications will define a "class of operation" for each test which defines the required operational status during and after the event. The TVS diodes are placed aiming at shut the transients while maintaining the downstream circuits operation.

The TVS diode is selected based on the following criteria:

- The diode breakdown voltage is lower than the breakdown voltage of the downstream circuits.

- The positive clamping voltage is above twice of the input battery voltage (for jump start) and clamped load dump voltages.

- The negative clamping voltage is slightly lower than the battery voltage in reverse connection so that it will clamp all negative voltages while it does not create short circuit during a reverse battery condition.

- The power rating of the TVS diode is higher than the power dissipation during the transient clamping. The important parameters for calculating the TVS diode power rating are: the clamping voltage, the voltage of the pulse it is clamping, and the source impedance of the pulse. One severe scenario according to the ISO7637 pulse 2a standard is:

- V<sub>Pulse</sub> = 75 V

- R<sub>Source</sub> = 4 Ω

- V<sub>Clamp</sub> = 33 V

## where:

- V<sub>Pulse</sub> is the voltage of the pulse that TVS diode is clamping

- R<sub>Source</sub> is the source impedance of the pulse

- V<sub>Clamp</sub> is the clamping voltage from TVS diode

The worst-case assumption is that the load is drawing zero current and all the current flows through the TVS diode. Thus, the power rating of the diode is calculated as:

$$P_{TVS} = \frac{V_{Pulse} - V_{Clamp}}{R_{source}} \times V_{clamp} = 346.5 \text{ W}$$

(1)

Two SMB-sized TVS diodes with 600-W peak power rating are selected for positive and negative clamping respectively for the design. For detailed testing results and waveforms, see the *Automotive Wide V<sub>IN</sub> Front-End Power Reference Design w/Cold Crank Operation and Transient Protection* reference design.

System Overview www.ti.com

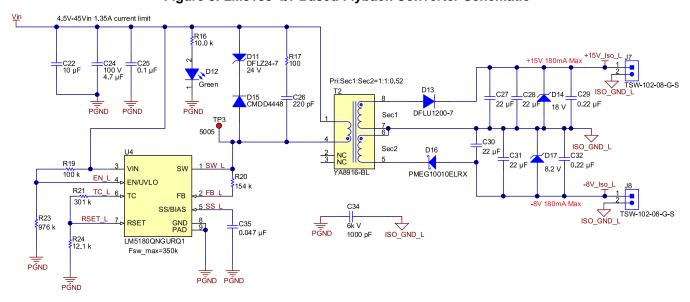

## 2.4.3 LM5180-Q1 Flyback Converter

The bias supply solution 1 is the flyback converter based on the LM5180-Q1 device which has integrated MOSFET and internal compensation. The converter provides isolated output voltages with tight regulation crossing load. Table 2 shows the design specifications. Highlights of the converter are summarized as:

- Boundary conduction mode (BCM) control architecture provides fast line and load transient response

- Peak current-mode control

- Quasi-resonant switching for reduced power loss

- Internal loop compensation

- Integrated 100-V flyback power MOSFET

- Provides large headroom for input voltage transients

- Cycle-by-cycle overcurrent protection (OCP)

- Low transformer primary-to-secondary (inter-winding) capacitance to accommodate high dv/dt secondary-side common-mode swings.

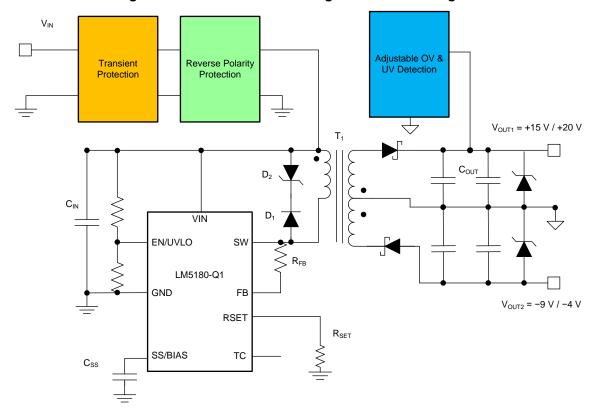

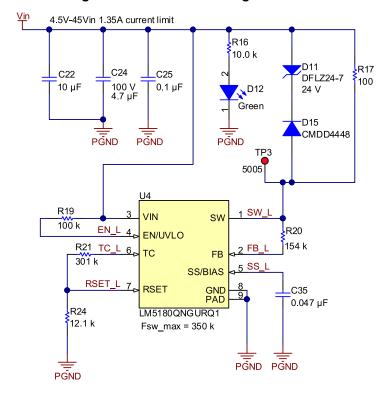

Figure 5 shows the schematic of the converter.

**Table 2. Flyback Converter Specifications**

| PARAMETER                                      | SPECIFICATION                                                                      |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------|--|--|

| Input voltage (V <sub>IN</sub> )               | 4.5 V-65 V DC (for flyback converter only, TVS limits the system input to 26 V DC) |  |  |

| Output voltage (V <sub>OUT</sub> )             | +15 V, –9 V                                                                        |  |  |

| Output ripple                                  | ±3%                                                                                |  |  |

| Maximum output current (I <sub>out_max</sub> ) | 180 mA                                                                             |  |  |

| Switching frequency                            | < 350 kHz                                                                          |  |  |

| Output power (P <sub>out_max</sub> )           | 4.2 W                                                                              |  |  |

| Efficiency                                     | > 86% peak, 82% at full load                                                       |  |  |

Figure 5. LM5180-Q1 Based Flyback Converter Schematic

www.ti.com System Overview

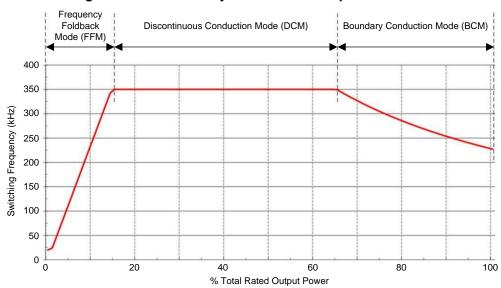

# 2.4.3.1 Modes of Operation and Switching Frequency

The LM5180-Q1 device uses a variable-frequency, peak current-mode (VFPCM) control architecture with three possible modes of operation as Figure 6 illustrates.

Figure 6. LM5180-Q1 Flyback Converter Operation Mode

At high loads, the LM5180-Q1 device operates in quasi-resonant boundary conduction mode. The power MOSFET turns on when the current in the secondary winding reaches zero. The MOSFET turns off when the peak primary current reaches the level dictated by the output of the internal error amplifier. As the load is decreased, the peak current decreases and the frequency increases to maintain BCM operation.

#### 2.4.3.2 Transformer Design

Key parameters to design the transformer include turns ratio, primary side inductance, switching frequency, saturation current and so forth.

If ignoring the drop voltage across the switching MOSFET, the winding turns ratio is calculated as:

$$V_{IN\ Min} \times T_{on} = (V_{OUT} + V_{D}) \times T_{off} \times N_{PS}$$

where

- V<sub>IN- Min</sub> is the minimum input voltage

- T<sub>on</sub> is the switch-on time of the switching MOSFET

- T<sub>off</sub> is the off time of the switching MOSFET

- N<sub>PS</sub> is the turns ratio of the transformer

- ullet  $V_D$  is the output rectification diode

Considering  $D = \frac{T_{on}}{T_{on} + T_{on}}$  is the duty cycle, and choosing the maximum duty cycle 75% at minimum input voltage, the turns patio of the transformer primary winding to the secondary winding is calculated as:

$$N_{PS} = \frac{V_{IN\_Min}}{V_{OUT} + V_D} \times \frac{D}{1 - D} = 0.65$$

(3)

Select a magnetizing inductance based on the minimum off-time constraint according to:

$$L_{\text{MAG}} \ge \frac{(V_{\text{OUT}} + V_{\text{D}}) \times N_{\text{PS}} \times t_{\text{OFF\_MIN}}}{I_{\text{PRI\_PK}}} = 26.5~\mu H$$

where

- V<sub>D</sub> is the forward drop voltage of the output rectification diode

- I<sub>PRL-PK</sub> is the primary winding current when converter operates in frequency fold back mode (1.5 A according to the datasheet)

(4)

(2)

(5)

(6)

System Overview www.ti.com

The built-in MOSFET of LM5180-Q1 is rated at 100 V. In the off cycle, when the secondary (flyback) diode is on, the voltage on the drain (V<sub>DS</sub>) is calculated as:

$$V_{DS} = V_{IN(MAX)} + V_{REF} + V_{RING} = 82 \text{ V}$$

#### where

- V<sub>IN(MAX)</sub> is the maximum input voltage

- I<sub>REF</sub> is the voltage reflected from the secondary side

The voltage across the secondary side diode is calculated as:

$$V_{\text{Diode}} = V_{\text{OUT}} + \frac{V_{\text{IN(MAX)}}}{N_{PS}} + V_{\text{SPIKE}} = 112 \text{ V}$$

#### where

- V<sub>OUT</sub> is the maximum output voltage

- V<sub>SPIKE</sub> is the excited spike due to resonance

The inductance of the transformer primarily determines the modes of operation in the LM5180-Q1 as the load is varied from the minimum load to full load. An increase in the magnetic inductance generally leads to an increase in the leakage inductance of the transformer. The LM5180-Q1 has a minimum off-time  $(T_{OFF(MIN)})$  of 500 ns: the magnetizing current should not decrease to zero in less than 500 ns. Therefore, the minimum primary side inductance is calculated as:

$$L_{PRI} \geq \frac{\left(V_{out} + V_{FWD}\right) \cdot T_{OFF\left(MIN\right)} \cdot N_{PS}^2}{I_{PRI\_MIN} \cdot N_{PS}} = 30 \quad \mu H$$

#### where

- V<sub>OUT</sub> is the nominal output voltage which is 24 V

- T<sub>OFF(MIN)</sub> is the minimum off time of LM5180-Q1

- I<sub>PRI MIN</sub> is the minimum peak current flowing at primary side for the LM5180-Q1 which is 0.27 A

- N<sub>PS</sub> is the primary to secondary turns ratio

Thus, the designed transformer should have the minimum primary inductance of 30  $\mu$ H. Specifications of the designed flyback transformer are summarized in Table 3.

**Table 3. Flyback Transformer Specifications**

| PARAMETER                                      |            | SPECIFICATION                            |

|------------------------------------------------|------------|------------------------------------------|

| Power rating                                   |            | 4.2 W                                    |

| Input voltage                                  |            | 4.5 V–65 V                               |

| Maximum output current (I <sub>out_max</sub> ) |            | 180 mA                                   |

| Switching f                                    | requency   | < 300 kHz                                |

| Maximum (                                      | duty cycle | 75%                                      |

| Primary side inductance                        |            | 30 μH ±10% at 300 kHz                    |

| Leakage inductance                             |            | < 1% of primary inductance               |

| Parasitic capacitance primary to secondary     |            | < 20 pF                                  |

| Output voltage and current                     |            | +15 V and -9 V at 180-mA average current |

| Turns ratio                                    |            | 1:1:0.52                                 |

| Peak<br>current                                | Primary    | 1.45 A                                   |

|                                                | Secondary  | 1 A                                      |

| RMS<br>current                                 | Primary    | 1.1 A                                    |

|                                                | Secondary  | 380 mA                                   |

www.ti.com System Overview

TI recommends the flyback transformer UA8916-BL from Coilcraft® for this reference design. The transformer features parasitic capacitance of 17 pF from primary to secondary side.

## 2.4.3.3 Input Capacitors

The input capacitor must supply the input current during the input voltage dip from the 12-V battery. Input capacitors are essential in limiting the ripple voltage while supplying most of the switch current during the MOSFET switch on-time.

The input capacitance is calculated as:

$$C_{in} = \frac{I_{pri\_pk} \times D_{on}}{F_{SW} \times \Delta V_{ripple}} = \frac{1.45 \times 0.75}{300k \times 4.5 \times 3\%} = 26.8 \,\mu\text{F}$$

(8)

## 2.4.3.4 Output Capacitors

The output capacitance ensures the converter has a small transient deviation to a step change of the load transient. The minimum needed capacitance is calculated as to maintain the output voltage drop less than 3% of the nominal voltage when the output current changes abruptly from the maximum to half (I<sub>step</sub>):

$$I_{\text{step}} = \frac{I_{\text{OUT}}}{2} = \frac{180 \text{ mA}}{2} = 90 \text{ mA}$$

(9)

$$V_{drop} = V_{OUT} \times 3\% = 24V \times 1\% = 0.24 V$$

(10)

As any forward converters, the right-half-plan-zero (RHPZ) limits the bandwidth of the flyback. The frequency of the RHPZ is calculated as:

$$f_{RHPZ}\!=\frac{R_{OUT}\times (V_{IN}/V_{OUT})^2}{L_{PRI}\times 2\pi}\!=24$$

.8 kHz

where

- R<sub>OUT</sub> is the load impedance

- L<sub>PRI</sub> is the primary inductance of the transformer (11)

The bandwidth of the system is estimated as 1/5 of the RHPZ:

$$f_{bandwidth} = \frac{1}{5} \times f_{RHPZ} = \frac{1}{5} \times 24.8 \text{ kHz} = 4.96 \text{ kHz}$$

(12)

As the result, the output capacitance at bandwidth frequency is calculated as:

$$C_{\text{out\_min}} = \frac{1}{2 \times \pi \times f_{\text{bandwidth}}} \times \frac{1}{\Delta V_{\text{OUT}} / \Delta I_{\text{loadstep}} - \text{ESR}_{\text{OUT}}} = 12 \quad \mu F$$

(13)

Therefore, a minimum of 12-µF capacitance is required for this design.

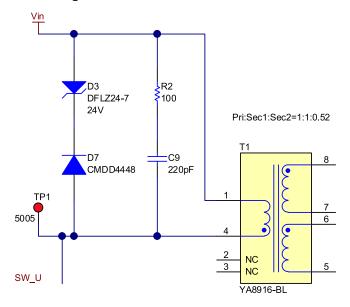

#### 2.4.3.5 RC Snubber Design

When the MOSFET turns off, a high voltage spike occurs at the drain (switch node) because of the resonances between leakage inductor of the main transformer and the parasitic capacitance in the circuit. This causes excessive voltage on the drain of the MOSFET which can lead to breakdown and eventually failure of the device. The parasitic capacitance is composed of 3 components: (1) output capacitance of the MOSFET, (2) junction capacitance of the output diode which reflects to the primary side, (3) parasitic capacitance of the transformer winding.

The transformer used in this design has relatively less leakage inductance. A Zener clamp is used in this reference design as Figure 7 shows, due to ease-of-design and higher light-load efficiency than the RCD snubber:

System Overview www.ti.com

Figure 7. Snubber Circuit Schematic

The power dissipated in the snubber can be calculated as:

$$P_{\text{sub}} = \frac{1/2 \times L_{LK} \times I_{PK}^2 \times F_{SW}}{1 - V_{FBK} / V_{Ze}}$$

where

- L<sub>IK</sub> is the leakage inductance of the transformer

- I<sub>PK</sub> is the primary peak current

- F<sub>sw</sub> is the switching frequency

- The Zener diode is selected as 24 V

## 2.4.3.6 Verification on Input Voltage Range

The LM5180-Q1 device integrates a 100-V power MOSFET with maximum current of 1.5 A. The maximum drain-to-source voltage ( $V_{ds_max}$ ) is calculated as:

$$V_{ds_{-}max} = n \times \frac{N_p}{N_s} \times (V_{OUT} + V_f) + V_{in_{-}max} = 102.5 \text{ V}$$

where

- n is the safe margin which is normally 1.5 or 2 times of the nominal value

- N<sub>n</sub>/N<sub>s</sub> is the turn ratio of the transformer primary winding to the secondary winding

- V<sub>out</sub> is the output voltage

- V<sub>f</sub> is the forward voltage of the output diode

Therefore, the selected MOSFET breaking voltage larger must be larger than 102.5 V.

# 2.4.3.7 LM5180-Q1 Settings

Figure 8 shows the schematic with components surrounding the LM5180-Q1 device. The UVLO is connected to  $V_{IN}$  directly for lowest undervoltage lockout. With the designed turns ratio of the transformer and forward voltage of the secondary diode, the ratio between R20 ( $R_{FB}$ ) and R24 ( $R_{RST}$ ) determines the output voltage. R24 ( $R_{RST}$ ) is selected as 12.1 k $\Omega$  according to data sheet. The output voltage is 24 V, the forward voltage drop of the secondary diode is 0.7 V.  $R_{FB}$  is calculated as:

$$R_{FB} = \frac{(V_{OUT} + V_{FD}) \times N_{PS}}{0.1 \text{ mA}} = 154 \text{ k}\Omega$$

(16)

(14)

www.ti.com System Overview

The LM5180-Q1 device employs a thermal-compensation circuit that adjusts the feedback reference based on the forward voltage thermal coefficient of the flyback diode. The thermal compensation resistor value is determined by R21 ( $R_{TC}$ ) which is calculated as:

$$R_{TC}\!=\!\frac{R_{FB}}{N_{PS}}$$

×  $\frac{3~mV/^{\circ}C}{TC_{Diode}}\!=\!301~k\Omega$

where

• TC<sub>Diode</sub> is the absolute value of the temperature coefficient of the flyback diode (17)

Figure 8. LM5180-Q1 Settings Schematic

System Overview www.ti.com

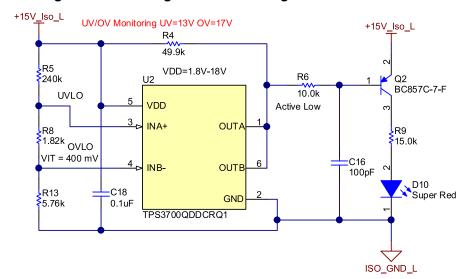

## 2.4.3.8 Overvoltage and Undervoltage Detection

The IGBT gate is driven from the 15-V rail to turn on the IGBT. The 15-V rail should not drop below the minimum gate voltage to properly turn on the IGBT. Driving the IGBT with lower gate voltage causes excessive power dissipation. Otherwise, excessive higher gate voltage will destroy the IGBT.

The overvoltage and undervoltage detection is designed with the window comparator TPS3700-Q1. It has two high-accuracy comparators with an internal 400-mV reference and two open-drain outputs. Figure 9 shows the schematic of the detection circuit. The INA+ and INB- pins implement open-drain output. OUTA is driven low when the voltage at INA+ is below ( $V_{\text{ITP}} - V_{\text{HYS}}$ ) (according to the TPS3700-Q1 data sheet). The output goes high when the sense voltage returns above the respective threshold. OUTB is driven low when the voltage at this comparator exceeds  $V_{\text{ITP}}$ . The output goes high when the sense voltage returns below the respective threshold. The undervoltage threshold is set as 13 V, and the overvoltage threshold is set as 17 V for this design. The OR logic is implemented by connecting the two open drain outputs of the TPS3700-Q1 device. OUTA and OUTB can merge into one logic signal that goes low if either output is asserted. A 49.9-k $\Omega$  pullup resistor is used to hold these lines high when the output goes to high impedance.

Figure 9. Overvoltage and Undervoltage Detection Schematic

## 3 Hardware, Testing Requirements, and Test Results

#### 3.1 Hardware

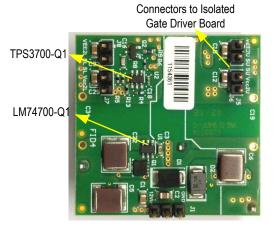

Figure 10 shows the isolated gate driver board and connectors pin description. The placement of components and corresponding circuits are also described. Figure 11 and Figure 12 show the PCB board image of LM5180-Q1 based flyback converter from the top and bottom side, respectively. The input and output connectors are indicated.

Figure 10. Isolated Gate Driver Board and Connectors Pin Description

Figure 11. LM5180-Q1 Based Flyback PCB Board Top Side

Figure 12. LM5180-Q1 Based Flyback PCB Board Bottom Side

Figure 13 shows the LM5180-Q1 based flyback PCB board implemented on top of the isolated gate driver board and the IGBT module.

Figure 13. Implementation With Power Stage and IGBT Module

# 3.2 Testing and Results

## 3.2.1 Startup

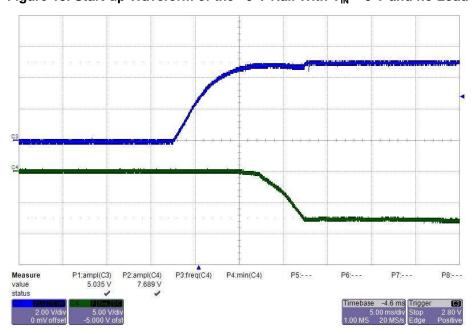

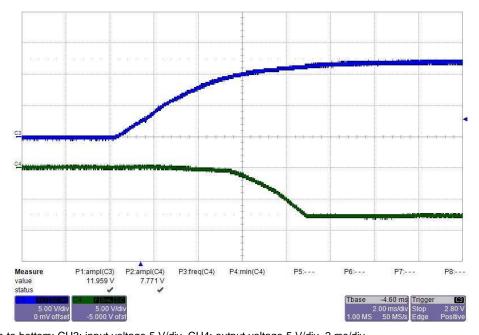

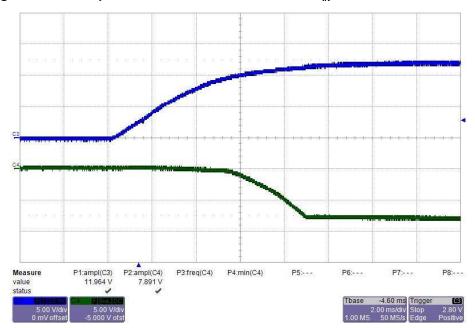

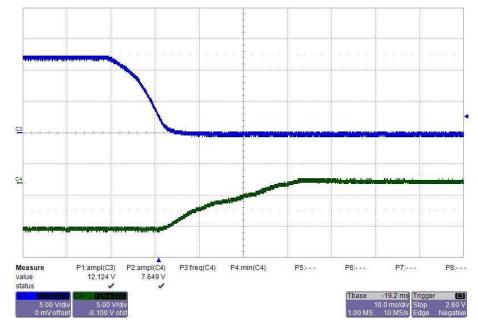

The startup waveforms of the flyback converter designed with LM5180-Q1 are measured under 5-V input and 12-V input, respectively. The 15-V and –9-V rails are measured separately.

Measure value 5.03 V 15.262 V 15.262 V 15.262 V 5.00 V/dity 5.00 V

Figure 14. Start-up Waveform of the 15-V Rail With  $V_{IN} = 5$  V and no Load

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 5 ms/div

Figure 15. Start-up Waveform of the -9-V Rail With  $V_{IN} = 5$  V and no Load

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 5 ms/div

C3

Measure value 11.999 V 15.315 V 15.315 V 15.00 V/drv 0 mV offset 11.00 V 15.00 V/drv -11.000 V 15.00 V/drv -11.00 0 V 15.00 V/drv -11

Figure 16. Start-up Waveform of the 15-V Rail With  $V_{\rm IN}$  = 12 V and no Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

Figure 17. Start-up Waveform of the –9-V Rail With  $V_{\rm IN}$  = 12 V and no Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

C4

Measure value 12.001 V 15.085 V 15.085 V 15.00 V/div 0 mV offset 11.000 V 15.00 V/div -11.000 V 15.00 V/div 10.00 MS 50 MS/s Edge Positive

Figure 18. Start-up Waveform of the 15-V Rail With  $V_{\rm IN}$  = 12 V and 180-mA Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

Figure 19. Start-up Waveform of the -9-V Rail With  $V_{IN} = 12 V$  and 180-mA Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

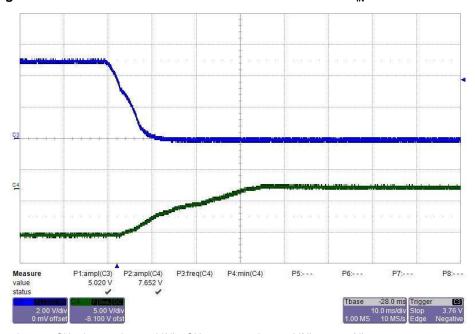

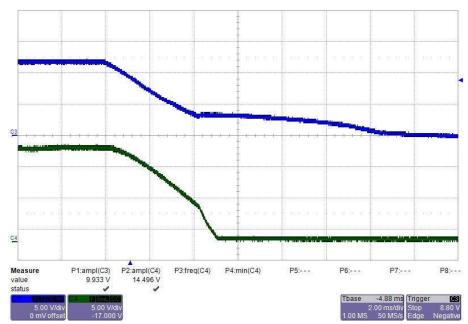

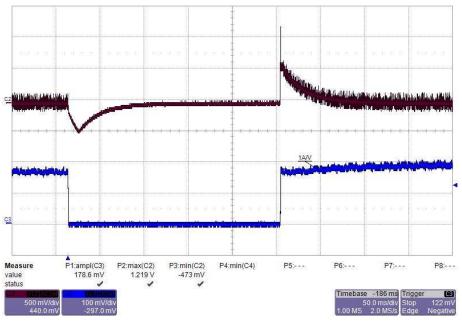

#### 3.2.2 Power Down

The power down waveforms of the flyback converter designed with LM5180-Q1 are measured under 5-V input and 12-V input, respectively. The 15-V and –9-V rails are measured separately.

C4

Measure value 5.016 V 14.600 V 14.6

Figure 20. Power Down Waveform of the 15-V Rail With  $V_{\rm IN}$  = 5 V and no Load

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 10 ms/div

Figure 21. Power Down Waveform of the -9-V Rail With  $V_{IN} = 5$  V and no Load

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 10 ms/div

C4

Measure value 12.110 V 14.655 V status

5.00 V/dry 0 mV offset 1.00 mS 10 mS/dry 1.00 mS/dry

Figure 22. Power Down Waveform of the 15-V Rail With  $V_{\rm IN}$  = 12 V and no Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 10 ms/div

Figure 23. Power Down Waveform of the -9-V Rail With  $V_{\rm IN}$  = 12 V and no Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 10 ms/div

Measure value 9.935 V 7.293 V

Figure 24. Power Down Waveform of the -9-V Rail With  $V_{IN} = 12 \text{ V}$  and 180-mA Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

Figure 25. Power Down Waveform of the +15-V Rail With  $V_{IN}$  = 12 V and 180-mA Load

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

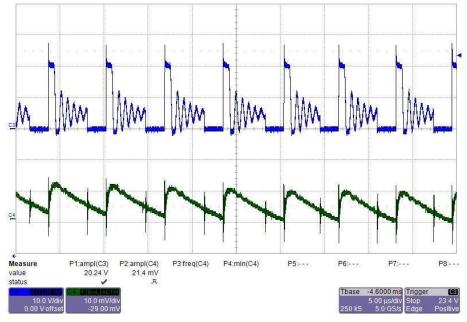

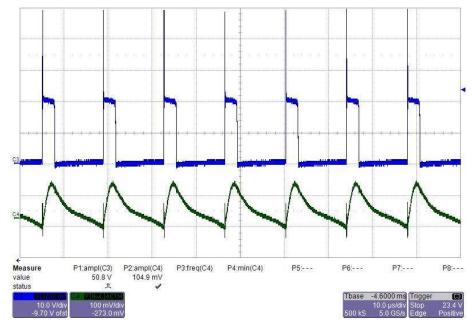

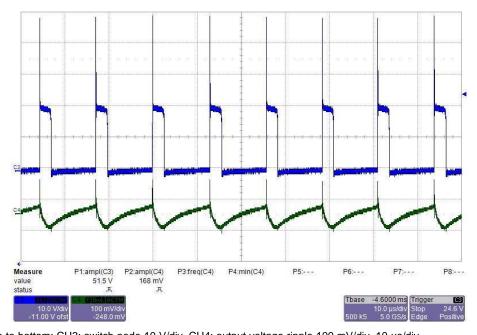

## 3.2.3 Switch Node and Output Voltage Ripple

Switch node and output voltage ripple of the flyback converter designed with LM5180-Q1 are measured under 5-V input, 12-V input, and 18-V input, respectively. The 15-V and –9-V rails are measured separately.

Figure 26. Switch Node and Output Ripple of the 15-V Rail With  $V_{IN} = 5$  V and no Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 10 mV/div, 5 µs/div

Figure 27. Switch Node and Output Ripple of the 15-V Rail With  $V_{IN} = 5$  V and 85-mA Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 100 mV/div, 10  $\mu$ s/div

Measure value 20.37 V 33.6 mV status 10.0 V/div 20.0 mV/div 20.0 m

Figure 28. Switch Node and Output Ripple of the -9-V Rail With  $V_{IN} = 5$  V and no Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 20 mV/div, 5 µs/div

Figure 29. Switch Node and Output Ripple of the -9-V Rail with  $V_{\rm IN}=5$  V and 85-mA Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 100 mV/div, 10  $\mu$ s/div

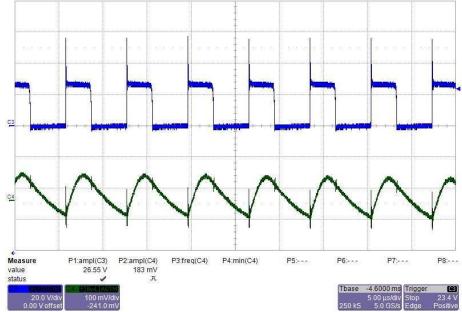

Figure 30. Switch Node and Output ripple of the 15-V Rail with  $V_{\rm IN}$  = 12 V and no Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 20 mV/div, 10 µs/div

Figure 31. Switch Node and Output ripple of the 15-V Rail with  $V_{IN}$  = 12 V and 180-mA Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5 µs/div

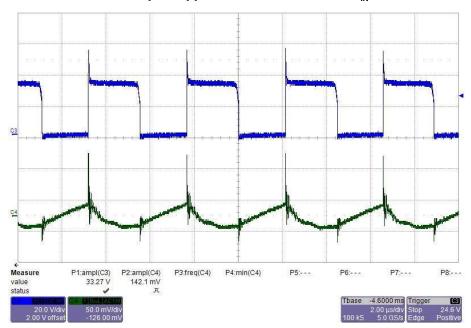

Measure P1:ampl(C3) P2:ampl(C4) P3:freq(C4) P4:min(C4) P5:-- P6:-- P7:-- P8:--- P8:--- P8:--- P7:-- P8:--- P8:--- P7:-- P8:--- P8:-- P8:--- P8

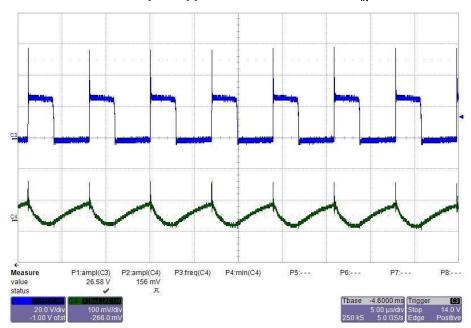

Figure 32. Switch Node and Output ripple of the -9-V Rail with  $V_{\text{IN}} = 12 \text{ V}$  and no Load

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 10 mV/div, 5 µs/div

Figure 33. Switch Node and Output Ripple of the -9-V Rail With  $V_{\rm IN}=12~V$  and  $180-{\rm mA}$  Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5  $\mu s/\text{div}$

Measure P1:ampl(C3) P2:ampl(C4) P3:freq(C4) P4:min(C4) P5:--- P6:--- P7:--- P8:--- P8:---

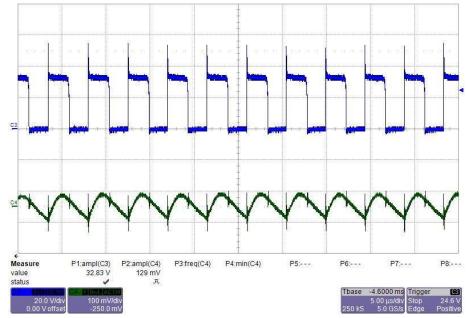

Figure 34. Switch Node and Output Ripple of the 15-V Rail With  $V_{\rm IN}$  = 18 V and no Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 20 mV/div, 5 µs/div

Figure 35. Switch Node and Output Ripple of the +15-V Rail With  $V_{\rm IN}$  = 18 V and 180-mA Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5 µs/div

Figure 36. Switch Node and Output Ripple of the -9-V Rail With  $V_{IN}=18~V$  and no Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 20 mV/div, 5 µs/div

Figure 37. Switch Node and Output Ripple of the -9-V Rail With  $V_{\rm IN}=18~V$  and  $180-{\rm mA}$  Load

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, 2  $\mu$ s/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div, 3  $\mu$ s/div, 2  $\mu$ s/div, 3  $\mu$ s/div

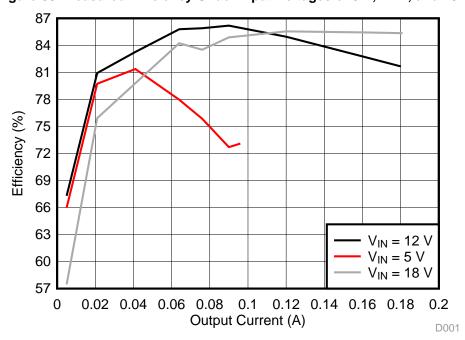

## 3.2.4 Efficiency

Figure 38 shows the measured efficiency of the flyback converter designed with LM5180-Q1 over the full load range. Around 86% peak efficiency is achieved with the input voltages of 5 V, 12 V, and 18 V, respectively.

Figure 38. Measured Efficiency Under Input Voltages of 5 V, 12 V, and 18 V

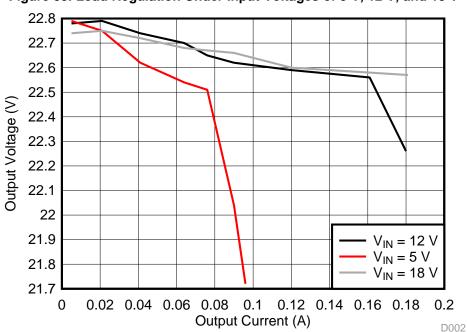

# 3.2.5 Load Regulation

Load regulation measurements show the % deviation from nominal output voltage as a function of output current. Figure 39 shows the measured result of the flyback converter designed with the LM5180-Q1 device. The load regulation is measured with the input voltages of 5 V, 12 V, and 18 V, respectively.

Figure 39. Load Regulation Under Input Voltages of 5 V, 12 V, and 18 V

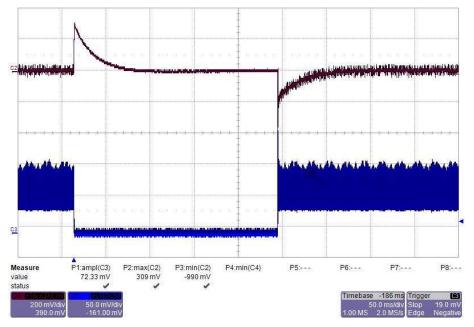

#### 3.2.6 Load Transients

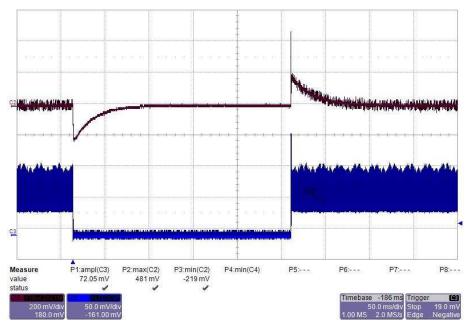

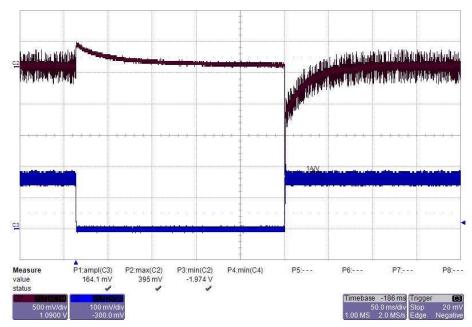

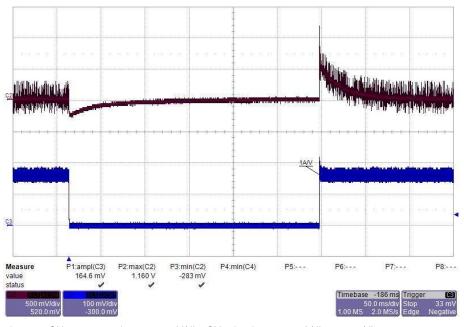

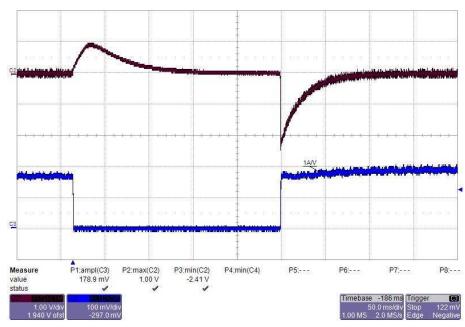

This section shows load transient measurements of the flyback converter designed with the LM5180-Q1 device. Load transient response presents how well a power supply copes with the changes in the load current demand. During the test the load is switching from 0 to full under input voltages of 5 V, 12 V, and 18 V, respectively.

Figure 40. Load Transient Response of the 15-V Rail Under  $V_{IN}$  = 5 V and  $I_{OUT}$  Switching Between 0 and 80 mA

From top to bottom: CH2: output voltage 200 mV/div, CH3: load current 500 mA/div, 50 ms/div

Figure 41. Load Transient Response of the -9-V Rail Under  $V_{IN} = 5$  V and  $I_{OUT}$  Switching Between 0 and 80 mA

From top to bottom: CH2: output voltage 200 mV/div, CH3: load current 500 mA/div, 50 ms/div

Figure 42. Load Transient Response of the 15-V Rail Under  $V_{\rm IN}$  = 12 V and  $I_{\rm OUT}$  Switching Between 0 and 180 mA

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

Figure 43. Load Transient Response of the -9-V Rail Under  $V_{\text{IN}}$  = 12 V and  $I_{\text{OUT}}$  Switching Between 0 and 180 mA

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

Figure 44. Load Transient Response of the 15-V Rail Under  $V_{IN}$  = 18 V and  $I_{OUT}$  Switching Between 0 and 180 mA

From top to bottom: CH2: output voltage 1 V/div, CH3: load current 1 A/div, 50 ms/div

Figure 45. Load Transient Response of the -9-V Rail Under  $V_{\text{IN}}$  = 18 V and  $I_{\text{OUT}}$  Switching Between 0 and 180 mA

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

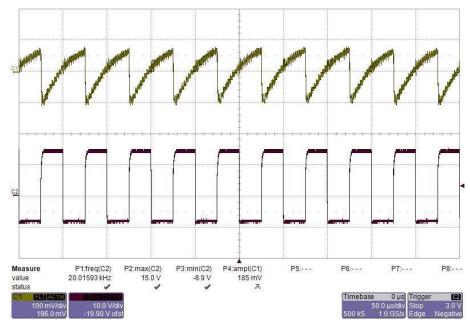

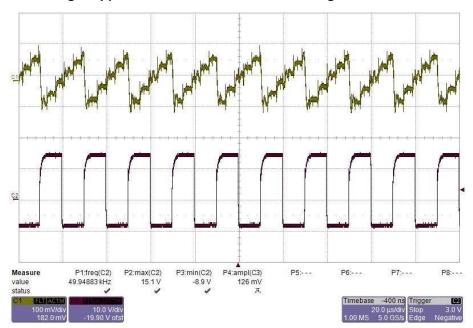

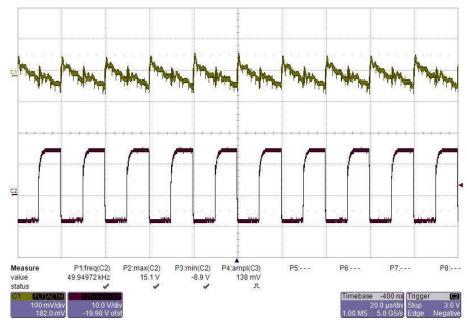

# 3.2.7 Voltage Ripple While Switching IGBT

The flyback converter designed with the LM5180-Q1 device is connected to the isolated gate drivers (ISO5852S-Q1) and the 1200-V IGBT module for checking the voltage ripple during the switching transients. The IGBTs are switched at 20-kHz and 50-kHz frequency, respectively.

Figure 46. Voltage Ripple of the 15-V Rail While Switching the IGBT Module at 20 kHz

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 50 µs/div

| Measure | P1.freq(C2) | P2:max(C2) | P3:min(C2) | P4:mpl(C3) | P5:--- | P6:--- | P7:--- | P8:--- | P8:--- | P8:--- | P7:--- | P8:--- | P

Figure 47. Voltage Ripple of the -9-V Rail While Switching the IGBT Module at 20 kHz

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 50 µs/div

Figure 48. Voltage Ripple of the 15-V Rail While Switching the IGBT Module at 50 kHz

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 20  $\mu$ s/div

Figure 49. Voltage Ripple of the -9-V Rail While Switching the IGBT Module at 50 kHz

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 20 µs/div

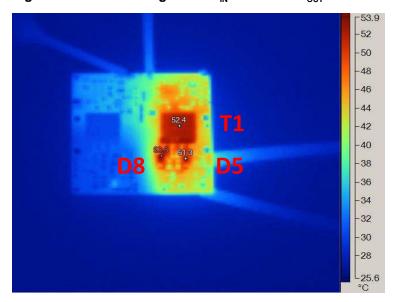

# 3.2.8 Thermal Image

The thermal of the flyback converter is measured under the full-load conditions. The circuit runs at room temperature for 30 minutes. A 12-V nominal voltage is applied. The converter is loaded with 180 mA. Figure 50 shows the thermal image of the board.

Figure 50. Thermal Image With  $V_{\rm IN}$  = 12 V and  $I_{\rm OUT}$  = 180 mA

T1: flyback transformer, D8 and D5: secondary rectification diode

## 3.2.9 High-Voltage Test

The bias supply is connected to the power stage and the IGBT module (FF150R12MS4G) for high-voltage tests.

#### 3.2.9.1 Double Pulse Test

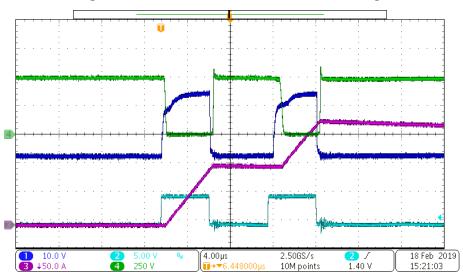

The double test is performed under high voltage and to evaluate the switching parameters of the IGBT and the performance of the isolated gate driver. The test is considered as one periodical snapshot of the system, and it is done with a purely inductive load. The driver parameters of switching speed, thermal, parasitic oscillations can be observed.

During the test, 500 V voltage is applied on the DC bus. The pulse train consists of two pulses with a repetition frequency of about 100 kHz. The widths of two pulses are both 4.5  $\mu$ s. The delay is set to be 5.5  $\mu$ s for the voltage and currents to settle out. The rise and fall time of the pulses are set as 5 ns.

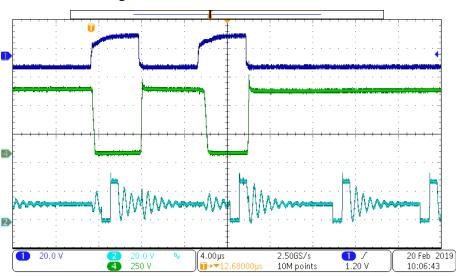

Figure 51. Double Pulse Test on the Power Stage

(From top to bottom: CH4: IGBT Vds voltage 250 V/div, CH1: IGBT gate signal, 10 V/div, CH2: PWM signal at ISO5852s-Q1 input, 5 V/div, CH3: Inductor current, 50 A/div, 4 µs/div)

Figure 52. dv/dt at the IGBT Vds Voltage Turn-off Transient (6 V/ns)

CH4: IGBT Vds voltage 250 V/div, 100 ns/div

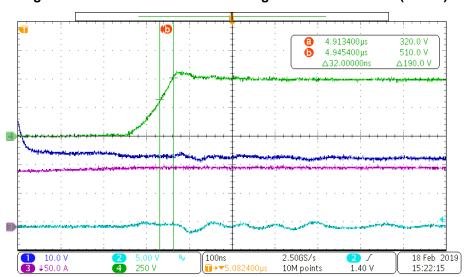

#### 3.2.9.2 CMTI

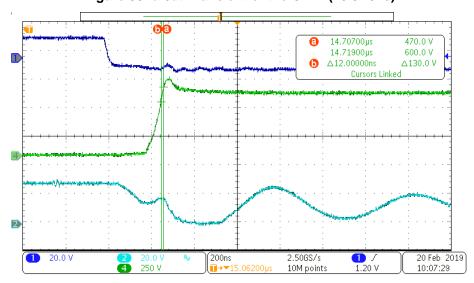

The TI design is connected to a high-voltage DC bus for the high-voltage immunity test. Common-mode transient immunity (CMTI) is a maximum tolerable rate of rise or fall of the common mode voltage applied between two isolated circuits. The unit is normally in kV/µs or V/ns. High CMTI means that the two isolated circuits, both transmitter side and receiver side, function well when striking the insulation barrier with very high rise (positive) slew rate, or high fall (negative) slew rate. For CMTI testing, the peak common-mode voltage should not exceed the allowed maximum repetitive working voltage between the two isolated circuits.

During the test, 570-V DC bus voltage is applied on the DC bus. A 20-µH air core inductor is connected between DC bus+ and IGBT half bridge neutral to bypass the high-side IGBT. The DC bus- terminal is connected to the low voltage ground which is also the bias supply primary-side ground. The low-side IGBT is pulsed twice. Hence, a pulsed high voltage is imposed between the primary and secondary grounds of high-side bias supply. The switch node of the high side bias supply is measured.

Testing waveforms on LM5180-Q1 based bias supply are shown in Figure 53 through Figure 55. The IGBT is switched with 570 V DC bus voltage and at 10.8 V/ns speed of dv/dt. Observe that the supply operates smoothly without interruption.

Figure 53. CMTI Test With Double Pulses

From top to bottom: CH1: IGBT gate signal, 20 V/div, CH4: IGBT Vds voltage, 250 V/div, CH2: LM5180-Q1 switch node voltage, 20 V/div, 100 µs/div

Figure 54. CMTI Waveforms Zoomed in

From top to bottom: CH1: IGBT gate signal, 20 V/div, CH4: IGBT Vds voltage, 250 V/div, CH2: LM5180-Q1 switch node voltage, 20 V/div, 4 µs/div

Figure 55. dv/dt Transient of the CMTI (10.8 V/ns)

From top to bottom: CH1: IGBT gate signal, 20 V/div, CH4: IGBT Vds voltage, 250 V/div, CH2: LM5180-Q1 switch node voltage, 20 V/div, 200 ns/div

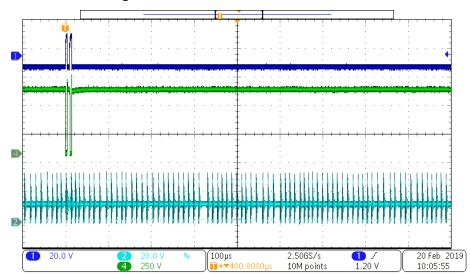

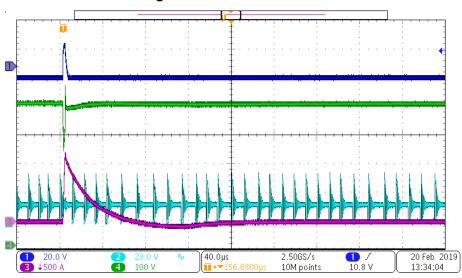

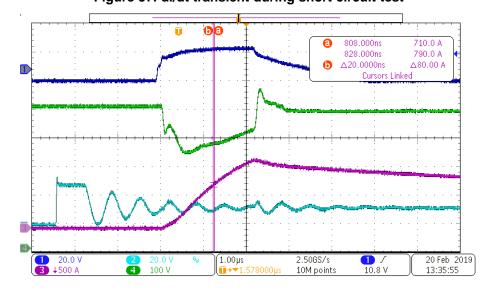

## 3.2.9.3 Short-Circuit Test

The IGBT module is turned on into short to measure the performance of power stage and the immunity of bias supplies under high di/dt. The high-side IGBT is shorted with thick cable with minimized impedance. The low-side IGBT is pulsed once and turned on into short. The switch node of the high-side bias supply is measured. The IGBT is switched with 500-V DC bus voltage and at 4 A/ns speed of di/dt. Observe that the supply operates smoothly without interruption.

Figure 56. Short-Circuit Test

From top to bottom: CH1: IGBT gate signal, 20 V/div, CH4: IGBT Vds voltage, 100 V/div, CH2: LM5180-Q1 switch node voltage 20/div, CH3: load current flowing from drain to source of the IGBT, 500 A/div, 40 µs/div

Figure 57. di/dt transient during short circuit test

From top to bottom: CH1: IGBT gate signal, 20 V/div, CH4: IGBT Vds voltage, 100 V/div, CH2: LM5180-Q1 switch node voltage 20/div, CH3: load current flowing from drain to source of the IGBT, 500 A/div, 1 µs/div

Design Files www.ti.com

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-020015.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-020015.

## 4.3 PCB Layout Recommendations

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-020015.

## 4.3.2 Layout Guidelines

The TIDA-020015 implements a 2-layer PCB. The board material, copper thickness, and the dielectric distance in between are shown in Figure 58.

Thickness Dielectric Coverlay Material Pullback (mil) Orientation Layer Name Type (mil) Material Expansion Top Overlay Overlay Top Solder Solder Mask. Surface Mat 0.4 Solder Resist 3.5 0 1.4 Top Layer Signal Copper Top 59.2 FR-4 4.8 Dielectric1 Dielectric Core **Bottom Layer** Signal Copper 1.4 Bottom 0.4 Solder Resist Bottom Solder Solder Mask. Surface Mat. 3.5 0 Bottom Over... Overlay

Figure 58. TIDA-020015 Layer Stack

## 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-020015.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-020015.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-020015.

#### 5 Related Documentation

- 1. Texas Instruments, Automotive Wide  $V_{IN}$  Front-End Power Reference Design w/Cold Crank Operation and Transient Protection

- 2. Texas Instruments, HEV/EV Traction Inverter Power Stage Reference Design With 3 Types of IGBT/SiC Bias-Supply Solutions

- 3. Texas Instruments, 98.6% Efficiency, 6.6-kW Totem-Pole PFC Reference Design for HEV/EV Onboard Charger Reference Design

- 4. Texas Instruments, Automotive Dual Channel SiC MOSFET Gate Driver Reference Design With Two Level Turn-Off Protection

www.ti.com Related Documentation

#### 5.1 Trademarks

E2E is a trademark of Texas Instruments.

Altium Designer is a registered trademark of Altium LLC or its affiliated companies.

Coilcraft is a registered trademark of Coilcraft Inc..

All other trademarks are the property of their respective owners.

# 5.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

## 6 About the Author

**Xun Gong** is an Automotive Systems Engineer at Texas Instruments, where he is responsible for developing reference design solutions for HEV/EV powertrain applications. Xun brings to this role expertise in the fields of onboard charger, DC/DC converter, and traction inverter with IGBT and SiC (Silicon Carbide) power transistors. Xun achieved his Ph.D. in Electrical Engineering from Delft University of Technology in Delft, Netherlands. Xun Gong won the 1st prize paper of the Academic Journal IEEE Transactions on Power Electronics in 2014.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated