User's Guide SLAU554A–March 2014–Revised July 2014

# AFE5401-Q1, 4-Channel, Integrated Analog Front-end Evaluation Module

This user's guide gives a general overview of the AFE5401-Q1 evaluation module (EVM) and provides a general description of the features and functions to be considered while using this module. This manual is applicable to the AFE5401-Q1 integrated analog front-end. The AFE5401-Q1 EVM provides a platform for evaluating the integrated signal chain under various signal, clock, reference, and ADC output formats.

### Contents

| 1     | AFE54 | 101-Q1 EVM Kit Contents                                                | 4  |

|-------|-------|------------------------------------------------------------------------|----|

| 2     | GUI S | oftware Installation                                                   | 5  |

|       | 2.1   | High Speed Data Converter Pro (HSDCpro) GUI Installation (TSW1400 GUI) | 5  |

|       | 2.2   | AFE5401-Q1 EVM GUI Installation                                        | 10 |

| 3     | AFE54 | 101-Q1 EVM Header and Test Points                                      | 17 |

|       | 3.1   | AFE5401-Q1 EVM Header Configuration                                    | 17 |

|       | 3.2   | AFE5401-Q1 EVM Test Points                                             | 19 |

| 4     | Setup | for Testing AFE5401-Q1 EVM                                             | 20 |

|       | 4.1   | External Connections                                                   | 20 |

|       | 4.2   | TSW1400 and AFE5401-Q1 GUI Software Setups                             | 22 |

| 5     | Captu | ring a RAMP Test Pattern                                               | 27 |

| 6     | Captu | ring a Sinusoidal Input                                                | 33 |

| 7     |       | 101-Q1 GUI Software in Detail                                          |    |

|       | 7.1   | Read Me First Tab                                                      | 38 |

|       | 7.2   | TOP LEVEL SETTINGS Tab                                                 | 40 |

|       | 7.3   | DIAGNOSTICS & TEST MODES Tab                                           | 48 |

|       | 7.4   | Low Level View Tab                                                     | 49 |

| 8     | AFE54 | 401-Q1 EVM Schematic                                                   | 50 |

| 9     | AFE54 | 401-Q1 EVM Bill of Materials (BOM)                                     | 59 |

| 10    | AFE54 | 101-Q1 EVM Layout                                                      | 62 |

| Appen |       | Blind Capture of RAMP Test Pattern                                     |    |

| Appen | dix B | FPGA Triggered Capture of a RAMP Test Pattern                          |    |

### List of Figures

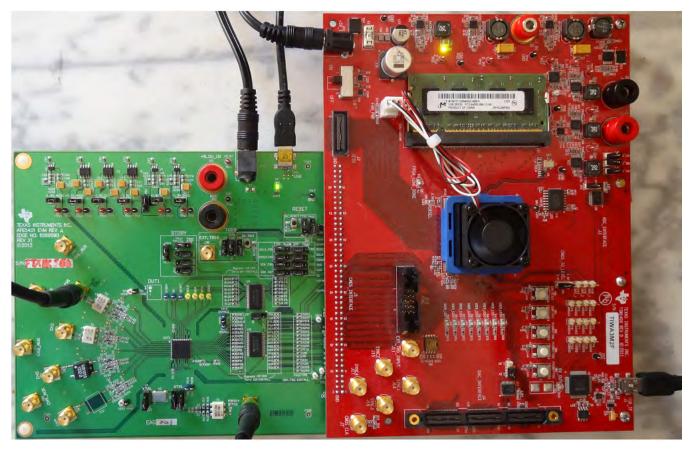

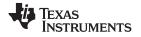

| 1  | AFE5401-Q1 EVM (Green) with TSW1400 Capture Card (Red) | 4  |

|----|--------------------------------------------------------|----|

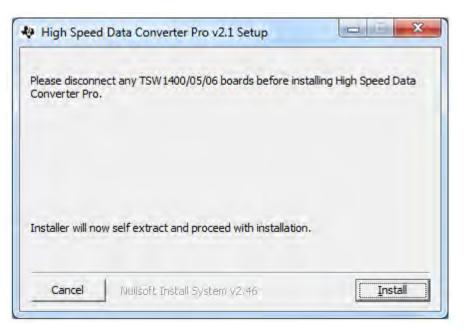

| 2  | HSDCpro Install (a)                                    |    |

| 3  | HSDCpro Install (b)                                    | 6  |

| 4  | HSDCpro Install (c)                                    | 7  |

| 5  | HSDCpro Install (d)                                    | 7  |

| 6  | HSDCpro Install (e)                                    | 8  |

| 7  | HSDCpro Install (f)                                    | 8  |

| 8  | HSDCpro Install (g)                                    | 9  |

| 9  | HSDCpro Install (h)                                    | 9  |

| 10 | HSDCpro Install (i)                                    | 10 |

| 11 | AFE5401-Q1 GUI Install (a)                             | 10 |

| 12 | AFE5401-Q1 GUI Install (b)                             | 11 |

|    |                                                        |    |

| www. | ti.com |

|------|--------|

|------|--------|

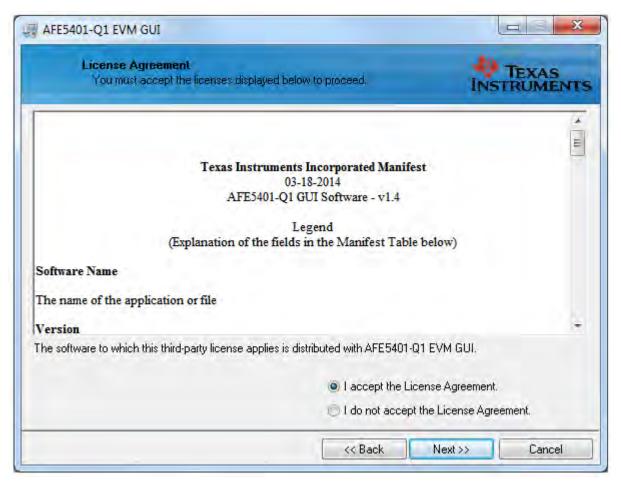

| 13 | AFE5401-Q1 GUI Install (c)                             | 12 |

|----|--------------------------------------------------------|----|

| 14 | AFE5401-Q1 GUI Install (c)                             |    |

| 15 | AFE5401-Q1 GUI Install (d)                             |    |

| 16 | AFE5401-Q1 GUI Install (e)                             | 15 |

| 17 | AFE5401-Q1 GUI Install (f)                             |    |

| 18 | AFE5401-Q1 EVM Default Header Configuration            |    |

| 19 | TSW1400 and AFE5401-Q1 Setup                           |    |

| 20 | TSW1400 Mated to AFE5401-Q1                            |    |

| 21 | TSW1400 GUI Setup (a)                                  |    |

| 22 | TSW1400 GUI Setup (b)                                  |    |

| 23 | TSW1400 GUI Setup (c)                                  | 23 |

| 24 | TSW1400 GUI Setup (d)                                  | 24 |

| 25 | TSW1400 GUI Setup (e)                                  | 24 |

| 26 | TSW1400 GUI Setup (f)                                  |    |

| 27 | AFE5401-Q1 Plug-in GUI Setup (g)                       |    |

| 28 | AFE5401-Q1 Plug-in GUI Setup (h)                       |    |

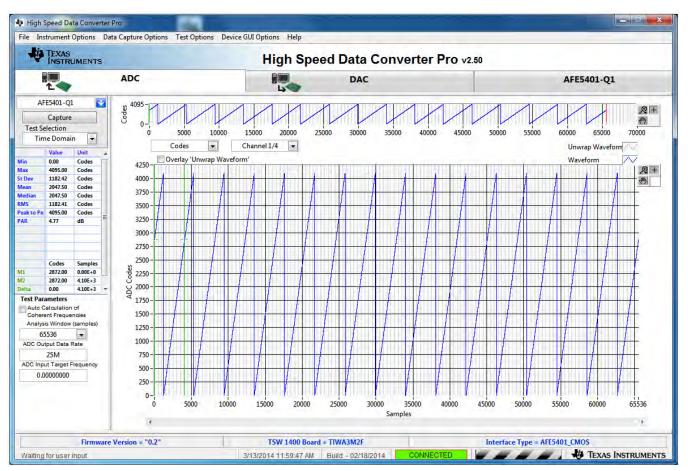

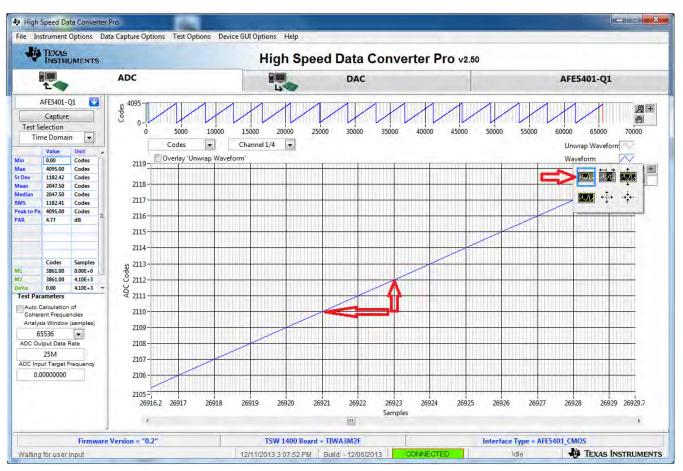

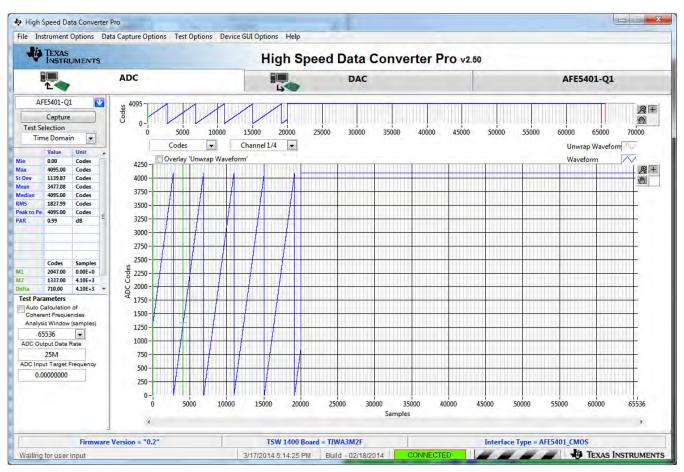

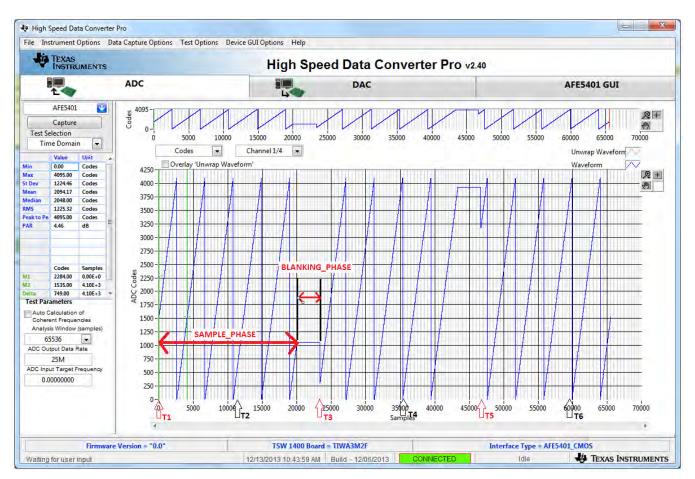

| 29 | AFE5401-Q1 Ramp Capture (a)                            | 27 |

| 30 | AFE5401-Q1 Ramp Capture (b)                            |    |

| 31 | AFE5401-Q1 Ramp Capture (c)                            |    |

| 32 | AFE5401-Q1 Ramp Capture (d)                            |    |

| 33 | AFE5401-Q1 Ramp Capture (e)                            |    |

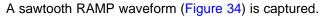

| 34 | AFE5401-Q1 Ramp Capture (f)                            |    |

| 35 | AFE5401-Q1 Ramp Capture (g)                            |    |

| 36 | AFE5401-Q1 Ramp Capture (h)                            |    |

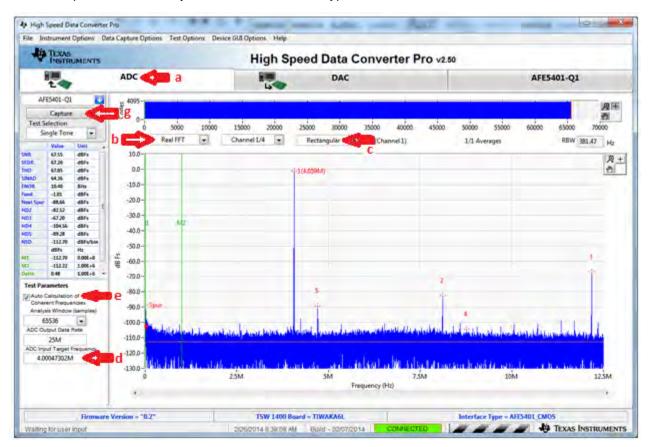

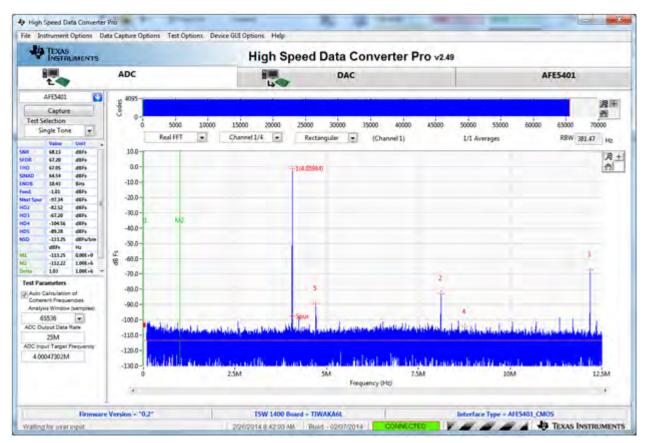

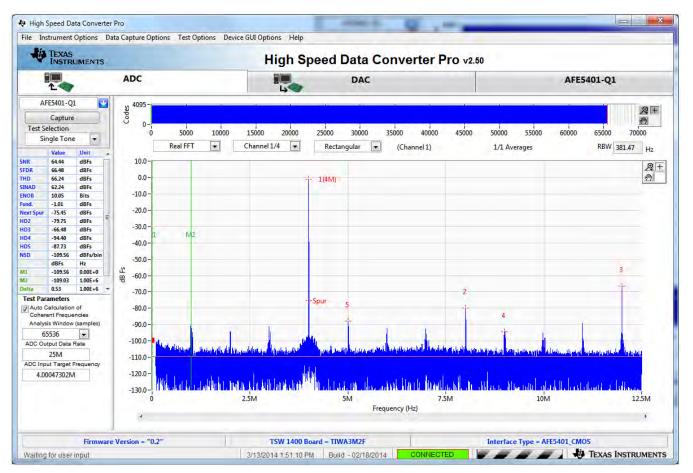

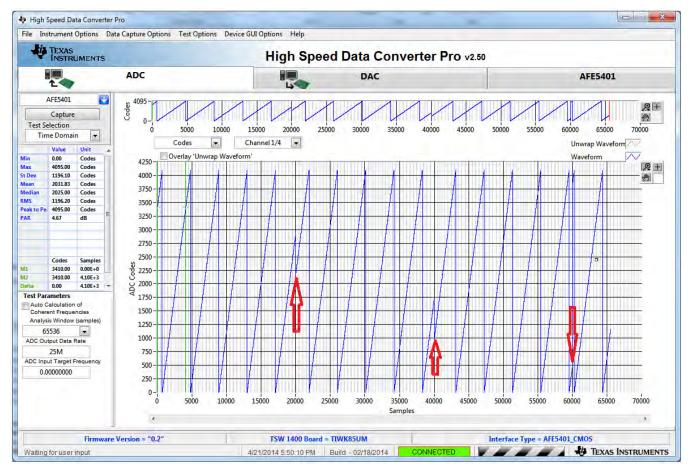

| 37 | AFE5401-Q1 Sine Capture (a)                            | 33 |

| 38 | AFE5401-Q1 Sine Capture (b)                            | 33 |

| 39 | AFE5401-Q1 Sine Capture (c)                            | 34 |

| 40 | AFE5401-Q1 Sine Capture (d)                            | 35 |

| 41 | AFE5401-Q1 Sine Capture (e)                            | 36 |

| 42 | AFE5401-Q1 Sine Capture (f)                            | 37 |

| 43 | AFE5401-Q1 Sine Capture (g)                            | 38 |

| 44 | AFE5401-Q1 Read Me First GUI Tab (a)                   | 39 |

| 45 | AFE5401-Q1 Read Me First GUI Tab (b)                   | 39 |

| 46 | AFE5401-Q1 TOP LEVEL SETTINGS Tab                      | 40 |

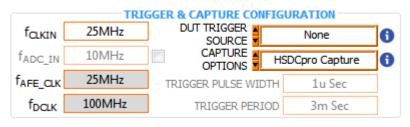

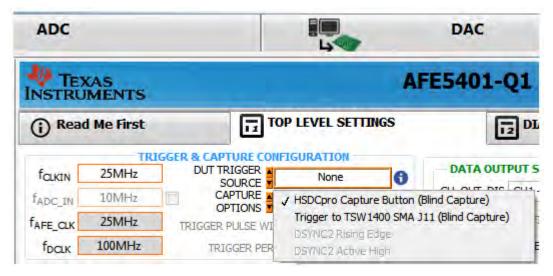

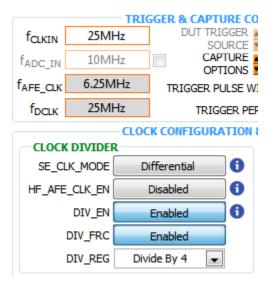

| 47 | AFE5401-Q1 TRIGGER & CAPTURE CONFIGURATION Section (a) | 41 |

| 48 | AFE5401-Q1 TRIGGER & CAPTURE CONFIGURATION Section (b) | 41 |

| 49 | AFE5401-Q1 TOP LEVEL SETTINGS Tab (c)                  | 42 |

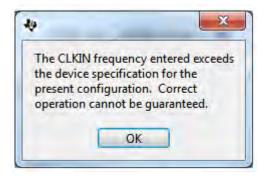

| 50 | AFE5401-Q1 TRIGGER & CAPTURE CONFIGURATION Section (e) | 42 |

| 51 | AFE5401-Q1 TRIGGER & CAPTURE CONFIGURATION Section (f) | 43 |

| 52 | AFE5401-Q1 CLOCK CONFIGURATION & PDN Section (a)       | 43 |

| 53 | AFE5401-Q1 CLOCK CONFIGURATION & PDN Section (b)       | 44 |

| 54 | AFE5401-Q1 CLOCK CONFIGURATION & PDN Section (c)       | 44 |

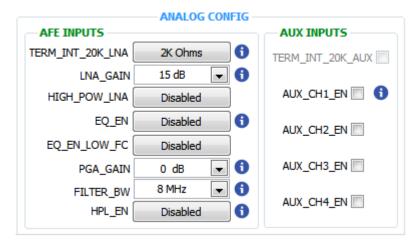

| 55 | AFE5401-Q1 ANALOG CONFIG Section                       | 45 |

| 56 | AFE5401-Q1 DIGITAL CONFIGURATION Section (a)           | 46 |

| 57 | AFE5401-Q1 DIGITAL CONFIGURATION Section (b)           | 47 |

| 58 | AFE5401-Q1 PIN CTRL Section                            | 47 |

| 59 | AFE5401-Q1 LAST WRITE Section                          | 48 |

| 60 | AFE5401-Q1 DIAGNOSTICS & TEST MODES Tab (a)            | 48 |

| 61 | AFE5401-Q1 DIAGNOSTICS & TEST MODES Tab (b)            | 49 |

|    |                                                        |    |

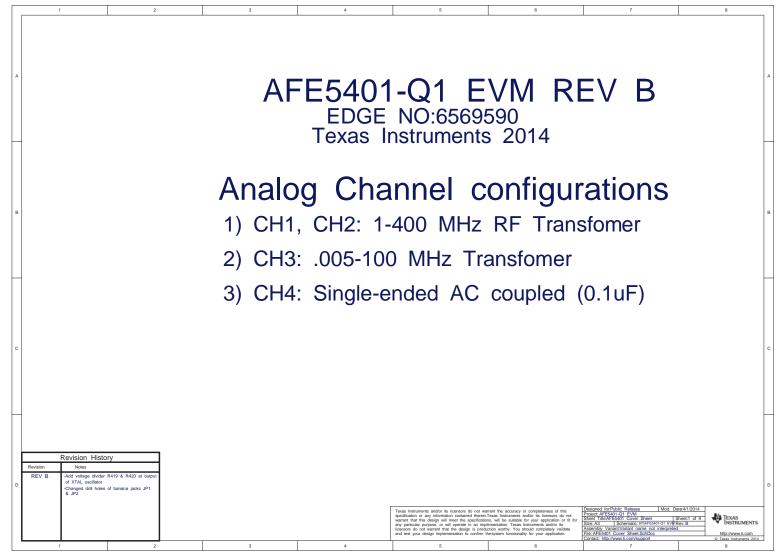

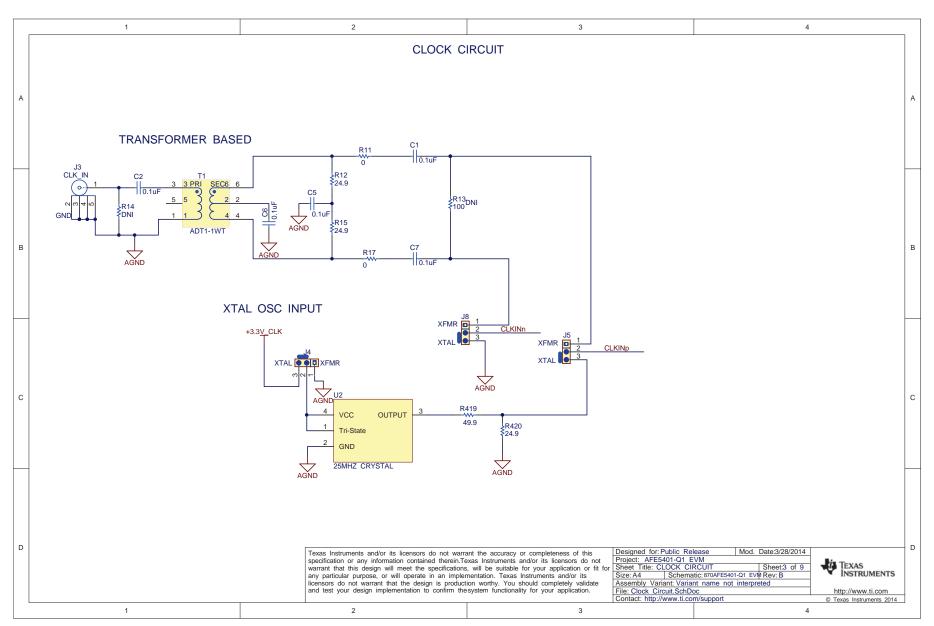

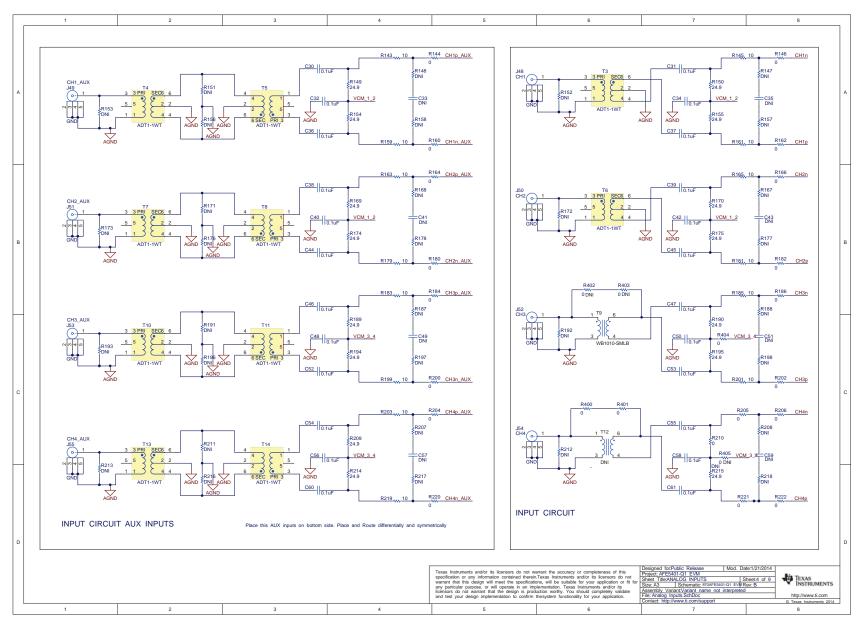

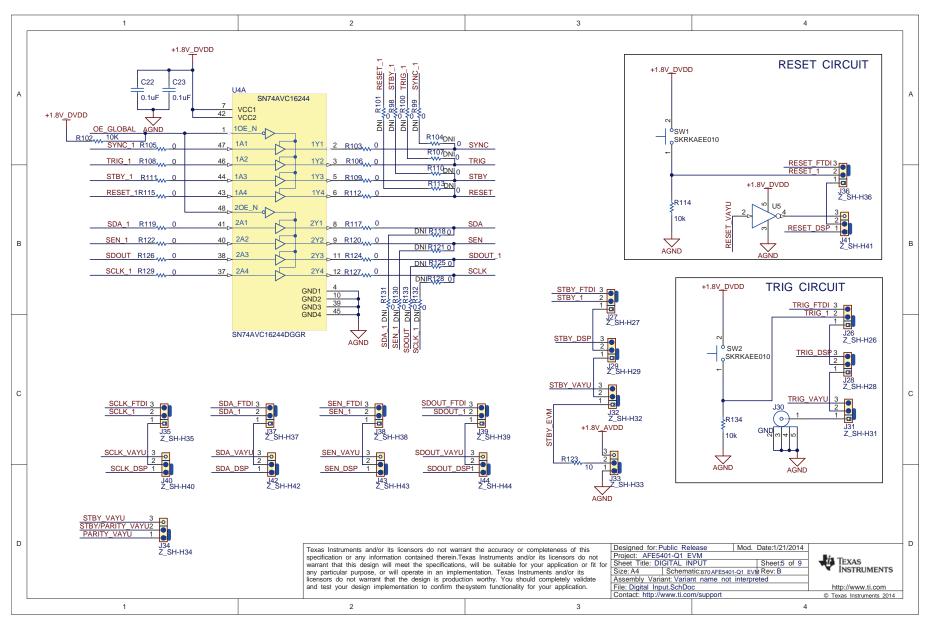

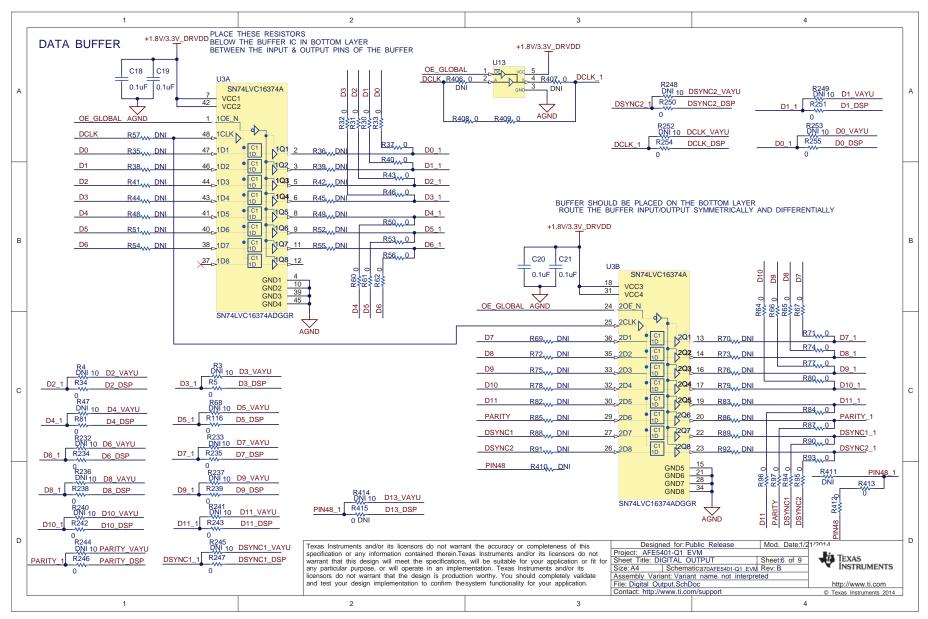

| 62 | AFE5401-Q1 EVM Schematic Sheet 1                   | 50 |

|----|----------------------------------------------------|----|

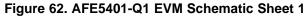

| 63 | AFE5401-Q1 EVM Schematic Sheet 2                   | 51 |

| 64 | AFE5401-Q1 EVM Schematic Sheet 3                   | 52 |

| 65 | AFE5401-Q1 EVM Schematic Sheet 4                   | 53 |

| 66 | AFE5401-Q1 EVM Schematic Sheet 5                   | 54 |

| 67 | AFE5401-Q1 EVM Schematic Sheet 6                   | 55 |

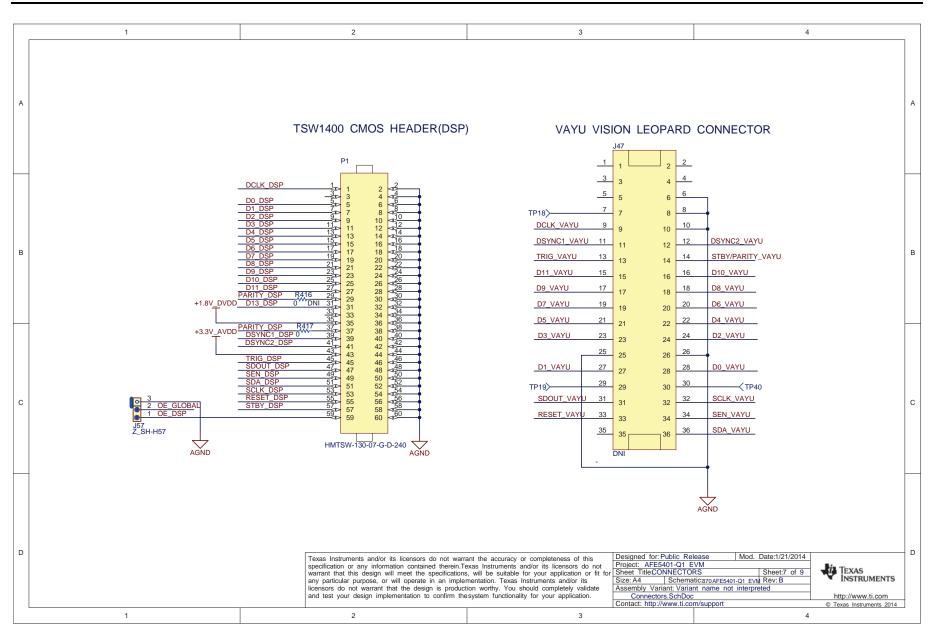

| 68 | AFE5401-Q1 EVM Schematic Sheet 7                   | 56 |

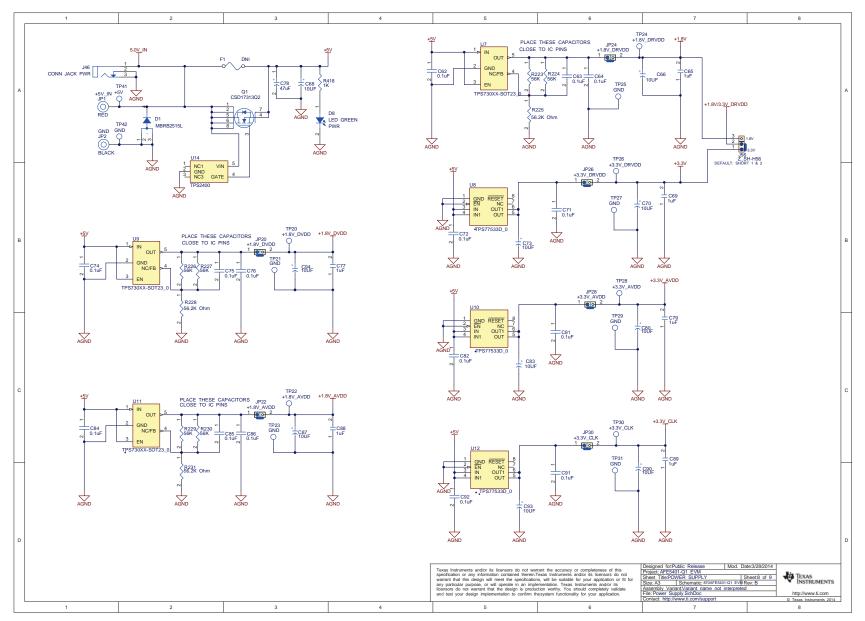

| 69 | AFE5401-Q1 EVM Schematic Sheet 8                   | 57 |

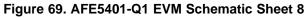

| 70 | AFE5401-Q1 EVM Schematic Sheet 9                   | 58 |

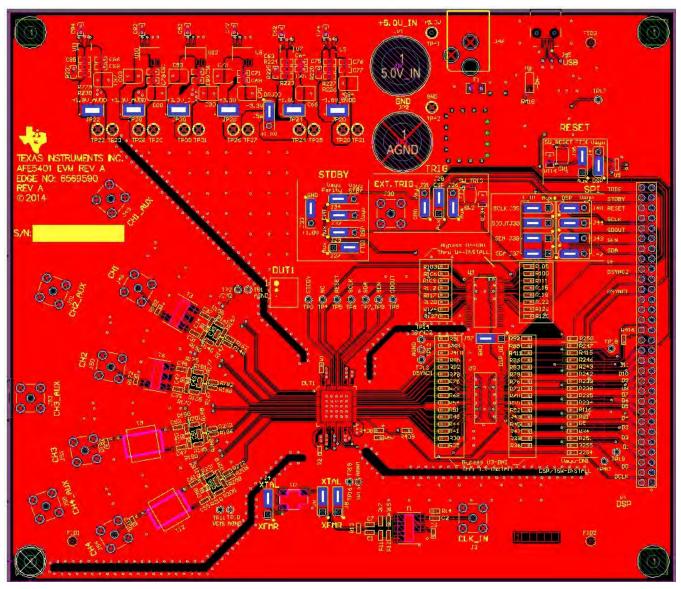

| 71 | AFE5401-Q1 EVM Layout                              |    |

| 72 | GUI Setup for Blind RAMP Test (a)                  | 63 |

| 73 | GUI Setup for Blind RAMP Test (b)                  | 64 |

| 74 | GUI Setup For Blind RAMP Test (c)                  | 65 |

| 75 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (a) | 66 |

| 76 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (b) | 67 |

| 77 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (c) | 68 |

| 78 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (d) | 69 |

| 79 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (e) | 70 |

| 80 | FPGA DSYNC2 Rising Edge Triggered RAMP Capture (f) | 71 |

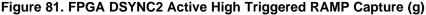

| 81 | FPGA DSYNC2 Active High Triggered RAMP Capture (g) | 72 |

|    |                                                    |    |

#### List of Tables

| 1 | AFE5401-Q1 Header Configuration  | 17 |

|---|----------------------------------|----|

| 2 | AFE5401-Q1 Header Configuration  | 19 |

| 3 | AFE5401-Q1 EVM Bill of Materials | 59 |

#### AFE5401-Q1 EVM Kit Contents

### 1 AFE5401-Q1 EVM Kit Contents

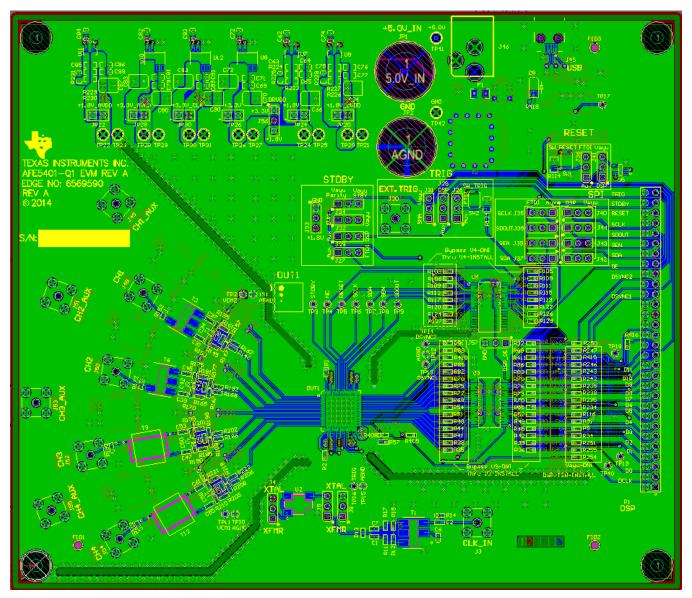

The AFE5401-Q1 EVM is a compact, USB-based evaluation kit for evaluating the AFE5401-Q1, a 4channel analog front-end. The kit consists of (1) AFE5401-Q1EVM, (2) a USB cable for SPI communication to the software GUI, and (3) a +5-V AC/DC adaptor with plug adaptors for powering the EVM. Figure 1 shows an overview of the evaluation setup which includes the TSW1400 Data Capture Card (not included with this kit).

Figure 1. AFE5401-Q1 EVM (Green) with TSW1400 Capture Card (Red)

**TSW1400 EVM**: The high-speed LVDS de-serializer board is required for capturing data from the AFE5401-Q1EVM. The graphical user interface (GUI) software that is available with the EVM, called *High Speed Data Converter Pro*, includes many data analysis features for processing and plotting captured data. The TSW1400 EVM and software can be used to test many of TI's ADCs, DACs, and AFEs. (*NOTE: the TSW1400 capture card is not included with the AFE5401-Q1 EVM Kit and must be ordered separately*). For more information pertaining to be TSW1400EVM, see: http://focus.ti.com/docs/toolsw/folders/print/tsw1400evm.html.

**Equipment**: No external equipment is required to test functionality of the setup. Using the on-EVM crystal oscillator for the input clock and an internally generated RAMP test mode, the CMOS interface can be verified. When signal capture is desired, signal generators, preferably with low-phase noise and harmonic distortion, must be used as source of input signal and input clock in order to get the desired performance. Additionally, band-pass filters (BPF) are required in signal and clock paths to attenuate the harmonics and noise from the generators.

**AFE5401-Q1 EVM**: The AFE5401-Q1 EVM is a compact USB 2.0 based evaluation kit for the AFE5401-Q1, Quad Channel Analog Front-End. This EVM provides versatility to begin evaluation quickly and with no external equipment required as a +5-V AC/DC power supply and an on-board crystal oscillator eliminate the need for these instruments. The EVM supplies a provision for interfacing I/Os via additional external buffering or a secondary Flexible Flat Cable (FFC) connector allowing users to evaluate with their

own DSP platform (in lieu of the TSW1400 capture card). In addition, monitoring the power consumption the individual power supply pins of the AFE5401-Q1 is possible via headers. Finally, the EVM allows for three unique AFE analog input configurations including (1) a transformer with input bandwidth from 1 MHz to 400 MHz, (2) a transformer with input bandwidth from 5 kHz to 100 MHz for low frequency applications and (3) a single-ended AC coupled input drive.

**USB Interface to PC**: USB connections from the AFE5401-Q1EVM and TSW1400EVM to the personal computer (PC) are used for communication from the GUIs to the boards. Section 2 explains the TSW1400 and AFE5401-Q1 GUI installation procedures.

### 2 GUI Software Installation

The AFE5401-Q1 GUI Software provides an easy interface in which to evaluate the AFE5401-Q1. As a plug-in to the *High Speed Data Convertor Pro GUI (HSDCpro)*, control of the AFE5401-Q1 EVM and the TSW1400 Capture Card (available in separate kit from the TI estore) is done with one GUI. The GUI allows for one-click auto configuration of the AFE5401-Q1 using one of several configuration files provided with the installer. Data capture and analysis are performed by *HSDCpro* including fast-Fourier transform (FFT) analysis providing SNR, SFDR, and Harmonic Distortion.

The AFE5401-Q1 EVM and the TSW1400 EVM both require software installations. The following two sections explain where to find and how to install the software properly. Ensure that no USB connections are made to the EVMs until after the installations are complete.

### 2.1 High Speed Data Converter Pro (HSDCpro) GUI Installation (TSW1400 GUI)

From the Texas Instruments website, <u>www.ti.com</u>, search for TSW1400. Under **Technical Documents**, find the **Software** section from which **High Speed Data Converter Pro GUI Installer** can be downloaded and saved (<u>SLWC107</u>). Revision J (Rev J) or higher of HSDCpro is required as earlier versions are not compatible with the AFE5401-Q1 GUI.

Instructions for installing HSDCpro follow:

- Unzip the saved folder and run the installer executable to obtain the menu shown in Figure 2.

- Click the *Install* button.

Figure 2. HSDCpro Install (a)

### GUI Software Installation

- Leave the destination directories as the default and press the Next button as shown in Figure 3. ٠

- NOTE: If a destination directory other than the default directory is used, the AFE5401-Q1 GUI is not found, therefore, it is not invoked as a plug-in tab to HSDCpro.

| Destination Directory<br>Select the primary installation directory.                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All software will be installed in the following locations. To install software into a<br>different locations, click the Browse button and select another directory. |

| Directory for Uick Council Data Converter Box                                                                                                                       |

| Directory for High Speed Data Converter Pro                                                                                                                         |

| C:\Program Files (x86)\Texas Instruments\High Speed Data Converter Pro\<br>Browse                                                                                   |

|                                                                                                                                                                     |

Figure 3. HSDCpro Install (b)

1. Read the License Agreement from Texas Instruments and select *I accept the License Agreement* and press the *Next* button as shown in Figure 4.

| License Agreement<br>You must accept the licenses disp                                                     | played below to proceed.                                                                                                                                      |                 |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| GUI Software Evaluatio                                                                                     | on and Internal Use License Agreement                                                                                                                         |                 |

|                                                                                                            | ving license agreement carefully. This is a le<br>read this license agreement, you will be a<br>the terms of the license agreement. Do not                    | sked            |

| "I have read and agree" unless: (<br>terms of this license agreement of                                    | (1) you are authorized to accept and agree to<br>on behalf of yourself and your company; are<br>be bound by the terms of this legally bir<br>nd your company. | o the<br>nd (2) |

| "I have read and agree" unless: (<br>terms of this license agreement of<br>you intend to enter into and to | (1) you are authorized to accept and agree t<br>on behalf of yourself and your company; ar<br>be bound by the terms of this legally bin                       | o the<br>nd (2) |

Figure 4. HSDCpro Install (c)

(b) Read the License Agreement from National Instruments and *I accept the License Agreement* and press the *Next* button as in Figure 5.

| License Agreement<br>You must accept the licenses displayer                                                                                                                                                                                                                                                | d below to proceed.                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NATIONAL INSTRUMENTS                                                                                                                                                                                                                                                                                       | SOFTWARE LICENSE AGREEMENT                                                                                                                                                                                                                                                                                    |

| AND/OR COMPLETE THE INSTALLATION P<br>DOWNLOADING THE SOFTWARE AND/OR<br>COMPLETE THE INSTALLATION PROCESS<br>AGREEMENT AND YOU AGREE TO BE BOU<br>BECOME A PARTY TO THIS AGREEMENT A<br>CONDITIONS, CLICK THE APPROPRIATE E<br>DO NOT INSTALL OR USE THE SOFTWARE<br>(30) DAYS OF RECEIPT OF THE SOFTWARE | 3. YOU CONSENT TO THE TERMS OF THIS<br>IND BY THIS AGREEMENT. IF YOU DO NOT WISH TO<br>ND BE BOUND BY ALL OF ITS TERMS AND<br>BUTTON TO CANCEL THE INSTALLATION PROCESS,<br>E, AND RETURN THE SOFTWARE WITHIN THIRTY<br>E (WITH ALL ACCOMPANYING WRITTEN MATERIALS,<br>E PLACE YOU OBTAINED THEM. ALL RETURNS |

| The software to which this National Instruments lice                                                                                                                                                                                                                                                       | ense applies is High Speed Data Converter Pro.                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                            | <ul> <li>Eaccept the License Agreement.</li> <li>I do not accept the License Agreement.</li> </ul>                                                                                                                                                                                                            |

Figure 5. HSDCpro Install (d)

#### GUI Software Installation

www.ti.com

3. Press the *Next* button as in Figure 6.

| Start Installation                        |                                                  |                           |

|-------------------------------------------|--------------------------------------------------|---------------------------|

| Review the follow                         | ing summary before continuing                    |                           |

| Upgrading<br>• National Instruments syste | en companyels                                    |                           |

| Adding or Changing                        | ner sområsen näl fild                            |                           |

| High Speed Data Convert                   | er Pro Files                                     |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

|                                           |                                                  |                           |

| sk lihe Next button to begin i            | installation. Click the Back button to change th | ne installation settings. |

| ck. The Next button to begin i            | installation. Click the Back button to change If | ne installation settings. |

### Figure 6. HSDCpro Install (e)

(d) The window in Figure 7 should appear, indicating that the installation is in progress.

| High Speed Data Converter Pro |                      |

|-------------------------------|----------------------|

|                               | [                    |

|                               |                      |

| Overall Progress: 5% Complete |                      |

|                               |                      |

|                               |                      |

|                               |                      |

|                               |                      |

|                               |                      |

|                               |                      |

|                               | S Back Mexils Cancel |

### Figure 7. HSDCpro Install (f)

5. The window shown in Figure 8 appears, indicating Installation Complete. Press the Next button.

| High | Speed Data Converter Pro                        |         | ×            |

|------|-------------------------------------------------|---------|--------------|

|      | Installation Complete                           |         |              |

|      | The installer has finished updating your system |         |              |

|      |                                                 |         |              |

|      |                                                 |         |              |

|      |                                                 |         |              |

|      |                                                 |         |              |

|      |                                                 | Ki Back | Next>> Emith |

Figure 8. HSDCpro Install (g)

(f) The window in Figure 9 appears briefly to complete the process.

| Execut      | e: C:\Users\a0193755\AppData\Loca | al\Temp\HSDCPro\Install\EVM G |

|-------------|-----------------------------------|-------------------------------|

| Show detail | s                                 |                               |

|             |                                   |                               |

|             |                                   |                               |

|             |                                   |                               |

|             |                                   |                               |

Figure 9. HSDCpro Install (h)

#### GUI Software Installation

www.ti.com

7. As shown in Figure 10, a computer restart might be requested depending on whether or not the PC already has the National Instruments' MCR installer. If requested, hit the *Restart* button to complete the installation.

Figure 10. HSDCpro Install (i)

## 2.2 AFE5401-Q1 EVM GUI Installation

The AFE5401-Q1 GUI software can be obtained from TI's local supporting FAE. A zipped file containing the installer shall be provided.

(a) Unzip the folder and run the setup.exe file as administrator by right clicking on it and selecting *Run as administrator* as shown in Figure 11.

| setup.ini      | 3/6/2014 7:5 Or     | <b>en</b><br>In as administrator |          |

|----------------|---------------------|----------------------------------|----------|

| setup.exe      | 5/14/2013 10-10-014 | A 12 12                          | 4 202 14 |

| nidist.id      | 3/6/2014 7:44 AM    | ID File                          | 1 KI     |

| 🌡 supportfiles | 3/10/2014 12:18 PM  | File folder                      |          |

| 📕 license      | 3/10/2014 12:18 PM  | File folder                      |          |

| 🍶 bin          | 3/10/2014 12:17 PM  | File folder                      |          |

| Name           | Date modified       | Туре                             | Size     |

Figure 11. AFE5401-Q1 GUI Install (a)

- 2. Leave the destination directory as the default and press the *Next* button as shown in Figure 12.

- **NOTE:** If a destination directory other than the default directory is used, the AFE5401-Q1 GUI is not found, therefore, it is not invoked as a plug-in tab to HSDCpro.

| FE5401-Q1 EVM GUI                                                                                                                                                |                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Destination Directory<br>Select the primary installation directory.                                                                                              | TEXAS<br>INSTRUMEN |  |

| All software will be installed in the following locations. To install software into<br>different location, click the Browse button and select another directory. | a                  |  |

| Directory for AFE5401-Q1 EVM GUI                                                                                                                                 |                    |  |

| C:\Program Files (x86)\Texas Instruments\AFE5401-Q1 EVM GUI\                                                                                                     | Browse             |  |

|                                                                                                                                                                  |                    |  |

|                                                                                                                                                                  |                    |  |

Figure 12. AFE5401-Q1 GUI Install (b)

#### GUI Software Installation

www.ti.com

3. Read the License Agreement from Texas Instruments, select the I accept the License Agreement button, and then press the Next button, as shown in Figure 13.

| AFE5401-Q1 EVM GUI                                                                                                                                                                                                                                                                                                                                                    |                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| License Agreement<br>You must accept the licenses displayed below to proceed.                                                                                                                                                                                                                                                                                         | TEXAS<br>INSTRUMENTS                                                   |

| Source and Binary Code Internal Use License Age                                                                                                                                                                                                                                                                                                                       | reement                                                                |

| Important - Please carefully read the following license agreen<br>binding. After you read it, you will be asked whether you ac<br>terms. Do not click "I have read and agree" unless: (1) you<br>Materials for your own benefit and personally accept, agree<br>bound by these terms; or (2) you are authorized to, and int<br>these terms on behalf of your company. | ccept and agree to its<br>will use the Licensed<br>to and intend to be |

| Important - Read carefully: In this Agreement "you" means you exercise the rights granted for your own benefit, but it means you                                                                                                                                                                                                                                      |                                                                        |

| <ul> <li>I accept the Licent</li> <li>I do not accept the</li> </ul>                                                                                                                                                                                                                                                                                                  | se Agreement.<br>e License Agreement.                                  |

| < Back                                                                                                                                                                                                                                                                                                                                                                | Next >> Cancel                                                         |

Figure 13. AFE5401-Q1 GUI Install (c)

4. Read the Texas Instruments Software Manifest, select the *I accept the License Agreement* check box, and then press the *Next* button, as shown in Figure 14.

Figure 14. AFE5401-Q1 GUI Install (c)

#### GUI Software Installation

www.ti.com

5. Begin the installation by pressing the *Next* button, as illustrated in Figure 15.

| INSTRUMENTS |

|-------------|

|             |

|             |

|             |

|             |

|             |

Figure 15. AFE5401-Q1 GUI Install (d)

6. The window shown in Figure 16 should appear showing that installation is in progress.

| TEXAS<br>INSTRUMENTS |

|----------------------|

|                      |

|                      |

|                      |

|                      |

|                      |

| lext>> Cancel        |

|                      |

Figure 16. AFE5401-Q1 GUI Install (e)

### GUI Software Installation

www.ti.com

7. Upon complete of installation, the window in Figure 17 appears. Press the *Finish* button to continue.

| AFE5401-Q1 EVM GUI                               |                      |

|--------------------------------------------------|----------------------|

| Installation Complete                            | TEXAS<br>INSTRUMENTS |

| The installer has finished updating your system. |                      |

|                                                  |                      |

|                                                  |                      |

|                                                  |                      |

|                                                  |                      |

| << Ba                                            | ck Next>> Einish     |

Figure 17. AFE5401-Q1 GUI Install (f)

### 3 AFE5401-Q1 EVM Header and Test Points

This section describes the functions of the headers on the EVM. It also provides a list of test points on the EVM that are useful for debug and general-use purposes.

### 3.1 AFE5401-Q1 EVM Header Configuration

The AFE5401-Q1 EVM is flexible in its configurability through the use of 2- and 3-pin headers. The default configuration of the EVM is set to facilitate initial testing by requiring no changes. Table 1 describes the purpose of all headers with the default position highlighted in red or yellow, while Figure 18 shows the default positions on the EVM.

| Jumpe # | Default Config | Pin 1<br>Silkscreen | Pin 3<br>Silkscreen | Circuit            | Description                                                                                                         |

|---------|----------------|---------------------|---------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|

| JP22    | Short pins 1-2 | +1.8V_AVDD          |                     | Power<br>Supply    | Power Supply to DUT pins 19, 24, 62 (AVDD18)                                                                        |

| JP28    | Short pins 1-2 | +3.3V_AVDD          |                     | Power<br>Supply    | Power Supply to DUT pin 18 (AVDD3)                                                                                  |

| JP20    | Short pins 1-2 | +1.8V_DVDD          |                     | Power<br>Supply    | Power Supply to DUT pins 28, 30, 51 (DVDD18)                                                                        |

| JP26    | Short pins 1-2 | +3.3V               |                     | Power<br>Supply    | +3.3V Supply to J56                                                                                                 |

| JP24    | Short pins 1-2 | +1.8V               |                     | Power<br>Supply    | +1.8V Supply to J56                                                                                                 |

| J56     | Short pins 1-2 | +3.3V               | +1.8V               | Power<br>Supply    | Power supply to DUT pins 32, 33, 50 (DRVDD);<br>selects output of (1) JP26, +3.3V or (2) output<br>of JP24, +1.8V   |

| JP30    | Short pins 1-2 | +3.3V_CLK           |                     | Power<br>Supply    | Power Supply to XTAL at U2                                                                                          |

| J33     | Short pins 1-2 | GND                 | +1.8V               | Standby<br>Circuit | Selects Voltage level of STDBY signal (1) GND or (3) +3.3V                                                          |

| J27     | short pins 2-3 | AUX                 | FTDI                | Standby<br>Circuit | Selects STDBY control source: (1) AUX determined by J29 or (3) Device GUI thru FTDI                                 |

| J29     | Short pins 1-2 | AUX                 | DSP                 | Standby<br>Circuit | Selects STDBY control source: (1) AUX determined by J32 or (3) CMOS connector P1                                    |

| J32     | Short pins 1-2 | EVM                 | Vayu                | Standby<br>Circuit | Selects STDBY control source: (1) EVM determined by J33 or (3) Vayu connector J47                                   |

| J34     | Short pins 1-2 | Vayu_Parity         | Vayu_STDBY          | Standby<br>Circuit | For Vayu control only, selects (1) outputs parity<br>from AFE5401-Q1 or (3) inputs STDBY from<br>Vayu connector J47 |

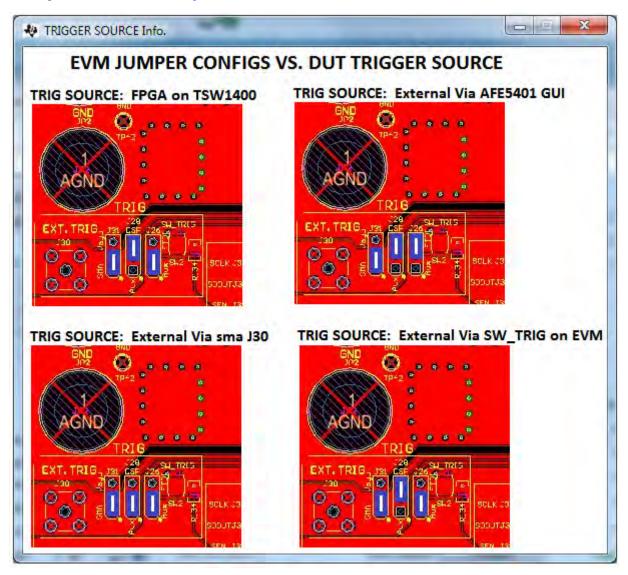

| J26     | Short pins 1-2 | Aux                 | FTDI                | Trigger            | Selects DUT Trigger signal source: (1) AUX determined by J28 or (3) Device GUI thru FTDI                            |

| J28     | short pins 2-3 | Aux                 | DSP                 | Trigger            | Selects DUT Trigger signal source: (1) AUX determined by J31 or (3) CMOS connector P1                               |

| J31     | Short pins 1-2 | SMA                 | Vayu                | Trigger            | Selects DUT Trigger signal source: (1) SMA<br>J30, EXT. TRIG or (3) Vayu connector J47                              |

| J41     | Short pins 1-2 | DSP                 | Vayu                | Reset              | Selects RESET control source when sma J36 is set to Aux (1) from DSP or (3) from Vayu                               |

| J36     | short pins 2-3 | Aux                 | FTDI                | Reset              | Selects DUT RESET signal source: (1) Aux determined by J41 or (3) Device GUI thru FTDI                              |

| J35     | short pins 2-3 | Aux                 | FTDI                | Reset              | Selects DUT SCLK signal source: (1) Aux determined by J40 (3) Device GUI thru FTDI                                  |

| J40     | short pins 1-2 | DSP                 | Vayu                | SPI                | Selects SCLK signal source: (1) CMOS connector P1 (3) Vayu connector J47                                            |

| J39     | short pins 2-3 | Aux                 | FTDI                | SPI                | Selects DUT SDOUT signal path: (1) Aux determined by J44 (3) Device GUI thru FTDI                                   |

| J44     | short pins 1-2 | DSP                 | Vayu                | SPI                | Selects SDOUT signal path: (1) CMOS connector P1 (3) Vayu connector J47                                             |

Table 1. AFE5401-Q1 Header Configuration

| Jumpe # | Default Config | Pin 1<br>Silkscreen | Pin 3<br>Silkscreen | Circuit | Description                                                                                                                                                  |

|---------|----------------|---------------------|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J38     | short pins 2-3 | Aux                 | FTDI                | SPI     | Selects DUT SEN signal source: (1) Aux determined by J43 (3) Device GUI thru FTDI                                                                            |

| J43     | short pins 1-2 | DSP                 | Vayu                | SPI     | Selects SEN signal source: (1) CMOS<br>connector P1 (3) Vayu connector J47                                                                                   |

| J37     | short pins 2-3 | Aux                 | FTDI                | SPI     | Selects DUT SDA signal source: (1) Aux determined by J42 (3) Device GUI thru FTDI                                                                            |

| J42     | short pins 1-2 | DSP                 | Vayu                | SPI     | Selects SDA signal source: (1) CMOS<br>connector P1 (3) Vayu connector J47                                                                                   |

| J57     | short pins 2-3 | DSP_OE              | GND                 | SPI     | Selects enablebar source for flip flop at U4<br>between (1)FPGA via P1 or (2) GND                                                                            |

| J4      | short pins 2-3 | XFMR                | XTAL                | CLOCK   | Power Supply for on-board 25MHz XTAL oscillator                                                                                                              |

| J5      | short pins 2-3 | XFMR                | XTAL                | CLOCK   | Selects clock input configuration to (1)<br>differential signal input to SMA J3, CLK_IN, thru<br>transformer or (3) single-ended on-board XTAL<br>oscillator |

| 8L      | short pins 2-3 | XFMR                | XTAL                | CLOCK   | Selects clock input configuration to (1)<br>differential signal input to SMA J3, CLK_IN, thru<br>transformer or (3) single-ended on-board XTAL<br>oscillator |

# Table 1. AFE5401-Q1 Header Configuration (continued)

Figure 18. AFE5401-Q1 EVM Default Header Configuration

# 3.2 AFE5401-Q1 EVM Test Points

Table 2 lists all the test points on the AFE5401-Q1-Q1 EVM and the purpose of each test point.

| Testpoint | Silkscreen | Circuit           | Description                                    |

|-----------|------------|-------------------|------------------------------------------------|

| TP2       | VCM2       | Analog Inputs VCM | Common Mode Voltage Node for Analog Inputs 1-2 |

| TP1       | AGND       | Analog Inputs VCM | Analog Ground                                  |

| TP11      | VCM1       | Analog Inputs VCM | Common Mode Voltage Node for Analog Inputs 3-4 |

| TP10      | AGND       | Analog Inputs VCM | Analog Ground                                  |

| TP3       | STDBY      | Digital Input     | Input to STBY pin 59                           |

| TP4       | NC         | n/a               |                                                |

| TP5       | RESET      | Digital Input     | Input to RESET pin 57                          |

Table 2. AFE5401-Q1 Header Configuration

AFE5401-Q1, 4-Channel, Integrated Analog Front-end Evaluation Module

| Testpoint | Silkscreen | Circuit         | Description                             |  |  |

|-----------|------------|-----------------|-----------------------------------------|--|--|

| TP6       | SCLK       | Digital Input   | Input to SCLK pin 56                    |  |  |

| TP7       | SDA        | Digital Input   | Input to SDATA pin 55                   |  |  |

| TP8       | SEN        | Digital Input   | Input to SEN pin 55                     |  |  |

| TP9       | SDOUT      | Digital Output  | Input to SDOUT pin 53                   |  |  |

| TP14      | DSYNC2     | Frame Clock     | Output from DSYCN2 pin 27               |  |  |

| TP12      | AGND       | Frame Clock     | Analog Ground                           |  |  |

| TP13      | DSYNC1     | Frame Clock     | Output from DSYCN2 pin 26               |  |  |

| TP16      | TRIG       | Frame Clock     | Input to TRIG pin 25                    |  |  |

| TP15      | AGND       | Frame Clock     | Analog Ground                           |  |  |

| TP21      | REFOUT     | CDC Cock Device | Output from REFOUT pin 29 of CDC device |  |  |

| TP17      | n/a        | not used        |                                         |  |  |

| TP18      | n/a        | not used        |                                         |  |  |

| TP19      | n/a        | not used        |                                         |  |  |

| TP20      | n/a        | not used        |                                         |  |  |

Table 2. AFE5401-Q1 Header Configuration (continued)

### 4 Setup for Testing AFE5401-Q1 EVM

This section outlines (1) the external connections required to test the AFE5401-Q1 EVM using the CMOS interface and (2) how to set up the GUIs for testing.

Only the minimal GUI software settings required to achieve the previously mentioned tests are described. For a detailed explanation of the AFE5401-Q1 GUI software and all its features, please see Section 6. For a detailed explanation of the *High Speed Data Converter Pro* GUI software, please consult the GUI User's Guide, (SLWU087). The TSW140x EVM User's Guide (SLWU079C) is available on www.ti.com.

### 4.1 External Connections

Figure 19 shows the connections for proper hardware setup (Note: Testing the parallel CMOS interface between the AFE5401-Q1 EVM and the TSW1400 EVM can be performed using a RAMP function generated within the AFE5401-Q1 device in lieu of the signal source listed in item 7. Also, an on-board 25-MHz crystal oscillator (XTAL) can provide the ADC sampling clock in lieu of the signal source listed in item 6. This configuration is only recommended for testing the RAMP function as low phase noise filtered signal sources must be provided to both the ADC clock input and the ADC analog inputs for measuring device performance).

Figure 19. TSW1400 and AFE5401-Q1 Setup

Mate the TSW1400 EVM at connector J1 (CMOS\_INTERFACE) to the AFE5401-Q1 EVM at connector P1 (DSP) through the CMOS header connector. The connection should be right justified looking from the CMOS outputs of the AFE5401-Q1 to the TSW1400 EVM as shown in Figure 20.

Figure 20. TSW1400 Mated to AFE5401-Q1

- 2. Connect the DC +5-V output of the provided AC-to-DC power supply to **J12 (+5V\_IN)** of the TSW1400 EVM and the input of the power supply cable to a 110-230 VAC source.

- 3. Connect the DC +5 V output of the provided AC-to-DC power supply to connector **JP46** of the

### Setup for Testing AFE5401-Q1 EVM

AFE5401-Q1 EVM.

- 4. Connect the USB cable from the PC to **J45** (**USB**) of AFE5401-Q1 EVM.

- 5. Connect the USB cable from the PC to **J5** (**USB\_IF**) of the TSW1400 EVM. [NOTE: it is recommended that the PC USB port be able to support USB2.0. If unsure, always chose the USB ports at the back of the PC chassis over ones located on the front or sides.]

- Supply an ADC clock signal through a bandpass filter to sma J3 (CLK\_IN) of the AFE5401-Q1 EVM (that is, +5 dBm, 25 MHz).

[NOTE: Not required if only testing the CMOS interface with a RAMP test pattern or for non-coherent sampling as 25MHz XTAL clock provided on the EVM.]

- Supply an analog input signal through a bandpass filter to sma J48 (CH1) of the AFE5401-Q1 EVM (that is, +4 dBm, 3.5 MHz).

[NOTE: Not required if only testing the CMOS interface with a test pattern.]

### 4.2 TSW1400 and AFE5401-Q1 GUI Software Setups

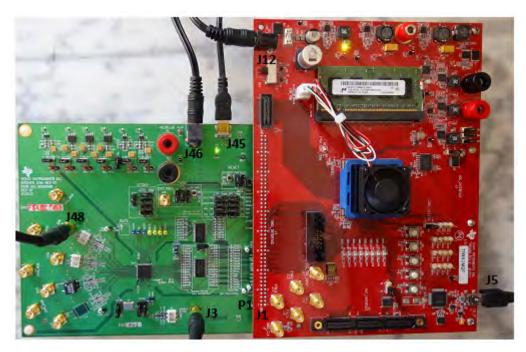

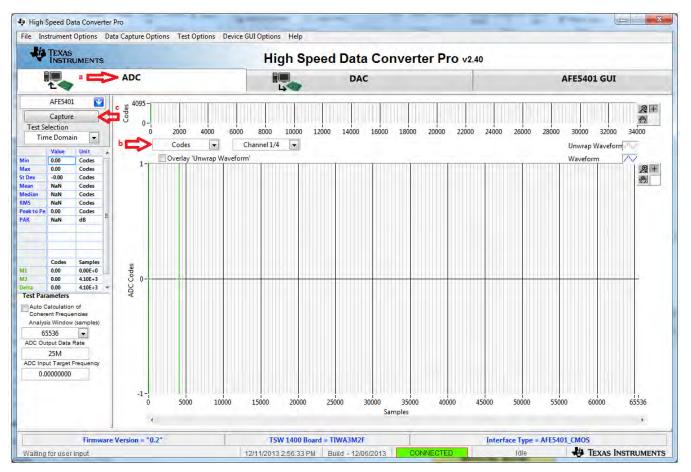

With the setup outlined in Figure 19 established, launch the *High Speed Data Converter Pro* GUI. The GUI should automatically detect the serial number of the TSW1400 EVM connected as shown in Figure 21. Click on *OK*.

Figure 21. TSW1400 GUI Setup (a)

Figure 22 shows the message that appears. Click OK.

Figure 22. TSW1400 GUI Setup (b)

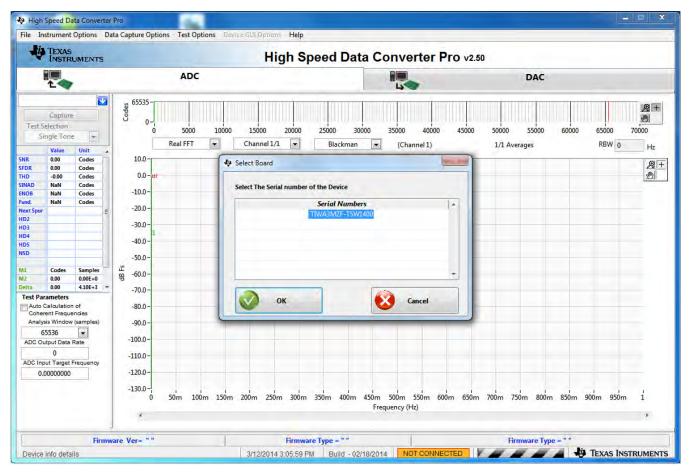

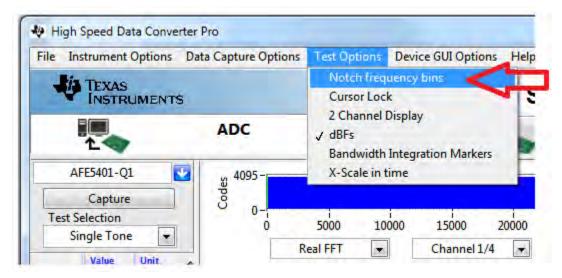

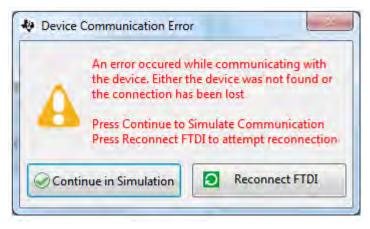

If instead, the message in Figure 23 appears, it indicates that the USB connection to the TSW1400 EVM is not present. Click *OK*, then establish a USB connection and repeat step 1.

|            | _                      |

|------------|------------------------|

| No Board   |                        |

| Connected! |                        |

| OK         |                        |

|            | No Board<br>Connected! |

Figure 23. TSW1400 GUI Setup (c)

Select a device by clicking on the blue arrow in the upper left corner of the *HSDCpro* GUI. Scroll down and select *AFE5401-Q1* as shown in Figure 24.

### Setup for Testing AFE5401-Q1 EVM

www.ti.com

Figure 24. TSW1400 GUI Setup (d)

Click the Yes button to update the ADC firmware on the TSW1400 FPGA as depicted in Figure 25.

Figure 25. TSW1400 GUI Setup (e)

While the firmware is being loaded into the TSW1400 FPGA, the menu shown in Figure 26 appears.

Figure 26. TSW1400 GUI Setup (f)

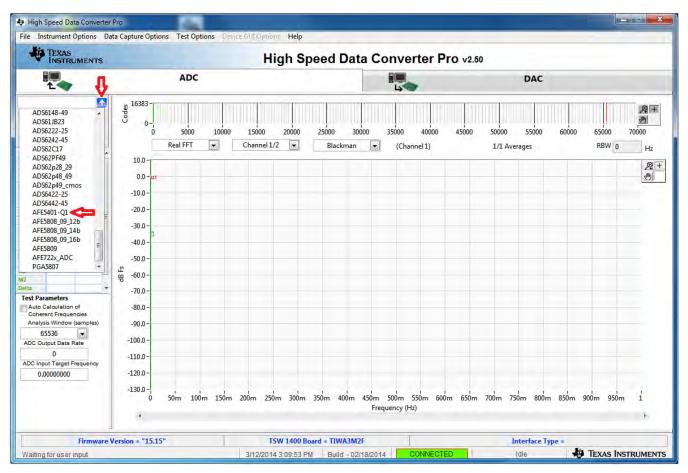

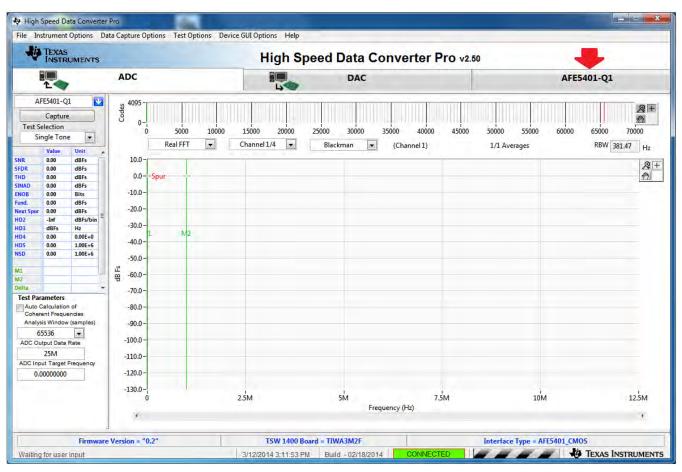

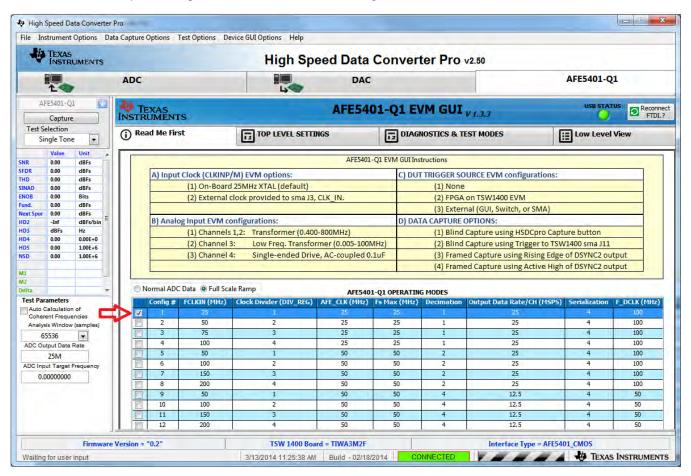

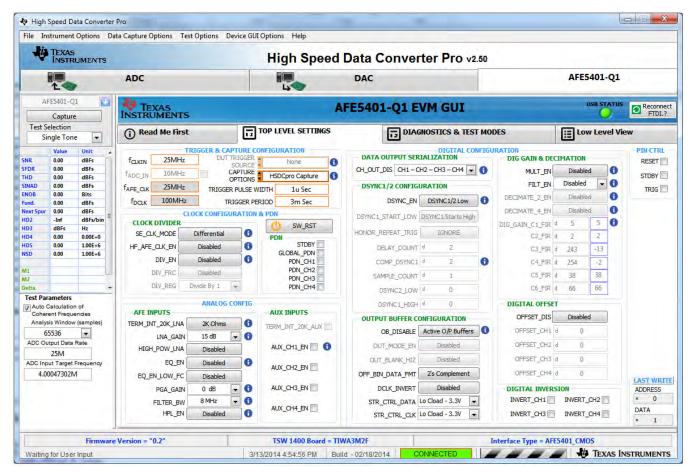

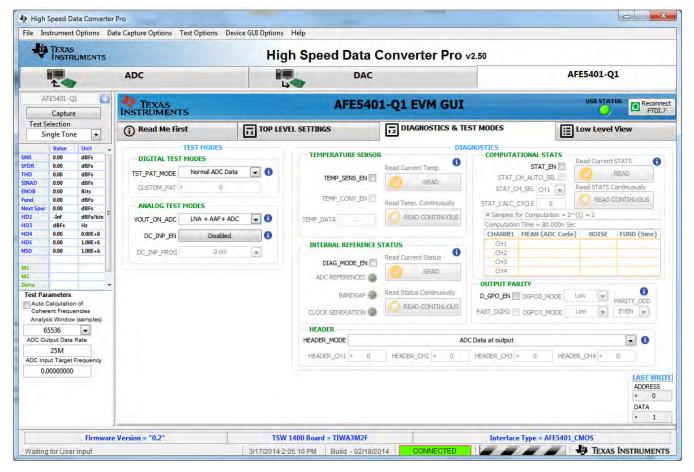

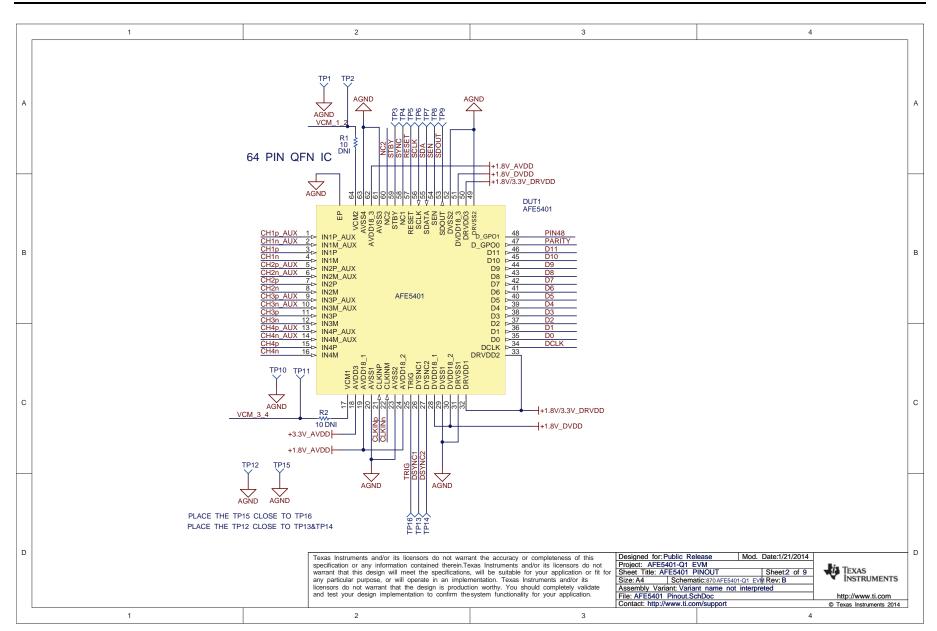

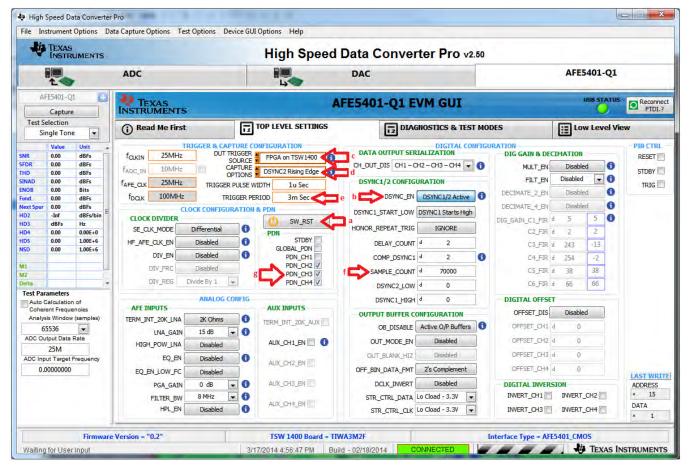

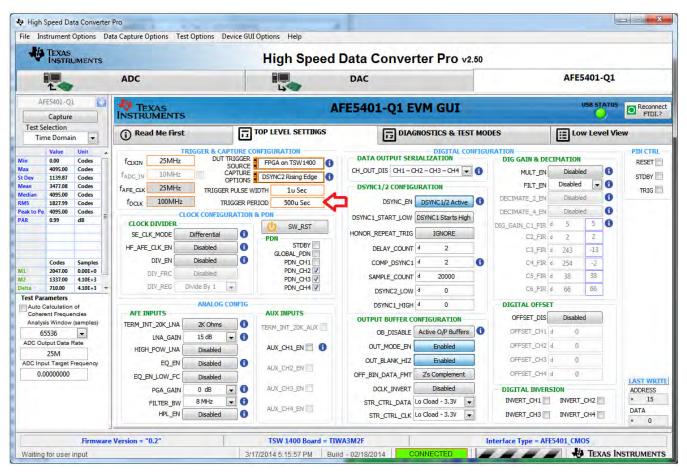

Once loaded, the plug-in AFE5401-Q1 GUI appears as a new tab within the *HSDCpro* GUI, as shown in Figure 27.

Figure 27. AFE5401-Q1 Plug-in GUI Setup (g)

#### Setup for Testing AFE5401-Q1 EVM

www.ti.com

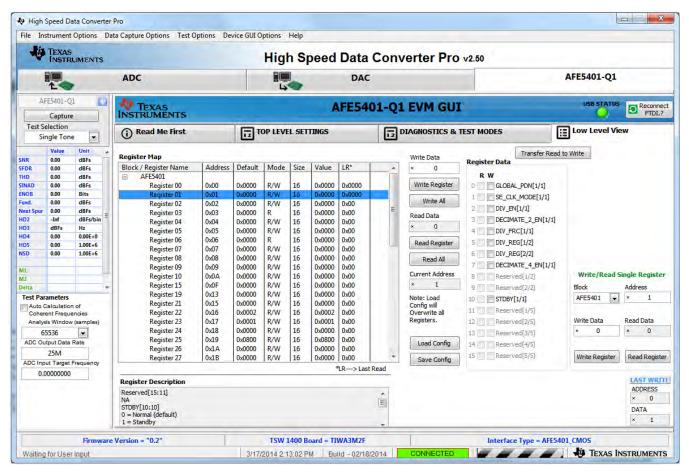

Click on the tab *AFE5401-Q1 GUII* to view the GUI software for the AFE5401-Q1. The GUI consists of four tabs: *Read Me First, TOP LEVEL SETTINGS, DIAGNOSTICS & TEST MODES,* and *Low Level View.* The *Read Me First* tab is presented initially as shown in Figure 28.

The easiest way to configure the AFE5401-Q1 EVM for testing is by using the pre-loaded configurations provided with the AFE5401-Q1 GUI software installation. The bottom of the *Read Me First* tab provides a way to load these configurations. Figure 28 shows there are 12 configurations, each with the possibility to capture *Normal ADC Data* (sampling signal at the analog inputs) or a *Full Scale Ramp* test pattern generated internal to the AFE5401-Q1.

| 🖗 High           | Speed Da                  | ata Converte     | r Pro      |                 | 6              |                          |                    |              |                |                     |                     | _ = ×            |

|------------------|---------------------------|------------------|------------|-----------------|----------------|--------------------------|--------------------|--------------|----------------|---------------------|---------------------|------------------|

| File Ins         | strument                  | Options D        | ata Captur | e Options Te    | st Options D   | evice GUI Options Help   |                    | _            |                |                     |                     |                  |

| -                | TEXAS                     | UMENTS           |            |                 |                | High Sp                  | eed Data (         | Conver       | ter Pro v2.    | 50                  |                     |                  |

|                  |                           |                  | ADC        |                 |                | 100 LOO                  | DAC                |              |                |                     | AFE5401-Q           | 1                |

| AF               | E5401-Q                   |                  |            | EXAS<br>RUMENTS |                |                          | AFE540             | 1-Q1 E       | VM GUI v1      | 3.3                 | USB STAT            | Reconnect FTDI.? |

|                  | election<br>ngle Ton      | •                | () R       | ead Me First    | -              | TOP LEVEL SETT           | INGS               | 12 DIAG      | NOSTICS & TEST | MODES               | Low Level           | View             |

| SNR              | Value<br>0.00             | Unit A           |            |                 |                | _                        | AFE5401-0          | 1 EVM GUI In | structions     | -                   |                     |                  |

| SFDR             | 0.00                      | dBFs             |            | A) Input (      | lock (CLKINE   | P/M) EVM options:        |                    | C) DU        | T TRIGGER SOUR | CE EVM configurati  | ons:                |                  |

| THD              | 0.00                      | dBFs<br>dBFs     |            |                 |                | d 25MHz XTAL (default)   |                    |              | (1) None       |                     |                     |                  |

| NOB              | 0.00                      | Bits             |            |                 | (2) External   | clock provided to sma J3 | CLK IN.            | 11           |                | TSW1400 EVM         |                     |                  |

| fund.            | 0.00                      | dBFs             |            |                 |                |                          | -                  |              |                | GUI, Switch, or SM  | A)                  |                  |

| lext Spur<br>ID2 | 0.00<br>-Inf              | dBFs<br>dBFs/bin |            | B) Analog       | Input EVM o    | onfigurations:           |                    | D) D4        | TA CAPTURE OPT |                     |                     |                  |

| 102              | dBFs                      | Hz               |            | of Analog       |                | s 1,2: Transformer (0.40 | 0.900MHz)          | Ujur         |                | ture using HSDCpr   | Canture button      |                  |

| HD4              | 0.00                      | 0.00E+0          |            | -               | (2) Channel    |                          |                    | 1-1          |                | 0 1                 | to TSW1400 sma J11  |                  |

| HD5              | 0.00                      | 1.00E+6          |            | -               |                |                          |                    |              |                |                     |                     |                  |

| NSD              | 0.00                      | 1.00E+6          |            | -               | (3) Channel    | 4: Single-ended Driv     | ve, AC-coupled 0.1 | ur-          |                |                     | Edge of DSYNC2 ou   |                  |

| 11               |                           |                  |            |                 |                |                          |                    |              | (4) Framed C   | apture using Activ  | e High of DSYNC2 ou | tput             |

| W2               |                           |                  |            |                 |                |                          | 1000               | 0.000        |                |                     |                     |                  |

| )elta            |                           | 1                |            | Normal ADC L    | Data 🔘 Full Sc | ale Ramp                 | AFE5401-           | Q1 OPERATI   | IG MODES       |                     |                     |                  |

| Test Par         |                           |                  |            | Config #        | FCLKIN (MHz)   | Clock Divider (DIV_REG)  |                    |              | Decimation Ou  | tput Data Rate/CH ( | MSPS) Serialization | F_DCLK (MHz)     |

|                  | Calculation<br>ent Freque |                  |            | 1               | 25             | 1                        | 25                 | 25           | 1              | 25                  | 4                   | 100              |

| Analys           | is Window                 | (samples)        | E          | 2               | 50             | 2                        | 25                 | 25           | 1              | 25                  | 4                   | 100              |

| 6                | 5536                      | -                |            | 3               | 75             | 3                        | 25                 | 25           | 1              | 25                  | 4                   | 100              |

| ADC Ou           | tput Data                 | Rate             |            | ] 4             | 100            | 4                        | 25                 | 25           | 1              | 25                  | 4                   | 100              |

|                  | 25M                       |                  |            | 5               | 50             | 1                        | 50                 | 50           | 2              | 25                  | 4                   | 100              |

| ADC Inp          | ut Target                 | Frequency        |            | 6               | 100            | 2                        | 50                 | 50           | 2              | 25                  | 4                   | 100              |

| 0.0              | 00000000                  |                  |            | 7               | 150            | 3                        | 50                 | 50           | 2              | 25                  | 4                   | 100              |

|                  |                           |                  |            | 8               | 200            | 4                        | 50                 | 50           | 2              | 25                  | 4                   | 100              |

|                  |                           |                  |            | 9               | 50             | 1                        | 50                 | 50           | 4              | 12.5                | 4                   | 50               |

|                  |                           |                  |            | 10              | 100            | 2                        | 50                 | 50<br>50     | 4              | 12.5                | 4                   | 50               |

|                  |                           |                  |            | 11              | 444            | 3                        | 50                 |              | 4              |                     | 4                   | 50               |

|                  |                           |                  |            | 12              | 200            | 4                        | 50                 | 50           | 4              | 12.5                | 4                   | 50               |

|                  |                           | Firmwar          | e Version  | = "0.2"         | T              | TSW 1400 Bo              | ard = TIWA3M2F     | T            |                | Interface Type =    | AFE5401_CMOS        |                  |

| Maitica          | for user                  | innut            |            |                 |                | 3/12/2014 3:17:39 PM     | Build Doldard      |              | ONNECTED       |                     | 🖌 🖌 Texas           | INSTRUMENTS      |

| statui lu        | not user                  | mput             |            | _               |                | J12/2014 3.17.39 FW      | Dullu - 02/16/2    |              |                |                     | TEAA.               | - noncoments     |

Figure 28. AFE5401-Q1 Plug-in GUI Setup (h)

### 5 Capturing a RAMP Test Pattern

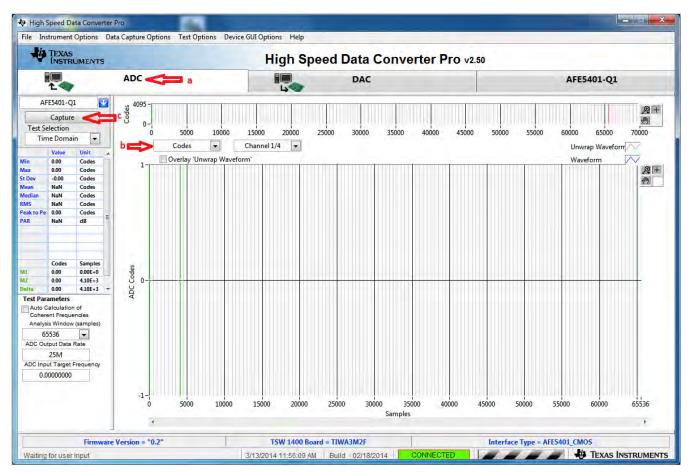

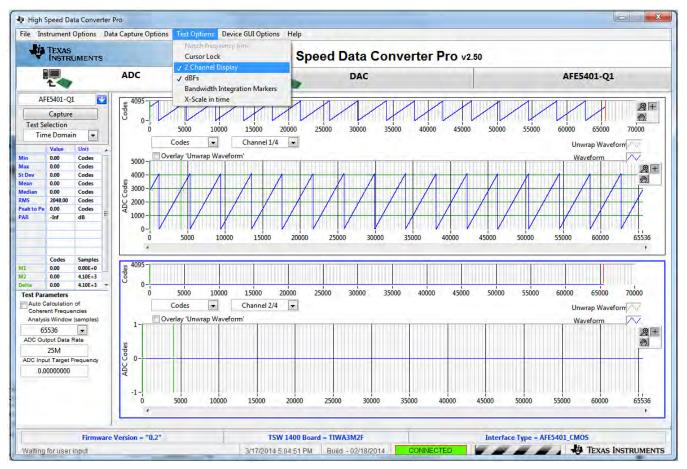

Program the AFE5401-Q1 device for a *Full Scale Ramp* test pattern by selecting the *Full Scale Ramp* radio button on the *Read Me First* tab as shown in Figure 29.

| File Ins       | strument                 | Options D        | ata Ca | pture O | ptions Te   | st Options Devi          | ce GUI Options Help    |                   |             |                   |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

|----------------|--------------------------|------------------|--------|---------|-------------|--------------------------|------------------------|-------------------|-------------|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ų              | TEXAS                    | UMENTS           |        |         |             |                          | High S                 | peed Data         | Conv        | erter Pro v2      | .50                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

|                |                          |                  | A      | DC      |             |                          | -                      | DAG               | c           |                   |                     | AFE5401-Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                 |

| AF             | E5401-Q                  |                  | IN     | TE      | XAS         | 6                        |                        | AFE54             | 01-Q1       |                   | .3.3                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | US Reconn<br>FTDI |

| -              | election<br>ngle Ton     | e 💌              | C      | ) Rea   | d Me First  |                          | TOP LEVEL SET          | TINGS             | T2 D        | IAGNOSTICS & TES  | MODES               | Low Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | View              |

| NR             | Value<br>0.00            | Unit dBFs        |        |         |             |                          |                        | AFE540            | 1-Q1 EVM GU | JI Instructions   |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |