# AN-1564 LXT971/972A to DP83848C/I/YB PHYTER System Rollover Document

#### ABSTRACT

This application report provides points to be considered when upgrading an existing 10/100 Mb/s Ethernet design, using Intel's LXT971 or LXT972A Ethernet Physical Layer (PHY) product, to the new Texas Instruments DP83848C/I/YB PHYTER<sup>™</sup> product.

| -      |                                                                                                                                            | ~                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|        |                                                                                                                                            |                                                           |

| Requir | red Changes                                                                                                                                | 3                                                         |

| 2.1    | Package                                                                                                                                    |                                                           |

| 2.2    | Pinout                                                                                                                                     | 3                                                         |

| 2.3    | PCB Modification                                                                                                                           | 3                                                         |

| Potent | tial Changes                                                                                                                               | 6                                                         |

| 3.1    | TX_ER                                                                                                                                      | 6                                                         |

| 3.2    | MII Interface                                                                                                                              | 6                                                         |

| 3.3    | PHY Address                                                                                                                                | 6                                                         |

| 3.4    | Physical Layer ID Register                                                                                                                 | 6                                                         |

| 3.5    | Auto-Negotiation and LED Pins                                                                                                              | 7                                                         |

| 3.6    | Fiber Support                                                                                                                              | 8                                                         |

| Inform |                                                                                                                                            |                                                           |

| 4.1    | RMII Interface                                                                                                                             | 9                                                         |

| 4.2    | SNI Mode                                                                                                                                   | 9                                                         |

| 4.3    | Auto_MDIX Setting                                                                                                                          | 9                                                         |

| 4.4    | Energy Detect                                                                                                                              |                                                           |

| 4.5    | CLK_to_MAC Output                                                                                                                          | 10                                                        |

| 4.6    | Power Down/Interrupt                                                                                                                       | 10                                                        |

| idix A | Pin Map                                                                                                                                    |                                                           |

| idix B | Register Differences                                                                                                                       | 13                                                        |

|        | Requi<br>2.1<br>2.2<br>2.3<br>Poten<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Inform<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>dix A | 2.2  Pinout    2.3  PCB Modification    Potential Changes |

#### List of Figures

| 1 | Special Connection in DP83848C/I/YB              | 4  |

|---|--------------------------------------------------|----|

| 2 | DP83848C/I/YB PMD Connections (Termination)      | 5  |

| 3 | LXT971 and LXT972A PMD Connections (Termination) | 5  |

| 4 | RMII Selection on DP83848C/I/YB                  | 9  |

| 5 | Auto-MDIX Operation                              | 10 |

#### List of Tables

| 1 | Packaging Differences                           | 3 |

|---|-------------------------------------------------|---|

| 2 | Bias Resistor Values                            | 4 |

| 3 | Termination and Biasing Differences             | 4 |

| 4 | Register Change for Vendor Model Number         | 6 |

|   | DP83848C/I/YB Pins for Auto-Negotiation and LED |   |

|   | ademark of Texas Instruments.                   |   |

All other trademarks are the property of their respective owners.

1

| 6  | DP83848C/I/YB Auto-Negotiation Modes      | . 7 |

|----|-------------------------------------------|-----|

|    | LXT971 and LXT972A Auto-Negotiation Modes |     |

| 8  | New Features of DP83848C/I/YB             |     |

| 9  | DP83848C/I/YB and LXT971/LXT972A Pin Map  | 11  |

| 10 | Register Bit Definitions                  | 13  |

#### 1 Purpose

Both the LXT971/972A and the DP83848C/I/YB feature the following:

- Support 10/100 MII interface

- Operation over the commercial temperature range, DP83848I also supports Industrial and DP83848YB supports extended temperature ranges

- Compliant with IEEE 802.3 specification

While both products have many similarities, the DP83848C/I/YB offers several features that simplify end user setup to ensure a better user experience. This application report compares differences including feature set, pin functions, package and pinout, and possible register operation differences between the LXT971/972A and the DP83848C/I/YB. The impact to a design is dependent on features used and their implementation.

# 2 Required Changes

This section documents the hardware changes required to transition to DP83848C/I/YB. The required changes for proper operation include package, pinout, bias and termination connections.

# 2.1 Package

The LXT971 is available in either 64 pin LQFP or 64 pin PBGA; the LXT972A is only available in the 64 pin PBGA. The DP83848C/I/YB is available in a 48 pin LQFP package. The differences in package between DP83848C/I/YB and LXT971/972A are shown in Table 1. For more information on the 48 pin LQFP package please visit Packaging Information.

#### Table 1. Packaging Differences

|                 | DP83848C/I/YB | LXT971ALC/E,<br>LXT972A | LXT971ABC/E |

|-----------------|---------------|-------------------------|-------------|

| Package         | 48-LQFP       | 64-LQFP                 | 64-PBGA     |

| Footprint       | 7 × 7mm       | 10 × 10mm               | 7 × 7mm     |

| Package Drawing | VBH48A        |                         |             |

# 2.2 Pinout

LXT971/972A has 64 pins while DP83848C/I/YB has only 48 pins. Please see Appendix A for the pin mapping between LXT971/972A and DP83848C/I/YB, as well as pins not applicable in the DP83848C/I/YB.

# 2.3 PCB Modification

This section describes the LXT971/972A circuit modifications required to use the DP83848C/I/YB in a similar design.

# 2.3.1 PFBOUT

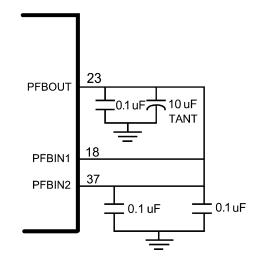

Parallel capacitors (10uF Tantalum capacitor and 0.1uF) should be placed close to pin 23 (PFBOUT, the output of the regulator) in DP83848C/I/YB. In DP83848C/I/YB, Pin 18 (PFBIN1) and 37 (PFBIN2) should be externally connected to pin 23 as shown in Figure 1. A small 0.1uF capacitor should be placed close to pin 18 and pin 37. LXT971/972A does not require a similar connection.

3

#### 2.3.2 Bias Resistor

4

Internal circuitry biasing between the devices is accomplished in a similar manner. The only difference is the value of the bias resistor and the bias connection pin number, see Table 2.

| Table | 2. | Bias | Resistor | Values |

|-------|----|------|----------|--------|

|-------|----|------|----------|--------|

|                     | DP83848C/I/YB | LXT971, LXT972A |

|---------------------|---------------|-----------------|

| Bias Resistor Value | 4.87k Ohm     | 22.1k Ohm       |

| Bias Pin            | 24            | 17 or 1H        |

# 2.3.3 Termination and PMD Biasing

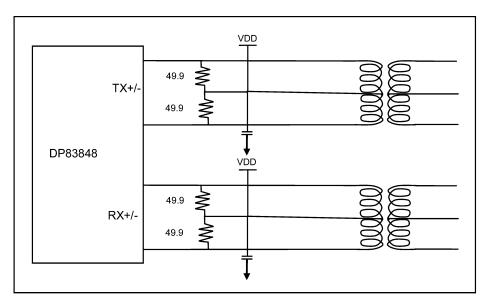

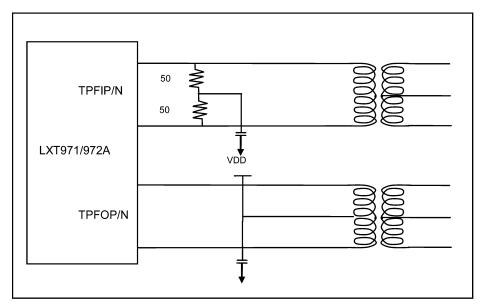

The DP83848C/I/YB requires a pair of 49.9 Ohm resistors, biased to VDD of the device. This matching of the termination resistors and common biasing between the receiver and transmitter of the DP83848C/I/YB allows the addition of the Auto-MDIX feature to the device. The LXT971/972A has the 100 Ohm termination integrated in the device. Hence, the receive pair is biased to VDD and does not require external resistors. The LXT971/972A does not support Auto-MDIX. See Table 3, Figure 2, and Figure 3.

#### **Table 3. Termination and Biasing Differences**

|                | DP83848C/I/YB | LXT971, LXT972A |

|----------------|---------------|-----------------|

| TX Termination | 49.9 Ohms     | 50 Ohms         |

| TX Bias        | 3.3V          | AC to GND       |

| RX Termination | 49.9 Ohms     | none            |

| RX Bias        | 3.3V          | 3.3V            |

Figure 2. DP83848C/I/YB PMD Connections (Termination)

Figure 3. LXT971 and LXT972A PMD Connections (Termination)

5

#### 3 Potential Changes

The following section describes the specific changes that may be need to be changed in converting to a DP83848C/I/YB based design.

# 3.1 TX\_ER

A design using the LXT971/972A may use the optional TX\_ER pin. This signal allows the system MAC to force the LXT971/972A to deliberately corrupt the transmitted packet by inserting bad symbol codes. A similar function can be accomplished by having the MAC signal the PHY to stop transmission mid-packet. By stopping mid-packet, the receiving node will interpret the packet as having a bad CRC. Upper layers can then decide to receive or reject the packet in question. Since the function of aborting a transmit packet is more easily attained with the latter method, the TX\_ER pin was not included on the DP83848C/I/YB.

#### 3.2 MII Interface

The MII interface is used to connect the PHY to the MAC in 10/100 Mb/s systems. For a 5V MII application, it is recommended to use 33 Ohm series resistor between the MAC and DP83848C/I/YB. The MII interface is a nibble-wide interface consisting of transmit data, receive data and control signals.

The transmit interface is comprised of the following signals:

- Transmit data bus, TXD[0:3] (pins 3,4,5 and 6 in DP83848C/I/YB)

- Transmit enable signal, TX\_EN (pin 2 in DP83848C/I/YB)

- Transmit clock, TX\_CLK (pin 1 in DP83848C/I/YB) which runs at 2.5MHz in 10 Mb/s mode and 25MHz in 100 Mb/s mode

The receive interface is comprised of the following signals:

- Receive data bus, RXD[0:3] (pin 43,44,45 and 46 in DP83848C/I/YB)

- Receive error signal, RX\_ER (pin 41 in DP83848C/I/YB)

- Receive data valid, RX\_DV (pin 39 in DP83848C/I/YB)

- Receive clock, RX\_CLK (pin 38 in DP83848C/I/YB) for synchronous data transfer which runs at 2.5MHz in 10 Mb/s mode and 25MHz in 100 Mb/s mode

Refer to Appendix A for an LXT971/972A to DP83848C/I/YB pin mapping.

# 3.3 PHY Address

In a given system, multiple PHYs may be controlled by a single MII management interface. In order to support this, each PHY must have a unique address. DP83848C/I/YB facilitates this with PHY address strap options.

In DP83848C/I/YB, RXD0:3 and COL are also used at power-up or reset time to set the PHY address. Pin COL has a weak internal pull-up and RXD0:3 have weak internal pull-downs in DP83848C/I/YB. Hence, the default setting for PHY address in DP83848C/I/YB is 01h. To change the PHY address, from the default, add external 2.2K Ohm pull-ups or pull-downs to the appropriate pin(s). LXT971 uses discrete ADDR [0:4] pins to set the device address. However, LXT972A has only ADDR[0] pin to set the device address is limited to 00h or 01h in the LXT972A.

# 3.4 Physical Layer ID Register

The PHYsical Layer ID (PHYID) register allows system software to determine applicability of device specific software based on the vendor model number. The vendor model number is represented by bits 9 to 4 in PHYIDR2. The vendor model number in DP83848C/I/YB is 001001b. In LXT971/972A, the vendor model number is 001110b. See Table 4.

| Register Address | Register Name | Register Description | Device        |                 |

|------------------|---------------|----------------------|---------------|-----------------|

| Register Address | Register Name |                      | DP83848C/I/YB | LXT971, LXT972A |

| 03h              | PHYIDR2       | PHY ID 2             | 5C90h         | 78EXh           |

#### Table 4. Register Change for Vendor Model Number

6 AN-1564 LXT971/972A to DP83848C/I/YB PHYTER System Rollover Document SNLA092B-December 2006-Revised April 2013 Submit Documentation Feedback

#### 3.5 Auto-Negotiation and LED Pins

The DP83848C/I/YB has 3 multifunction pins to configure the Auto-Negotiation capabilities. At power up or reset time, they strap the media mode and during normal operation they provide status LED indications. Pin 26 has multiple LED functions, Activity or Collision status, as well as enabling Auto-Negotiation. Pin 28 indicates link status and controls the advertised or forced mode (AN0) of DP83848C/I/YB. Pin 27 indicates speed status and controls the advertised and forced mode (AN1) of DP83848C/I/YB. DP83848C/I/YB does not have separate LED pins to indicate transmit and receive activity status.

In LXT971/972A, LED/CFG1 pin enables Auto-Negotiation when set. The functions of AN0 and AN1 pins are performed by the LED/CFG2 and LED/CFG3 pins. Each LED can display one of the following status based on the programming of bits 4 to 12 in the LEDCR (014h) register – Speed, Transmit, Receive, Collision, Link, Duplex, Link and Receive status combined, Link and Activity status combined, Duplex and Collision status combined.

| DP83848C/I/YB<br>Pin Number | Auto-Negotiation Function                     | LED Function                  |

|-----------------------------|-----------------------------------------------|-------------------------------|

| 26                          | Auto-Negotiation enable                       | Activity and collision status |

| 27                          | Controls the advertised and forced mode (AN1) | Speed status                  |

| 28                          | Controls the advertised and forced mode (AN0) | Link status                   |

#### Table 5. DP83848C/I/YB Pins for Auto-Negotiation and LED

| AN_EN         | AN0 | AN1        | Mode                          |

|---------------|-----|------------|-------------------------------|

| Forced Mode:  |     | +          |                               |

| 0             | 0   | 0          | 10 Base-T, Half-Duplex        |

| 0             | 0   | 1          | 10 Base-T, Full-Duplex        |

| 0             | 1   | 0          | 100 Base-TX, Half-Duplex      |

| 0             | 1   | 1          | 100 Base-TX, Full-Duplex      |

| Advertised Mo | de: | - <b>!</b> |                               |

| 1             | 0   | 0          | 10 Base-T, Half/Full-Duplex   |

| 1             | 0   | 1          | 100 Base-TX, Half/Full-Duplex |

| 1             | 1   | 0          | 10 Base-T, Half-Duplex        |

|               |     |            | 100 Base-TX, Half-Duplex      |

| 1             | 1   | 1          | 10 Base-T, Half/Full-Duplex   |

|               |     |            | 100 Base-TX, Half/Full-Duplex |

#### Table 6. DP83848C/I/YB Auto-Negotiation Modes

#### Table 7. LXT971 and LXT972A Auto-Negotiation Modes

| LED/CFG1      | LED/CFG2 | LED/CFG3 | Mode                          |

|---------------|----------|----------|-------------------------------|

| Forced Mode:  |          | L        |                               |

| 0             | 0        | 0        | 10 Base-T, Half-Duplex        |

| 0             | 0        | 1        | 10 Base-T, Full-Duplex        |

| 0             | 1        | 0        | 100 Base-TX, Half-Duplex      |

| 0             | 1        | 1        | 100 Base-TX, Full-Duplex      |

| Advertised Mo | de:      |          |                               |

| 1             | 0        | 0        | 100 Base-TX, Half-Duplex      |

| 1             | 0        | 1        | 100 Base-TX, Full-Duplex      |

| 1             | 1        | 0        | 10 Base-T, Half-Duplex        |

|               |          |          | 100 Base-TX, Half-Duplex      |

| 1             | 1        | 1        | 10 Base-T, Half/Full-Duplex   |

|               |          |          | 100 Base-TX, Half/Full-Duplex |

8

#### 3.6 Fiber Support

The LXT971 offers Fiber interface support. The LXT972A and the DP83848C/I/YB do not offer Fiber support. Please see Texas Instruments PHYTER family of products that offer Fiber support at www.ti.com. The DP83849 is one such device.

#### 4 **Informational Changes**

This section describes new features offered in the DP83848C/I/YB and the changes required to implement them. These features may or may not be offered in the LXT971/972A device. See Table 8.

#### Table 8. New Features of DP83848C/I/YB

|                      | DP83848C/I/YB                       | LXT971, LXT972A                          |  |

|----------------------|-------------------------------------|------------------------------------------|--|

| System Interfaces:   |                                     |                                          |  |

| RMII                 | Yes                                 | No                                       |  |

| SNI                  | Yes                                 | No                                       |  |

| JTAG                 | Available in DP83848I and DP83848YB | Yes                                      |  |

| Auto-MDIX            | Yes                                 | No                                       |  |

| Energy Detect        | Yes                                 | No                                       |  |

| LED Outputs          | 3                                   | 3                                        |  |

| CLK-to-MAC Output    | Yes                                 | No                                       |  |

| Power Down/Interrupt | Yes                                 | Yes                                      |  |

| Temperature Range:   |                                     |                                          |  |

| 0_to_70°C            | Yes                                 | Available in LXT971ALC/ABC,<br>LXT972ALC |  |

| -40_to_85°C          | Available in DP83848I               | Available in LXT971ALE/ABE               |  |

| -40_to_125°C         | Available in DP83848YB              | No                                       |  |

| Power Consumption:   | · · · · ·                           |                                          |  |

| Active Power (Typ)   | 264mW                               | 300mW                                    |  |

#### 4.1 RMII Interface

The RMII interface can be used to connect the MAC to the PHY, in 10/100 Mb/s systems, using a reduced number of pins. By utilizing this feature, significant PCB space savings can be realized within the system, especially a design with a large number of physical layer devices.

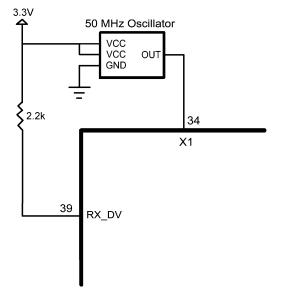

The DP83848C/I/YB uses an external 50 MHz clock (X1) as reference for both transmit and receive in the RMII mode. The 50 MHz is provided by an external oscillator. To enable RMII mode, RX DV should be pulled high using a 2.2k Ohm resistor. See Figure 4.

Figure 4. RMII Selection on DP83848C/I/YB

#### 4.2 SNI Mode

DP83848C/I/YB incorporates a 10 Mb/s Serial Network Interface (SNI) which allows a simple data interface for 10 Mb/s only system. While there is no defined standard for this interface, the interface is based on the earlier Texas Instruments 10 Mb/s physical layer devices. The following pins are used in SNI mode:

- TX CLK

- TX EN

- TXD 0

- RX\_CLK

- RXD 0

- CRS

- COL

#### 4.3 Auto\_MDIX Setting

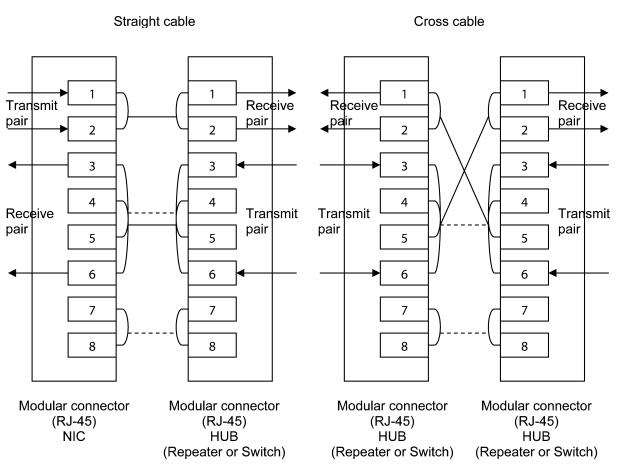

Auto-MDIX removes cabling complications and simplifies end customer applications by allowing either a straight or a cross-over cable to be used without changing the system configuration, see Figure 5. Auto-MDIX is enabled by default in the DP83848C/I/YB. To disable Auto-MDIX, pin 41 (RX\_ER) should be pulled to ground using a 2.2 K Ohm resistor. When enabled, this function utilizes Auto-Negotiation to determine the proper configuration for transmission and reception of data and subsequently selects the appropriate MDI pair for MDI/MDIX operation.

Document

Informational Changes

Figure 5. Auto-MDIX Operation

# 4.4 Energy Detect

Energy Detect facilitates flexible and automatic power management based on detection of a signal on the cable. This enables an application to use an absolute minimum amount of power over time. Energy Detect functionality is controlled via the Energy Detect Control Register (EDCR), address 1Dh. When Energy detect is enabled and there is no activity on the cable, DP83848C/I/YB will remain in a low power mode while monitoring the receive pair in the transmission line. Activity on the line will cause the DP83848C/I/YB to return to the normal power mode.

# 4.5 CLK\_to\_MAC Output

The DP83848C/I/YB offers a clock output that may be routed directly to the MAC and act as the MAC reference clock, eliminating the need, and hence space and cost, of an additional MAC clock source. In MII mode, the clock output is 25 MHz and in RMII mode, it is 50 MHz clock.

# 4.6 Power Down/Interrupt

The DP83848C/I/YB offers a separate, multifunction pin to allow the system to power down the device, or to indicate an interrupt. In Power\_Down mode, the PWR\_DOWN/INT pin (pin 7) may be asserted low to put the device in a power down state. In Interrupt mode, this pin is an open drain output and will be asserted low when an interrupt condition occurs, based on various criteria defined by the MISR and MICR registers. It is recommended to use an external pull-up resistor for proper operation of this function. LXT971/972A only has a PWRDWN pin (pin 39 in LQFP package and pin 8E in PBGA package) which puts the device in a power down mode when set high.

www.ti.com

# Appendix A Pin Map

| DP83848C/I/YB<br>Signal Name | DP83848C/I/YB<br>Pin # | LXT971ALC/E,<br>LXT972A Pin # | LXT971ABC/E<br>Pin # | Description         |

|------------------------------|------------------------|-------------------------------|----------------------|---------------------|

| MII Interface Pins:          |                        |                               |                      |                     |

| MDC                          | 31                     | 43                            | 7E                   | MGMT DATA CLOCK     |

| MDIO                         | 30                     | 42                            | 8D                   | MGMT DATA I/O       |

| MDDIS                        | n/a                    | 3                             | 3D                   | MGMT DATA DISABLE   |

| MDINT                        | n/a                    | 64                            | 1A                   | MGMT DATA INTERRUPT |

| RXD0:3/PHYAD1:4              | 43,44,45,46            | 45,46,47,48                   | 6D,8C,8B,8A          | MII RX DATA         |

| RX_CLK                       | 38                     | 52                            | 6B                   | MII RX CLOCK        |

| RX_ER/MDIX_EN                | 41                     | 53                            | 5A                   | MII RX ERROR        |

| RX_DV/MII_MODE               | 39                     | 49                            | 7A                   | MII RX DATA VALID   |

| TXD0:3                       | 3,4,5,6                | 57,58,59,60                   | 4A,4C,3B,3A          | MII TX DATA         |

| TX_CLK                       | 1                      | 55                            | 5C                   | MII TX CLOCK        |

| TX_EN                        | 2                      | 56                            | 4B                   | MII TX ENABLE       |

| <br>TX_ER                    | n/a                    | 54                            | 5B                   | MII TX ERROR        |

| COL/PHYAD0                   | 42                     | 62                            | 2B                   | MII COL DETECT      |

| CRS/LED_CFG                  | 40                     | 63                            | 2A                   | MII CARRIER SENSE   |

| PMD Interface Pins:          |                        |                               |                      |                     |

| RD-/+                        | 13,14                  | 19,20                         | 2H,3H                | RX DATA             |

| TD-/+                        | 16,17                  | 23,24                         | 4H,5H                | TX DATA             |

| Clock Interface Pins:        |                        |                               |                      |                     |

| X1                           | 34                     | 1                             | 1B                   | XTAL/OSC INPUT      |

| X2                           | 33                     | 2                             | 1C                   | XTAL OUTPUT         |

| LED Interface Pins:          | -                      |                               |                      | 4                   |

| LED_ACT/COL/AN_EN            | 26                     | 36,37,38                      | 6E,7F,8F             | COL LED STATUS      |

| LED_ACT/COL/AN_EN            | 26                     | 36,37,38                      | 6E,7F,8F             | DUPLEX LED STATUS   |

| LED_LINK/AN_0                | 28                     | 36,37,38                      | 6E,7F,8F             | LINK LED STATUS     |

| LED_SPEED/AN_1               | 27                     | 36,37,38                      | 6E,7F,8F             | SPEED LED STATUS    |

| LED_ACT/COL/AN_EN            | 26                     | 36,37,38                      | 6E,7F,8F             | ACT LED STATUS      |

| LED_RX/PHYAD4                | n/a                    | 36,37,38                      | 6E,7F,8F             | RX ACTIVITY LED     |

| LED_TX/PHYAD3                | n/a                    | 36,37,38                      | 6E,7F,8F             | TX ACTIVITY LED     |

| JTAG Interface Pins:         |                        |                               |                      |                     |

| TCK <sup>(1)</sup>           | 8                      | 30                            | 6G                   | TEST CLOCK          |

| TDO <sup>(1)</sup>           | 9                      | 28                            | 5G                   | TEST DATA OUTPUT    |

| TMS <sup>(1)</sup>           | 10                     | 29                            | 6F                   | TEST MODE SELECT    |

| TRST <sup>(1)</sup>          | 11                     | 31                            | 6H                   | TEST RESET          |

| TDI <sup>(1)</sup>           | 12                     | 27                            | 5F                   | TEST DATA INPUT     |

| Reset Function Pin:          | 1                      |                               | 1                    | 1                   |

| RESET_N                      | 29                     | 4                             | 2C                   | RESET               |

| Strap Pins:                  | +                      | ł                             | 1                    | 1                   |

| PHYAD0:4                     | 42,43,44,45,46         | 12,13,14,15,16                | 1E,2E,2F,1F,1G       | PHY ADDRESS         |

| MDIX_EN/RX_ER                | 41                     | n/a                           | n/a                  | AUTO MDIX ENABLE    |

| MII_MODE/RX_DV               | 39                     | n/a                           | n/a                  | MII MODE SELECT     |

| SNI_MODE/TXD3                | 6                      | n/a                           | n/a                  | MII MODE SELECT     |

| <br>LED_CFG/CRS              | 40                     | 36,37.38                      | 6E,7F,8F             | LED CONFIGURATION   |

#### Table 9. DP83848C/I/YB and LXT971/LXT972A Pin Map

<sup>(1)</sup> Not applicable for DP83848C.

**Reserved Pins:** RESERVED

TXSLEW0:1

SD/TP

Miscellaneous Pins:

8,9,10,11,12,20

n/a

n/a

| Table                        | e 9. DP83848C/I/Y      | B and LXT971/LX               | T972A Pin Map (o               | continued)          |

|------------------------------|------------------------|-------------------------------|--------------------------------|---------------------|

| DP83848C/I/YB<br>Signal Name | DP83848C/I/YB<br>Pin # | LXT971ALC/E,<br>LXT972A Pin # | LXT971ABC/E<br>Pin #           | Description         |

| PAUSE_EN/RX_ER               | n/a                    | 33                            | 8H                             | PAUSE ENABLE        |

| Bias Function Pin:           | •                      | +                             | •                              | -                   |

| RBIAS                        | 24                     | 17                            | 1H                             | BIAS RES CONNECTION |

| Test Mode Pins:              |                        |                               |                                |                     |

| AN_0/LED_LINK                | 28                     | 37,38                         | 7F,8F                          | TEST MODE SELECT    |

| AN_1/LED_SPEED               | 27                     | 37,38                         | 7F,8F                          | TEST MODE SELECT    |

| AN_EN/LED_ACT/COL            | 26                     | 36                            | 6E                             | TEST MODE SELECT    |

| Special Function Pins:       |                        | ·                             |                                |                     |

| 25MHz_OUT                    | 25                     | n/a                           | n/a                            | 25 MHz CLOCK OUTPUT |

| PWR_DOWN/INT                 | 7                      | 39                            | 8E                             | POWER DOWN/INT      |

| PFBIN1:2                     | 18,37                  | n/a                           | n/a                            | POWER FEEDBACK IN   |

| PFBOUT                       | 23                     | n/a                           | n/a                            | POWER FEEDBACK OUT  |

| Supply Pins:                 | ·                      |                               | ·                              |                     |

| VDD                          | 22,32,48               | 8,21,22,40,51                 | 6A,5D,5E,3G,4G                 | 3.3V                |

| GND                          | 15,19,35,36,47         | 7,11,18,25,34,35,41,<br>50,61 | 3C,6C,4D,3E,4E,3F,<br>4F,7G,8G | GROUND              |

7B,7C,7D

1D,2D

2G

RES

TX OUTPUT SLEW CTRL

SIGNAL DETECT

9,10,44

5,6

26

Texas Instruments

# Appendix B Register Differences

This appendix covers differences between the registers in DP83848C/I/YB and LXT971 applicable to software configuration of these devices.

IEEE specified registers of Texas Instruments Physical Layer devices comply with the respective IEEE standards. Only vendor specific registers have functions that may vary from device to device. If no vendor specific registers are modified for operation in the system application, the devices will have similar operation. In designs that modify any of these optional registers, the system may use the PHY\_ID register, offset 03h, to detect which device is being used and make the appropriate changes to device registers. Specific functions of these vendor defined registers, may be available in another register or possibly in a different bit within the same register location.

- DP83848C PHYTER Comm Temp Single Port 10/100Mb/s Ethernet Phy Layer Transceiver (SNOSAT2)

- DP83848I Ind Temp Single Port 10/100 Mb/s Ethernet Phy Layer Transceiver (SNLS207)

- DP83848YB Extreme Temp Single Port 10/100 Mb/s Ethernet Phy Layer Transceiver (SNLS208)

| Register     | Register | Begister Description                       | Device                        |                            |  |

|--------------|----------|--------------------------------------------|-------------------------------|----------------------------|--|

| Address Name |          | Register Description                       | DP83848C/I/YB                 | LXT971, LXT972A            |  |

| 00h          | BMCR     | Basic Mode Control                         | Bit 6 Res                     | Bit 6 Speed Selection      |  |

| 01h          | BMSR     | Basic Mode Status                          | Bits 10:8 Res                 | Bit 10 100Base-T2 Full Dup |  |

|              |          |                                            |                               | Bit 9 100Base-T2 Half Dup  |  |

|              |          |                                            |                               | Bit 8 Extended Status      |  |

| 02h          | PHYIDR1  | PHY ID 1                                   | 2000h                         | 0013h                      |  |

| 03h          | PHYIDR2  | PHY ID 2                                   | 5C90h                         | 78EXh                      |  |

| 05h          | ANLPAR   | Auto-Neg Link Partner Ability              | Bit 13 Message page           | Bit 13 RF                  |  |

|              |          |                                            | Bit 12 Acknowledge            | Bit 12 Reserved            |  |

|              |          |                                            | Bit 11 Toggle                 | Bit 11 Asymmetric Pause    |  |

|              |          |                                            | Bit 10:0 NP transmission code | Bit 10 Pause               |  |

|              |          |                                            |                               | Bit 9 100Base-T4           |  |

|              |          |                                            |                               | Bit 8 100Base-TX Full Dup  |  |

|              |          |                                            |                               | Bit 7 100Base-TX           |  |

|              |          |                                            |                               | Bit 6 10Base-T Full Dup    |  |

|              |          |                                            |                               | Bit 5 10Base-T             |  |

|              |          |                                            |                               | Bit 4:0 Selector field     |  |

| 06h          | ANER     | Auto-Neg Expansion                         | Bit 5 Res                     | Bit 5 Base Page            |  |

| 08h          | ANLPNPR  | Auto-Neg Link Partner Next<br>Page Receive | Res                           | See LXT971/972A datashee   |  |

| 10h : 1D     |          | Function differs                           | (See datasheet)               | See LXT971/972A datashee   |  |

#### Table 10. Register Bit Definitions

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated