# TMS470R1x System Module Reference Guide

Literature Number: SPNU189H November 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of that third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

| Products                                                                                     |                                                                                                                                      | Applications                                                                                                   |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Amplifiers<br>Data Converters<br>DSP<br>Interface<br>Logic<br>Power Mgmt<br>Microcontrollers | amplifier.ti.com<br>dataconverter.ti.com<br>dsp.ti.com<br>interface.ti.com<br>logic.ti.com<br>power.ti.com<br>microcontroller.ti.com | Audio<br>Automotive<br>Broadband<br>Digital Control<br>Military<br>Optical Networking<br>Security<br>Telephony |

|                                                                                              |                                                                                                                                      | Video & Imaging                                                                                                |

|                                                                                              |                                                                                                                                      | Wireless                                                                                                       |

www.ti.com/audio www.ti.com/automotive www.ti.com/broadband www.ti.com/digitalcontrol www.ti.com/military www.ti.com/opticalnetwork www.ti.com/security www.ti.com/telephony www.ti.com/video

www.ti.com/wireless

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

#### **REVISION HISTORY**

| REVISION | VISION DATE NOTES |                                                             |

|----------|-------------------|-------------------------------------------------------------|

| Н        | 11/04             | Release for mass market                                     |

| G        | 4/04              | Updates:<br>"Analog RTI" , formerly section 5.4.4 , removed |

# Contents

| 1<br>2 |         |          | e Overview                                            |    |

|--------|---------|----------|-------------------------------------------------------|----|

| -      | 2.1     |          | IS                                                    |    |

|        | 2.2     |          | ion Bus                                               |    |

|        |         | 2.2.1    | Protocol for Memory Accesses on the Expansion Bus.    |    |

|        |         | 2.2.2    | Protocol for Peripheral Accesses on the Expansion Bus |    |

| 3      | Memo    | rv       |                                                       |    |

|        | 3.1     |          | / Map                                                 |    |

|        | 3.2     |          | / Selects                                             |    |

|        |         | 3.2.1    | Configuring Memory Selects                            |    |

|        |         | 3.2.2    | Enabling the Memory Map                               |    |

|        |         | 3.2.3    | Relocating Boot Memory                                |    |

|        | 3.3     | Memory   | Protection                                            |    |

|        |         | 3.3.1    | Memory Block Protection                               |    |

|        |         | 3.3.2    | Auxiliary Memory Protection—MPU for Internal RAM      | 19 |

|        | 3.4     | Memory   | / Resets                                              | 21 |

|        |         | 3.4.1    | Illegal Address                                       | 22 |

|        |         | 3.4.2    | Illegal Access                                        | 22 |

|        |         | 3.4.3    | Illegal Map                                           |    |

|        |         | 3.4.4    | Peripheral Illegal Access                             |    |

| 4      | Interru | upts     |                                                       |    |

|        | 4.1     |          | t Handling at the CPU                                 |    |

|        | 4.2     | Interrup | t Generation at the Peripheral                        | 25 |

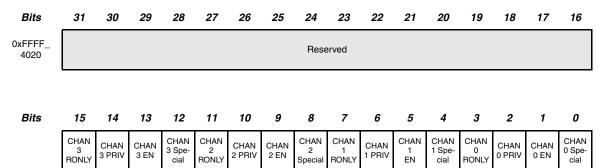

|        | 4.3     | CIM Inte | errupt Management                                     | 26 |

|        |         | 4.3.1    | CIM Input Channel Management                          | 27 |

|        |         | 4.3.2    | CIM Prioritization                                    | 27 |

|        |         | 4.3.3    | CIM Operation                                         | 27 |

|        | 4.4     | System   | Software Interrupts (SSI)                             | 29 |

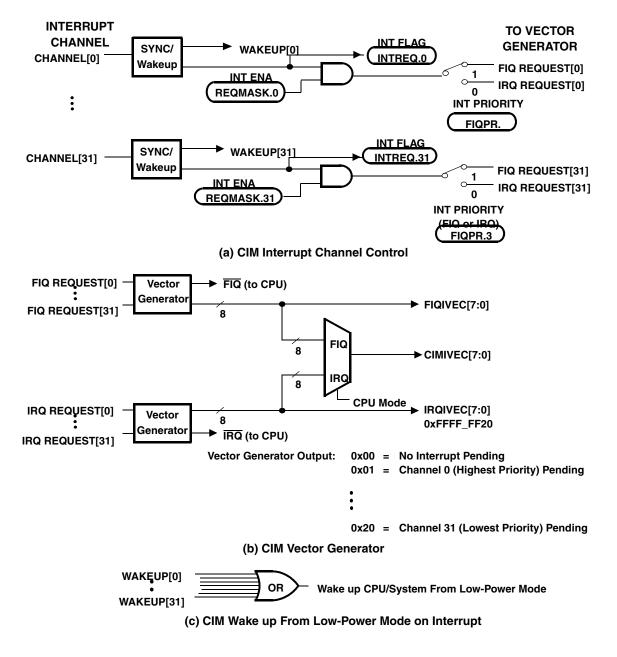

| 5      | Real-1  |          | rrupt (RTI)                                           |    |

|        | 5.1     |          | erview                                                |    |

|        | 5.2     | RTI Ope  | erating Modes and Conditions                          | 30 |

|        |         | 5.2.1    | RTI Module Clock Source.                              | 31 |

|        | 5.3     | RTI Ope  | eration                                               | 31 |

|        |         | 5.3.1    | Tap Interrupt                                         |    |

|        |         | 5.3.2    | Compare Interrupts.                                   | 34 |

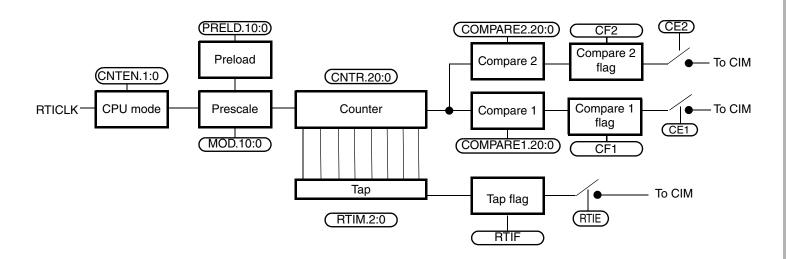

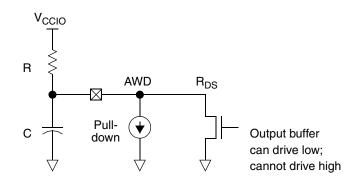

|   | 5.4     | Analog | Watchdog                                           | 35 |

|---|---------|--------|----------------------------------------------------|----|

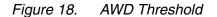

|   |         | 5.4.1  | AWD Threshold                                      |    |

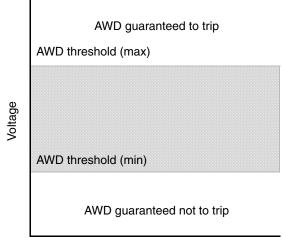

|   |         | 5.4.2  | Effect of Pull-down                                |    |

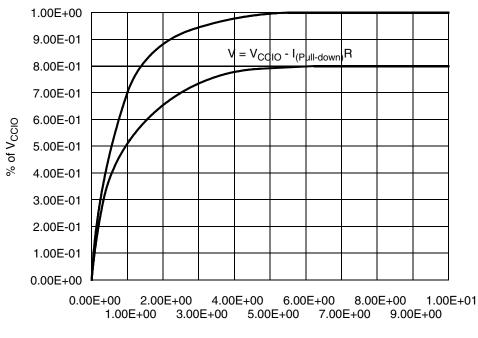

|   |         | 5.4.3  |                                                    |    |

| 6 |         |        |                                                    |    |

| 7 | Clocks  | s      |                                                    | 43 |

|   | 7.1     | Low-Po | ower Modes                                         | 44 |

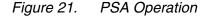

| 8 | Paralle |        | ture Analyzer Overview                             |    |

|   | 8.1     |        | pdates                                             |    |

|   | 8.2     |        | Vrite Operation                                    |    |

|   | 8.3     |        | ion Support                                        |    |

|   | 8.4     |        | /Disable                                           |    |

|   | 8.5     |        | seudo Code                                         |    |

| 9 | Regist  |        |                                                    |    |

|   | 9.1     |        | ddress Registers                                   |    |

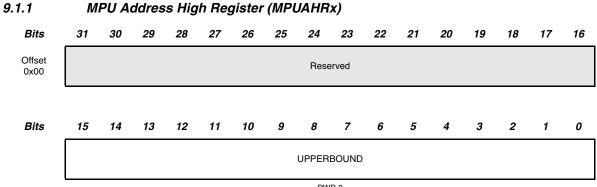

|   |         | 9.1.1  | MPU Address High Register (MPUAHRx)                |    |

|   |         | 9.1.2  | MPU Address Low Register (MPUALRx)                 |    |

|   | 9.2     |        | ontrol Register                                    |    |

|   |         | 9.2.1  | MPU Control Register (MPUCTRL)                     |    |

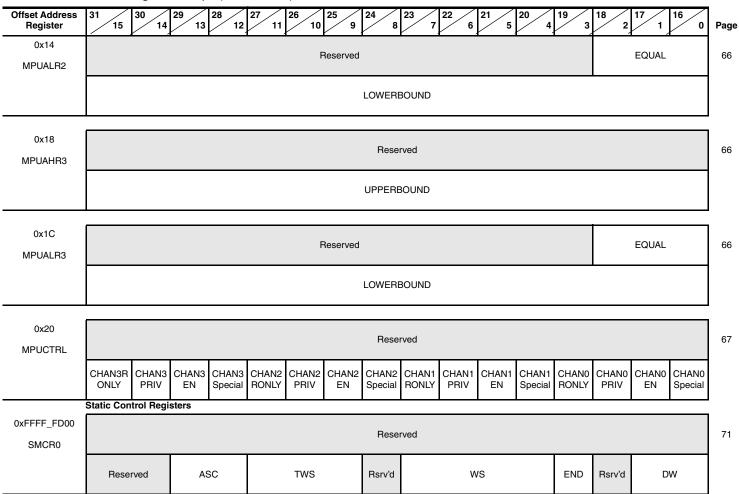

|   | 9.3     |        | Memory Control Registers                           |    |

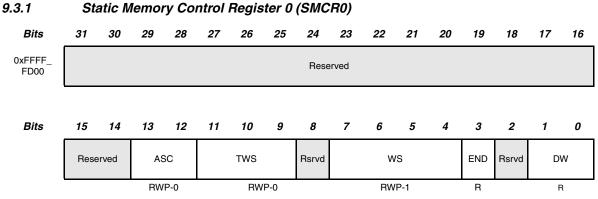

|   |         | 9.3.1  | Static Memory Control Register 0 (SMCR0)           |    |

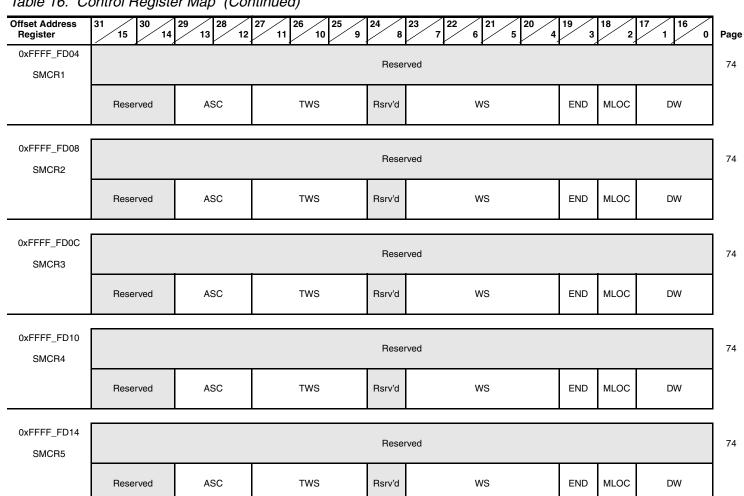

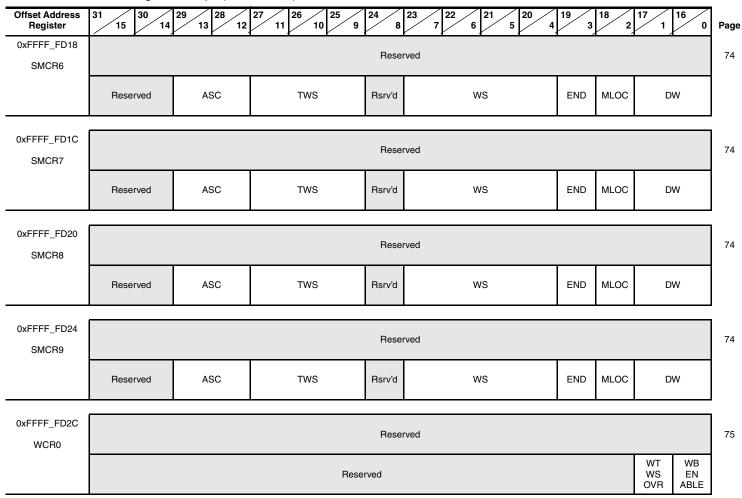

|   |         | 9.3.2  | Registers SMCR1-SMCR9                              |    |

|   |         | 9.3.3  | Static Memory Control Registers (SMCRx)            |    |

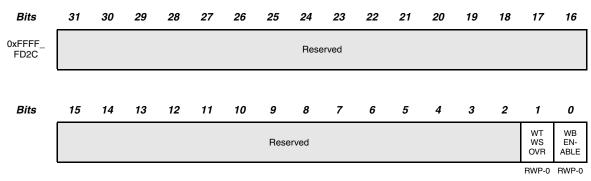

|   | 9.4     |        | Control Register (WCR0)                            |    |

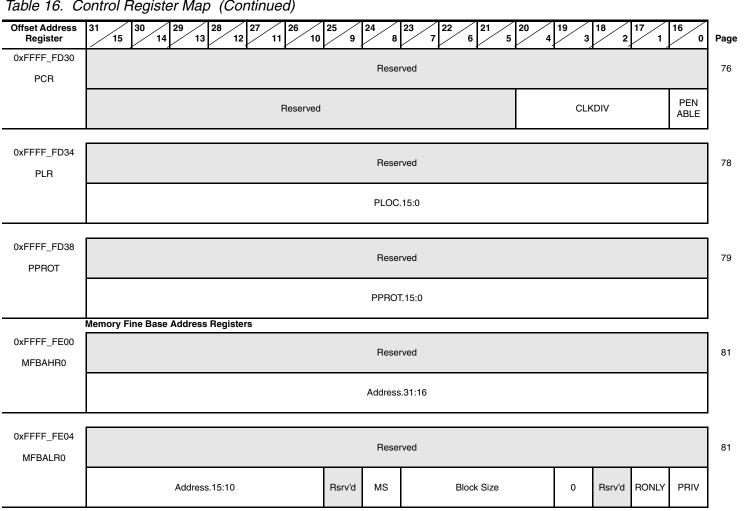

|   | 9.5     |        | eral Clock Register (PCR)                          |    |

|   | 9.6     |        | eral Location Register (PLR)                       |    |

|   | 9.7     |        | eral Protection Register (PPROT)                   |    |

|   | 9.8     |        | y Fine Base Address Registers                      |    |

|   |         | 9.8.1  | Memory Fine Base Address High Register 0 (MFBAHR0) |    |

|   |         | 9.8.2  | Memory Fine Base Address Low Register 0 (MFBALR0)  |    |

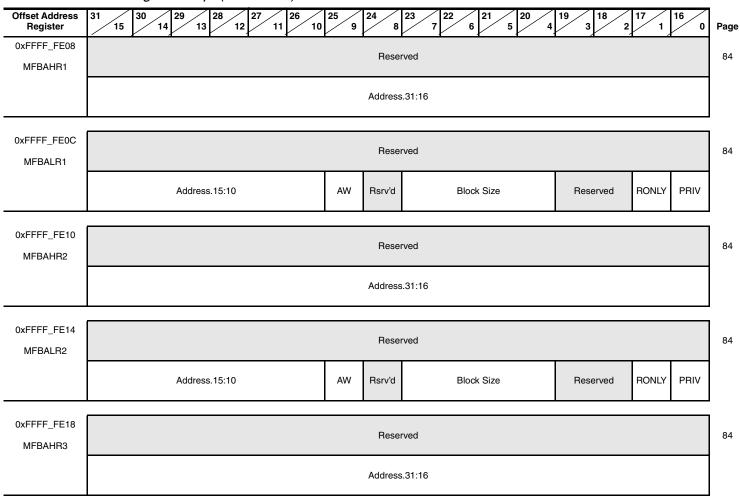

|   |         | 9.8.3  | Memory Fine Base Address High Register (MFBAHRx)   |    |

|   |         | 9.8.4  | Memory Fine Base Address Low Register (MFBALRx)    |    |

|   | 9.9     |        | y Coarse Select Control Registers                  |    |

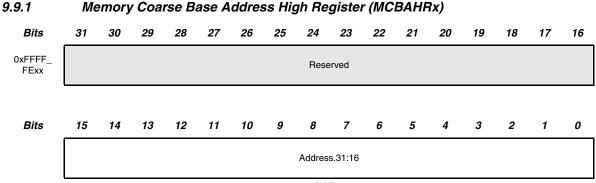

|   |         | 9.9.1  | Memory Coarse Base Address High Register (MCBAHRx) |    |

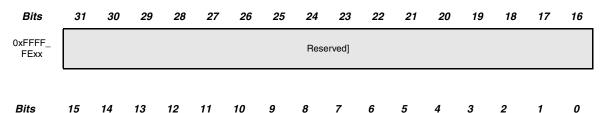

|   |         | 9.9.2  | Memory Coarse Base Address Low Register (MCBALRx)  |    |

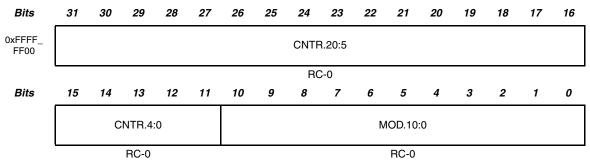

|   | 9.10    |        | unter (RTICNTR)                                    |    |

|   | 9.11    |        | eload Control Register (RTIPCTL)                   |    |

|   | 9.12    |        | ntrol Register (RTICNTL).                          |    |

|   | 9.13    |        | log Key Register (WKEY)                            |    |

|   | 9.14    |        | mpare Register 1(RTICMP1)                          |    |

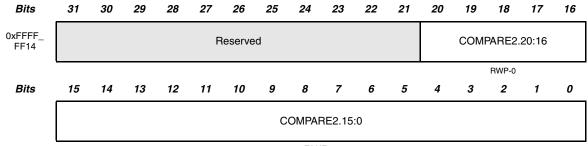

|   | 9.15    |        | mpare Register 2(RTICMP2)                          |    |

|   | 9.16    |        | re Interrupt Control Register (RTICINT)            |    |

|   | 9.17    |        | unt Enable Register (RTICNTEN)                     |    |

|   | 9.18    |        | fset Vector Registers                              |    |

|   |         | 9.18.1 | IRQ Index Offset Vector Register (IRQIVEC)         |    |

|   |         | 9.18.2 | FIQ Index Offset Vector Registers (FIQIVEC)        |    |

|      | 9.18.3 CIM Index Offset Vector Register (CIMIVEC)            | 00 |

|------|--------------------------------------------------------------|----|

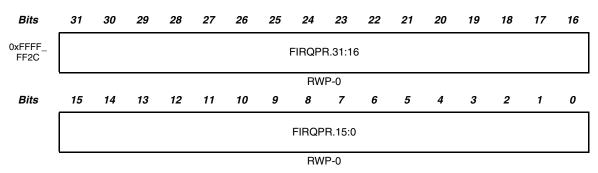

| 9.19 | FIQ/IRQ Program Control Register (FIRQPR) 1                  | 01 |

| 9.20 | Pending Interrupt Read Location (INTREQ)1                    | 01 |

| 9.21 | Interrupt Mask Register (REQMASK)1                           | 02 |

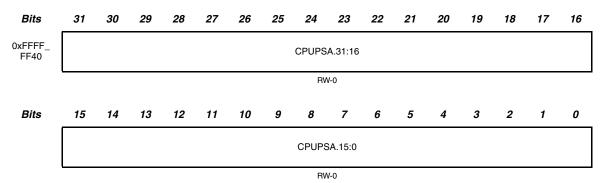

| 9.22 | CPU Data Bus Parallel Signature Analysis Register (CPUPSA) 1 | 03 |

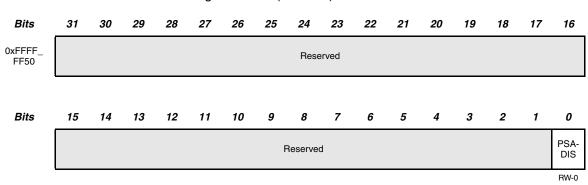

| 9.23 | PSA Enable (PSAENABLE) 1                                     | 03 |

| 9.24 | New Global Control Register (GCR_N) 1                        |    |

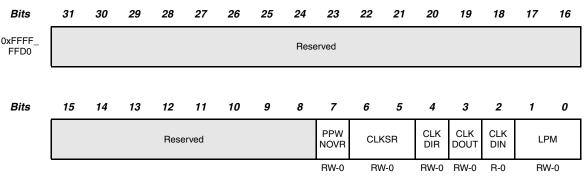

| 9.25 | Clock Control Register (CLKCNTL) 1                           | 05 |

| 9.26 | Global Control Register (GLBCTRL) 1                          | 80 |

| 9.27 | System Exception Control Register (SYSECR) 1                 | 10 |

| 9.28 | System Reset Exception Status Register (SYSESR) 1            | 12 |

| 9.29 | Abort Exception Status Register (ABRTESR) 1                  | 15 |

| 9.30 | Global Status Register (GLBSTAT) 1                           | 16 |

| 9.31 | Device Identification Register (DEV) 1                       | 19 |

| 9.32 | System Software Interrupt Flag Register (SSIF)1              | 20 |

| 9.33 | System Software Interrupt Request Register (SSIR) 1          | 21 |

vii

# Figures

| 1  | System Block Diagram                                          |

|----|---------------------------------------------------------------|

| 2  | Zero Wait-State Memory Read Transaction9                      |

| 3  | Zero Wait-State Memory Write Transaction9                     |

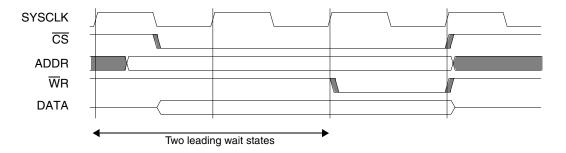

| 4  | Leading Wait-State Memory Write Transaction                   |

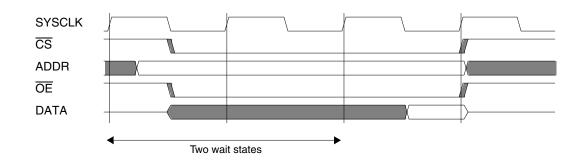

| 5  | Wait-State Memory Read Transaction10                          |

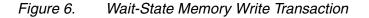

| 6  | Wait-State Memory Write Transaction11                         |

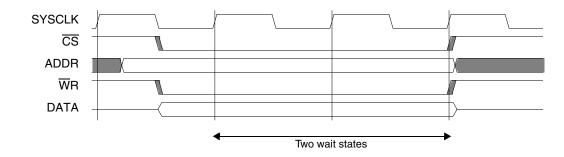

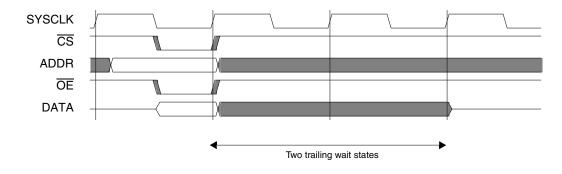

| 7  | Trailing Wait-State Memory Read Transaction11                 |

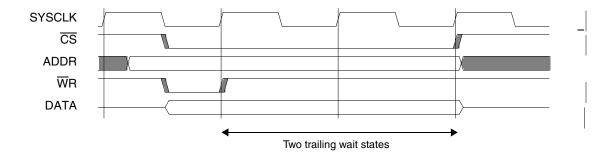

| 8  | Trailing Wait-State Memory Write Transaction12                |

| 9  | Generic Device Memory Map15                                   |

| 10 | Memory Map After Reset                                        |

| 11 | Sample Memory Map After Memory Map is Configured and Enabled  |

| 12 | Memory Mapping Scheme for Relocating Boot Memory              |

| 13 | MPU Address Decode                                            |

| 14 | Typical Operating System Use of the MPU21                     |

| 15 | Central Interrupt Manager (CIM) Block Diagram                 |

| 16 | RTI Block Diagram                                             |

| 17 | External Required Circuit for Watchdog                        |

| 18 | AWD Threshold                                                 |

| 19 | Effect of Pull-down                                           |

| 20 | Sequential AWD Charge/Discharge Cycles Reach Charge Asymptote |

| 21 | PSA Operation                                                 |

| 22 | MPU Register Alignment with Address Bus65                     |

# **Tables**

| 1  | System Module Overview                                        |

|----|---------------------------------------------------------------|

| 2  | System Module Internal Registers 2                            |

| 3  | Aligned Address Boundary by Access Type                       |

| 4  | Priority of Control Register Bits for Overlapping Channels    |

| 5  | Memory Reset/Abort Causes and Their Associated Exception Flag |

| 6  | RTI Operating Modes                                           |

| 7  | PLL State During Standby Mode                                 |

| 8  | Tap Interrupts                                                |

| 9  | Example WKEY Register Sequence                                |

| 10 | Maximum Resistance by Buffer Strength                         |

| 11 | RC Discharge Curve                                            |

| 12 | Causes of TMS470R1x Reset/Abort 41                            |

| 13 | Clock Domains                                                 |

| 14 | Active Clock Domains and Device Condition 44                  |

| 15 | System Register Accessibility                                 |

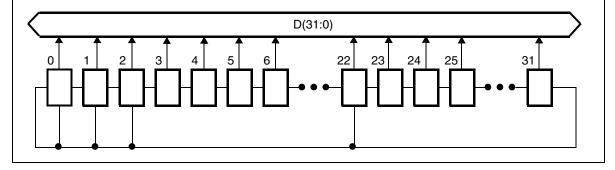

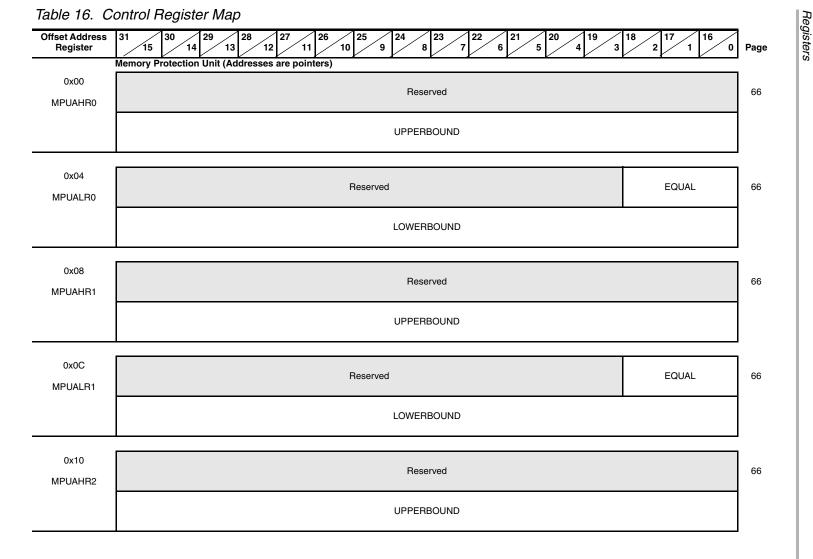

| 16 | Control Register Map                                          |

| 17 | MPU Registers                                                 |

| 18 | Static Memory Control Register Starting Addresses             |

| 19 | Wait State Definition for Memory Bank073                      |

| 20 | Data Widths for Data Memory Bank074                           |

| 21 | Peripheral Clock Division Ratios                              |

| 22 | Fine Base Control Register Addresses 80                       |

| 23 | Block Size Bit Encoding (Fine Memory Selects) 82              |

| 24 | Coarse Base Control Register Addresses 85                     |

| 25 | Block Size Bit Encoding (for Coarse Selects)                  |

| 26 | Tap Interrupts                                                |

| 27 | Example of a WKEY Sequence                                    |

| 28 | Real-Time Interrupt Counter Enable Modes                      |

| 29 | Interrupt Dispatch Table                                      |

| 30 | CLKOUT Values                                                 |

| Wake-up Interrupt Reset Modes | . 10                          | 7                             |

|-------------------------------|-------------------------------|-------------------------------|

|                               |                               |                               |

|                               | Wake-up Interrupt Reset Modes | Wake-up Interrupt Reset Modes |

# **System Module**

The system module provides an interface from the ARM CPU to the Texas Instruments (TI) TMS470R1x family of devices. The module defines the CPU bus and the expansion bus. The system module is responsible for memory interface and protection, interrupt prioritization, reset generation, and clock synthesis.

| Торі | ic                                   | Page |

|------|--------------------------------------|------|

| 1    | System Module Overview               | 2    |

| 2    | Bus Structure                        | 7    |

| 3    | Memory                               | 14   |

| 4    | Interrupts                           | 25   |

| 5    | Real-Time Interrupt (RTI)            | 30   |

| 6    | Resets                               | 41   |

| 7    | Clocks                               | 43   |

| 8    | Parallel Signature Analyzer Overview | 46   |

| 9    | Registers                            | 49   |

|      |                                      |      |

# 1 System Module Overview

This section provides an overview of the system module. Table 1 contains a brief description of the system module and lists its significant pins.

### Table 1. System Module Overview

| Description | The system module sets the protocol for bus accesses, decodes addresses, provides memory protection, manages interrupt requests, handles exceptions, and controls the clock distribution. A real-time interrupt is also located within the system module. |                                                                                                                        |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

|             |                                                                                                                                                                                                                                                           | Bidirectional reset. The internal circuitry can assert a reset and an external system reset can assert a device reset. |  |

|             | AWD                                                                                                                                                                                                                                                       | Analog watchdog reset. AWD provides a system reset if<br>the WD KEY is not written in time by the system.              |  |

|             | PORRST Input master chip power-up reset. External circuitry must assert a power-on reset.                                                                                                                                                                 |                                                                                                                        |  |

|             | CLKOUT                                                                                                                                                                                                                                                    | Clock out bidirectional pin. CLKOUT can be programmed as a GIO pin or the output of SYSCLK, ICLK, or MCLK.             |  |

Table 2 lists the system registers in the order they are discussed in this chapter and provides an overview of their functionality.

Table 2. System Module Internal Registers

| Address          | Mnemonic                | Register Name                    | Register Description                                         | Page |  |  |  |  |

|------------------|-------------------------|----------------------------------|--------------------------------------------------------------|------|--|--|--|--|

| Bus Structure Re | Bus Structure Registers |                                  |                                                              |      |  |  |  |  |

| 0xFFFF_FD00      | SMCR0                   | Static Memory Control Register 0 | Controls the wait states, memory                             | 72   |  |  |  |  |

| 0xFFFF_FD04      | SMCR1                   | Static Memory Control Register 1 | width, and endianism for accesses to given expansion memory. | 74   |  |  |  |  |

| 0xFFFF_FD08      | SMCR2                   | Static Memory Control Register 2 | Configurable on a memory by                                  | 74   |  |  |  |  |

| 0xFFFF_FD0C      | SMCR3                   | Static Memory Control Register 3 | memory basis                                                 | 74   |  |  |  |  |

| 0xFFFF_FD10      | SMCR4                   | Static Memory Control Register 4 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD14      | SMCR5                   | Static Memory Control Register 5 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD18      | SMCR6                   | Static Memory Control Register 6 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD1C      | SMCR7                   | Static Memory Control Register 7 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD20      | SMCR8                   | Static Memory Control Register 8 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD24      | SMCR9                   | Static Memory Control Register 9 |                                                              | 74   |  |  |  |  |

| 0xFFFF_FD2C      | WCR0                    | Write Control Register           | Controls global attributes of<br>expansion memory accesses   | 75   |  |  |  |  |

| Address          | Mnemonic        | Register Name                                 | <b>Register Description</b>                                                                              | Page |

|------------------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|------|

| Bus Structure Re | egisters (Conti | nued)                                         |                                                                                                          |      |

| 0xFFFF_FD34      | PLR             | Peripheral Location Register                  | Configures the peripheral as internal/external                                                           | 78   |

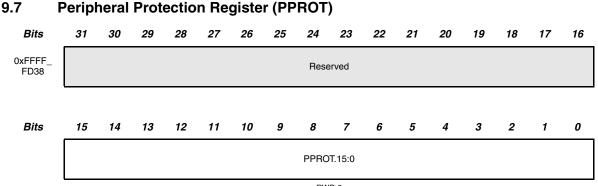

| 0xFFFF_FD38      | PPROT           | Peripheral Protection Register                | Controls whether peripherals may<br>be addressed in privilege mode<br>only or in user and privilege mode | 79   |

| Memory Register  | rs              |                                               |                                                                                                          |      |

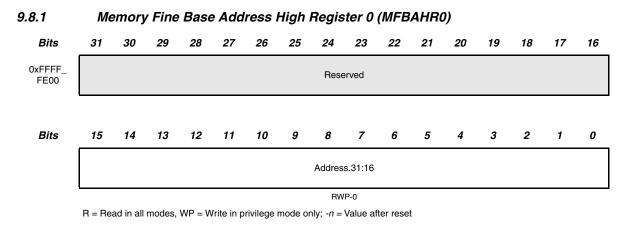

| 0xFFFF_FE00      | MFBAHR0         | Memory Fine Base Address High Register 0      | Memory Fine Base Address High<br>and Memory Fine Base Address                                            | 81   |

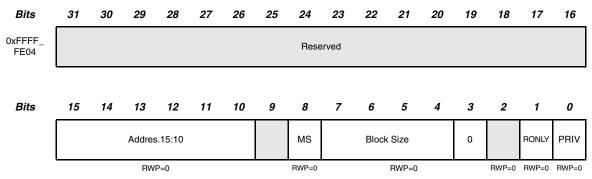

| 0xFFFF_FE04      | MFBALR0         | Memory Fine Base Address Low Register 0       | Low registers configure the<br>memory-select signals. The base<br>address, block size, and protection    | 81   |

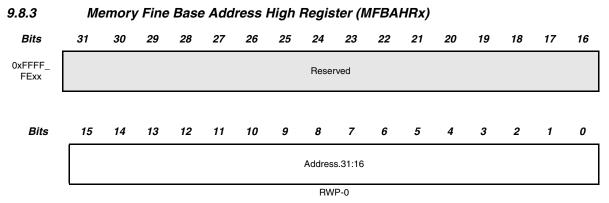

| 0xFFFF_FE08      | MFBAHR1         | Memory Fine Base Address High<br>Register 1   | for the associated memory are set<br>in these registers.                                                 | 84   |

| 0xFFFF_FE0C      | MFBALR1         | Memory Fine Base Address Low Register 1       | Memory Fine Base Address Low<br>Register 0 contains the memory-                                          | 84   |

| 0xFFFF_FE10      | MFBAHR2         | Memory Fine Base Address High<br>Register 2   | select bit that enables the memory<br>maps as configured through the<br>memory fine base address and     | 84   |

| 0xFFFF_FE14      | MFBALR2         | Memory Fine Base Address Low Register 2       | memory coarse base address registers.                                                                    | 84   |

| 0xFFFF_FE18      | MFBAHR3         | Memory Fine Base Address High<br>Register 3   |                                                                                                          | 84   |

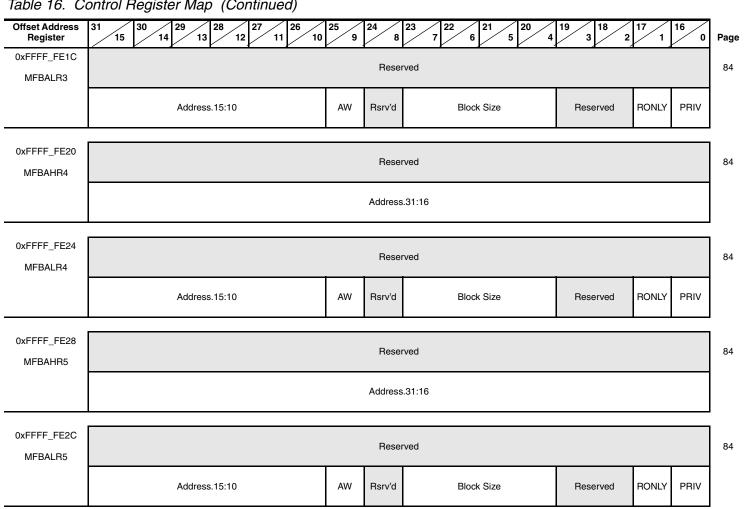

| 0xFFFF_FE1C      | MFBALR3         | Memory Fine Base Address Low Register 3       |                                                                                                          | 84   |

| 0xFFFF_FE20      | MFBAHR4         | Memory Fine Base Address High<br>Register 4   |                                                                                                          | 84   |

| 0xFFFF_FE24      | MFBALR4         | Memory Fine Base Address Low Register 4       |                                                                                                          | 84   |

| 0xFFFF_FE28      | MFBAHR5         | Memory Fine Base Address High<br>Register 5   |                                                                                                          | 84   |

| 0xFFFF_FE2C      | MFBALR5         | Memory Fine Base Address Low Register 5       |                                                                                                          | 84   |

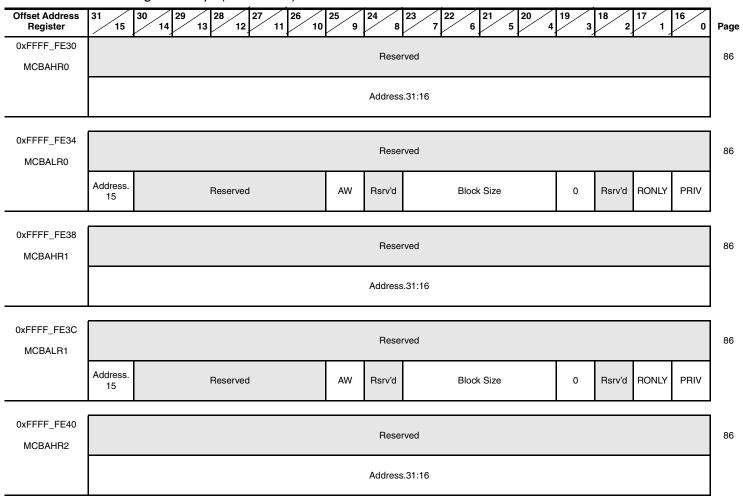

| 0xFFFF_FE30      | MCBAHR0         | Memory Coarse Base Address<br>High Register 0 |                                                                                                          | 86   |

| 0xFFFF_FE34      | MCBALR0         | Memory Coarse Base Address<br>Low Register 0  |                                                                                                          | 86   |

|                  |                 |                                               |                                                                                                          |      |

Table 2. System Module Internal Registers (Continued)

| Address         | Mnemonic       | Register                                                  | Name   | e        | Register Description                                                                                  | Page |

|-----------------|----------------|-----------------------------------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------|------|

| Memory Register | rs (Continued) |                                                           |        |          |                                                                                                       |      |

| 0xFFFF_F38      | MCBAHR1        | Memory Coarse I<br>High Register 1                        | Base   | Address  | Memory Fine Base Address High<br>and Memory Fine Base Address                                         | 86   |

| 0xFFFF_FE3C     | MCBALR1        | Memory Coarse I<br>Low Register 1                         | Base   | Address  | Low registers configure the<br>memory-select signals. The base<br>address, block size, and protection | 86   |

| 0xFFFF_FE40     | MCBAHR2        | Memory Coarse I<br>High Register 2                        | Base   | Address  | for the associated memory are set in these registers.                                                 | 86   |

| 0xFFFF_FE44     | MCBALR2        | Memory Coarse I<br>Low Register 2                         | Base   | Address  | Memory Fine Base Address Low<br>Register 0 contains the memory-                                       | 86   |

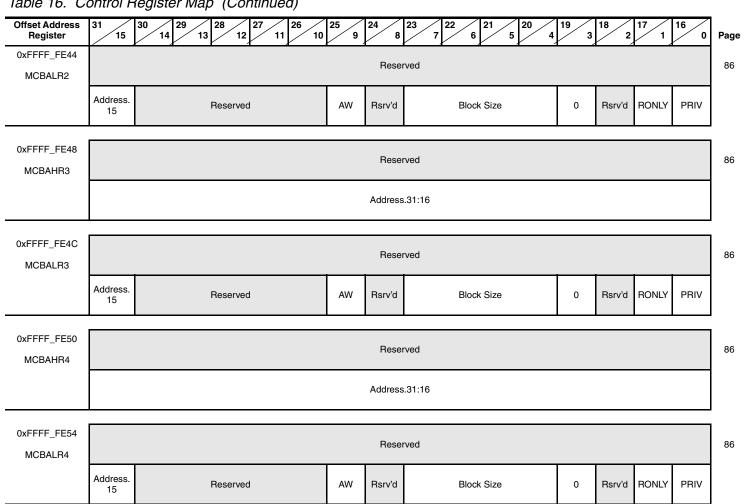

| 0xFFFF_FE48     | MCBAHR3        | Memory Coarse I<br>High Register 3                        | Base   | Address  | select bit that enables the memory<br>maps as configured through the<br>memory fine base address and  | 86   |

| 0xFFFF_FE4C     | MCBALR3        | Memory Coarse I<br>Low Register 3                         | Base   | Address  | memory coarse base address registers.                                                                 | 86   |

| 0xFFFF_FE50     | MCBAHR4        | Memory Coarse I<br>High Register 4                        | Base   | Address  |                                                                                                       | 86   |

| 0xFFFF_FE54     | MCBALR4        | Memory Coarse I<br>Low Register 4                         | Base   | Address  |                                                                                                       | 86   |

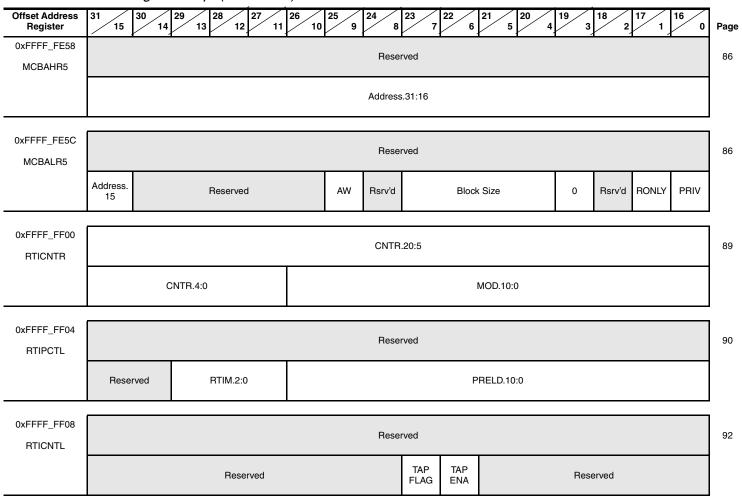

| 0xFFFF_FE58     | MCBAHR5        | Memory Coarse I<br>High Register 5                        | Base   | Address  |                                                                                                       | 86   |

| 0xFFFF_FE5C     | MCBALR5        | Memory Coarse I<br>Low Register 5                         | Base   | Address  |                                                                                                       | 86   |

| Memory Protecti | on Unit (MPU)  | Address Registers (                                       | Offset | Address) |                                                                                                       |      |

| 0x00            | MPUAHR0        | MPU Address High                                          | Regis  | ter 0    |                                                                                                       | 66   |

| 0x04            | MPUALR0        | MPU Address Low F                                         | Regist | er 0     |                                                                                                       | 66   |

| 0x08            | MPUAHR1        | MPU Address High                                          | Regis  | ter 1    | MPU Address High and MPU                                                                              | 66   |

| 0x0C            | MPUALR1        | MPU Address Low F                                         | Regist | er 1     | Address Low Registers configure<br>the address range to be protected                                  | 66   |

| 0x10            | MPUAHR2        | MPU Address High Register 2<br>MPU Address Low Register 2 |        |          | by the MPU. The MPU channel is                                                                        | 66   |

| 0x14            | MPUALR2        |                                                           |        |          | enabled (and the channel's protection set) within the MPU                                             | 66   |

| 0x18            | MPUAHR3        | MPU Address High Register 3                               |        |          | control register                                                                                      | 66   |

| 0x1C            | MPUALR3        | MPU Address Low Register 3                                |        |          |                                                                                                       | 66   |

| 0x20            | MPUCTRL        | MPU Control Regist                                        | er     |          | Controls the channel's protection and enable                                                          | 67   |

# Table 2. System Module Internal Registers (Continued)

| Address           | Mnemonic        | Register Name                                 | Register Description                                                                                     | Page |

|-------------------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|------|

| Interrupts        |                 |                                               |                                                                                                          |      |

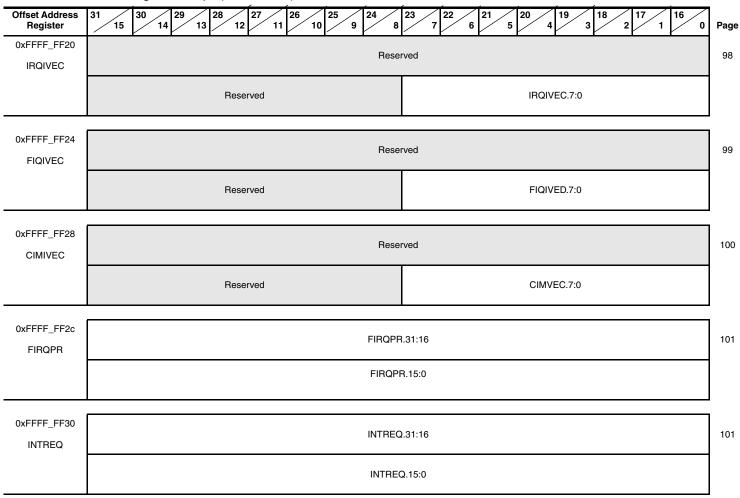

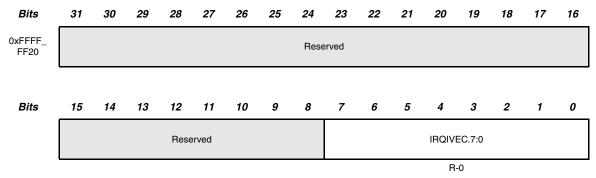

| 0xFFFF_FF20       | IRQIVEC         | IRQ Index Offset Vector Register              | Provides a numerical offset to the<br>highest priority pending interrupt<br>request (IRQ) interrupt      | 98   |

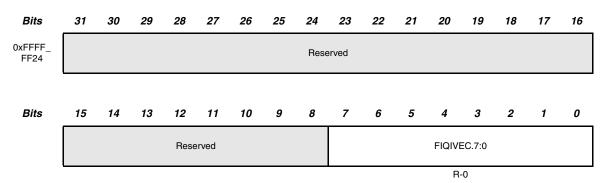

| 0xFFFF_FF24       | FIQIVEC         | FIQ Index Offset Vector Register              | Provides a numerical offset to the<br>highest priority pending fast<br>interrupt request (FIQ) interrupt | 99   |

| 0xFFFF_FF28       | CIMIVEC         | CIM Index Offset Vector Register              | Provides a numerical offset to the<br>highest priority pending interrupt                                 | 100  |

| 0xFFFF_FF2C       | FIRQPR          | FIQ/IRQ Program Control Register              | Controls whether the request<br>channel generates an IRQ or an<br>FIQ request to the CPU                 | 101  |

| 0xFFFF_FF30       | INTREQ          | Pending Interrupt Read Location Register      | Shows the pending interrupts                                                                             | 101  |

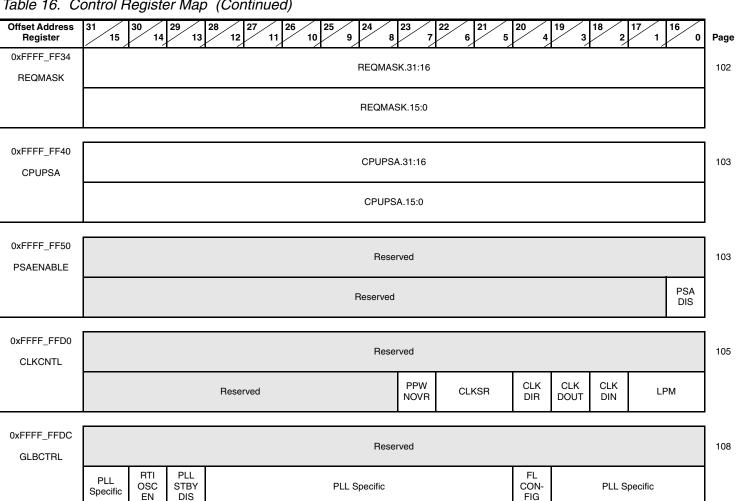

| 0xFFFF_FF34       | REQMASK         | Interrupt Mask Register                       | Enables interrupt request channels                                                                       | 102  |

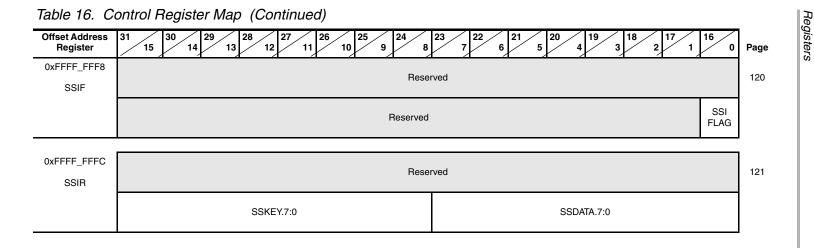

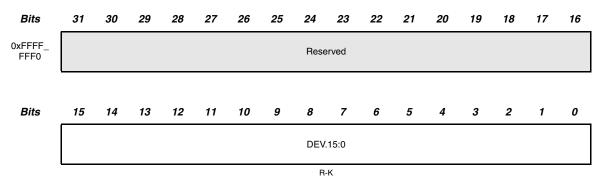

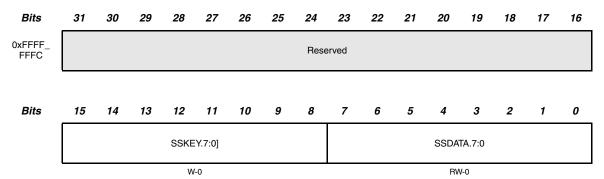

| 0xFFFF_FF8        | SSIF            | System Software Interrupt Flag<br>Register    | Flag for software interrupt                                                                              | 120  |

| 0xFFFF_FFC        | SSIR            | System Software Interrupt Request<br>Register | Generates software interrupt                                                                             | 121  |

| Real-Time Interru | ıpt (RTI) Regis | ters                                          |                                                                                                          |      |

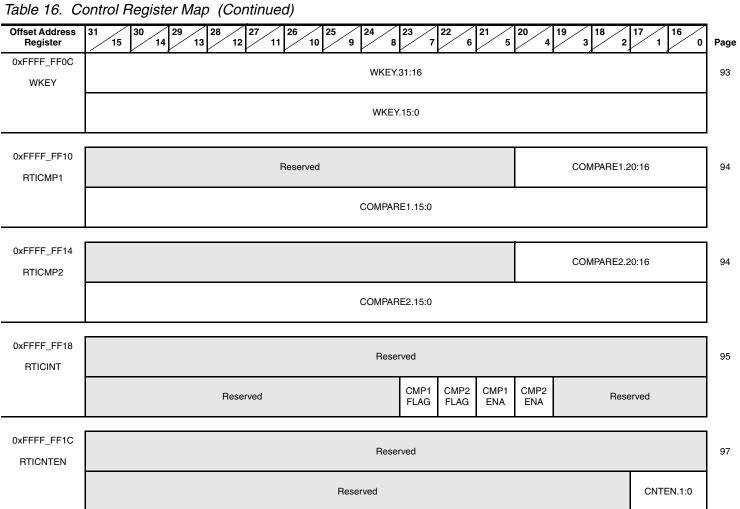

| 0xFFFF_FF00       | RTICNTR         | RTI Counter                                   | Contains MOD and CNTR<br>counters for the RTI                                                            | 89   |

| 0xFFFF_FF4        | RTI<br>PCTL     | RTI Preload Control Register                  | Controls the MOD preload value<br>and tap interrupt selection                                            | 90   |

| 0xFFFF_FF08       | RTI<br>CNTL     | RTI Control Register                          | Contains tap interrupt flag and enable                                                                   | 92   |

| 0xFFFF_FF0C       | WKEY            | Watchdog Key Register                         | Correct sequence written to this register discharges the watchdog capacitor.                             | 93   |

| 0xFFFF_FF10       | RTI<br>CMP1     | RTI Compare Register 1                        | Contains value to compare to CNTR.                                                                       | 94   |

| 0xFFFF_FF14       | RTI<br>CMP2     | RTI Compare Register 2                        | Contains value to compare to CNTR.                                                                       | 94   |

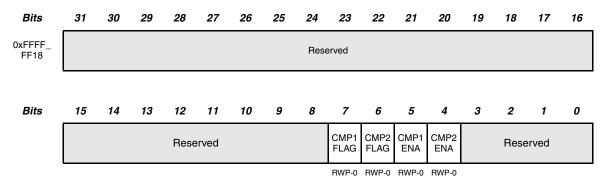

| 0xFFFF_FF18       | RTI<br>CINT     | RTI Compare Interrupt Control<br>Register     | Contains enables and flags for<br>compare 1 and compare 2<br>interrupts                                  | 95   |

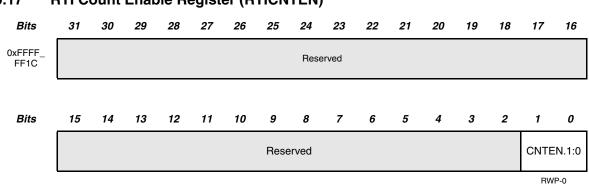

| 0xFFFF_FF1C       | RTI<br>CNTEN    | RTI Counter Enable Register                   | Enables the RTI counter based upon the CPU operating mode                                                | 97   |

Table 2. System Module Internal Registers (Continued)

| Address                                     | Mnemonic       | Register Name                             | <b>Register Description</b>                                                                                 | Page |  |  |

|---------------------------------------------|----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|--|--|

| <b>Clock Registers</b>                      |                |                                           |                                                                                                             |      |  |  |

| 0xFFFF_FD30                                 | PCR            | Peripheral Clock Register                 | Contains the ICLK divider and peripheral enable                                                             | 76   |  |  |

| 0xFFFF_FFD0                                 | CLKCNTL        | Clock Control Register                    | Controls CLKOUT pin, peripheral<br>power down, and device low power<br>modes                                | 105  |  |  |

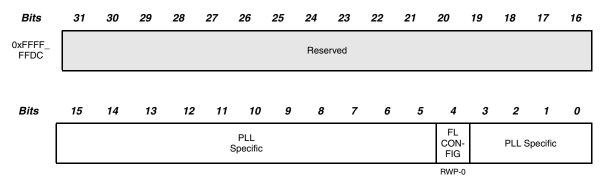

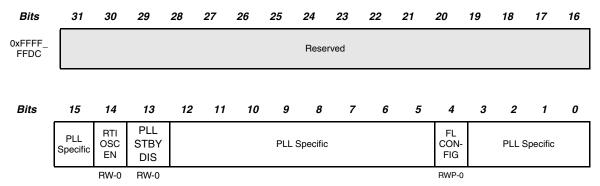

| 0xFFFF_FFDC                                 | GLBCTRL        | Global Control Register                   | Contains PLL-specific bits as well<br>as the flash memory configuration<br>bit                              | 108  |  |  |

| <b>Reset Registers</b>                      |                |                                           |                                                                                                             |      |  |  |

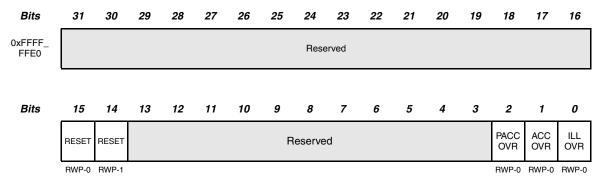

| 0xFFFF_FFE0                                 | SYSECR         | System Exception Control Register         | Contains software reset                                                                                     | 110  |  |  |

| 0xFFFF_FFE4                                 | SYSESR         | System Reset Exception Status<br>Register | Contains reset flags                                                                                        | 112  |  |  |

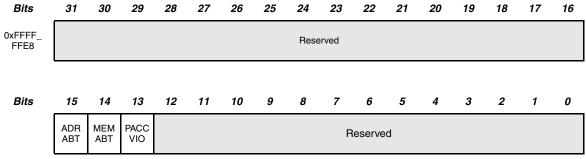

| 0xFFFF_FFE8                                 | ABRTESR        | Abort Exception Status Register           | Contains abort flags                                                                                        | 115  |  |  |

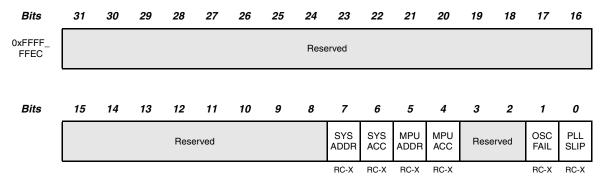

| 0xFFFF_FFEC                                 | GLBSTAT        | Global Status Register                    | Contains bits that determine the<br>source of illegal address, illegal<br>access and clock reset exceptions | 116  |  |  |

| Parallel Signature Analysis (PSA) Registers |                |                                           |                                                                                                             |      |  |  |

| 0xFFFF_FF40                                 | CPU<br>PSA     | CPU Data Bus PSA Registers                | Contains the signature value for the PSA                                                                    | 103  |  |  |

| 0xFFFF_FF50                                 | PSA<br>DISABLE | PSA Enable                                | Contains PSA enable bit                                                                                     | 103  |  |  |

| Miscellaneous Registers                     |                |                                           |                                                                                                             |      |  |  |

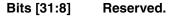

| 0xFFFF_FFF0                                 | DEV            | Device Identification Register            | Contains device-specific<br>information hard-coded during<br>device manufacture                             | 119  |  |  |

# Table 2. System Module Internal Registers (Continued)

## 2 Bus Structure

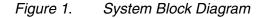

The system module defines two independent buses: a CPU bus and an expansion bus. The memory arrays (flash, ROM and RAM), CPU, DMA, and system module connect to the CPU bus. The system module, DMA, expansion peripherals, and expansion memories (for example, HET RAM) connect to the expansion bus. These buses are illustrated in Figure 1. This section (bus structure) discusses the protocol on the separate buses.

- CPU bus protocol

- Expansion bus protocol

- Protocol for memory accesses on expansion bus

- Protocol for peripheral accesses on expansion bus

## 2.1 CPU Bus

The CPU bus connects the central processor to its tightly coupled memories (that is, ROM, RAM, flash). In general, the CPU bus is a high-speed, internal bus. The system module acts as a bridge between the CPU and the expansion buses.

### 2.2 Expansion Bus

While the CPU bus protocol is fixed, the expansion bus protocol is configurable. The expansion bus supports protocol for interfacing to:

- □ Memory

- Peripherals

#### 2.2.1 Protocol for Memory Accesses on the Expansion Bus

#### Memory Select:

Memory selects allow the user to place physical memory within the address space at user-defined addresses. The memory selects are configured by the MFBAHRx, MFBALRx, MCBAHRx, and MCBALRx registers (see section 9.8). Memory accesses on the expansion bus are carried out at the SYSCLK frequency. The WCR0 register contains bits that control the global properties of the expansion bus protocol for memory; you can enable a write buffer that allows the CPU to write to the expansion bus and the CPU can perform other actions (not on the expansion bus) while the wait state is ongoing. You must configure the WCR0 register so that the expansion bus protocol is appropriate for the accessed memory.

Additionally, each memory select may be configured uniquely for the memory accessed through the expansion bus. Each SMCRx register configures the expansion bus separately for specific data widths and wait states. The mapping of SMCRx registers to different memory selects is device specific. (See the device-specific data sheet for additional details.)

#### Data Width

The expansion bus supports 8-bit, 16-bit, and 32-bit read/write operations to all memory modules. You configure the data width of the memory region with the DW bit field (SMCRx.1:0) as shown in Table 3. (The system module automatically configures the DW bit field for SMCR0 during reset.) No unaligned memory accesses are permitted.

| Read/Write Access | Aligned Address Boundary                    |

|-------------------|---------------------------------------------|

| 8-bit             | Any boundary (0x00, 0x01, 0x02, 0x03,)      |

| 16-bit            | Any even boundary (0x00, 0x02, 0x04, 0x06,) |

| 32-bit            | Any multiple of 4 (0x00, 0x04, 0x08, 0x0C)  |

## Memory Wait States

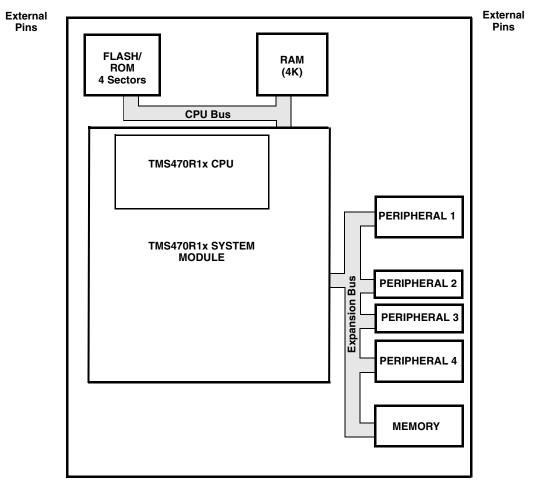

The expansion bus can support zero wait states, but it also supports wait states on the address setup, during the memory access, and on the trailing edge in order to meet the memory requirements of the expansion bus memory. These wait states are summed together. The memory access timing can be customized on a memory select by programming the ASC, WS, and TWS bits of the appropriate SMCRx register. Figure 2 and Figure 3 illustrate the timing of the zero wait state memory read and write transaction, respectively.

**Note:** The timings in Figure 2 through Figure 8 are presented for reference. The signal behavior should be verified in the device data sheet.

## Figure 2. Zero Wait-State Memory Read Transaction

Figure 3. Zero Wait-State Memory Write Transaction

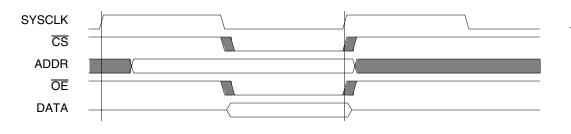

- Address setup wait states are programmed into the ASC bit field (SMCRx.13:12).

- Read:

- The ASC wait states do not affect read accesses.

- Figure 4 illustrates the leading wait-state memory write transaction.

Figure 4. Leading Wait-State Memory Write Transaction

- The memory select (CS) is active and the data is valid ASC SYSCLK cycles before the write strobe (WR) is asserted.

- The address setup wait states support flexible WR setup time requirements for write operations.

- Wait states during the memory access are programmed into the WS.3:0 bit field (SMCRx.7:4). For devices with 470+ architecture, there is a minimum of one wait state.

- Figure 5 illustrates the wait-state memory read transaction.

Figure 5. Wait-State Memory Read Transaction

■ The memory select (CS), output enable (OE), and data are valid at the same time. These signals are stretched for WS SYSCLK cycles.

■ The wait states support slow read/write accesses.

■ Figure 6 illustrates the wait-state memory write transaction.

- The memory select (CS), write strobe (WR), and data are valid at the same time. These signals are stretched for WS SYSCLK cycles.

- The wait states support slow read/write accesses.

- □ Trailing edge wait states are programmed into the TWS bit field (SMCRx.11:9). Write accesses on the expansion bus have at least one trailing wait state unless TWS is cleared to 0x00 and the WTWSOVR bit field (WCR0.1) is set to 1.

- Figure 7 illustrates the trailing wait-state memory read transaction.

Figure 7. Trailing Wait-State Memory Read Transaction

The memory select (CS), output enable (OE), and data are valid at the same time. The expansion bus is held for TWS SYSCLK cycles, but there are no wait states at the CPU unless another expansion bus access is required prior to the completion of the trailing wait states.

- The trailing wait states prevent bus drive conflicts from memories with slow output disables. A slow output disable is not a concern for byte reads to the same memory. Byte reads do not have trailing wait states between the byte reads because the same memory does not require the output disable.

- Figure 8 illustrates the trailing wait-state memory write transaction.

Figure 8. Trailing Wait-State Memory Write Transaction

- The memory select (CS), write strobe (WR), and data are valid at the same time. The memory select and data are stretched by TWS SYSCLK cycles. The write strobe goes inactive TWS SYSCLK cycles before the memory select and the data.

- The trailing wait state supports flexible hold times for write operations.

- □ The expansion bus can be used for off-chip memory accesses (if the bus is brought external). The location of the memory (on chip or external) is configured in the MLOC bit field (SMCRx.2 [in this case x cannot be 0].)

- □ The system allows for interfacing to different endian memories. The endianism of the expansion memory is programmed into the END bit field (SMCRx.3 [in this case x cannot be 0].)

- **□** Expansion bus frequency is SYSCLK frequency for memory accesses.

## 2.2.2 Protocol for Peripheral Accesses on the Expansion Bus

Peripheral accesses on the expansion bus are carried out at the ICLK frequency (see Section 7, *Clocks*, on page 43). The expansion bus protocol for peripheral access is handled by the system module.

□ The expansion bus supports 8-bit, 16-bit, and 32-bit read/write operations to all peripheral modules. (However, the peripheral itself may not support 8-bit, 16-bit, and 32-bit read/write operations.)

- The expansion bus can be used for off-chip peripheral accesses (if the bus is brought external). The location of the peripheral (on chip or external) is configured in the PLR register.

- □ The peripheral control registers may be protected on a peripheral-byperipheral basis through the peripheral protection register, PPROT. The peripheral protection register allows the user to restrict access to the peripherals based upon whether the ARM CPU is in user mode.

- □ The peripheral modules (including HET) are held in reset until the PENABLE bit (PCR.0) is set.

ICLK is generated from SYSCLK. The ICLK frequency is determined by the CLKDIV bit field (PCR.4:1); the system divides the SYSCLK frequency to generate ICLK for reduced power.

- □ ICLK is not guaranteed to be a 50% duty cycle.

- □ Peripheral accesses are measured in terms of ICLK.

- Peripheral reads take a minimum of 2 ICLK cycles.

- Peripheral writes take a minimum of 2 ICLK + 1 SYSCLK cycles.

- If ICLK is divided down from SYSCLK (that is, CLKDIV ≠ 0x00), the system asserts wait states at the beginning of the peripheral access, if required, so that the access begins on an ICLK boundary.

## 3 Memory

#### Memory Map:

The memory map shows where the memory is located within the address space. discusses:

The memory arrays have a user-defined address. The memory section

□ Protection for these memory arrays

the device

#### 3.1 Memory Map

#### Address Space:

The address space is the set of all possible unique addresses. For the 470R1x family of devices, the memory map is 4G bytes because of the 32-bit architecture.

#### Peripheral Select:

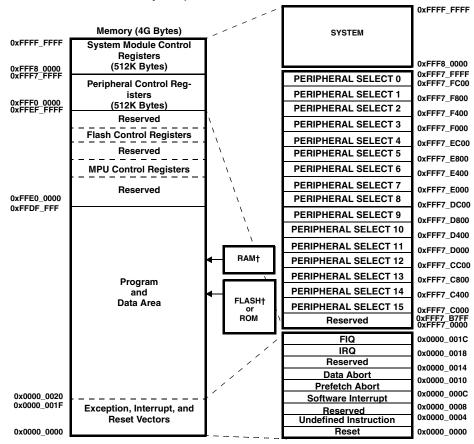

The system module decodes the top 22 bits of the address bus. If the address lies between addresses 0xFFF7\_FFF and 0xFFF7\_C000, then the system sends a peripheral-select signal plus the bottom 10 bits of the address bus to the selected peripheral. A generic device memory map is shown in Figure 9. The physical memory of the device (control registers, flash memory, ROM, and RAM) must be addressed within this memory map. The control registers are located at fixed addresses that are device specific. (See the device-specific data sheet for the mapping of peripherals to the peripheral selects.) 1K-byte sections of the memory map are reserved for each peripheral's control registers, and these 1-Kbyte sections of memory are accessed through a peripheral select.

The system control registers and flash control registers are located in the upper 2M bytes of the memory map. System control registers (except for the MPU) are located from  $0xFFFF_FFFF$  to  $0xFFFF_FD00$ . In addition to the control registers, the exception vectors have a fixed map from 0x1F to 0x00. These vectors are shown in Figure 9. These control registers and vector addresses are always valid. To access the peripheral control registers, the peripheral must be released from reset by setting PENABLE to 1 (PCR.0 = 1).

There are exceptions that consist of reset, undefined instruction, software interrupt, prefetch, abort, data abort, IRQ, and FIQ. Each of these exceptions has its own vector.

Figure 9. Generic Device Memory Map

<sup>†</sup> The base address for the flash and RAM is programmable.

## 3.2 Memory Selects

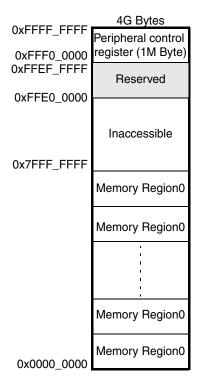

After reset, the memory map control registers for flash, system, and peripherals are all valid. Valid too are the exception vectors located from 0x1F to 0x00. Additionally, the entire flash or ROM is available. This flash or ROM is mirrored throughout the bottom 2G bytes of the memory map. (See Figure 10.)

Figure 10. Memory Map After Reset

#### 3.2.1 Configuring Memory Selects

The available memory arrays are configured within the memory map (the arrays should not be addressed within the top 2M bytes) through definition of memory selects. The memory selects are configured in the MFBAHRx, MFBALRx, MCBAHRx, and MCBALRx registers by defining:

The first 22 bits (maximum) of the starting address (origin) of the array area

The block size (length) of the array

The block size determines how many address bits must be used to address the memory array; these n bits are masked from the address bus for memory selection generation. When the remaining (top) bits on the address bus match the base address for a memory array, the associated memory select is activated. The memory array then receives the memory select plus the n remaining bits of the address.

#### Note: Base Address Must be a Multiple of the Block Size

The details concerning how the system generates memory selects can be summarized with the rule that the base address must be a multiple of the block size.

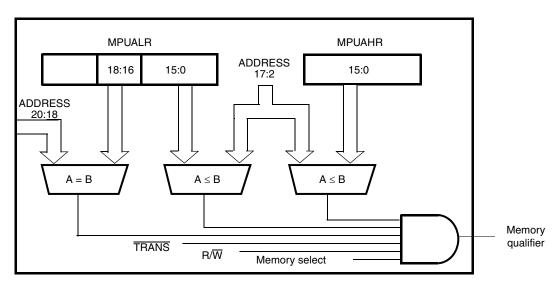

#### 3.2.2 Enabling the Memory Map

All memory selects except memory select 0 (attached to boot) are disabled at reset. The boot program should set up the memory base address control registers (configure all memory selects) and then set the memory map select bit in the memory base address register 0 (MFBALR0.8). Once the memory map select bit is set, the memory selects are generated based on the content of the memory base address registers.

The memory map is activated when the memory map select bit (MFBALR0.8) is set. Figure 11 shows an example of an enabled memory map.

Figure 11. Sample Memory Map After Memory Map is Configured and Enabled

|                            | 4G Bytes                                 |  |  |  |

|----------------------------|------------------------------------------|--|--|--|

| 0xFFFF_FFFF<br>0xFFF0_0000 | Peripheral control<br>register (1M Byte) |  |  |  |

| 0xFFEF_FFFF                | Reserved                                 |  |  |  |

| 0xFFE0_0000                |                                          |  |  |  |

|                            | Memory Region4                           |  |  |  |

|                            | Memory Region3                           |  |  |  |

|                            |                                          |  |  |  |

|                            | Memory Region0                           |  |  |  |

|                            |                                          |  |  |  |

|                            | Memory Region2                           |  |  |  |

| 0x0000_0000                | Memory Region1                           |  |  |  |

#### 3.2.3 Relocating Boot Memory

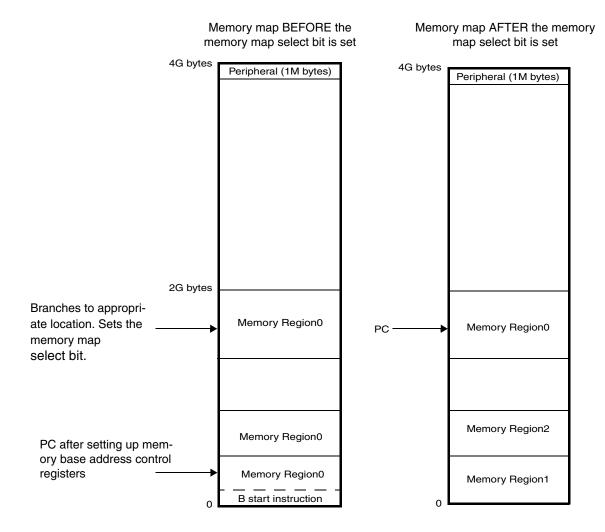

If any application needs to map the boot memory to a location other than 0x0000\_0000, the boot program should have a branch instruction that changes the program counter (PC) to the new boot program address region. (The memory attached to memory select 0 is mirrored throughout the lower 2G bytes—from 0x0000\_0000 to 0x7FFF\_FFF; at every boundary of the memory size, the memory repeats.) Changing the PC to the new boot location ensures that the PC does not get lost when the memory map is reconfigured. Figure 12 shows the memory mapping scheme with the boot memory mapped to a location other than 0x0000\_0000.

## Figure 12. Memory Mapping Scheme for Relocating Boot Memory

## 3.3 Memory Protection

Memory protection is implemented through memory selects and an auxiliary memory protection unit (MPU).

The memory-select protection provides uniform protection for the entire memory block selected, and as such, the memory protection constitutes a block protection scheme.

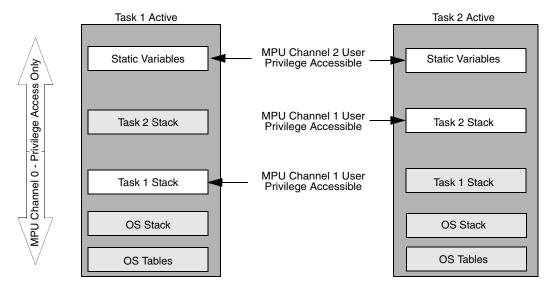

The memory protection unit allows a more refined granularity on the protection of memory blocks, and this finer protection is typically used with RAM. (See Figure 14, on page 21.) Both auxiliary and block memory protection allow the user to:

- □ Declare the memory accessible in privilege mode only (or in user and privilege mode)

- □ Configure the memory as read only (or allow both reads and writes)

#### 3.3.1 Memory Block Protection

The block memory protection relies on the memory selects, and the options for protection are configured within the MFBALRx and MCBALRx registers. An access which uses the memory select invokes the protection for the entire memory region. The privilege protection is set with the PRIV bit (MFBALRx.0 and MCBALRx.0). The read-only protection is set with the RONLY bit (MFBALRx.1 and MCBALRx.1).

#### Note: Memory-Select Protection and MPU Work Separately

On memories in which the block and auxiliary memory protection are both active, the protection schemes work separately. The block protection restricts access, whereas the auxiliary memory protection unit (MPU) allows access. Therefore, the block protection must be as minimal as the minimal MPU protection within the memories in which both MPU and memory-select protections are active.

## 3.3.2 Auxiliary Memory Protection—MPU for Internal RAM

The MPU is activated by enabling any one of the four channels. Until one MPU channel is enabled, the entire MPU is disabled and the memory is protected only by the block protection. As soon as one channel is enabled, the MPU protects the entire RAM by making the entire array inaccessible except for the area in which access is **allowed** by an MPU channel.

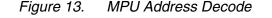

The MPU allows access to memory addresses based upon whether the addresses fall within specified address windows. The MPU address windows

are specified by defining the upper and lower address of the accessible window (see Figure 14, on page 21). The window may be as great as 256K bytes or as small as 4 bytes. (Additionally, a window may not cross a 256K-byte boundary.) The MPU allows access to a memory location under the following conditions:

- Address bus bits 20:2 correspond to the bits programmed into MPUALRx and MPUAHRx.

- □ The associated memory select is active (see Figure 13). See the device-specific data sheet for additional information on which memory selects are associated with the MPU.

- □ The access type (privilege/user mode, write/read) is allowed.

The MPU decodes the address (bits 31:21 and 1:0 of the address bus are masked off of the address) and generates illegal access or illegal address errors based upon the protection.

If the memory address is not within one of the four specified address windows, the MPU does not permit access. All memory that is not specified in an address window is inaccessible — that is, protected with the strongest possible protection.

When two or more channel ranges overlap the same memory region, the channel with the lowest protection controls the memory. Table 4 shows the priority of the control register bits when two or more channels overlap. Note the changing role of the PRIV bit in privilege (non-user) mode.

| Protection | User Mode   | Privilege Mode    |

|------------|-------------|-------------------|

| Highest    | RONLY+ PRIV | RONLY, RONLY+PRIV |

| :          | PRIV        |                   |

| :          | RONLY       |                   |

| Lowest     | None        | PRIV, None        |

Table 4. Priority of Control Register Bits for Overlapping Channels

Figure 14 shows a typical configuration in which the MPU protects the RAM and allows access to only one task's stack at a time. In the left image, task 1 is active and the operating system has allowed access to the static variables and the task 1 stack. When the operating system switches to task 2, it opens the task 2 stack and makes the tasks 1 stack inaccessible.

Figure 14. Typical Operating System Use of the MPU

## 3.4 Memory Resets

#### Reset:

On a reset condition, the program counter jumps to address 0x0000\_0000. The CPSR mode changes to reset mode, and the control registers are reset to their default values. The different memory protection schemes generate resets and aborts when the protection is violated (for additional details, see Section 6, *Resets*, on page 41). The system generates four separate reset/abort conditions that relate to memory protection (see Table 5, on page 24):

Illegal address

- Illegal access

- 🗅 Illegal map

- Peripheral illegal access

#### 3.4.1 Illegal Address

An illegal address reset/abort indicates an access to an unimplemented address in the memory map. The illegal address exception is generated by the memory selects or the MPU.

- An illegal address in user mode generates an abort.

- An illegal address in privilege mode generates a reset.

- □ The System Illegal Address exception indicates an access to an unimplemented address in the memory map. The SYS ADDR status bit in the global status register (GLBSTAT) is set to 1 to indicate that an illegal address signal has been detected from the system.

#### Peripheral Register Frame:

The 1-Kbyte regions of the memory map that may be accessed by peripheral selects are referred to as peripheral register frames. MPU Illegal Address indicates an access to a memory location not specified by one of the four MPU channels (with the MPU enabled). Both MPUADDR and MPUACC status bits of the global status register (GLBSTAT) are set to 1 to indicate that illegal address and illegal access signals have been detected from the MPU.

#### Note: Addresses Within the Peripheral Register Frame

Addresses within the peripheral register frame that are not used by the peripheral are not detected as illegal addresses because the peripheral select is valid.

#### 3.4.2 Illegal Access

An illegal access reset/abort indicates an access to a protected memory region. The two types of illegal access protection are read-only protection and access-only protection in privilege mode.

- □ An illegal access in user mode generates an abort.

- □ An illegal access in privilege mode generates a reset.

□ Memory-select illegal access:

All protection violations (such as writing to the read-only memory, a data fetch from memory in user mode while memory is programmed for privilege mode) are detected. When a protection violation is detected, the system manager asserts an illegal access signal, which prevents write operations for the illegal accesses.

MPU illegal access:

While one of the memory-select inputs to the MPU is active, the MPU generates an illegal access signal to the system if the application program attempts to write to a subregion which is programmed read-only or attempts to access, in user mode, a subregion which is accessible only in privilege mode. Hence, the MPUACC status bit of the system module global status register (GLBSTAT) is set to 1 to indicate that an illegal access has been detected from the MPU.

#### Note: Privilege Access in Control Registers

Control register bits have access protection. Illegal accesses to the control registers do not generate an exception. Illegal accesses to control register bits are ignored.

#### 3.4.3 Illegal Map

If the memory map is programmed so that two memory regions overlap, or if a memory array is programmed to access the top 1M byte (reserved for peripheral frame), a system reset occurs. The reset occurs when the overlapping memory regions is accessed by software.

Illegal map does not detect a memory overlap of control registers in the second megabyte (0xFFF0\_0000 to 0xFFE0\_0000). The top 2M bytes are reserved for TI use, so you must not map memory to this region.

#### 3.4.4 Peripheral Illegal Access

In user mode, a peripheral illegal access abort indicates an access to a protected peripheral. The peripheral protection register (PPROT) allows you to restrict access to peripherals in user mode. The system does not generate

a peripheral select when a peripheral illegal access is detected. A peripheral illegal access generates an abort in user mode (see Table 5).

Table 5. Memory Reset/Abort Causes and Their Associated Exception Flag

|                      | Abort Cause                      |                              |                          |                             |                                 | Reset Cause               |                              |                          |                             |

|----------------------|----------------------------------|------------------------------|--------------------------|-----------------------------|---------------------------------|---------------------------|------------------------------|--------------------------|-----------------------------|

| Exception<br>Flags   | Illegal Address                  |                              |                          | Illegal Access              |                                 | Illegal Address           |                              | Illegal Access           |                             |

|                      | MPU<br>Illegal<br>Address        | System<br>Illegal<br>Address | MPU<br>Illegal<br>Access | System<br>Illegal<br>Access | Peripheral<br>Illegal<br>Access | MPU<br>Illegal<br>Address | System<br>Illegal<br>Address | MPU<br>Illegal<br>Access | System<br>Illegal<br>Access |

| System Exception     | Status Reg                       | ister (SYSI                  | ESR)                     |                             |                                 |                           |                              |                          |                             |

| ILL ADDR             |                                  |                              |                          |                             |                                 | 1                         | 1                            |                          |                             |

| ILL ACC              |                                  |                              |                          |                             |                                 | 1                         |                              | 1                        | 1                           |

| PILL ACC             |                                  |                              |                          |                             |                                 |                           |                              |                          |                             |

| Abort Exception Sta  | tus Registe                      | r (ABRTESF                   | R)                       |                             |                                 | -                         |                              |                          |                             |

| ADDR ABT             | 1                                | 1                            |                          |                             |                                 |                           |                              |                          |                             |

| MEM ABT              | 1                                |                              | 1                        | 1                           |                                 |                           |                              |                          |                             |

| PACC VIO             |                                  |                              |                          |                             | 1                               |                           |                              |                          |                             |

| Global Status Regist | Global Status Register (GLBSTAT) |                              |                          |                             |                                 |                           |                              |                          |                             |

| SYS ADDR             |                                  | 1                            |                          |                             |                                 |                           | 1                            |                          |                             |

| SYS ACC              |                                  |                              |                          | 1                           |                                 |                           |                              |                          | 1                           |

| MPU ADDR             | 1                                |                              |                          |                             |                                 | 1                         |                              |                          |                             |

| MPU ACC              | 1                                |                              | 1                        |                             |                                 | 1                         |                              | 1                        |                             |

### 4 Interrupts

The TMS470R1x interrupt architecture includes a central interrupt controller that provides hardware assistance for prioritizing and controlling the many interrupt sources present on a device. Interrupts are caused by events outside the normal flow of program execution. Normally these events require a timely response from the central processing unit (CPU); therefore, when an interrupt occurs, the CPU switches execution from the normal program flow to an interrupt service routine. The interrupt service routine is a small program designed to handle the event occurrence in a timely manner.

#### 4.1 Interrupt Handling at the CPU

#### FIQ/IRQ:

Interrupt exception vectors in the CPU. FIQs are higher priority than IRQ, and FIQ interrupts may interrupt IRQ interrupts. The ARM7<sup>™</sup> CPU provides two vectors for interrupt requests—fast interrupt requests (FIQ) and normal interrupt requests (IRQ). The CPU may enable these interrupt request channels individually within the CPSR; CPSR bits 6 and 7 must be cleared to enable the FIQ and IRQ interrupt requests at the CPU. When both interrupt requests are enabled, the FIQ interrupt request has higher priority than the IRQ and is handled first.

When the CPU recognizes an interrupt request, the CPSR changes mode to either the FIQ or IRQ mode. When an IRQ interrupt is recognized, the CPU disables other IRQ interrupts by setting CPSR bit 7. When an FIQ interrupt is recognized, the CPU disables both IRQ and FIQ interrupts by setting CPSR bits 6 and 7. After the interrupt is recognized by the CPU, the program counter jumps to the appropriate interrupt vector—0x0018 for IRQ and 0x001C for FIQ.

#### 4.2 Interrupt Generation at the Peripheral

Interrupts begin when an event occurs within a peripheral module. Some examples of interrupt-capable events are expiration of a counter within a timer module, receipt of a character in a communications module, and completion of a conversion in an analog-to-digital converter (ADC) module. Some TMS470R1x peripherals are capable of requesting interrupts on more than one central interrupt manager (CIM) channel.

Interrupts are not always generated when an event occurs; the peripheral must make an interrupt request to the central interrupt manager (CIM) based upon the event occurrence. Typically, the peripheral contains:

- □ An interrupt flag bit for each event to signify the event occurrence

- An interrupt-enable bit to control whether the event occurrence causes an interrupt request to the CIM

### 4.3 CIM Interrupt Management

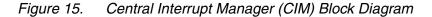

A block diagram of the CIM is shown in Figure 15.

The CIM can support 32 interrupt request lines (channel [0] to channel [31]) from the peripherals. These peripheral interrupt requests are hardwired to each of the CIM 32 channels, and these connections are device specific. (See the device-specific data sheet for details on which module is tied to which interrupt request channel.) All requests pass through a synchronizer to prevent setup time violations; the CIM samples the interrupt requests from the synchronizer every system clock (SYSCLK) cycle. The CIM combines the 32 channels into two outputs – an FIQ request to the CPU and an IRQ request to the CPU. The CIM performs the following functions:

Manages the input channels

□ Prioritizes the interrupt requests to the CPU

#### 4.3.1 CIM Input Channel Management

On the input side, the CIM enables channels on a channel-by-channel basis (in the REQMASK register); unused channels may be masked to prevent spurious interrupts. Each interrupt channel can be designated to send either an FIQ or IRQ request to the CPU (in the FIQPR register).

#### Note: LPM Wake-up Interrupts are not Masked at the CIM

Note that if an interrupt is to be used to wake the device up out of any lowpower mode (LPM), the interrupts must be enabled/disabled at the individual module level. The REQMASK register has no effect on the enable/disable of an interrupt while the device is in low-power mode.

#### 4.3.2 CIM Prioritization

The CIM prioritizes the received interrupts based upon a hardware and software prioritization scheme. The software prioritization scheme is user configurable. The CIM can send two interrupt requests to the CPU simultaneously—one IRQ and one FIQ. If both interrupt types are enabled at the CPU, then the FIQ has greater priority and is handled first. The hardware prioritization scheme sends the lowest numbered active channel (in each FIQ and IRQ interrupt request) to the CPU. Within the FIQ and IRQ classes of interrupts, the lowest channel has the highest priority interrupt. The CIM sends the highest priority interrupt (that is, the lowest active channel) of both the IRQ and FIQ classes of interrupt requests to the CPU.

#### 4.3.3 CIM Operation

When the CPU recognizes an interrupt request and responds, the program counter jumps to the appropriate interrupt vector. The interrupt vector is typically a branch statement to an interrupt table. The interrupt table reads the pending interrupt from a vector offset register (FIQIVEC.7:0 for FIQ interrupts

and IRQIVEC.7:0 for IRQ interrupts). The CIM has an overall offset register (CIMIVEC.7:0) that is read as IRQ offset or FIQ offset depending upon the mode of the CPU. (All pending interrupts can be viewed in the INTREQ register.)

Example 1 has the fastest response to the FIQ interrupt and is applicable to a system which has only one channel assigned as FIQ (remainder are all IRQ). The FIQ interrupt does not have to take additional branches before reaching the service routine.

### Example 1. How to Respond to FIQ With Short Latency

| Label | Address                                                                                 | Instructions                                                                                                                                                    | Comments                                                                                                                                |

|-------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|       | 00000000h<br>00000004h<br>000000000<br>000000000<br>00000010h<br>00000014h<br>00000018h | <pre>.sect ".intvecs" b _RESET b _UNDEF_INST_INT b _SW_INT b _ABORT_PREF_INT b _ABORT_DATA_INT b #-8 b _IRQ_ENTRY_0 ;************************************</pre> | A                                                                                                                                       |

|       | 0000001Ch                                                                               | ;=====================================                                                                                                                          | ; FIQ INTERRUPT ENTRY                                                                                                                   |

|       | 0000001Ch                                                                               | ;=====================================                                                                                                                          | =======<br>;Load R8 with address of CIMIVEC<br>; R8 used as address pointer is<br>; the first FIQ banked register                       |

|       | 00000020h<br>00000024h                                                                  | ldrb R8, [R8]<br>ldr PC, [PC, R8, LSL#2]                                                                                                                        | ;Get the FIQ index                                                                                                                      |