# TMS470R1x External Clock Prescale (ECP) Reference Guide

Literature Number: SPNU202B November 2004

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different form or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Audio

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

## Products Applications

Amplifiers amplifier.ti.com

Data Converters dataconverter.ti.com

DSP dsp.ti.com

Interface interface.ti.com

Logic logic.ti.com

Power Mgmt power.ti.com

Microcontrollers microcontroller.ti.com

**Automotive** www.ti.com/automotive www.ti.com/broadband Broadband Digital Control www.ti.com/digitalcontrol www.ti.com/military Military www.ti.com/opticalnetwork **Optical Networking** Security www.ti.com/security Telephony www.ti.com/telephony www.ti.com/video Video & Imaging Wireless www.ti.com/wireless

www.ti.com/audio

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

### **REVISION HISTORY**

| REVISION | DATE  | NOTES                                        |  |

|----------|-------|----------------------------------------------|--|

| В        | 11/04 | Removed author names; released to mass marke |  |

| А        | 9/02  | Converted to a stand-alone book              |  |

| *        | 2/00  | Pre-dates revision history                   |  |

|          |       |                                              |  |

|          |       |                                              |  |

|          |       |                                              |  |

# **Contents**

| Onal Description of the ECP Module       2         Overview       2         ECP Block Diagram       2 |

|-------------------------------------------------------------------------------------------------------|

|                                                                                                       |

| EGF DIOCK DIAGRAIII                                                                                   |

| ECP Prescaler                                                                                         |

| ECP Enable                                                                                            |

| Standby and Halt Modes                                                                                |

| Suspend4                                                                                              |

| ontrol Register (ECPCTRL)                                                                             |

| S                                                                                                     |

# **Figures**

| 1 | External Clock Prescaler Block Diagram | 2  |

|---|----------------------------------------|----|

|   | EXIGNAL CLOCK Prescaler Block Diagram  | .5 |

# **Tables**

| 1 | ECP Module Overview | 2 |

|---|---------------------|---|

| 2 | Settings for ECPEN  | 4 |

# **External Clock Prescaler (ECP)**

The external clock prescaler (ECP) provides the TMS470R1x family of devices with an external output clock (ECLK). The ECP is multiplexed with a GIO pin.

## 1 Functional Description of the ECP Module

The ECP allows the device to output a continuous external clock on a general-purpose I/O pin (GIO). The external clock (ECLK) frequency is a user-programmable ratio of the interface clock (ICLK) frequency.

#### 1.1 Overview

Table 1 contains a brief description of the ECP, lists applicable pins, and describes its significant features.

Table 1. ECP Module Overview

| Description | The external clock prescaler provides the device with a free-running external clock that can be scaled from ICLK.     |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Pins        | The ECP is multiplexed through a GIO pin (typically GIOA[1]). A control register is located the GIO peripheral frame. |  |

| Features    | The ECPEN bit enables/disables the ECLK output.                                                                       |  |

|             | The ECPDIV provides programmable prescale for generating ECLK from ICLK.                                              |  |

# 1.2 ECP Block Diagram

The ECP block diagram (see Figure 1) shows the overall functionality of the ECP module. The interface clock (ICLK) input is divided by the user-selected value programmed into the ECPCTRL register. The output of the divider is then multiplexed with the selected GIODOUT register. The output of the multiplexer is controlled by the ECP enable bit (ECPEN), and is output on the external I/O pin of the device.

$$ECLK = \frac{ICLK}{(ECPDIV + 1)}$$

ECPCTRL.7:0

ECPDIV 7:0

Prescale†

/N

GIODOUT

External pin (typically GIOA[1])

† Prescale value is between 1 and 256

Figure 1. External Clock Prescaler Block Diagram

#### 1.3 ECP Prescaler

The ECP prescaler generates the ECLK signal by dividing ICLK to a lower frequency; the prescale is implemented as a digital counter, programmable via the ECPCTRL register (ECPDIV.7:0). The prescale counts ICLK edges, and when the counter reaches the desired value programmed in ECPDIV.7:0, an ECLK edge is generated.

The prescale divider may be changed while the ECP module is enabled. However, in order to assure a smooth transition between output frequencies, the new prescale value does not take effect until the current ECLK period is complete.

The prescaler can be programmed with divider values ranging from a minimum of 1 to a maximum of 256. The divider values are programmed into the ECPDIV.7:0 bits in the ECPCTRL register (ECPCTRL.7:0). When the ECPDIV.7:0 bits are 0x07, the prescaler is set to divide by 8. This is the default state after reset.

# Note: High Frequency Output May Generate EMI

High ECLK frequencies may result in electromagnetic interference (EMI).

#### 1.4 ECP Enable

The ECPEN bit (ECPCTRL.15) controls the external I/O pin function of the device, as shown in Table 2.

Table 2. Settings for ECPEN

| ECPEN | GIODIRx | External I/O Pin Function |  |

|-------|---------|---------------------------|--|

| 0     | 0       | GIO input                 |  |

| 0     | 1       | GIO output                |  |

| 1     | X       | ECLK output               |  |

You control the multiplexer output via the ECPEN bit in the ECPCTRL register (ECPCTRL.15). If the ECPEN bit is set, the multiplexer outputs ECLK on the external I/O pin of the device. If ECPEN is cleared, the multiplexer allows control of the external pin by the GIO control registers. See Chapter 4, *General-Purpose Input/Output*, of the *TMS470 Peripheral Module User Guide, Volume 1*, literature number SPNU166, for more information.

## 1.5 Standby and Halt Modes

When the device enters standby or halt mode, the ICLK input is disabled. Therefore, the ECLK output is also disabled. After waking up from low-power modes, the ECP returns to its previous state, and you do not need to reconfigure the ECPCTRL register after the ECP wakes up from standby or halt mode.

# 1.6 Suspend

When the ECP is in suspend mode, the ECP control register can still be modified. This allows you to modify the control register when a JTAG emulator/debugger tool is being used.

When the ECPCOS bit (ECPCTRL.14) is set, the ECP continues to output its ECLK if the ECPEN bit is set when the ECP is in suspend mode.

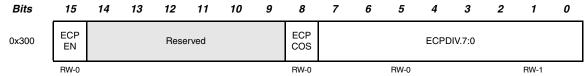

# **2** ECP Control Register (ECPCTRL)

This section describes the ECP control register. This register supports 16-bit and 32-bit write accesses.

RWP = Read in all modes, write in privilege mode only; -n = Value after reset

#### Bit 15 ECPEN. ECP enable.

Any operation mode (read/write):

0 = ECLK output is disabled. GIO registers control the device I/O pin.

1 = ECLK output is enabled. ECLK output will be seen on the device I/O pin.

#### Bits 14:9 Reserved.

Reads are undefined and writes have no effect.

#### Bit 8 ECPCOS. ECP continue on suspend.

Any operation mode (read/write):

- 0 = ECLK output is disabled in suspend mode. ECLK output will not be seen on the I/O pin of the device.

- 1 = ECLK output is enabled in suspend mode. ECLK output will be seen on the I/O pin of the device.

#### Bits 7:0 ECPDIV 7:0. ECP divider value.

Any operation mode (read/write):

The value of the ECPDIV 7:0 bits determine the external clock (ECLK) output frequency as a ratio of the interface clock (ICLK), as shown in Equation 1.

## Equation 1. External Clock Output

Where  $0xFF \ge ECPDIV \ge 0x00$

After reset, ECPDIV 7:0 = 0x07.

<sup>†</sup> The ECPCTRL register is located within the GIO peripheral frame. The physical address of the register is device specific. Please see the device-specific data sheet for the physical address of the ECPCTRL register.