# DLPC200 SPI Slave Interface Specification

#### 1 Purpose

The purpose of this document is to provide details on programming DLPC200 chipset over its SPI Slave port. The document contains list of commands along with their detailed specifications. The commands listed in this document provide similar functionality as compared to the DLPC200 API reference manual that is used in controlling DLPC200 over USB port. It must be noted that not all the interfaces available in the API reference manual are supported on SPI interface. This is because the intended use on SPI slave port is to allow real time control functionality.

#### 2 Assumptions

This document does not contain details on SPI Slave hardware interface specifications. Refer to the SPI Slave interface section of DLPC200 datasheet for the SPI slave hardware interface specification.

#### 3 Reference Links

DLPC200 DLP Digital Controller for the DLP5500 DMD (DLPS014) DLP LightCommander API (DLPA024) DLPC200 API Programmer's Guide(DLPA014)

#### 4 Overview

The SPI slave bus on DLPC200 is a standard synchronous four-wire serial data link that operates in full duplex mode. There is an additional signal available to read DLPC200 busy status.

The SPI bus specifies four logic signals plus the DLPC200 BUSY status.

- SLAVE\_SPI\_CLK Serial Clock (Output from master)

- SLAVE\_SPI\_MOSI Master Output, Slave Input (Output from master)

- SLAVE\_SPI\_MISO Master Input, Slave Output (Output from DLPC200)

- SLAVE\_SPI\_CS Slave Select (Active LOW; output from master) Additional signal

- SLAVE\_SPI\_ACK Slave is busy (Output from DLPC200)

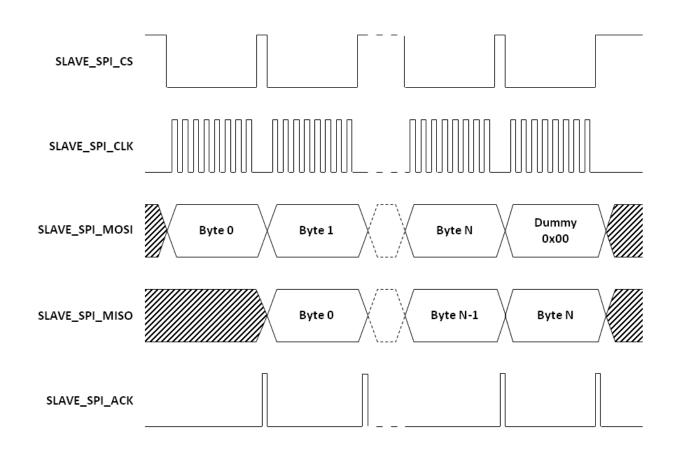

The data transmission over SPI bus happens in byte-by-byte mode. To begin communication the master should first check for SLAVE\_SPI\_ACK signal status LOW. In the next step the master pulls the SLAVE\_SPI\_CS signal to LOW. After this the master can proceed with clocking data at a frequency less than or equal to 5MHz. During each SPI clock cycle, a full duplex data transmission occurs; that is the master sends a bit on the SLAVE\_SPI\_MOSI line; the slave reads it from that same line and the slave sends a bit on the SLAVE\_SPI\_MISO line; the master reads it from that same line. The master must always check SLAVE\_SPI\_ACK LOW before transmitting or receiving data byte, see Figure 1.

#### Figure 1. SPI Byte Transfer

At a high level the commands supported over SPI interface in two categories. The first category of commands are called "Extended Packet". The second category commands are called "Low Level Packet". An Extended Packet is represented as an array of bytes with a maximum array size up to 511 bytes. [NOTE: The packet is limited to 511 bytes because if a packet is 512 bytes the additional Dummy byte will cause the data length to be 513 and the dummy byte will be pushed into the next packet]

Commands larger than one Extended Packet size are called as multi-packet commands. For the full list of commands supported by the extended packet communication interface, please see the List of Contents later in this section. Similar to Extended Packet the Low Level Packet is also represented as an array of bytes with a maximum size up to 511 bytes. These command packets allow low level control like Flash Programming, Firmware Update, EDID update, and direct image download. For the full list of commands, please see List of Contents of Low Level Commands in Section 7.

#### 5 Command/Response Protocol

The DLPC200 SPI slave interface follows the command/response mode of operation. The SPI master sends a command and then reads a response from the slave. The SPI master cannot directly send the next command before reading the response for the previous command.

#### 5.1 Sending Command

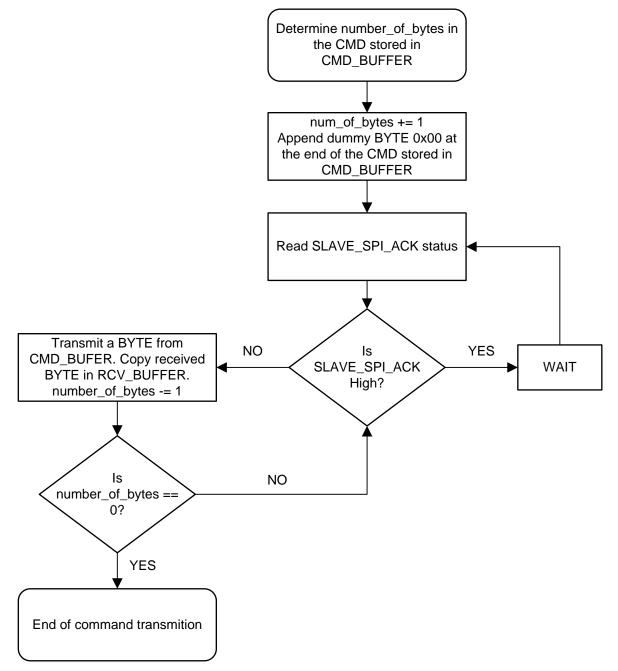

Each byte written by master is echoed back on the SLAVE\_SPI\_MISO pin of the DLPC200 controller. Basically the first byte in the command is echoed during transmission of the second byte of the command. Therefore the master has to send one extra dummy byte to read the entire command. This mechanism provides an option for the master to validate if the command is delivered successfully. If the master finds the command is not delivered successfully then it can resend the command again. It should be noted that in case of an unsuccessful delivery the master still has to read the command response for the unsuccessful command. Aborting command transmission in the middle is not allowed. In case of multi packet command, the master should read the response only at the end of the last packet of the command. See Figure 2 and Figure 3 for command transmit and response flow charts.

Figure 2. Write Command Transmit Flowchart

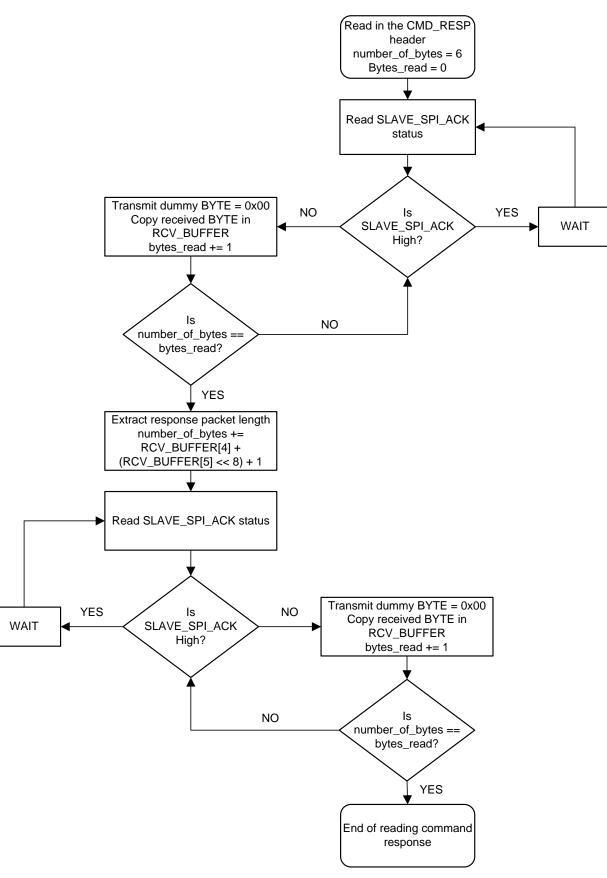

#### 5.2 Reading Command Response

After sending the command the DLPC200 sets SLAVE\_SPI\_ACK signal HIGH to indicate it is busy in processing the command packet. This signal is set to LOW at the end of command execution. The master should not read the response until the signal is LOW. The amount of time taken to process the command packet varies on the type request made in the command. To read the response from the DLPC200 the SPI master must transmit a number of dummy (0x00) bytes and the response will be sent through the SLAVE\_SPI\_MISO signal. The amount of dummy bytes to be sent by the master can be predetermined by the expected command response structure or determined dynamically by reading the length of the response in its header. For details on the packet response header structure see Extended Packet Definition. It is important to note, that if a trailing dummy byte was sent with the SPI command, when attempting to read the command response the dummy (0x00) byte will be echoed before the command response and must be disregarded. The read response flow chart in Figure 3 assumes that a trailing dummy byte was not sent with the SPI command.

Command/Response Protocol

Figure 3. Read Command Response Flowchart

#### 6 Extended Packet Definition

The structure of this 511-byte extended packet is shown below:

| HEADER |        |        |        |         | DATA    | CHECKSUM |        |

|--------|--------|--------|--------|---------|---------|----------|--------|

| CMD1   | CMD2   | CMD3   | CMD4   | Len_LSB | Len_MSB | 0-504    | 1 byte |

| 1 byte  | 1 byte  | bytes    |        |

#### **Definition of CMD1**

- WRITE 0x02 (for set/enable/configure type functionality)

- WRITE\_RESP 0x03

- READ 0x04 (for status/query type functionality)

- READ RESP 0x05

#### **Definition of CMD2**

• Unique ID assigned to CMD2 as 0xAA to identify the packet is of Extended Packet type.

#### **Definition of CMD3**

CMD3 is reserved or unused. By default CMD3 should be set to 0x00

#### Definition of CMD4

- CMD4 is meant to serve as a flag to track where in a multi-packet transfer it is. For example, there may be many packets needed to download an ImageOrderLut (CMD ID = 0x000D). This flag will track where in this packet transfer stream it is – beginning, middle, or end.

- Only transfer of command 0x00, that is single register accesses

- First of many transfers 0x01

- Middle of many transfer 0x02

- Last of many transfers 0x04

At a high level the commands are categorized as Set/Enable/Configure type or Get/GetStatus type. For all Set/Enable/Configure type commands the response is the same. Upon receipt of a command, the DLPC200 will send a response back to the master. If the command was received and accepted, a value of 0x0000 would be returned in the data buffer. It would look like the following:

#### **RESPONSE PACKET STRUCTURE:**

CMD1 = 0x03 (WRITE\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Checksum = 0x02 (of everything after CMD4)

If the transfer was corrupted in some way then the DLPC200 will set certain bits in the data buffer Data[0] and Data[1] as indicated in the following table.

| Data[0] <sup>(1)(2)</sup>    |                                        |  |  |

|------------------------------|----------------------------------------|--|--|

| Bit 0: CMD_ERR_CHK_SUM_ERROR | Request packet has checksum error.     |  |  |

| Bit 1: CMD_ERR_INVALID_CMD1  | Request packet has invalid CMD1 value. |  |  |

| Bit 2: CMD_ERR_INVALID_CMD2  | Request packet has invalid CMD2 value. |  |  |

(1) The flags shaded in GRAY will be applicable for the Extended Packet response; other flags are not applicable and will be set to '0'.

<sup>&</sup>lt;sup>(2)</sup> If the packet is processed without errors then all the flags defined in Data[0] and Data[1] of response packet will be set to '0' to indicate success.

www.ti.com

| Data[0] <sup>(1)(2)</sup>                    |                                                                                                                                 |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 3: CMD_ERR_INVALID_CMD3                  | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 4: CMD_ERR_INVALID_CMD4                  | Request packet has invalid CMD4 value.                                                                                          |  |  |  |

| Bit 5: CMD_ERR_INVALID_ADDRESS               | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 6: CMD_ERR_CMD_EXE_FAILED                | Extended Packet processing failed.                                                                                              |  |  |  |

| Bit 7:<br>CMD_ERR_ABRUPT_TERM_OF_MUL_PKT_CMD | Will be set when a packet containing a CMD4 value of 0x01 or 0x00 is sent after a packet containing CMD4 value of 0x01 or 0x02. |  |  |  |

| Data[1] <sup>(1)(2)(3)</sup>                 |                                                                                                                                 |  |  |  |

| Bit 0: RFU (Reserved for Future Use)         | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 1: RFU                                   | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 2: RFU                                   | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 3: CMD_ERR_INSUF_CMD_DATA                | Insufficient or excess data passed in the extended command packet.                                                              |  |  |  |

| Bit 4: CMD_ERR_INVALID_ADD_OFST              | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 5: CMD_ERR_FLSH_DWLD_FAIL                | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 6: CMD_ERR_EDID_UPDATE_FAIL              | Not applicable for Extended Packet.                                                                                             |  |  |  |

| Bit 7: CMD_ERR_CORRUPT_PKT_RCVD              | Not applicable for Extended Packet.                                                                                             |  |  |  |

<sup>(3)</sup> If error encountered while processing a command one of the flag (shaded in GRAY) along with Bit 6 is SET. In the event that only Bit 6 of Data[0] is SET, GetExtendedPktFailReason (CMD ID = 0x0000) can be sent to find specific reason for failure.

The response for Get/GetStatus type commands are different for each command, refer to a command's detailed specifications for the expected response structure.

TEXAS INSTRUMENTS

www.ti.com

#### Table 1. List of Commands

| SECTION<br>NO. | TITLE                                                  |

|----------------|--------------------------------------------------------|

| 6.1            | GetExtendedPktFailReason (0x0000)                      |

| 6.2            | DisplayPatternManualStep (0x0001)                      |

| 6.3            | DisplayPatternManualForceFirstPattern (0x0002)         |

| 6.4            | DisplayPatternAutoStepRepeatForMultiplePasses (0x0003) |

| 6.5            | DisplayStop (0x0004)                                   |

| 6.6            | ParkDMD (0x0005)                                       |

| 6.7            | UnparkDMD (0x0006)                                     |

| 6.8            | SetDegammaEnable (0x0007)                              |

| 6.9            | HorizontalFlip (0x0008)                                |

| 6.10           | VerticalFlip (0x0009)                                  |

| 6.11           | LEDintensity (0x000A)                                  |

| 6.12           | LEDdriverEnable (0x000B)                               |

| 6.13           | SetLEDEnable (0x000C)                                  |

| 6.14           | WriteImageOrderLut (0x000D)                            |

| 6.15           | SetDataSource (0x000E)                                 |

| 6.16           | SetExternalTriggerEdge (0x000F)                        |

| 6.17           | SetTestPattern (0x0010)                                |

| 6.18           | SetSyncEnable (0x0011)                                 |

| 6.19           | SyncConfigure (0x0012)                                 |

| 6.20           | GetDMDparkState (0x0013)                               |

| 6.21           | GetDMDhardwareParkState (0x0014)                       |

| 6.22           | GetDMDsoftwareParkState (0x0015)                       |

| 6.23           | GetSeqRunState (0x0016)                                |

| 6.24           | GetEEPROMfault (0x0017)                                |

| 6.25           | GetDADfault (0x0018)                                   |

| 6.26           | GetLEDdriverFault (0x0019)                             |

| 6.27           | GetUARTfault (0x001A)                                  |

| 6.28           | GetFlashProgrammingMode (0x001B)                       |

| 6.29           | GetDADcommStatus (0x001C)                              |

| 6.30           | GetDMDcommStatus (0x001D)                              |

| 6.31           | GetLEDcommStatus (0x001E)                              |

| 6.32           | GetSeqDataMode (0x001F)                                |

| 6.33           | GetSeqDataNumPatterns (0x0020)                         |

| 6.34           | GetSeqDataBPP (0x0021)                                 |

| 6.35           | GetSeqDataFrameRate (0x0022)                           |

| 6.36           | GetSeqDataExposure (0x0023)                            |

| 6.37           | GetFlashSeqCompilerVersion (0x0024)                    |

| 6.38           | GetDlpControllerSWVersion (0x0025)                     |

| 6.39           | GetDlpControllerVersion (0x0026)                       |

| 6.40           | GetBISTdone (0x0027)                                   |

| 6.41           | GetBISTfail (0x0028)                                   |

| 6.42           | GetInitFromParallelFlashFail (0x0029)                  |

| 6.43           | GetOverallLEDlampLitState (0x002A)                     |

| 6.44           | GetLEDdriverLitState (0x002B)                          |

| 6.45           | GetOverallLEDdriverTempTimeoutState (0x002C)           |

| 6.46           | GetLEDdriverTempTimeoutState (0x002D)                  |

| 6.47           | GetOverallLEDdriverStrobeTimeoutState (0x002E)         |

| 6.48           | GetLEDdriverStrobeTimeoutState (0x002F)                |

| 6.49           | DownloadBPPfromFlashToExtMem (0x0030)                  |

| 6.50           | LoadSolutionFromFlash (0x0031)                         |

| 6.51           | PWMSeqEnable (0x0032)                                  |

#### Table 1. List of Commands (continued)

| SECTION<br>NO. | TITLE                                        |

|----------------|----------------------------------------------|

| 6.52           | DisplayPatternAutoStepForSinglePass (0x0033) |

| 6.53           | GenerateSWVSync(0x0034)                      |

| 6.54           | ConfigurePWMPeriod(0x0035)                   |

| 6.55           | ConfigurePWMDutyCycle(0x0036)                |

### 6.1 GetExtendedPktFailReason (0x0000)

This packet is used to find the reason the last Extended Packet sent failed. The two bytes allocated Data[0] Data[1] in the response packet will give some level of information which is generic in nature. This packet will give reason for failure specific to Extended Packets.

#### PACKET STRUCTURE:

```

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x02

Len_MSB = 0x00

Data[0] = 0x00 (Extended packet ID 16bit value)

Data[1] = 0x00

Checksum = 0x02 (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

#### **RESPONSE PACKET STRUCTURE:**

```

CMD1 = 0x05 (READ_RESP)

CMD2 = 0xAA

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x04

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

//Extended Packet processing failure reason 16bit value

Data[2] = 0xXX (LSB)

Data[3] = 0xXX (LSB+1)

Checksum = 0xXX (sum of everything after CMD4)

```

To interpret 16bit Extended Packet Processing failure reason use the values below:

0x0000: No error occurred while processing the packet.

0x0001: Unknown Extended Packet ID

0x0002: CMD1 mismatch that is, the packet is query or status type but packet received as write (CMD1 = 0x02) OR the packet is set/configure type while the packet received as read (CMD1 = 0x04)

0x0003: Invalid or wrong parameter the packet definition does not match.

0x0004: Test Pattern display failed; system is NOT in "Video Mode".

0x0005: Load Solution failed - Device cannot be accessed

0x0006: Load Solution failed - Solution offset address is invalid

0x0007: Load Solution failed - Flash is not programmed

0x0008: Load Solution failed - Failures detected while loading the Solution

0x0009 - 0x00FF: Reserved/Unused

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

**NOTE:** After reading the reason for failure, the error would be reset. That means sending this packet twice (one after another) returns 0x0000 (no error) for the second packet.

Extended Packet Definition

### 6.2 DisplayPatternManualStep (0x0001)

Repeatedly displays the next structured light image (as defined in the Image Order LUT-0x000D). Once bit plane patterns have been loaded into external memory and the DLP Control Chip is fully configured, this function can be called to command the DMD and DLP Controller Chip to display the patterns as defined in the Image Order LUT. If multiple image patterns are available for display, then each pattern can be displayed upon request by calling this function (repeatedly). When using an internally-programmed VSYNC, a single pattern will be displayed continuously, which allows for (human) visual inspection.

### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x01 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x03 (sum of everything after CMD4)

# 6.3 DisplayPatternManualForceFirstPattern (0x0002)

Repeatedly displays the first structured light image (as defined in the Image Order LUT-0x000D). Once bit plane patterns have been loaded into external memory, and the DLP Control Chip is fully configured, this function can be called to command the DMD and DLP Controller Chip to display the first pattern as defined in the Image Order LUT. Use this function in conjunction with DLP\_Display\_Display Pattern Manual Step to start at the beginning of the Image Order LUT and index through it to see its corresponding images.

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x02 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x04 (sum of everything after CMD4)

#### 6.4 DisplayPatternAutoStepRepeatForMultiplePasses (0x0003)

Continuously displays all structured light images (as defined in Image Order LUT-0x000D), one image per frame. Once bit plane patterns have been loaded into external memory, and the DLP Control Chip is fully configured, this function can be called to command the DMD and DLP Controller Chip to display the patterns. If multiple image patterns are available for display, then the series of patterns can repeatedly be displayed by calling this function (once). If there are 10 patterns available for display, calling this function will display all 10 patterns then repeat.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x03 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x05 (sum of everything after CMD4)

# 6.5 DisplayStop (0x0004)

This function will disable the display of bit plane patterns.

### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x04 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x06 (sum of everything after CMD4)

# 6.6 ParkDMD (0x0005)

Mirrors in the DMD will be parked upon receipt of this packet. LEDs will be turned off so that there will not be any light output.

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x05 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x07 (sum of everything after CMD4)

www.ti.com

#### 6.7 UnparkDMD (0x0006)

Mirrors in the DMD will be unparked upon receipt of this packet.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x06 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x08 (sum of everything after CMD4)

### 6.8 SetDegammaEnable (0x0007)

Enable/disable degamma function. The degamma function is typically associated with video data and is used to linearize the light output (by removing the applied Gamma transfer function). When enabling degamma, a corresponding LUT must have already been programmed with non-zero values. The degamma LUT is an output of the LOGIC application SW.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)  $Len\_LSB = 0x03$   $Len\_MSB = 0x00$  Data[0] = 0x07 (Extended packet ID 16bit value) Data[1] = 0x00 Data[2] = 0x00 (disable degamma) 0x01 (enable degamma)

Checksum = 0x0X (sum of everything after CMD4)

**NOTE:** Unlike ParkDMD LEDs will not be turned ON upon receipt of this packet. This is done to preserve the user set state for the LEDs ON or OFF.

# 6.9 HorizontalFlip (0x0008)

Enable/disable horizontal flip of the display image/pattern.

# PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)  $Len\_LSB = 0x03$   $Len\_MSB = 0x00$  Data[0] = 0x08 (Extended packet ID 16bit value) Data[1] = 0x00 Data[2] = 0x00 (disable horizontal flip) 0x01 (enable horizontal flip) Checksum = 0x0X (sum of everything after CMD4)

# 6.10 VerticalFlip (0x0009)

Enable/disable vertical flip of the displayed image/pattern.

# PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)  $Len\_LSB = 0x03$   $Len\_MSB = 0x00$  Data[0] = 0x09 (Extended packet ID 16bit value) Data[1] = 0x00 Data[2] = 0x00 (disable vertical flip) 0x01 (enable vertical flip) Checksum = 0x0X (sum of everything after CMD4)

#### 6.11 LEDintensity (0x000A)

Sets the LED intensity. Upon receiving this packet, the DLP Controller SW sends a request to the LED driver to supply current to the LED using the value specified in the packet. For 100% intensity, the LED will be driven using the max allowed LED current.

For example, if the max LED current is 10 A, then sending this packet with a value of 50 (decimal) will set the LED current to 5 A (=10 A $\times$ 50/100).

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00CMD4 = 0x00 (only packet of transfer)  $Len_LSB = 0x05$  $Len_MSB = 0x00$ Data[0] = 0x0A (Extended packet ID 16bit value) Data[1] = 0x00Data[2] = 0x00 (Red LED)0x01 (Green LED) 0x02 (Blue LED) 0x03 (IR LED) //Intensity in percentage in 8.8 format, 0.0% = 0x0000 and 100.0% = 0x6400Data[3] = 0xXX (integer portion of 8.8 format) Data[4] = 0xXX (fractional portion of 8.8 format) Checksum = 0xXX (sum of everything after CMD4)

#### **GetLEDintensity (READ)**

Gets the LED intensity being applied to the LEDs.

#### PACKET STRUCTURE:

```

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len\_LSB = 0x03

Len\_MSB = 0x00

Data[0] = 0x0A (Extended packet ID 16bit value)

Data[1] = 0x00

Data[2] = 0x00 (Red LED)

0x01 (Green LED)

0x02 (Blue LED)

0x03 (IR LED)

Checksum = 0xXX (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

#### **RESPONSE PACKET STRUCTURE**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x04 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) //Intensity in percentage in 8.8 format, 0.0% = 0x0000 and 100.0% = 0x6400 Data[2] = 0xXX (integer portion of 8.8 format) Data[3] = 0xXX (fractional portion of 8.8 format) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

Extended Packet Definition

#### www.ti.com

#### 6.12 LEDdriverEnable (0x000B)

This is the debug packet for testing driver enable/disable. Send 0 to disable LED driver; send 0x01 to enable. This packet can be used to re-enable the LED driver for cases where it has "timed out" and become disabled because of missing strobes or over temperature.

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)  $Len\_LSB = 0x03$   $Len\_MSB = 0x00$  Data[0] = 0x0B (Extended packet ID 16bit value) Data[1] = 0x00 Data[2] = 0x01 (enable driver) 0x00 (disable driver)

Checksum = 0x0X (sum of everything after CMD4 )

### 6.13 SetLEDEnable (0x000C)

Debug interface to enable or disable individual LED driver channel. If the PWM Seq has been built with the specified LED, then this API can be used to disable (then re-enable) the LED.

#### PACKET STRUCTURE:

```

CMD1 = 0x02 (WRITE)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len\_LSB = 0x04

Len\_MSB = 0x00

Data[0] = 0x0C (Extended packet ID 16bit value)

Data[1] = 0x00

Data[2] = 0x00 (Red LED)

0x01 (Green LED)

0x02 (Blue LED)

0x03 (IR LED)

Data[3] = 0x00 (disable LED)

0x01 (enable LED)

Checksum = 0xXX (sum of everything after CMD4)

```

**NOTE:** If the specified LED does not have a PWM sequence built in the current solution, enabling the LED using this command will not cause the LED to turn on.

### 6.14 WriteImageOrderLut (0x000D)

Sets the Image Order LUT. This function allows users to define the display order for image data stored in external memory which will be used in structured light mode. This allows the display order of the images to be changed without having to re-load the image data to external memory.

**Example:** Three 8-bit image patterns are stored in external memory as {image 0, image 1, image2}, but user wants display order = {2, 1, 0}

The LightCommander<sup>™</sup> system has 1Gbit NOR flash to store the patterns. On a 1Gbit flash the maximum number of patterns allowed are 960 for 1bpp type and 120 for 8bpp type patterns. Due to the packet structure limitation, a maximum of 249 patterns information allowed in a packet. When the number of patterns exceeds 249, a multi-packet transaction will be required. Therefore maximum of 4 packets will be required to load the Image Order LUT for entire 960 1bpp patterns in the external memory. Typically, for 8bpp patterns all the 120 patterns can fit into a single packet.

#### Case 1:

The number of patterns in Image Order LUT is  $\leq$  249 (single packet transaction), below is an example with 250 entries is shown.

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00CMD4 = 0x00 (only packet of transfer) Len LSB = 0xF9 $Len_MSB = 0x01$ Data[0] = 0x0D (Extended packet ID 16bit value) Data[1] = 0x00//Bit per pixel, 0x01 = 1 bpp or 0x08 = 8 bpp Data[2] = 0x01//Number of images in pattern order LUT //Valid range 0-960 if 1bpp, else 0-120 Data[3] = 0xFA (LSB)Data[4] = 0x00 (LSB+1)//Image pattern display order entries //1st image: external memory image index [0:959] Data[5] = 0xXXData[6] = 0xXX//2nd image: external memory image index [0:959] Data[7] = 0xXXData[8] = 0xXX//249th image: external memory image index [0:959] Data[501] = 0xXXData[502] = 0xXXChecksum = 0xXX (sum of everything after CMD4)

The response for LUT entires of a single packet, will have the same response as a typical Set/Enable/Configure command, see for details.

#### Case 2:

The number of patterns > 249 (multi-packet transaction). The example shown below is for 960 LUT entries.

**NOTE:** Only fetch write response after sending all packets (e.g. don't get write response after each packet).

PACKET STRUCTURE (1st packet):

```

CMD1 = 0x02 (WRITE)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x01 (First of many)

Len_LSB = 0xF9

Len_MSB = 0x01

Data[0] = 0x0D (Extended packet ID 16bit value)

Data[1] = 0x00

//Bits per pixel, 0x01 = 1 bpp or 0x08 = 8 bpp//

Data[2] = 0x01

//Number of images in pattern order LUT

//Valid range 0-960 if 1bpp, else 0-120

Data[3] = 0x03 (LSB)

Data[4] = 0xC0 (LSB+1)

//Image pattern display order entries

//1st image: external memory image index [0:959]

Data[5] = 0xXX

Data[6] = 0xXX

//2nd image: external memory image index [0:959]

Data[7] = 0xXX

Data[8] = 0xXX

...

//249th image: external memory image index [0:959]

Data[501] = 0xXX

Data[502] = 0xXX

Checksum = 0xXX (sum of everything after CMD4)

```

#### PACKET STRUCTURE (2nd packet):

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x02 (Intermediate packet) Len\_LSB = 0xF9 Len\_MSB = 0x01 Data[0] = 0x0D (Extended packet ID 16bit value) Data[1] = 0x00

```

//Bit per pixel, 0x01 = 1bpp or 0x08 = 8bpp//

Data[2] = 0x01

//Number of images in pattern order LUT

//Valid range 0-960 if 1bpp, else 0-120

Data[3] = 0x03 (LSB)

Data[4] = 0xC0 (LSB+1)

//Image pattern display order entries

//250th image: external memory image index [0:959]

Data[5] = 0xXX

Data[6] = 0xXX

//252nd image: external memory image index [0:959]

Data[6] = 0xXX

Data[7] = 0xXX

...

//500th image: external memory image index [0:959]

Data[501] = 0xXX

Data[502] = 0xXX

Checksum = 0xXX (sum of everything after CMD4)

PACKET STRUCTURE (3rd packet):

CMD1 = 0x02 (WRITE)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x02 (Intermediate packet)

Len LSB = 0xF9

Len_MSB = 0x01

Data[0] = 0x0D (Extended packet ID 16bit value)

Data[1] = 0x00

//Bit per pixel, 0x01 = 1 bpp or 0x08 = 8 bpp

Data[2] = 0x01

//Number of images in pattern order LUT

//Valid range 0-960 if 1bpp, else 0-120

Data[3] = 0x03 (LSB)

Data[4] = 0xC0 (LSB+1)

//Image pattern display order entries

//501st image: external memory image index [0:959]

Data[5] = 0x0X

Data[6] = 0xXX

//502nd image: external memory image index [0:959]

Data[7] = 0x0X

Data[8] = 0xXX

...

//750th image: external memory image index [0:959]

Data[501] = 0x0X

Data[502] = 0xXX

```

www.ti.com

Checksum = 0xXX (sum of everything after CMD4)

PACKET STRUCTURE (4th and last packet):

```

CMD1 = 0x02 (WRITE)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x04 (last of many packet)

Len LSB = 0xA9

Len_MSB = 0x01

Data[0] = 0x0D (Extended packet ID 16bit value)

Data[1] = 0x00

//Bit per pixel, 0x01 = 1 bpp or 0x08 = 8 bpp

Data[2] = 0x01

//Number of images in pattern order LUT

//Valid range 0-960 if 1bpp, else 0-120

Data[3] = 0x03 (LSB)

Data[4] = 0xC0 (LSB+1)

//Image pattern display order entries

//751st image: external memory image index [0:959]

Data[5] = 0xXX

Data[6] = 0xXX

//752nd image: external memory image index [0:959]

Data[7] = 0xXX

Data[8] = 0xXX

...

//960th image: external memory image index [0:959]

Data[423] = 0xXX

Data[424] = 0xXX

Checksum = 0xXX (sum of everything after CMD4)

```

Upon receipt of the last packet, the DLPC200 will send a response back to the master. If the command was received and accepted, Data[0] = 0x00 and Data[1] = 0x00 in the command response. The response packet will have the following structure:

**RESPONSE PACKET STRUCTURE:**

```

CMD1 = 0x03 (WRITE_RESP)

CMD2 = 0x06 (Function Group name)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x08

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

// Zero bytes

Data[2] = 0x00

Data[3] = 0x00

```

// No. of packets received by controller, 32bit value Data[4] = 0xXX (LSB) Data[5] = 0xXX (LSB+1) Data[6] = 0xXX (LSB+2) Data[7] = 0xXX (LSB+3)

Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

#### **bpp**—bits-per-pixel

**1bpp** — Pixel represented in 1bit.

For example the number of bits required to represent a 1bpp XGA pattern will be 1024\*768\*1 = 786432 bits

8bpp — Pixel represented in 8bits

For example the number of bits required to represent a 8bpp XGA pattern will be 1024\*768\*8 = 6291456 bits

- **NOTE:** Sending wrong info on bpp and/or number of images (more than actual patterns loaded in the DDR2 memory) and/or wrong pattern slot number will result in displaying corrupted data.

- **NOTE:** On encountering an invalid slot number (slot number > 959) no further processing of the packet will be done. GetExtendedPktFailReason packet will return the appropriate error code tht is, 0x0003: Invalid or wrong parameter.

#### 6.15 SetDataSource (0x000E)

Sets the input data source.

#### PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00CMD4 = 0x00 (only packet of transfer)  $Len_LSB = 0x03$ Len MSB = 0x00Data[0] = 0x0E (Extended packet ID 16bit value) Data[1] = 0x00Data[2] = 0x00 (DVI - port 0) 0x01 (Expansion port - port 1) 0x02 (Test pattern generator, frame triggers VSYNC) 0x03 (Structured light auto gen) 0x04 (Structured light external trigger 3.3V) 0x05 (Structured light external trigger 1.8V) 0x06 (Structured light software generated Trigger) Checksum = 0xXX (sum of everything after CMD4)

# 6.16 SetExternalTriggerEdge (0x000F)

Programs the trigger edge.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)  $Len\_LSB = 0x03$   $Len\_MSB = 0x00$  Data[0] = 0x0F (Extended packet ID 16bit value) Data[1] = 0x00 Data[2] = 0x00 (Falling Edge) 0x01 (Rising Edge) Checksum = 0xXX (sum of everything after CMD4)

www.ti.com

### 6.17 SetTestPattern (0x0010)

When the input source is Test Pattern Generator, this command programs which test pattern to display. Valid values for spatial repetition parameter in XGA type device are 1,2,4,8,16,32,64,128,256,512. Patterns that display horizontally will repeat according to this parameter. Due to the non-power of 2 vertical DMD resolutions, vertical repetition of patterns is loosely based on the spatial repetition value. Test Patterns can be displayed in Video Mode only.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00CMD4 = 0x00 (only packet of transfer) Len LSB = 0x06Len MSB = 0x00Data[0] = 0x10 (Extended packet ID 16bit value) Data[1] = 0x00Data[2] = 0x00 (Solid Field) 0x01 (Horizontal Ramp) 0x02 (Vertical Ramp) 0x03 (Horizontal Lines) 0x04 (Diagonal Lines) 0x05 (Vertical Lines) 0x06 (Horizontal Stripes) 0x07 (Vertical Stripes) 0x08 (Grid) 0x09 (Checkerboard) Data[3] = 0x00 (Black) 0x01 (Red) 0x02 (Green) 0x03 (Blue) 0x04 (Yellow) 0x05 (Cyan) 0x06 (Magenta) 0x07 (White) //Pattern spatial repeat frequency (16bit value) Data[4] = 0xXX (LSB)Data[5] = 0xXX (LSB+1)Checksum = 0xXX (sum of everything after CMD4)

# 6.18 SetSyncEnable (0x0011)

There are three sync outputs available for the external source trigger. This packet used to enable/disable the specified output sync.

PACKET STRUCTURE:

CMD1 = 0x02 (WRITE) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)

Extended Packet Definition

Len\_LSB = 0x04 Len\_MSB = 0x00 Data[0] = 0x11 (Extended packet ID 16bit value) Data[1] = 0x00 //Sync number to enable Data[2] = 0x01 (Sync# 1) 0x02 (Sync# 2) 0x03 (Sync# 3) Data[3] = 0x01 (enable Sync) 0x00 (disable Sync) Checksum = 0xXX (sum of everything after CMD4)

### 6.19 SyncConfigure (0x0012)

There are three sync outputs available for the external source trigger. This packet is used to configure the specified output sync.

PACKET STRUCTURE:

```

CMD1 = 0x02 (WRITE)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len LSB = 0x0C

Len_MSB = 0x00

Data[0] = 0x12 (Extended packet ID 16bit value)

Data[1] = 0x00

//Sync channel to configure

Data[2] = 0x01 (Sync# 1)

0x02 (Sync# 2)

0x03 (Sync# 3)

//Sync polarity

Data[3] = 0x01 (Positive)

0x00 (Negative)

//Output sync delay in microseconds 32bit value

Data[4] = 0xXX (LSB)

Data[5] = 0xXX (LSB+1)

Data[6] = 0xXX (LSB+2)

Data[7] = 0xXX (LSB+3)

//Output sync pulse width in microseconds 32bit value

Data[8] = 0xXX (LSB)

Data[9] = 0xXX (LSB+1)

Data[10] = 0xXX (LSB+2)

Data[11] = 0xXX (LSB+3)

Checksum = 0xXX (sum of everything after CMD4)

```

### 6.20 GetDMDparkState (0x0013)

Gets the DMD park state.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x13 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x15 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE:

```

CMD1 = 0x05 (READ_RESP)

CMD2 = 0xAA

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x03

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

Data[2] = 0x00 (DMD is un-parked)

0x01 (DMD is parked)

Checksum = 0xXX (sum of everything after CMD4)

```

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.21 GetDMDhardwareParkState (0x0014)

Helps in determining if DMD isparked by the hardware switch.

```

PACKET STRUCTURE:

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x02

Len_MSB = 0x00

Data[0] = 0x14 (Extended packet ID 16bit value)

Data[1] = 0x00

Checksum = 0x16 (sum of everything after CMD4)

```

www.ti.com

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (hardware switch not activated) 0x01 (DMD park active by hardware switch) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

#### 6.22 GetDMDsoftwareParkState (0x0015)

Determines if the DMD parked state is caused by a software issued command (that is ParkDMD – 0x0005).

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x15 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x17 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (DMD park not requested by the software) 0x01 (DMD park requested by the software)

Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.23 GetSeqRunState (0x0016)

Gets the PWM sequence run state: running or stopped.

```

PACKET STRUCTURE:

```

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x16 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x18 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

### RESPONSE PACKET STRUCTURE:

```

CMD1 = 0x05 (READ_RESP)

CMD2 = 0xAA

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x03

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

Data[2] = 0x00 (PWM sequence stopped)

0x01 (PWM sequence running)

Checksum = 0xXX (sum of everything after CMD4)

```

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.24 GetEEPROMfault (0x0017)

The EEPROM device stores the EDID info. This packet is used to check if an EEPROM fault is detected.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer)

Extended Packet Definition

Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x17 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x19 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE: CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (no fault detected) 0x01 (fault detected) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.25 GetDADfault (0x0018)

Checks for DLPA200 (aka DAD = Analog reset driver) fault.

```

PACKET STRUCTURE:

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x02

Len_MSB = 0x00

Data[0] = 0x18 (Extended packet ID 16bit value)

Data[1] = 0x00

Checksum = 0x1A (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03

31

Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (no fault detected) 0x01 (fault detected) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.26 GetLEDdriverFault (0x0019)

Checks for LED Driver fault.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x19 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x1B (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (no fault detected) 0x01 (fault detected)

Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.27 GetUARTfault (0x001A)

Checks for UART port fault.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x1A (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x1C (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (no fault detected) 0x01 (fault detected) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

#### 6.28 GetFlashProgrammingMode (0x001B)

Checks if the system is in flash programming mode.

PACKET STRUCTURE:

```

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x02

Len_MSB = 0x00

Data[0] = 0x1B (Extended packet ID 16bit value)

Data[1] = 0x00

Checksum = 0x1D (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

# TEXAS INSTRUMENTS

www.ti.com

#### **RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (normal mode) 0x01 (flash programming mode) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.29 GetDADcommStatus (0x001C)

Gets DLPA200/DAD SPI communication status.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x1C (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x1E (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

#### **RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (DAD comm-stat OK) 0x01 (DAD comm-stat Failure) Checksum = 0xXX (sum of everything after CMD4)

www.ti.com

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

#### 6.30 GetDMDcommStatus (0x001D)

Gets DMD SPI communication status.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x1D (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x1F (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

#### **RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (DMD comm-stat OK) 0x01 (DMD comm-stat Failure) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.31 GetLEDcommStatus (0x001E)

Gets LED Driver SPI communication status.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00

Data[0] = 0x1E (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x20 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (LED comm-stat OK) 0x01 (LED comm-stat Failure) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.32 GetSeqDataMode (0x001F)

Gets sequence data mode. Meta data describing the currently loaded PWM sequence.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x1F (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x21 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE: CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully)

Extended Packet Definition

Data[1] = 0x00 (request processed successfully)

Data[2] = 0x00 (Structured light, non real-time input) 0x01 (Structured light, real-time input) 0x02 (Video mode) 0x03 (Video plus Structured Light) 0x04 (Object mode) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

### 6.33 GetSeqDataNumPatterns (0x0020)

Gets sequence data - number of patterns per frame. Meta data describing the number of patterns per frame is used for building currently loaded PWM sequences.

#### PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x20 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x22 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

#### **RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) //Number of patterns output per frame (16bit value) Data[2] = 0xXX (LSB) Data[3] = 0xXX (LSB+1) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.34 GetSeqDataBPP (0x0021)

Gets sequence data BPP (number of bits per pixel). Meta data describing the BPP used for building the currently loaded PWM sequence. BPP is only applicable in structured light mode.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x21 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x23 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

```

CMD1 = 0x05 (READ_RESP)

CMD2 = 0xAA

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x03

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

Data[2] = 0x01 (1bpp)

0x08 (8bpp)

Checksum = 0xXX (sum of everything after CMD4)

```

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.35 GetSeqDataFrameRate (0x0022)

Meta data describing the frame rate (in Hz) used for building the currently loaded PWM sequence.

PACKET STRUCTURE: CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02

37

Len\_MSB = 0x00 Data[0] = 0x22 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x24 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x05 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) //Sequence frame rate 20bit value in u16.4 format Data[2] = 0xXX (LSB) Data[3] = 0xXX (LSB+1) Data[4] = 0xXX (LSB+2) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

### 6.36 GetSeqDataExposure (0x0023)

Gets sequence data for structured light exposure. Meta data describing the exposure time (in µsec) used for building the currently loaded PWM sequence.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x23 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x25 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE: CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x04 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) //Exposure time in uSecs (16bit value) Data[2] = 0xXX (LSB) Data[3] = 0xXX (LSB+1) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.37 GetFlashSeqCompilerVersion (0x0024)

Gets the version number of the sequence compiler DLL used to build the PWM sequence. Format: Major.Minor.patch.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x24 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x26 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

### RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x05 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0xXX (major version) Data[3] = 0xXX (minor version) Data[4] = 0xXX (patch version) Checksum = 0xXX (sum of everything after CMD4)

#### Extended Packet Definition

www.ti.com

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

### 6.38 GetDlpControllerSWVersion (0x0025)

Gets the DLPC200 controller software version. Format: Major.Minor.Patch.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x25 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x27 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

### RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x05 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0xXX (major version) Data[3] = 0xXX (minor version) Data[4] = 0xXX (patch version ) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

### 6.39 GetDlpControllerVersion (0x0026)

Gets the DLPC200 HW version number. Format: Major.Minor.patch.

PACKET STRUCTURE: CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02

Len\_MSB = 0x00 Data[0] = 0x26 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x28 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

## RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x06 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0xXX (major version) Data[3] = 0xXX (minor version) Data[4] = 0xXX (patch version LSB) Data[5] = 0xXX (patch version LSB+1) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.40 GetBISTdone (0x0027)

Get External Memory BIST done state. The Packet can be used to determine if the Built-In-Self-Test (BIST) operation has completed. A BIST operation is performed on the external frame memory every power up.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x27 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x29 (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (BIST Not done) 0x01 (BIST done) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.41 GetBISTfail (0x0028)

Gets the BIST fail state. Every power up, a Built-In-Self-Test (BIST) operation is run on the external memory, and the pass/fail state is saved off. This packet is used to check whether the BIST passed or failed.

PACKET STRUCTURE:

```

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x02

Len_MSB = 0x00

Data[0] = 0x28 (Extended packet ID 16bit value)

Data[1] = 0x00

Checksum = 0x2A (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE:

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (BIST passed) 0x01 (BIST failed)

Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.42 GetInitFromParallelFlashFail (0x0029)

As part of system power on, the user stored default settings will be loaded from parallel flash. This packet returns the result of initialization from flash.

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x29 (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x2B (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

### **RESPONSE PACKET STRUCTURE:**

| CMD1 = 0x05 (READ_RESP)                                 |  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|--|

| CMD2 = 0xAA                                             |  |  |  |  |  |

| CMD3 = 0x00                                             |  |  |  |  |  |

| CMD4 = 0x00 (only packet of transfer)                   |  |  |  |  |  |

| $Len_LSB = 0x03$                                        |  |  |  |  |  |

| $Len_MSB = 0x00$                                        |  |  |  |  |  |

| Data[0] = 0x00 (request processed successfully)         |  |  |  |  |  |

| Data[1] = 0x00 (request processed successfully)         |  |  |  |  |  |

| // Parallel flash initialization status                 |  |  |  |  |  |

| Data[2] = 0x00 (Success)                                |  |  |  |  |  |

| 0x01 (Failed for unknown reason)                        |  |  |  |  |  |

| 0x02 (No flash init attempt was made)                   |  |  |  |  |  |

| 0x03 (Fail mode - Parallel flash could not be accessed) |  |  |  |  |  |

| 0x04 (Fail mode - Invalid flash signature detected)     |  |  |  |  |  |

| 0x05 (Fail mode - Error in TI power up section)         |  |  |  |  |  |

| 0x06 (Fail mode - Error in user power up section)       |  |  |  |  |  |

| 0x07 (Fail mode - Error in requested solution)          |  |  |  |  |  |

| Checksum = 0xXX (sum of everything after CMD4)          |  |  |  |  |  |

#### Extended Packet Definition

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.43 GetOverallLEDlampLitState (0x002A)

Gets overall LED/Lamp lit state. Checks all channels on the LED driver to determine if all LEDs are lit (e.g. ready for operation).

PACKET STRUCTURE:

CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x2A (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x2C (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

```

CMD1 = 0x05 (READ_RESP)

CMD2 = 0xAA

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len_LSB = 0x03

Len_MSB = 0x00

Data[0] = 0x00 (request processed successfully)

Data[1] = 0x00 (request processed successfully)

Data[2] = 0x00 (LEDs Not lit)

0x01 (All LEDs lit)

Checksum = 0xXX (sum of everything after CMD4)

```

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.44 GetLEDdriverLitState (0x002B)

Gets the LED driver lit state by LED type. Checks for individual driver ready for operation.

PACKET STRUCTURE: CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03

```

Len_MSB = 0x00

Data[0] = 0x2B (Extended packet ID 16bit value)

Data[1] = 0x00

Data[2] = 0x00 (Red LED)

0x01 (Green LED)

0x02 (Blue LED)

0x03 (IR LED)

Checksum = 0xXX (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (LED Not lit) 0x01 (LED lit) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

## 6.45 GetOverallLEDdriverTempTimeoutState (0x002C)

Gets overall LED driver over-temperature-timeout state.

PACKET STRUCTURE: CMD1 = 0x04 (READ) CMD2 = 0xAA (Extended cmd packet) CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x02 Len\_MSB = 0x00 Data[0] = 0x2C (Extended packet ID 16bit value) Data[1] = 0x00 Checksum = 0x2E (sum of everything after CMD4)

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

**RESPONSE PACKET STRUCTURE:**

CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully) Data[2] = 0x00 (LEDs operating normally) 0x01 (Driver shutdown because of over temperature) Checksum = 0xXX (sum of everything after CMD4

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

### 6.46 GetLEDdriverTempTimeoutState (0x002D)

Gets individual LED driver over-temperature -timeout state.

PACKET STRUCTURE:

```

CMD1 = 0x04 (READ)

CMD2 = 0xAA (Extended cmd packet)

CMD3 = 0x00

CMD4 = 0x00 (only packet of transfer)

Len\_LSB = 0x03

Len\_MSB = 0x00

Data[0] = 0x2D (Extended packet ID 16bit value)

Data[1] = 0x00

Data[2] = 0x00 (Red LED)

0x01 (Green LED)

0x02 (Blue LED)

0x03 (IR LED)

Checksum = 0xXX (sum of everything after CMD4)

```

Upon receipt of the packet, the DLPC200 will send a response back to the host. If the packet was received and accepted the response would look like the following:

RESPONSE PACKET STRUCTURE: CMD1 = 0x05 (READ\_RESP) CMD2 = 0xAA CMD3 = 0x00 CMD4 = 0x00 (only packet of transfer) Len\_LSB = 0x03 Len\_MSB = 0x00 Data[0] = 0x00 (request processed successfully) Data[1] = 0x00 (request processed successfully)

Data[2] = 0x00 (LEDs operating normally)

0x01 (Driver shutdown because of over temperature) Checksum = 0xXX (sum of everything after CMD4)

If the command packet was corrupted in some way then the embedded application would set bits in Data[0] and Data[1] in the response packet to signify this error, see Section 6 for details. If that was the case, the response packet might only include Data[0] and Data[1] depending on which part of the command packet the error was located.

# 6.47 GetOverallLEDdriverStrobeTimeoutState (0x002E)

Get overall LED driver strobe-timeout state.

PACKET STRUCTURE: