# **DLPC350 Programmer's Guide**

# **User's Guide**

Literature Number: DLPU010G May 2013-Revised July 2018

# Contents

| Pref | ace    |                       |                                                    | 5   |

|------|--------|-----------------------|----------------------------------------------------|-----|

| 1    | Interf | face Pro              | otocol                                             | . 6 |

|      | 1.1    | I <sup>2</sup> C Inte | erface                                             | . 6 |

|      |        | 1.1.1                 | I <sup>2</sup> C Transaction Structure             | . 6 |

|      |        | 1.1.2                 | I <sup>2</sup> C Read Transaction Sequence         | . 7 |

|      |        | 1.1.3                 | I <sup>2</sup> C Write Transaction Sequence        | . 8 |

|      | 1.2    | USB Ir                | nterface                                           | . 9 |

|      |        | 1.2.1                 | USB Transaction Sequence                           | . 9 |

|      |        | 1.2.2                 | USB Read Transaction Sequence                      | . 9 |

|      |        | 1.2.3                 | USB Write Transaction Sequence                     | 10  |

| 2    | DLPC   | C350 Co               | ontrol Commands                                    | 11  |

|      | 2.1    | DLPC3                 | 350 Status Commands                                | 11  |

|      |        | 2.1.1                 | Hardware Status                                    | 11  |

|      |        | 2.1.2                 | System Status                                      | 12  |

|      |        | 2.1.3                 | Main Status                                        | 12  |

|      |        | 2.1.4                 | Retrieve Firmware Version                          | 13  |

|      |        | 2.1.5                 | Input Video Signal Detection Status                | 13  |

|      | 2.2    | DLPC3                 | 350 Programming Commands                           | 14  |

|      |        | 2.2.1                 | Enter Program Mode                                 | 14  |

|      | 2.3    | Chipse                | et Control Commands                                | 15  |

|      |        | 2.3.1                 | Chipset Configuration and Control Commands         | 15  |

|      |        | 2.3.2                 | Interface Configuration and Control                |     |

|      |        | 2.3.3                 | FPD-Link Interface Configuration and Control       | 18  |

|      |        | 2.3.4                 | Input Source Control                               | 20  |

|      |        | 2.3.5                 | Image Flip                                         | 24  |

|      |        | 2.3.6                 | Image Processing Control                           | 26  |

|      |        | 2.3.7                 | LED Driver Control                                 | 26  |

|      |        | 2.3.8                 | GPIO Control                                       | 28  |

|      |        | 2.3.9                 | Pulse Width Modulated (PWM) Control                | 30  |

|      |        | 2.3.10                | PWM Enable                                         | 31  |

|      |        | 2.3.11                | PWM Capture Configuration                          | 31  |

|      |        | 2.3.12                | PWM Capture Read                                   | 32  |

|      |        | 2.3.13                | I <sup>2</sup> C0 Master Port Control Command      | 32  |

|      |        | 2.3.14                | I <sup>2</sup> C0 Master Read/Write Error Response | 33  |

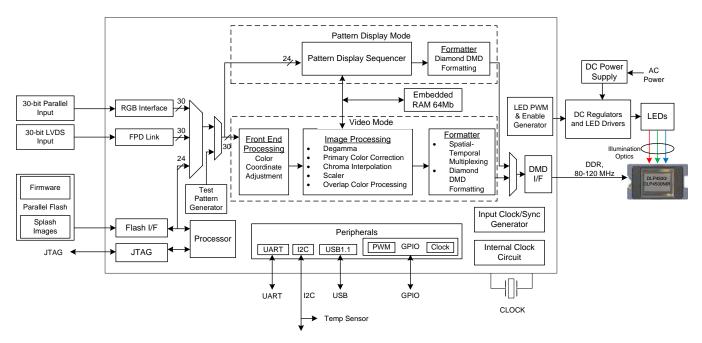

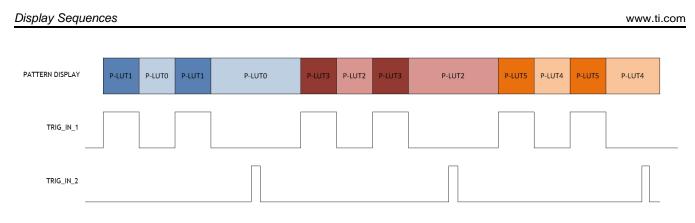

|      | 2.4    | Display               | y Sequences                                        | 34  |

|      |        | 2.4.1                 | Display Mode Selection Command                     | 37  |

|      |        | 2.4.2                 | Video Mode Commands                                | 38  |

|      |        | 2.4.3                 | Pattern Display Mode Commands                      | 39  |

| 3    | Powe   | er-Up, F              | Power-Down and Initialization Considerations       | 58  |

|      | 3.1    | Power                 | Up                                                 | 58  |

|      | 3.2    | Power                 | Down                                               | 58  |

|      | 3.3    | Power                 | -Up Auto-Initialization                            | 58  |

| 4    | Patte  | ern Disc              | blay Mode Examples                                 | 59  |

| -    | 4.1    | •                     | n Display Mode Example                             |     |

|      |        |                       |                                                    | -   |

| www. | ti.com     |                                                                                                                               |    |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------|----|

|      | 4.2        | Trigger Mode 0 Example                                                                                                        |    |

|      | 4.3<br>4.4 | Variable Exposure Pattern Sequence Example       6         Variable Exposure Video Streaming Pattern Sequence Example       6 |    |

| Α    |            | ster Quick Reference                                                                                                          |    |

| ~    | A.1        | I <sup>2</sup> C Register Quick Reference                                                                                     |    |

|      | A.2        | Command Guide                                                                                                                 | 57 |

|      | A.3        | DLPC350 Programming Commands                                                                                                  | ;9 |

|      |            | A.3.1 Read Control                                                                                                            | ;9 |

|      |            | A.3.2 Exit Program Mode 7                                                                                                     | 0  |

|      |            | A.3.3 Start Address                                                                                                           |    |

|      |            | A.3.4 Erase Sector                                                                                                            | '1 |

|      |            | A.3.5 Download Data Size 7                                                                                                    | '1 |

|      |            | A.3.6 Download Data                                                                                                           | '1 |

|      |            | A.3.7 Calculate Checksum                                                                                                      | '1 |

| Revi | sion H     | istory7                                                                                                                       | 3  |

3

# List of Figures

| 1-1.  | I <sup>2</sup> C Read Register Sequence                   | 8  |

|-------|-----------------------------------------------------------|----|

| 1-2.  | I <sup>2</sup> C Write Register Sequence                  | 8  |

| 1-3.  | USB HID Protocol                                          | 9  |

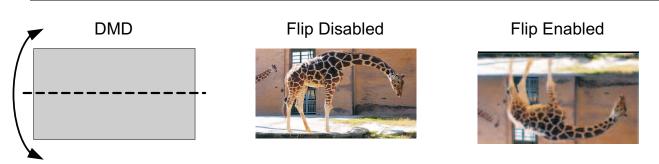

| 2-1.  | Image Long-Axis Flip Example                              | 25 |

| 2-2.  | Image Short-Axis Flip Example                             | 25 |

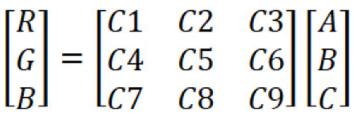

| 2-3.  | CSC Matrix                                                | 26 |

| 2-4.  | DLPC350 Functional Block Diagram                          | 35 |

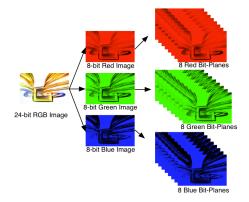

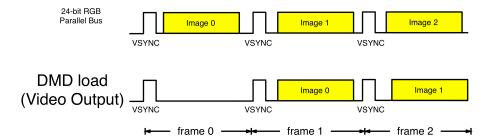

| 2-5.  | Bit-Planes of a 24-Bit RGB Image                          | 36 |

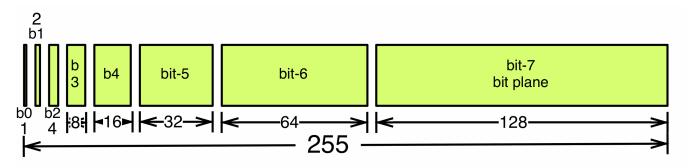

| 2-6.  | Bit Partition in a Frame for an 8-Bit Monochrome Image    |    |

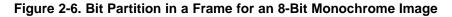

| 2-7.  | DLP4500 Frame Buffer                                      | 37 |

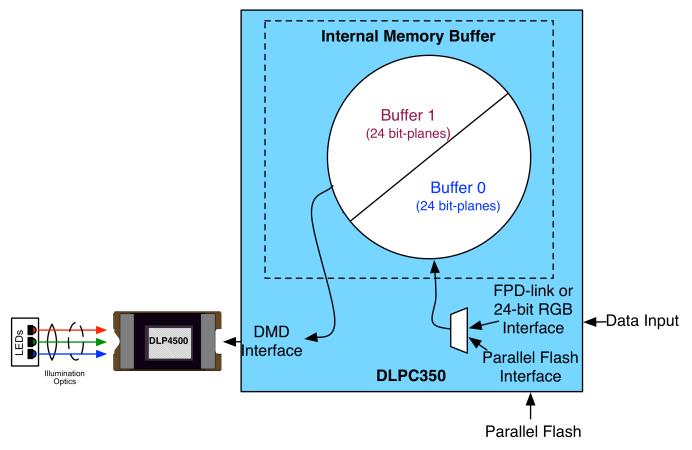

| 2-8.  | Frame Delay Between RGB Input and Video Output            | 37 |

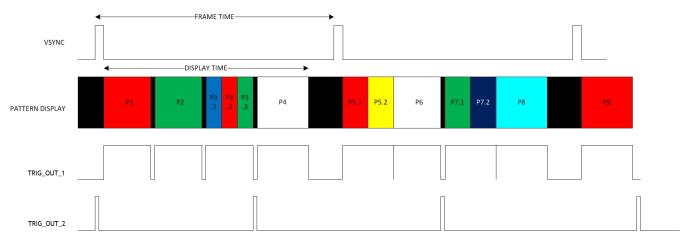

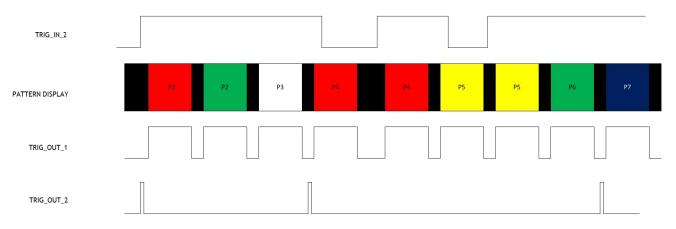

| 2-9.  | Trigger Mode 0 Timing Diagram Example                     | 41 |

| 2-10. | Trigger Mode 1 Timing Diagram Example                     | 41 |

| 2-11. | Trigger Mode 2 Timing Diagram Example                     | 42 |

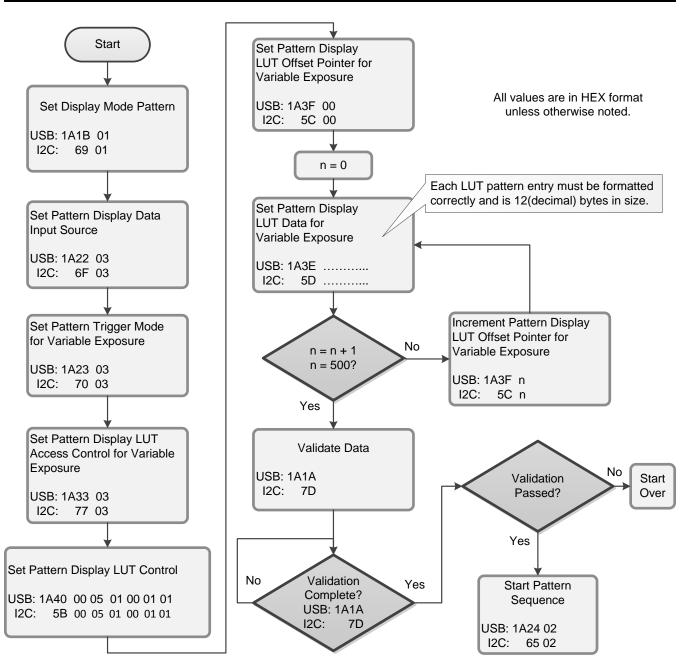

| 2-12. | Flowchart Example for Programming 1280 Variable Exposures | 56 |

|       |                                                           |    |

# **Read This First**

#### **About This Manual**

This document specifies the command and control interface to the DLP4500 and DLP4500NIR chipsets. The document defines all applicable commands, default settings, and control register bit definitions to communicate with the DLP4500 and DLP4500NIR chipsets.

#### **Related Documents from Texas Instruments**

- DLPC350 Data Sheet: DLP® Digital Controller for DLP4500 and DLP4500NIR DMDs, DLPS029

- DLP4500 Data Sheet: DLP4500 0.45 WXGA DMD, DLPS028

- DLP4500NIR Data Sheet: DLP4500NIR 0.45 WXGA Near-Infrared DMD, DLPS032

- DLPC350 Configuration and Support Firmware, DLPR350

#### If You Need Assistance

See the DLP LightCrafter<sup>™</sup> 4500 Development Platform Forum.

#### Trademarks

LightCrafter, E2E are trademarks of Texas Instruments.

DLP is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

5

# Interface Protocol

This chapter describes the interface protocol between the DLPC350 and a host processor. The DLPC350 supports two host interface protocols:  $I^2C$  and USB 1.1 slave interfaces.

#### 1.1 I<sup>2</sup>C Interface

The DLPC350 controller uses the I<sup>2</sup>C protocol to exchange commands and data with a host processor. The I<sup>2</sup>C protocol is a two-wire serial data bus that conforms to the NXP I<sup>2</sup>C specification, up to 400 kHz(See application note SLVA689 about optimizing I<sup>2</sup>C bus speed). One wire (SCL) serves as a serial clock, while the second wire (SDA) serves as serial data. Several different devices can be connected together in an I<sup>2</sup>C bus. Each device is software addressable by a unique address. Communication between devices occurs in a simple master-to-slave relationship.

#### 1.1.1 *fC Transaction Structure*

All I<sup>2</sup>C transactions are composed of a number of bytes, combined in the following order:

#### START Condition, Slave Address Byte + R/W Bit, Subaddress Byte, N-Data Bytes, STOP Condition

where N in "N-Data Bytes" varies based on the subaddress.

#### 1.1.1.1 I<sup>2</sup>C START Condition

All I<sup>2</sup>C transactions begin with a START condition. A START condition is defined by a high-to-low transition on the SDA line, while the SCL line is high.

#### 1.1.1.2 DLPC350 I<sup>2</sup>C Slave Address

The DLPC350 offers two different 7-bit I<sup>2</sup>C slave addresses based on the power-up state of the I2C\_ADDR\_SEL pin. If the I2C\_ADDR\_SEL pin is low, then the DLPC350 slave address is 0x1A. If the I2C\_ADDR\_SEL pin is high, then the DLPC350 slave address is 0x1D ( Fixed binary/hex mislabel in Section 2.4.3.4.1).

#### Table 1-1. I<sup>2</sup>C Slave Address

| PIN          | STATE DLPC350 7-BIT I <sup>2</sup> C |      |

|--------------|--------------------------------------|------|

| I2C_ADDR_SEL | Low 0x1A                             |      |

|              | High                                 | 0x1D |

The first 8-bit I2C packet includes the 7-bit slave address followed by a read/write bit. A read command to the DLPC350 concatenates the slave address with a 1. A write command to the DLPC350 concatenates the slave address with a 0. Thus, when I2C\_ADDR\_SEL is low, the first byte packet of an I<sup>2</sup>C command to the DLPC350 is 0x34 for write and 0x35 for read. When I2C\_ADDR\_SEL is high, the first byte packet of an I<sup>2</sup>C command is 0x3A for write and 0x3B for read ( Fixed example in Section 4.4).

#### Table 1-2. First 8-Bit I2C Packet

| 7-BIT I <sup>2</sup> C SLAVE ADDRESS | <b>READ/WRITE BIT</b> | FIRST 8-BIT I <sup>2</sup> C PACKET | TRANSACTION |

|--------------------------------------|-----------------------|-------------------------------------|-------------|

| 0x1A                                 | 0                     | 0x34                                | Write       |

| 0x1A                                 | 1                     | 0x35                                | Read        |

|                                      |                | · · · · · ·                         |             |

|--------------------------------------|----------------|-------------------------------------|-------------|

| 7-BIT I <sup>2</sup> C SLAVE ADDRESS | READ/WRITE BIT | FIRST 8-BIT I <sup>2</sup> C PACKET | TRANSACTION |

| 0x1D                                 | 0              | 0x3A                                | Write       |

| 0x1D                                 | 1              | 0x3B                                | Read        |

#### Table 1-2. First 8-Bit I2C Packet (continued)

#### 1.1.1.3 DLPC350 I<sup>2</sup>C Subaddress and Data Bytes

The DLPC350 subaddress corresponds to the byte address of the DLPC350 registers shown in Appendix A. Each register address requires a certain number of data bytes, typically four. Thus, a register address is followed by variable length data. These bytes contain the value read or written into this register, with the most significant byte first.

The DLPC350 subaddress contains a read/write bit in the most significant bit position. For read functions, bit 7 is set to 0. For write functions, bit 7 is set to 1. As an example, to read from register 0x06 in the DLPC350, the most significant bit is cleared, resulting in the read subaddress 0x06. To write to register 0x06 in the DLPC350, the most significant bit must be set, resulting in the write subaddress 0x86 ( Fixed binary/hex mislabel in Section 2.4.3.4.2).

#### Table 1-3. Read/Write Subaddressing Example With Register 0x06

| TRANSACTION | SUBADDRESS | DATA                             |

|-------------|------------|----------------------------------|

| Write       | 0x86       | Byte (N-1), Byte (N-2), , Byte 0 |

| Read        | 0x06       |                                  |

#### 1.1.1.4 I<sup>2</sup>C STOP Condition

All I<sup>2</sup>C transactions end with a STOP condition. A STOP condition is defined by a low-to-high transition on the SDA line while the SCL line is high.

#### 1.1.2 **PC Read Transaction Sequence**

To issue a command to read a DLPC350 value, the host must perform the following steps:

- 1. Host sends a START condition ( shown as S in Figure 1-1) followed by the DLPC350 address with the I<sup>2</sup>C read/write bit cleared (0x34 or 0x3A).

- 2. Host sends a subaddress byte that contains the command of the desired DLPC350 function.

- 3. Host sends a STOP (shown as P in Figure 1-1) condition.

- 4. Host sends another I<sup>2</sup>C START condition followed by the DLPC350 address with the I<sup>2</sup>C read/write bit set (0x35 or 0x3B).

- Host reads a status byte and checks that bit zero is set. If bit zero is not set, the read transaction repeats until bit zero is set. If bit one is also set, an error occurred. Successful command requests only have bit zero set.

- 6. Host reads the required bytes for each command.

- 7. Host issues a STOP condition to terminate the command read access.

#### 1.1.2.1 Example Read Transaction Sequence

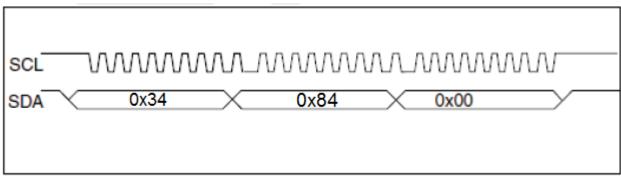

An example of a host reading DLPC350's register 4h whose contents are 00h, shown in Figure 1-1, would follow this sequence:

S 34 04 P S 35 01 00 P

7

| fC Interface www   | .ti.com |

|--------------------|---------|

| SDA 0x34 0x04      |         |

|                    |         |

| SDA 0x35 0x01 0x00 | _       |

Figure 1-1. I<sup>2</sup>C Read Register Sequence

# 1.1.3 **PC Write Transaction Sequence**

To issue a command to set a DLPC350 value, the host must perform the following steps:

- 1. Host sends a START condition ( shown as S in Figure 1-2) followed by the DLPC350 address with the I<sup>2</sup>C read/write bit cleared (0x34 or 0x3A).

- 2. Host sends a subaddress byte that contains the command of the desired DLPC350 function with the DLPC350 read/write bit set.

- **NOTE:** When in programming mode (see Section A.3 DLPC350 Programming Commands), the read/write bit must not be set for the write transactions.

- 3. Host sends the required bytes for the desired DLPC350 function.

- 4. Host issues a STOP condition ( shown as P in Figure 1-2) to terminate the command write access.

- (Optional) Read status byte with I<sup>2</sup>C read/write bit set (0x35 or 0x3B). If bit zero of the status byte is not set, the read transaction repeats until bit zero is set. If bit one is also set, an error occurred. Successful command requests only have bit zero set.

#### 1.1.3.1 Example Write Transaction Sequence

An example of a host writing DLPC350's register 4h with the content 00h, shown in Figure 1-2, would follow this sequence:

S 34 84 00 P

8

EXAS

**FRUMENTS**

#### 1.2 USB Interface

The DLPC350 controller supports the USB 1.1 human interface device (HID) to exchange commands and data with a host processor. The USB commands are variable length data packets that are sent with the least significant byte first. The DLPC350 offers two different string descriptors for USB enumeration based on whether the I2C\_ADDR\_SEL pin is high or low. The two strings are 'L', 'C', 'R', '2' or alternatively 'L', 'C', 'R', '3'. The USB Vendor ID (VID) is 0x0451 and the Product ID (PID) is 0x6401.

# 1.2.1 USB Transaction Sequence

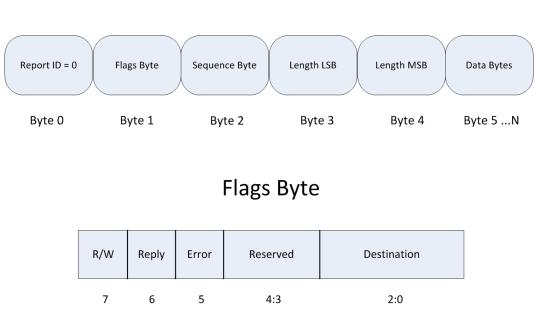

Figure 1-3 shows the structure of the USB 1.1 HID protocol.

**USB** Transaction Sequence

Figure 1-3. USB HID Protocol

# 1.2.2 USB Read Transaction Sequence

To issue a command to request a DLPC350 value, the host must perform the following steps:

- 1. Host sends the report ID byte, which is set to 0.

- 2. Host sends the Flags byte, where:

- Bits 2:0 are set to 0x0 for regular DLPC350 operation, and is set to 0x7 for debugging assistance

- Bit 6 is set to 0x1 which indiciates that the host requires a reply from the device

- Bit 7 is set to 0x1 which indicates a read transaction

- 3. Host sends the sequence byte. When a single command is more than 64 bytes, the command is sent as multiple USB packets and the sequence byte numbers the packets so the device can assemble them in the right sequence. In other cases, this value is irrelevant and generally set to 0.

- 4. Host sends two bytes with the length of the data packet. This length denotes the number of data bytes in the packet and excludes the number of bytes in steps 1 through 4. It denotes the total number of bytes sent in steps 5 (command bytes) and 6 (data bytes).

- 5. Host sends two subcommand bytes: CMD2 and CMD3.

- 6. Host sends data appropriate to command.

- 7. After completion of this command, DLPC350 responds with a packet that includes:

- A. Byte with the command requested by the host (the matching sequence byte)

USB Interface

USB Interface

- B. Length of the data packet

- C. Requested data

### 1.2.3 USB Write Transaction Sequence

To issue a command to set a DLPC350 value, the host must perform the following steps:

- 1. Host sends the report ID byte, which is set to 0.

- 2. Host sends the flags byte, where

- Bits 2:0 are set to 0x0 for regular DLPC350 operation, and is set to 0x7 for debugging assistance

- Bit 6 is set to 0x1 to indicate the host requires a reply from the device. This bit must be set for write transactions only if an acknowledgment or reply is required, which is not typical. For multi-packet transactions, bit 6 must not be set to 0x1 for intermediate packets

- Bit 7 is set to 0x1 to indicate a read transaction

- 3. Host sends the sequence byte. When a single command is more than 64 bytes, the command is sent as multiple USB packets and the sequence byte numbers the packets so the device can assemble them in the right sequence. In other cases, this value is irrelevant and generally set to 0.

- 4. Host sends two bytes with the length of the data packet. This length denotes the number of data bytes in the packet and excludes the number of bytes in steps 1 through 4. It denotes the total number of bytes sent in steps 5 (command bytes) and 6 (data bytes).

- 5. Host sends two subcommand bytes: CMD2 and CMD3.

- 6. Host sends data appropriate to command.

- 7. After completion of this command, DLPC350 responds with a packet that includes a byte with the command requested by the host. This occurs only if bit 6 is set in the flags byte.

# **DLPC350 Control Commands**

The DLPC350 has two operational modes: normal mode and programming mode. Section A.3 shows the programming mode commands. Normal mode commands do not work while in program mode. This chapter lists the normal mode DLPC350 control commands.

The following sections list the supported control commands of the DLPC350. In the *Type* column, 'WR' type is a writeable field through  $I^2C$  or USB write transactions. Data is read through  $I^2C$  or USB read transactions for 'WR' type bits. Type *r* is read-only. Write transactions to read-only fields are ignored.

The *Reset* column in all of the following command tables is the default value after power up. These values may be overwritten after power up.

- **NOTE:** Reserved bits and registers. When writing to valid command bit fields, all bits marked as unused or reserved must be set to 0, unless otherwise noted.

- **NOTE:** Momentary Image Corruption During Command Writes. Certain commands may cause brief visual artifacts in the display image under some circumstances. Command data values may always be read without impacting displayed image. To avoid momentary image corruption due to a command, disable the LEDs prior to the command write, then reenable the LEDs after all commands are issued.

NOTE: Writing or reading from undocumented registers is NOT recommended.

#### 2.1 DLPC350 Status Commands

The DLPC350 has the following set of status commands:

Hardware Status System Status Main Status Retrieve Firmware Version Input Video Signal Detection Status

#### 2.1.1 Hardware Status

(**I**<sup>2</sup>**C**: 0x20)

(**USB**: CMD2: 0x1A, CMD3: 0x0A)

The Hardware Status command provides status information on the sequencer of the DLPC350, DMD controller, and initialization.

| BYTE | BITS | DESCRIPTION                                                                         | RESET    | TYPE |

|------|------|-------------------------------------------------------------------------------------|----------|------|

|      |      | Internal Initialization                                                             | b1       | R    |

|      | 0    | 0 = Error                                                                           |          |      |

|      |      | 1 = Successful                                                                      |          |      |

|      | 1    | Reserved                                                                            | b0       | R    |

|      |      | DMD Reset Controller Error                                                          |          |      |

|      | 2    | 0 = No error has occurred                                                           | b0       | R    |

|      | -    | 1 = Multiple overlapping bias or reset operations are accessing the same DMD block. | U        |      |

|      |      | Forced Swap Error                                                                   | b0       | R    |

| 0    | 3    | 0 = No error has occurred.                                                          |          |      |

|      |      | 1 = Forced Swap Error occurred.                                                     |          |      |

|      | 4    | Reserved                                                                            | b0       | R    |

|      | 5    | Reserved                                                                            | b0       | R    |

|      |      | Sequencer Abort Status Flag                                                         |          |      |

|      | 6    | 0 = No error has occurred                                                           | b0<br>b0 | R    |

|      |      | 1 = Sequencer has detected an error condition that caused an abort                  |          |      |

|      |      | Sequencer Error                                                                     |          |      |

|      | 7    | 0 = No error has occurred.                                                          |          | R    |

|      |      | 1 = Sequencer detected an error.                                                    |          |      |

**NOTE:** Any error condition indicates a fault condition and must be corrected.

#### 2.1.2 System Status

(**I**<sup>2</sup>**C**: 0x21)

(USB: CMD2: 0x1A, CMD3: 0x0B)

The System Status command provides DLPC350 status on internal memory tests.

Table 2-2. System Status Register

| BYTE | BITS | DESCRIPTION                     | RESET | TYPE |

|------|------|---------------------------------|-------|------|

|      | 0    | Internal Memory Test            | b1    | R    |

| 0    |      | 0 = Internal Memory Test failed |       |      |

| 0    |      | 1 = Internal Memory Test passed |       |      |

|      | 1:7  | Reserved                        | b0    | R    |

#### 2.1.3 Main Status

(**I**<sup>2</sup>**C**: 0x22)

(USB: CMD2: 0x1A, CMD3: 0x0C)

The Main Status command shows the status of DMD park and DLPC350 sequencer, frame buffer, and gamma correction.

#### Table 2-3. Main Status Register

| BITS | BITS | DESCRIPTION                         | RESET | TYPE |

|------|------|-------------------------------------|-------|------|

|      |      | DMD Park Status                     |       | R    |

|      | 0    | 0 = DMD micromirrors are not parked | b0    |      |

|      |      | 1 = DMD micromirrors are parked     |       |      |

|      |      | Sequencer Run Flag                  |       |      |

|      | 1    | 0 = Sequencer is stopped            | b0    | R    |

|      |      | 1 = Sequencer is running normally   | 1     |      |

| 0    | 2    | Frame Buffer Swap Flag              |       |      |

|      |      | 0 = Frame buffer is not frozen      | b0    | R    |

|      |      | 1 = Frame buffer is frozen          |       |      |

|      |      | Gamma Correction Function Enable    |       |      |

|      | 3    | 0 = Gamma correction is disabled    | b0    | R    |

|      |      | 1 = Gamma correction is enabled     | 1     |      |

|      | 4:7  | Reserved                            | b0    | R    |

# 2.1.4 Retrieve Firmware Version

(**I**<sup>2</sup>**C**: 0x11)

(USB: CMD2: 0x02, CMD3: 0x05)

This command (**supported in firmware version 2.0.0 and newer**) reads the version information of the DLPC350 firmware.

#### Table 2-4. Get Version Command

| BYTE               | BITS  | DESCRIPTION                            | RESET | TYPE |  |

|--------------------|-------|----------------------------------------|-------|------|--|

|                    |       | Application software revision:         |       |      |  |

| 2.0                | 15:0  | Application software patch number      | x0    | R    |  |

| 3:0<br>7:4<br>11:8 | 23:16 | Application software minor revision    | ×0    | ĸ    |  |

|                    | 31:24 | Application software major revision    |       |      |  |

|                    |       | API software revision:                 |       |      |  |

| 7:4                | 15:0  | API patch number                       |       | R    |  |

|                    | 23:16 | API minor revision                     | x0    | ĸ    |  |

|                    | 31:24 | API major revision                     |       |      |  |

|                    |       | Software configuration revision:       |       |      |  |

| 11.0               | 15:0  | Software configuration patch number    |       | R    |  |

| 11.0               | 23:16 | Software configuration minor revision  | x0    | ĸ    |  |

|                    | 31:24 | Software configuration major revision  |       |      |  |

|                    |       | Sequencer configuration revision:      |       |      |  |

| 45.40              | 15:0  | Sequencer configuration patch number   |       | Р    |  |

| 15:12              | 23:16 | Sequencer configuration minor revision | x0    | R    |  |

|                    | 31:24 | Sequencer configuration major revision |       |      |  |

#### 2.1.5 Input Video Signal Detection Status

(**I**<sup>2</sup>**C**: 0x01)

(**USB**: 0x04, CMD2: 0x07, CMD3: 0x1C)

#### DLPC350 Programming Commands

www.ti.com

When this command (**supported in firmware version 2.0.0 and newer**) is executed, the DLPC350 controller returns the Input Video Signal timing information based the Video Port Selection made through I2C command 0x00 or USB commands 0x1A00. This command is applicable for RGB Parallel Interface and FPD-link interface. On receiving the command the controller monitors the signal for ~ 200 ms before reporting the signal status. This command is used as a debugging aid to detect if the controller reads the resolution correctly, especially in the Pattern Display Mode where the resolution must match the native resolution of  $912 \times 1140$  pixels.

| BYTE  | BITS |                     | DESCRIPTION                                                          | RESET | TYPE |

|-------|------|---------------------|----------------------------------------------------------------------|-------|------|

|       |      | Signal Detec        | tion Status                                                          |       |      |

|       |      | 0x00                | Stopped – Controller is not processing the input video signal        | x0    | R    |

| 0     | 7:0  | 0x01                | Processing – Controller BUSY detecting the input video signal        | x0    | R    |

|       |      | 0x02                | Detected – Controller is successfully processed the input source     | x0    | R    |

|       |      | 0x03                | Lock Failed – Controller couldn't failed to process the video signal | x0    | R    |

| 2:1   | 15:0 | Horizontal res      | solution                                                             | x0    | R    |

| 4:3   | 15:0 | Vertical resolution | ution                                                                | x0    | R    |

| 5     | 7:0  | Reserved 0x0        | 00                                                                   | x0    | R    |

|       |      | HSYNC Pola          | rity                                                                 |       |      |

| 6     | 7:0  | 0x00 - Negat        | ive                                                                  | x0    | R    |

|       |      | 0x01 – Positiv      | ve                                                                   |       |      |

|       |      | VSYNC Polarity      |                                                                      |       |      |

| 7     | 7:0  | 0x00 - Negat        | ive                                                                  | x0    | R    |

|       |      | 0x01 – Positiv      | ve                                                                   |       |      |

| 11:8  | 31:0 | Pixel clock in      | (100 × KHz)                                                          | x0    | R    |

| 13:12 | 15:0 | Horizontal fre      | quency (100 × KHz)                                                   | x0    | R    |

| 15:14 | 15:0 | Vertical frequ      | ency (100 × Hz)                                                      | x0    | R    |

| 17:16 | 15:0 | Total pixels p      | er line                                                              | x0    | R    |

| 19:18 | 15:0 | Total lines pe      | r frame                                                              | x0    | R    |

| 21:20 | 15:0 | Active pixels       | Active pixels per line                                               |       | R    |

| 23:22 | 15:0 | Active lines p      | er frame                                                             | x0    | R    |

| 25:24 | 15:0 | First pixel (be     | ginning of active pixel in the line)                                 | x0    | R    |

| 27:26 | 15:0 | First Line (be      | ginning of active line in the frame)                                 | x0    | R    |

| Table 2-5. Input Vid | leo Signal detection | Status Read Command |

|----------------------|----------------------|---------------------|

|----------------------|----------------------|---------------------|

#### 2.2 DLPC350 Programming Commands

The programming commands download a new firmware image into flash memory. This is accomplished with I<sup>2</sup>C or USB communication. When operating in normal mode, an enter program mode command can be issued, which exits normal mode and enters program mode. When in program mode, the user must issue the proper exit program mode command to return to normal mode. Normal mode commands do not work while in program mode. See Section A.3 for the list of program mode commands.

#### 2.2.1 Enter Program Mode

(**I**<sup>2</sup>**C**: 0x30)

(**USB**: CMD2: 0x30, CMD3: 0x01)

If the main application receives this command while in normal mode, the controller enters program mode. When called, the main application powers off the illumination system, parks the DMD, and jumps to the boot loader application. If the boot loader receives this command, then the command has no effect.

#### Table 2-6. Enter Program Mode Command

| BYTE | BITS | DESCRIPTION                                  | RESET | TYPE |

|------|------|----------------------------------------------|-------|------|

|      | 0    | Program Mode                                 | d0    | w    |

| 0    | 0    | 1 = Enter Program Mode – Jump to boot loader |       |      |

|      | 7:1  | Reserved                                     |       |      |

# 2.3 Chipset Control Commands

The DLPC350 has the following set of control commands:

Chipset configuration and control

Interface configuration and control

Input source control

Image rotation and flip control

Image processing control

LED driver control

Sleep mode control

**GPIO** control

I<sup>2</sup>C control commands are accepted in any order, except when special sequencing is required (for example, setting up the flash). Each control command is validated for subaddress and parameter errors as the command is received. Commands failing validation are ignored. On power up, it is required to wait for DLPC350 to complete initialization before sending the device any I<sup>2</sup>C or USB transactions. The INIT\_DONE pin signals when initialization is complete (see the DLPC350 data sheet, DLPS029).

### 2.3.1 Chipset Configuration and Control Commands

The Chipset and Configuration Control commands manage software reset, power down modes, buffer freeze, and image curtain display.

#### 2.3.1.1 Software Reset

(**I**<sup>2</sup>**C**: 0x13)

(USB: CMD2: 0x08, CMD3: 0x02)

This command issues a software reset to the DLPC350, regardless of the argument that is sent. This command provides a back-up recovery mechanism.

| Table 2-7. So | ftware Reset | Command |

|---------------|--------------|---------|

|---------------|--------------|---------|

| BYTE | BITS | DESCRIPTION                                                           | RESET | TYPE |

|------|------|-----------------------------------------------------------------------|-------|------|

| 0    | 0    | Software Reset. A set or reset of this bit performs a software reset: | 40    | W    |

|      | 0    | 0 or 1 – Perform a software reset                                     | - d0  | vv   |

#### 2.3.1.2 DMD Park/Unpark

(**I**<sup>2</sup>**C**: 0x14)

(**USB**: CMD2: 0x06, CMD3: 0x09)

This command is used to park or unpark the DMD, whenever system is idle user can send this command to park the DMD. By using this command, it will not alter the overall system configuration. For example, if the DLPC350 controller is configured in Pattern Mode, upon sending this command to park the DMD, user need not reconfigure the system after DMD unpark, this command not change the system configuration status.

Chipset Control Commands

www.ti.com

#### Table 2-8. DMD Park/Unpark Command

| BYTE | BITS | DESCRIPTION                        | RESET | TYPE |

|------|------|------------------------------------|-------|------|

| 0    | 0    | 0x00 – DMD un-park 0x01 – DMD park | d0    | WR   |

#### 2.3.1.3 Power Control

(**I**<sup>2</sup>**C**: 0x07)

(**USB**: CMD2: 0x02, CMD3: 0x00)

The power control places the DLPC350 in a low-power state and powers down the DMD interface. Standby mode must only be enabled after all data for the last frame is transferred to the DLPC350. Standby mode must be disabled prior to sending any new data.

| BYTE | BITS | DESCRIPTION                                                                           | RESET | TYPE |

|------|------|---------------------------------------------------------------------------------------|-------|------|

|      |      | Power control                                                                         |       |      |

|      | 0    | 0 = Normal operation. The selected external source is displayed                       | d0    | WR   |

| 0    | Ŭ    | 1 = Standby mode. Places DLPC350 in low-power state and powers down the DMD interface | uo    |      |

|      | 7:1  | Reserved                                                                              | d0    | R    |

#### 2.3.1.4 Buffer Controls

The Buffer Control commands allow buffer swaps, provides the current buffer pointer, and freezes the buffer.

#### 2.3.1.4.1 Force Buffer Swap

(**I**<sup>2</sup>**C**: 0x71)

(USB: CMD2: 0x1A, CMD3: 0x26)

The Force Buffer Swap command switches between the two internal memory buffers by swapping the read and write pointers. After a buffer swap, the 24 bit-plane buffer that streams data to the DMD is now used for input, while the previous 24 bit-plane input buffer now streams data to the DMD. The buffer must be frozen before executing this command.

| BYTE | BITS | DESCRIPTION                                          | RESET | TYPE |

|------|------|------------------------------------------------------|-------|------|

|      |      | Buffer swap                                          |       |      |

| 0    | 0    | 1 - Swap internal memory buffer pointers             | d0 V  | WR   |

| 0    |      | 0 - No change to the internal memory buffer pointers |       |      |

|      | 7:1  | Reserved                                             | d0    | R    |

#### 2.3.1.4.2 Display Buffer Freeze

(**I**<sup>2</sup>**C**: 0x7C)

(**USB**: CMD2: 0x10, CMD3: 0x0A)

The Display Buffer Freeze command disables swapping the memory buffers. When reconfiguring the chipset through a series of commands that change the input source or operating mode, TI recommends the Display Buffer Swap Freeze command to prevent temporary artifacts from reaching the display. When the display buffer is frozen, the last image streamed to the DMD continues to display.

#### Table 2-11. Display Buffer Freeze Command

| BYTE | BITS | DESCRIPTION                                         | RESET | TYPE |

|------|------|-----------------------------------------------------|-------|------|

| 0    |      | Display buffer swap freeze                          | d1    | WR   |

|      | 0    | 0 - Enable buffer swapping                          |       |      |

|      |      | 1 - Disable buffer swapping (freeze display buffer) |       |      |

#### 2.3.1.4.3 Buffer Write Disable

(**I**<sup>2</sup>**C**: 0x72)

(USB: CMD2: 0x1A, CMD3: 0x27)

The Buffer Write Disable command prevents the overwriting of the contents of the 48 bit-planes or two 24bit frame buffers of the internal memory buffer.

| BYTE | BITS                                                                                                                                                         | DESCRIPTION                                           | RESET | TYPE |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|------|

| 0    | Buffer write disable           0         1 = Disables writes to all the internal memory buffer           0 = Normal operation           7:1         Reserved | Buffer write disable                                  |       |      |

|      |                                                                                                                                                              | 1 = Disables writes to all the internal memory buffer | d0    | WR   |

|      |                                                                                                                                                              | 0 = Normal operation                                  |       |      |

|      |                                                                                                                                                              | Reserved                                              | d0    | R    |

#### 2.3.1.4.4 Current Read Buffer Pointer

(**I**<sup>2</sup>**C**: 0x73)

(**USB**: CMD2: 0x1A, CMD3: 0x28)

The Current Read Buffer Pointer command returns the pointer to the current internal memory buffer (this data is streamed to the DMD).

|  | Table 2-13. | Current | Buffer | Pointer | Command |

|--|-------------|---------|--------|---------|---------|

|--|-------------|---------|--------|---------|---------|

| BYTE | BITS                                                                                                                       | DESCRIPTION                             | RESET | TYPE |

|------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|------|

|      | Current read buffer pointer command                                                                                        |                                         |       |      |

| 0    | 0       1 = Buffer number 1 is streaming to DMD         0 = Buffer number 0 is streaming to DMD         7:1       Reserved | 1 = Buffer number 1 is streaming to DMD | d0    | WR   |

|      |                                                                                                                            | 0 = Buffer number 0 is streaming to DMD |       |      |

|      |                                                                                                                            | Reserved                                | d0    | R    |

#### 2.3.1.5 Display Curtain Control

(**I**<sup>2</sup>**C**: 0x06)

(**USB**: CMD2: 0x11, CMD3: 0x00)

This register provides image curtain control. When enabled and the input source is set to external video with no video source connected, a solid color field is displayed on the entire DMD display. The Display Curtain Control provides an alternate method of masking temporary source corruption from reaching the display due to on-the-fly reconfiguration. The register is useful for optical test and debug support.

| BYTE | BITS | DESCRIPTION                                     | RESET | TYPE |

|------|------|-------------------------------------------------|-------|------|

| 1:0  | 9:0  | Red color intensity in a scale from 0 to 1023   | x0    | WR   |

| 3:2  | 9:0  | Green color intensity in a scale from 0 to 1023 | x0    | WR   |

| 5:4  | 9:0  | Blue color intensity in a scale from 0 to 1023  | x0    | WR   |

Table 2-14. Display Curtain Control Command

# 2.3.2 Interface Configuration and Control

The Interface Configuration and Control manages the operation of the parallel and FPD-link interfaces.

# 2.3.2.1 Input Data Channel Swap

(**I**<sup>2</sup>**C**: 0x04)

(**USB**: CMD2: 0x1A, CMD3: 0x37)

The Input Data Channel Swap commands configure the specified input data port and map the data subchannels. The DLPC350 interprets channel A as green, channel B as red, and channel C as blue.

| BYTE | BITS | DESCRIPTION                                                              | RESET | TYPE |

|------|------|--------------------------------------------------------------------------|-------|------|

|      |      | Swap Parallel Interface Data Subchannel:                                 |       |      |

|      |      | 0 - ABC = ABC, No swapping of data subchannels                           |       |      |

|      |      | 1 - ABC = CAB, Data subchannels are right shifted and circularly rotated |       |      |

|      |      | 2 - ABC = BCA, Data subchannels are left shifted and circularly rotated  |       |      |

|      | 2:0  | 3 - ABC = ACB, Data subchannels B and C are swapped                      | x4    | WR   |

| 0    |      | 4 - ABC = BAC, Data subchannels A and B are swapped                      |       |      |

|      |      | 5 - ABC = CBA, Data subchannels A and C are swapped                      |       |      |

|      |      | 6 - Reserved                                                             |       |      |

|      |      | 7 - Reserved                                                             |       |      |

|      | 6:3  | Reserved                                                                 | b0    | R    |

|      |      | Specified Port                                                           |       |      |

|      | 7    | 0 - Parallel interface                                                   | b0    | WR   |

|      |      | 1 - FPD-link interface                                                   |       |      |

Table 2-15. Input Data Channel Swap Command

# 2.3.3 FPD-Link Interface Configuration and Control

The following commands are unique to the FPD-link interface.

# 2.3.3.1 FPD-Link Mode and Field Select

(**I**<sup>2</sup>**C**: 0x05)

(USB: CMD2: 0x1A, CMD3: 0x04)

The FPD-Link Mode and Field Select command configures the FPD-link pixel map, polarity, and signal select.

| BYTE | BITS | DESCRIPTION                                                                                     | RESET | TYPE |

|------|------|-------------------------------------------------------------------------------------------------|-------|------|

| 0    |      | Field signal select: <sup>(1)</sup>                                                             |       |      |

|      |      | 0 = Map FPD- link LVDS output from CONT1 onto field signal for FPD-link interface port (port 2) |       |      |

|      | 2:0  | 1 = Map FPD- link LVDS output from CONT2 onto field signal for FPD-link interface port (port 2) | x0    | WR   |

|      |      | 2 = Force 0 onto field signal for FPD-link interface port (port 2)                              |       |      |

|      |      | 3 = Reserved                                                                                    |       |      |

|      | 3    | Swap polarity                                                                                   | x1    | WR   |

|      | 5:4  | Reserved                                                                                        | x0    | R    |

|      |      | FPD-link pixel mapping mode (see Table 2-17) <sup>(2)</sup>                                     |       |      |

|      |      | 0 = Mode 1                                                                                      |       |      |

|      | 7:6  | 1 = Mode 2                                                                                      | x1    | WR   |

|      |      | 2 = Mode 3                                                                                      | 1     |      |

|      |      | 3 = Mode 4                                                                                      | 1     |      |

Table 2-16. FPD-Link Mode and Field Select Command

<sup>(1)</sup> See Table 2-17 for CONT1 and CONT2 mapping.

(2) Pixel mapping mode defines how the FPD-Link LVDS output pixels are mapped into DLPC350 FPD-link interface port (port 2). Table 2-16 lists the mapping of the LVDS parallel data output buses RDA(6:0), RDB(6:0), RDC(6:0), RDD(6:0), and RDE(6:0) into the 30-bit LVDS input port (Port 2:FPD-link interface port of the DLPC350).

| <b>Table 2-17</b> | . FPD-Link | Pixel | Mapping | Modes |

|-------------------|------------|-------|---------|-------|

|-------------------|------------|-------|---------|-------|

| PIXEL    | MODE1 | MODE2 | MODE3 | MODE4 |

|----------|-------|-------|-------|-------|

| Green[9] | RDB4  | RDD3  | RDE1  | RDB4  |

| Green[8] | RDB3  | RDD2  | RDE2  | RDB3  |

| Green[7] | RDB2  | RDB4  | RDD1  | RDB2  |

| Green[6] | RDB1  | RDB3  | RDD2  | RDB1  |

| Green[5] | RDB0  | RDB2  | RDB4  | RDB0  |

| Green[4] | RDA6  | RDB1  | RDB3  | RDA6  |

| Green[3] | RDD3  | RDB0  | RDB2  | 0     |

| Green[2] | RDD2  | RDA6  | RDB1  | 0     |

| Green[1] | RDE3  | RDE3  | RDB0  | 0     |

| Green[0] | RDE2  | RDE2  | RDA6  | 0     |

| Red[9]   | RDA5  | RDD1  | RDE1  | RDA5  |

| Red[8]   | RDA4  | RDD0  | RDE0  | RDA4  |

| Red[7]   | RDA3  | RDA5  | RDD1  | RDA3  |

| Red[6]   | RDA2  | RDA4  | RDD0  | RDA2  |

| Red[5]   | RDA1  | RDA3  | RDA5  | RDA1  |

| Red[4]   | RDA0  | RDA2  | RDA4  | RDA0  |

| Red[3]   | RDD1  | RDA1  | RDA3  | 0     |

| Red[2]   | RDD0  | RDA0  | RDA2  | 0     |

| Red[1]   | RDE1  | RDE1  | RDA1  | 0     |

| Red[0]   | RDE0  | RDE0  | RDA0  | 0     |

| Blue[9]  | RDC3  | RDD5  | RDE5  | RDC3  |

| Blue[8]  | RDC2  | RDD4  | RDE4  | RDC2  |

| Blue[7]  | RDC1  | RDC3  | RDD5  | RDC1  |

| Blue[6]  | RDC0  | RDC2  | RDD4  | RDC0  |

| Blue[5]  | RDB6  | RDC1  | RDC3  | RDB6  |

| Blue[4]  | RDB5  | RDC0  | RDC2  | RDB5  |

| Blue[3]  | RDD5  | RDB6  | RDC1  | 0     |

| Blue[2]  | RDD4  | RDB5  | RDC0  | 0     |

|         |       |       | · · · |       |

|---------|-------|-------|-------|-------|

| PIXEL   | MODE1 | MODE2 | MODE3 | MODE4 |

| Blue[1] | RDE5  | RDE5  | RDB6  | 0     |

| Blue[0] | RDE4  | RDE4  | RDB5  | 0     |

| DATA_EN | RDC6  | RDC6  | RDC6  | RDC6  |

| VSYNC   | RDC5  | RDC5  | RDC5  | RDC5  |

| HSYNC   | RDC4  | RDC4  | RDC4  | RDC4  |

| CONT1   | RDD6  | RDD6  | RDD6  | RDD6  |

| CONT2   | RDE6  | RDE6  | RDE6  | RDE6  |

#### Table 2-17. FPD-Link Pixel Mapping Modes (continued)

# 2.3.4 Input Source Control

The Input Source Selection determines the input source for the DLPC350 data display.

#### 2.3.4.1 Port Clock Select (for Parallel Port)

(**I**<sup>2</sup>**C**: 0x03)

(USB: CMD2: 0x1A, CMD3: 0x03)

This command selects the port 1 clock for the parallel interface. For the FPD-Link, the port clock is automatically set to port 2.

| BYTE | BITS | DESCRIPTION             | RESET | TYPE |

|------|------|-------------------------|-------|------|

|      |      | Select port input clock |       |      |

|      | 0.0  | 0: Port 1, clock A      | 0     |      |

| 0    | 2:0  | 1: Port 1, clock B      | x0    | WR   |

|      |      | 2: Port 1, clock C      |       |      |

|      | 7:3  | Reserved                | x0    | R    |

#### Table 2-18. Input Source Selection Command

#### 2.3.4.2 Input Source Selection

(**I**<sup>2</sup>**C**: 0x00)

(USB: CMD2: 0x1A, CMD3: 0x00)

The Input Source Selection command selects the input source that is displayed by the DLPC350: 30-bit parallel port, internal test pattern, flash memory, or FPD-link interface.

| BYTE | BITS | DESCRIPTION                                                                                               | RESET | TYPE |

|------|------|-----------------------------------------------------------------------------------------------------------|-------|------|

|      |      | Select the input source and interface mode:                                                               |       |      |

|      |      | 0 = Parallel interface with 8-bit, 16-bit, 20-bit, 24-bit, or 30-bit RGB or YCrCb data formats            |       |      |

|      | 2:0  | 1 = Internal test pattern; $I^2C$ command 0x11 selects the test pattern type.                             | x0    | WR   |

|      |      | 2 = Flash. Images are 24-bit single-frame, still images that are stored in flash and uploaded on command. |       |      |

|      |      | 3 = FPD-link interface                                                                                    |       |      |

| 0    |      | Parallel Interface bit depth                                                                              | ×1    |      |

| Ū    |      | 0 = 30 bits                                                                                               |       |      |

|      |      | 1 = 24 bits                                                                                               |       |      |

|      | 5:3  | 2 = 20 bits                                                                                               |       | WR   |

|      |      | 3 = 16 bits                                                                                               |       |      |

|      |      | 4 = 10 bits                                                                                               |       |      |

|      |      | 5 = 8 bits                                                                                                |       |      |

|      | 7:6  | Reserved                                                                                                  | x0    | R    |

### 2.3.4.3 Input Pixel Data Format

(**I**<sup>2</sup>**C**: 0x02)

(**USB**: CMD2: 0x1A, CMD3: 0x02)

The input pixel data format command defines the pixel data format input into the DLPC350.

| Table 2-20. | Input Pixel | Data | Format | Command |

|-------------|-------------|------|--------|---------|

|-------------|-------------|------|--------|---------|

| BYTE | BITS |                               | DESCI    | RIPTION            |                  |          | RESET | TYPE |

|------|------|-------------------------------|----------|--------------------|------------------|----------|-------|------|

|      |      | Select the pixel data format: | Su       | pported Pixel Form | nats vs Source T | уре      |       |      |

|      |      |                               | Parallel | Test Pattern       | Flash Image      | FPD-Link |       |      |

| 0    | 3:0  | 0 - RGB 4:4:4 (30 bit)        | Yes      | Yes                | Yes              | Yes      | d0    | WR   |

| 0    |      | 1 - YCrCb 4:4:4 (30 bit)      | Yes      | No                 | No               | No       |       |      |

|      |      | 2 - YCrCb 4:2:2               | Yes      | No                 | Yes              | No       |       |      |

|      | 7:6  | Reserved                      |          |                    |                  |          | x0    | R    |

#### 2.3.4.4 Internal Test Patterns Select

(**I**<sup>2</sup>**C**: 0x0A)

(USB: CMD2: 0x12, CMD3: 0x03)

When the internal test pattern is the selected input, the internal test patterns select defines the test pattern displayed on the screen. These test patterns are internally generated and injected into the beginning of the DLPC350 image processing path. Therefore, all image processing is performed on the test images. All command registers must be set up as if the test images are input from an RGB 8:8:8 external source. The resolution of the test pattern must be configured with the Input Display Resolutions commands. Frame rate must be configured with the frame rate commands.

| BYTE | BITS | DESCRIPTION                   | RESET | TYPE |

|------|------|-------------------------------|-------|------|

|      |      | Internal test pattern select: |       |      |

|      |      | 0x0 = Solid field             | -     |      |

|      |      | 0x1 = Horizontal ramp         | -     |      |

|      |      | 0x2 = Vertical ramp           | =     |      |

|      |      | 0x3 = Horizontal lines        | x8    |      |

|      | 0.0  | 0x4 = Diagonal lines          |       |      |

| 0    | 3:0  | 0x5 = Vertical lines          |       | WR   |

|      |      | 0x6 = Grid                    |       |      |

|      |      | 0x7 = Checkerboard            | -     |      |

|      |      | 0x8 = RGB ramp                | -     |      |

|      |      | 0x9 = Color bars              |       |      |

|      |      | 0xA = Step bars               |       |      |

|      | 7:4  | Reserved                      |       |      |

Table 2-21. Internal Test Patterns Select Command

#### 2.3.4.5 Internal Test Patterns Color Control

(**I**<sup>2</sup>**C**: 0x1A)

(USB: CMD2: 0x12, CMD3: 0x04)

When the internal test pattern is the selected input, the internal test patterns color control defines the colors of the test pattern displayed on the screen. These test patterns are internally generated and injected into the beginning of the DLPC350 image processing path. Therefore, all image processing is performed on the test images. All command registers must be set up as if the test images are input from an RGB 8:8:8 external source. The foreground color setting affects all test patterns. The background color setting affects test patterns that have a foreground and background component, such as horizontal lines, diagonal lines, vertical lines, grid, and checkerboard.

| BYTE | BITS | DESCRIPTION                                                | RESET | TYPE |

|------|------|------------------------------------------------------------|-------|------|

|      |      | Red Foreground Color intensity in a scale from 0 to 1023   |       |      |

| 1:0  | 9:0  | 0x0 = No Red Foreground color intensity                    | x3FF  | WR   |

| 1.0  | 9.0  | -                                                          | X3FF  | WK   |

|      |      | 0x3FF = Full Red Foreground color intensity                |       |      |

|      |      | Green Foreground Color intensity in a scale from 0 to 1023 |       |      |

| 3:2  | 9:0  | 0x0 = No Green Foreground color intensity                  | x3FF  | WR   |

| 3.2  | 9.0  | -                                                          | X3FF  | WK   |

|      |      | 0x3FF = Full Green Foreground color intensity              |       |      |

|      | 9:0  | Blue Foreground Color intensity in a scale from 0 to 1023  |       |      |

| 5:4  |      | 0x0 = No Blue Foreground color intensity                   | x3FF  | WR   |

| 5.4  | 9.0  | -                                                          | X3FF  | WK   |

|      |      | 0x3FF = Full Blue Foreground color intensity               |       |      |

|      |      | Red Background Color intensity in a scale from 0 to 1023   |       |      |

| 7:6  | 9:0  | 0x0 = No Red Background color intensity                    | x0    | WR   |

| 7.0  | 9.0  | -                                                          | 20    | WIN  |

|      |      | 0x3FF = Full Red Background color intensity                |       |      |

|      |      | Green Background Color intensity in a scale from 0 to 1023 |       |      |

| 9:8  | 9:0  | 0x0 = No Green Background color intensity                  | x0    | WR   |

| 9.0  | 9.0  | -                                                          | XU    | VVR  |

|      |      | 0x3FF = Full Green Background color intensity              |       |      |

Table 2-22. Internal Test Patterns Color Control Command

| BYTE  | BITS | DESCRIPTION                                               | RESET | TYPE |

|-------|------|-----------------------------------------------------------|-------|------|

|       | 9:0  | Blue Background Color intensity in a scale from 0 to 1023 |       |      |

| 11.10 |      | 0x0 = No Blue Background color intensity                  | ×0    |      |

| 11:10 |      | -                                                         | x0    | WR   |

|       |      | 0x3FF = Full Blue Background color intensity              |       |      |

#### Table 2-22. Internal Test Patterns Color Control Command (continued)

#### 2.3.4.6 Load Image

(**I**<sup>2</sup>**C**: 0x7F)

(USB: CMD2: 0x1A, CMD3: 0x39)

This command loads an image from flash memory and then performs a buffer swap to display the loaded image on the DMD.

| Table 2-23. | Load Image | e Command |

|-------------|------------|-----------|

|-------------|------------|-----------|

| BYTE | BITS | DESCRIPTION                                                                                                                          | RESET | TYPE |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 7:0  | Image Index. Loads the image at this index. Reading this back provides the index that was loaded most recently through this command. | x0    | WR   |

#### 2.3.4.7 Image Load Timing

(**I**<sup>2</sup>**C**: 0x61)

(**USB**: CMD2: 0x1A, CMD3: 0x3A)

When this command is executed, the system loads the image index shown in Section 2.3.4.6 and collects the amount of time that the image took to load. The busy status of the system is high until the images are loaded and the timing information is collected. This command cannot be executed while the system is already displaying patterns from flash.

#### Table 2-24. Image Load Timing Write Command

| BYTE | BITS | DESCRIPTION                                                  | RESET | TYPE |

|------|------|--------------------------------------------------------------|-------|------|

| 0    | 7:0  | Starting index of the image that requires timing information | x0    | W    |

| 1    | 7:0  | Number of images that require timing information             | x0    | W    |

The following data format is received when the load timing information is read back:

#### Table 2-25. Image Load Timing Read Command

| BYTE | BITS | DESCRIPTION                                                                        | RESET | TYPE |

|------|------|------------------------------------------------------------------------------------|-------|------|

| 3:0  | 31:0 | Image load time. Divide this value by 18667 to calculate the time in milliseconds. | x0    | R    |

#### 2.3.4.8 Retrieve Image Resolution Information

(**I**<sup>2</sup>**C**: 0x62)

(**USB**: CMD2: 0x1A, CMD3: 0x41)

When this command is executed, the system loads the image index shown in Section 2.3.4.6 and the horizontal and vertical resolution information of the image(s). The busy status of the system is high until the images resolution information is collected. This command cannot be executed while the system is already displaying patterns from flash.

#### Chipset Control Commands

www.ti.com

#### Table 2-26. Retrieve Image Resolution Information Write Command

| BYTE | BITS | DESCRIPTION                                                  | RESET | TYPE |

|------|------|--------------------------------------------------------------|-------|------|

| 0    | 7:0  | Starting index of the image that requires timing information | x0    | W    |

| 1    | 7:0  | Number of images that requires timing information            | x0    | W    |

The following data format is received when the load timing information is read back:

#### Table 2-27. Retrieve Image Resolution Information Read Command

| BYTE    | BITS | DESCRIPTION                           | RESET | TYPE |

|---------|------|---------------------------------------|-------|------|

| 1:0     | 15:0 | Horizontal resolution of first image  | x0    | R    |

| 3:2     | 15:0 | Vertical resolution of first image    | x0    | R    |

| 5:4     | 15:0 | Horizontal resolution of second image | x0    | R    |

| 7:6     | 15:0 | Vertical resolution of second image   | x0    | R    |

| _       | —    | _                                     | —     | —    |

| _       | —    | _                                     | —     | —    |

| N-2:N-3 | 15:0 | Horizontal resolution of nth image    | x0    | R    |

| N:N-1   | 15:0 | Vertical resolution of nth image      | x0    | R    |

#### 2.3.4.9 RetrieveNumber of Images in the Flash

(**I**<sup>2</sup>**C**: 0x0C)

(USB: CMD2: 0x1A, CMD3: 0x42)

This command retrieves the information about the number of Images in the flash. During creation of pattern LUT this command is useful. Using this command decreases the chances of setting wrong index numbers in the image LUT. One dummy byte must be sent as part of the command

#### Table 2-28. [Write] Retrieve Number of Images in the Flash

| BYTES | BITS | DESCRIPTION           | RESET | TYPE |

|-------|------|-----------------------|-------|------|

| 0     | 7:0  | Reserved; set to 0x00 | 0x00  | W    |

#### Table 2-29. [Response] Retrieve Number of Images in the Flash

| BYTES | BITS | DESCRIPTION                   | RESET | TYPE |

|-------|------|-------------------------------|-------|------|

| 0     | 7:0  | Number of images in the flash | N/A   | R    |

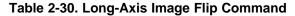

# 2.3.5 Image Flip

The DLPC350 supports long- and short-axis image flips to support rear- and front-projection table- and ceiling-mounted projection.

**NOTE:** If showing image from Flash, load image (I2C: 0x7F, USB: 0x1A, 0x39). This must be called to update the image flip setting.

#### 2.3.5.1 Long-Axis Image Flip

(**I**<sup>2</sup>**C**: 0x08)

(USB: CMD2: 0x10, CMD3: 0x08)

The long-axis image flip defines whether the input image is flipped across the long axis of the DMD. If this parameter is changed while displaying a still image, the input still image must be resent. If the image is not resent, the output image may be slightly corrupted. Figure 2-1 shows an example of a long-axis image flip. In structured light mode, the image flip takes effect on the next bit-plane, image, or video frame load.

| BYTE | BITS | DESCRIPTION                                 | RESET | TYPE |

|------|------|---------------------------------------------|-------|------|

|      |      | Flips image along the long side of the DMD: |       |      |

| 0    | 0    | 0 = Disable flip                            | d0    | WR   |

| 0    |      | 1 = Enable flip                             |       |      |

|      | 7:1  | Reserved                                    | d0    | R    |

Figure 2-1. Image Long-Axis Flip Example

# 2.3.5.2 Short Axis Image Flip

(**I**<sup>2</sup>**C**: 0x09)

(USB: CMD2: 0x10, CMD3: 0x09)

The short-Axis image flip defines whether the input image is flipped across the short axis of the DMD. If this parameter is changed while displaying a still image, the input still image must be resent. If the image is not resent, the output image may be slightly corrupted. Figure 2-2 shows an example of a short-axis image flip. In structured light mode, the image flip takes effect on the next bit-plane, image, or video frame load.

| BYTE | BITS | DESCRIPTION                                  | RESET | TYPE |

|------|------|----------------------------------------------|-------|------|

|      |      | Flips image along the short side of the DMD: |       |      |

| 0    |      | 0 - Disable flip                             | d0    | WR   |

|      |      | 1 - Enable flip                              |       |      |

|      | 7:1  | Reserved                                     | d0    | R    |

#### 2.3.6 Image Processing Control

#### 2.3.6.1 Color Space Conversion (CSC)

(**I**<sup>2</sup>**C**: 0x26)

(**USB**: CMD2: 0x1A, CMD3: 0x0D)

The CSC command specifies the color matrix used to translate the input data to RGB data or to color correct the RGB input data. The color space converter contains one color space matrix with nine elements. All nine command bytes must be sent as one contiguous block to ensure that all the coefficient values are updated simultaneously.

| BYTE | BITS | DESCRIPTION                                   |           | RESET       |             | TYPE |

|------|------|-----------------------------------------------|-----------|-------------|-------------|------|

|      |      | Attributes of input source:                   |           |             |             |      |

|      | 1:0  | 0 - RGB 4:4:4                                 |           |             |             |      |

| 0    | 1.0  | 1 - YCrCb 4:4:4                               | d0        |             |             | WR   |

| 0    |      | 2 - YCrCb 4:2:2                               |           |             |             |      |

|      | 7.0  | Reserved                                      |           | d0          |             | R    |

|      | 7:2  | RGB 4:4:4                                     | RGB 4:4:4 | YCrCb 4:4:4 | YCrCb 4:2:2 | R    |

| 1    | 12:0 | CSC coefficient 1                             | x0400     | x04A8       | x04A8       | WR   |

| 2    | 12:0 | CSC coefficient 2                             | x0000     | xFDC7       | xFCC0       | WR   |

| 3    | 12:0 | CSC coefficient 3                             | x0000     | xFF26       | xFE6F       | WR   |

| 4    | 12:0 | CSC coefficient 4                             | x0000     | x04A8       | x04A8       | WR   |

| 5    | 12:0 | CSC coefficient 5                             | x0400     | x0715       | x0662       | WR   |

| 6    | 12:0 | CSC coefficient 6                             | x0000     | x0000       | x0000       | WR   |

| 7    | 12:0 | CSC coefficient 7                             | x0000     | x04A8       | x04A8       | WR   |

| 8    | 12:0 | CSC coefficient 8         x0000         x0000 |           | WR          |             |      |

| 9    | 12:0 | CSC coefficient 9                             | x0400     | x0875       | x0812       | WR   |

| Table | 2-32. | CSC | Command  |

|-------|-------|-----|----------|

| Table | 2-92. |     | oominana |

Figure 2-3. CSC Matrix

All programmable CSC coefficient values represent numbers less than 4, but greater than or equal to –4. The CSC coefficient values are 13-bit signed 2's complement numbers with the binary point between bits 9 and 10 (s2.10 format).

| Table 2-33. Color Space Cor | nversion Coefficient Format |

|-----------------------------|-----------------------------|

|-----------------------------|-----------------------------|

| BIT 12 | BIT 11         | BIT 10         | BIT 9           | BIT 8           | BIT 7           | BIT 6 | BIT 5           | BIT 4 | BIT 3           | BIT 2 | BIT 1           | BIT 0            |

|--------|----------------|----------------|-----------------|-----------------|-----------------|-------|-----------------|-------|-----------------|-------|-----------------|------------------|

| Sign   | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2-4   | 2 <sup>-5</sup> | 2-6   | 2 <sup>-7</sup> | 2-8   | 2 <sup>-9</sup> | 2 <sup>-10</sup> |

# 2.3.7 LED Driver Control

LED driver operation is a function of the individual red, green, and blue LED-enable software-control parameters. The recommended order for initializing LED drivers is to:

1. Program the individual red, green, and blue LED driver currents.

- 2. Program the LED PWM polarity.

- 3. Enable the individual LED enable outputs.

- 4. Turn on the DLP display sequence (see Section 2.4.1).

The LED-current software-control parameters define PWM values that drive corresponding LED current. The LED enables indicate which LED is activated.

#### CAUTION

Careful control of LED current is needed to prevent damage to LEDs. Follow all LED manufacturer recommendations and maintain LED current levels within recommended operating conditions. The setting of the LED current depends on many system and application parameters (including projector thermal design, LED specifications, selected display mode, and so forth). Therefore, the recommended and absolute-maximum settings vary greatly.

### 2.3.7.1 LED Enable Outputs

(**I**<sup>2</sup>**C**: 0x10)

(**USB**: CMD2: 0x1A, CMD3: 0x07)

The DLPC350 contains three sets of pins to control the LED enables:

- LEDR\_EN for the red LED

- LEDG\_EN for the green LED

- LEDB\_EN for the blue LED

After reset, all LED enables are placed in the inactive state until the board initializes.

| BYTE | BITS | DESCRIPTION                                                                             | RESET | TYPE |

|------|------|-----------------------------------------------------------------------------------------|-------|------|

|      |      | Red LED Enable                                                                          |       |      |

|      | 0    | 0 - Red LED is disabled                                                                 | x0    | WR   |

|      |      | 1 - Red LED is enabled                                                                  |       |      |

|      |      | Green LED Enable                                                                        |       |      |

|      | 1    | 0 - Green LED is disabled                                                               | x0    | WR   |

|      |      | 1 - Green LED is enabled                                                                |       |      |

| 0    | 3    | Blue LED Enable                                                                         | x0    | WR   |

|      |      | 0 - Blue LED is disabled                                                                |       |      |

|      |      | 1 - Blue LED is enabled                                                                 |       |      |

|      |      |                                                                                         |       |      |

|      |      | 0 - All LED enables are controlled by bits 2:0 and ignore sequencer control             | x1    | WR   |

|      |      | 1 - All LED enables are controlled by the sequencer and ignore the settings in bits 2:0 |       |      |

|      | 7:4  | Reserved                                                                                | x0    | R    |

#### 2.3.7.1.1 LED PWM Polarity

# (**I**<sup>2</sup>**C**: 0x0B)

(**USB**: CMD2: 0x1A, CMD3: 0x05)

The LED PWM polarity command sets the polarity of all PWM signals. This command must be issued before powering up the LED drivers.

#### Table 2-35. LED PWM Polarity Command

| BYTE | BITS | DESCRIPTION                                                                                                           | RESET | TYPE |

|------|------|-----------------------------------------------------------------------------------------------------------------------|-------|------|

|      |      | Polarity of PWM signals                                                                                               |       |      |

|      | 1:0  | 0 - Normal polarity, PWM 0 value corresponds to no current while a PWM value of 255 corresponds to maximum current.   |       | WR   |

| 0    |      | 1 - Inverted polarity. PWM 0 value corresponds to maximum current while a PWM value of 255 corresponds to no current. |       |      |

|      | 7:2  | Reserved                                                                                                              | x0    | R    |