# TI UHF Gen2 Protocol

SCBU001

# **TI UHF Gen2 Protocol**

# **Reference Guide**

Literature Number: SCBU001 JULY 2006

# Contents

| Pref | ace   |                                                         | <br>7   |

|------|-------|---------------------------------------------------------|---------|

| 1    | Intro | duction                                                 | <br>. 9 |

|      | 1.1   | General                                                 | <br>10  |

|      | 1.2   | System Description                                      | <br>10  |

|      | 1.3   | Product Description                                     | <br>11  |

|      | 1.4   | Functional Description                                  | <br>11  |

|      | 1.5   | Memory Organization                                     | <br>1:  |

|      |       | 1.5.1 Reserved Memory                                   | <br>1:  |

|      |       | 1.5.2 Electronic Product Code <sup>™</sup> (EPC) Memory | <br>1   |

|      |       | 1.5.3 TID Memory                                        | <br>1:  |

|      |       | 1.5.4 User Memory                                       | <br>1:  |

| 2    | IC C  | ommands                                                 | <br>1   |

|      | 2.1   | Command Set                                             |         |

|      |       | 2.1.1 Select Command                                    | <br>1   |

|      |       | 2.1.2 Query Command                                     |         |

|      |       | 2.1.3 QueryAdjust Command                               |         |

|      |       | 2.1.4 QueryRep Command                                  |         |

|      |       | 2.1.5 ACK Command                                       | <br>1   |

|      |       | 2.1.6 NAK Command                                       | <br>1   |

|      |       | 2.1.7 Req_RN Command                                    | <br>2   |

|      |       | 2.1.8 Read Command                                      | <br>2   |

|      |       | 2.1.9 Write Command                                     | <br>2   |

|      |       | 2.1.10 KILL Command                                     | <br>2   |

|      |       | 2.1.11 Lock Command                                     | <br>2   |

|      |       | 2.1.12 Access Command                                   | <br>2   |

|      |       | 2.1.13 BlockWrite Command                               | <br>2   |

|      |       | 2.1.14 BlockErase Command                               | <br>2   |

| 3    | Reg   | ulatory, Safety, and Warranty Notices                   | <br>2   |

|      | 3.1   | Regulatory and Safety Notices                           | <br>3   |

|      | 3.2   | Warranty and Liability                                  | <br>3   |

|      | 3.3   | Hazards From Electrostatic Discharge (ESD)              | <br>30  |

| Α    | Tern  | ns and Abbreviations                                    | <br>3'  |

# List of Figures

| 1-1  | System Overview                    | 10 |

|------|------------------------------------|----|

| 1-2  | IC States                          | 11 |

| 1-3  | The Memory Structure               | 12 |

| 1-4  | Default EPC Data                   | 13 |

| 2-1  | Select Command                     | 17 |

| 2-2  | Query Command                      | 17 |

| 2-3  | QueryAdjust Command                | 18 |

| 2-4  | QueryRep Command                   | 18 |

| 2-5  | ACK Command                        | 18 |

| 2-6  | ACK Command: Nontruncated Response | 19 |

| 2-7  | ACK Command: Truncated Response    | 19 |

| 2-8  | NAK Command                        | 19 |

| 2-9  | Req_RN Command                     | 20 |

| 2-10 | Req_RN Response                    | 20 |

| 2-11 | Read Command                       | 21 |

| 2-12 | Read Response                      | 21 |

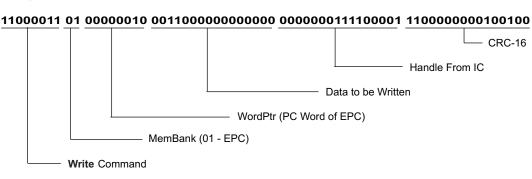

| 2-13 | Write Command                      | 22 |

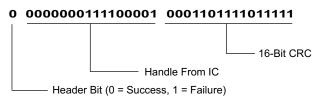

| 2-14 | Write Response                     | 22 |

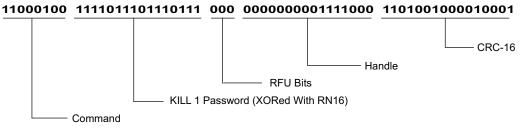

| 2-15 | KILL 1 Command                     | 22 |

| 2-16 | KILL 1 Response                    | 23 |

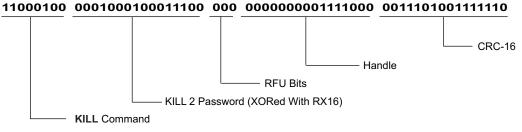

| 2-17 | KILL 2 Command                     | 23 |

| 2-18 | KILL 2 Response                    | 23 |

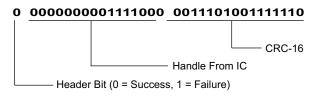

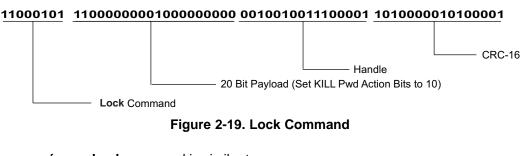

| 2-19 | Lock Command                       | 25 |

| 2-20 | Lock Response                      | 25 |

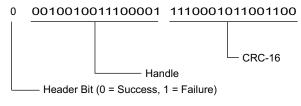

| 2-21 | Access 1 Command                   | 25 |

| 2-22 | Access 1 Response                  | 26 |

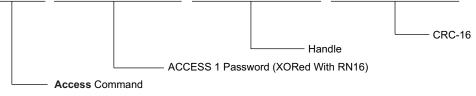

| 2-23 | Access 2 Command                   | 26 |

| 2-24 | Access 2 Response                  | 26 |

| 2-25 | BlockWrite Command                 | 27 |

| 2-26 | BlockWrite Response                | 27 |

| 2-27 | BlockErase Command                 | 27 |

| 2-28 | BlockErase Response                | 28 |

# List of Tables

| 2-1 | Command Set                    | 16 |

|-----|--------------------------------|----|

| 2-2 | Lock Command Payload           | 24 |

| 2-3 | Lock Command Mask Bits         | 24 |

| 2-4 | Lock Command Action Bits       | 24 |

| 2-5 | Lock Command Action Bits Table | 24 |

|     |                                |    |

Preface SCBU001–JULY 2006

This is the first edition of the Texas Instruments (TI) UHF Gen2 Protocol Reference Guide.

This reference guide contains a description of the IC, its functionality, command set, and operations.

This document has been created to help support TI's customers in designing in and/or using TI-RFid<sup>™</sup> products for their chosen application. TI does not warrant that its products will be suitable for the application, and it is the responsibility of the customer to ensure that these products meet their needs, including conformance to any relevant regulatory requirements.

TI reserves the right to make changes to its products or services or to discontinue any product or service at any time without notice. TI provides customer assistance in various technical areas, but does not have full access to data concerning the use and applications of customers' products.

Therefore, TI assumes no liability and is not responsible for customer applications or product or software design or performance relating to systems or applications incorporating TI products. In addition, TI assumes no liability and is not responsible for infringement of patents and/or any other intellectual or industrial property rights of third parties, which may result from assistance provided by TI.

TI products are not designed, intended, authorized, or warranted to be suitable for life-support applications or any other life-critical applications that could involve potential risk of death, personal injury, or severe property or environmental damage.

This document may be downloaded onto a computer, stored, and duplicated as necessary to support the use of the related TI products. Any other type of duplication, circulation, or storage on data carriers in any manner not authorized by TI represents a violation of the applicable copyright laws and shall be prosecuted.

#### About This Guide

This reference guide (11-09-21-700) is written for the use by TI partners who are engineers experienced with radio frequency identification devices (RFIDs).

Regulatory and safety notes that need to be followed are given in Chapter 3.

Conventions

#### Conventions

# WARNING

A warning is used where care must be taken or a certain procedure must be followed, in order to prevent injury or harm to your health.

# CAUTION

This indicates information on conditions, which must be met, or a procedure, which must be followed, which if not heeded could cause permanent damage to the system.

**Note:** Indicates conditions, which must be met, or procedures, which must be followed, to ensure proper functioning of any hardware or software.

# If You Need Assistance

For more information, please contact the sales office or distributor nearest you. This contact information can be found on our web site at: <u>http://www.ti-rfid.com</u>.

#### Trademarks

TIRIS, TI-RFid, and Tag-it are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

Chapter 1 SCBU001–JULY 2006

Page

This chapter describes the TI Gen2 IC.

# Торіс

| 1.1 | General 10                |

|-----|---------------------------|

|     |                           |

| 1.2 | System Description 10     |

| 1.3 | Product Description 11    |

| 1.4 | Functional Description 11 |

| 1.5 | Memory Organization 12    |

# 1.1 General

Large retailers, such as Wal-Mart<sup>™</sup> and Target<sup>™</sup> in the USA and Metro<sup>™</sup> in the European Union (EU), have issued mandates to their suppliers to ship cases and pallets of goods/products with radio-frequency identification (RFid) smart labels attached. TI's Generation 2 (Gen2) IC is intended to be used primarily in case- and pallet-level retail supply-chain applications, and is based on the EPCglobal<sup>™</sup> Gen2 Specification Version 1.0.9 approved in December 2004.

TI's UHF Gen2 IC operates with extremely low power and yet provides long read and write ranges, fast data transfer, and high smart-label throughput, which are all crucial for the following applications:

- Express parcel delivery

- Airline baggage handling

- Distribution logistics and supply-chain management

- Building access badges

- Asset tagging

This low-power passive IC is designed to operate on the energy extracted from the radio frequency (RF) signals transmitted from the reader (interrogator) via its antenna. The IC does not require a battery to operate. The IC returns data to the reader using modulated backscatter.

# 1.2 System Description

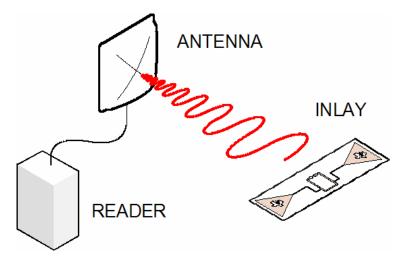

To form a functional transponder, the IC (sometimes called a die) requires bonding to an antenna. When the parameters of this antenna match the characteristics of the IC, the antenna resonates at the required frequency and is capable of receiving power and instructions and returning data.

For operation, a reader with antenna is required to send a command to the transponder and to receive its response (see Figure 1-1). The inlay does not transmit data until the reader sends a valid request (reader talks first principle).

Figure 1-1. System Overview

# **1.3 Product Description**

The IC has been manufactured to fully meet the EPCglobal Gen2 specification and can be used to create a functional transponder in three main ways:

• Forming an inlay

The TI Gen2 IC can be bonded to an antenna, printed on a plastic or paper substrate, or etched from copper or aluminum. This creates an 'inlay' that can then be converted into a 'wet inlay' having a peel-off adhesive layer, or integrated directly into a smart label. Currently, the majority of the RFID applications use inlays to make smart labels for use on cases and pallets.

- Direct attach to label

The TI Gen2 IC can be mounted directly on an antenna that is part of a printed label substrate, to construct a smart label. Currently, a number of manufacturers are exploring this approach.

- Attach to FR4

The TI Gen2 IC can also be mounted on FR4 antennas or antennas designed on printed circuit boards.

# 1.4 Functional Description

The IC is composed of a number of building blocks that include the analog front end (AFE), which converts RF to digital, digital logic, and memory.

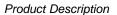

The digital logic includes a state machine, where groups of commands become available once the chip has transitioned to the correct state. This manual describes the functional operation of the state machine.

Figure 1-2. IC States

As soon as the chip enters the RF field, it changes to the **Ready** state and accepts **Select** commands. **Select** commands are sent to all ICs to inform each one if it is to take part in the **Inventory** process that is to follow. Multiple **Select** commands can be used to precisely define which ICs are to respond. All exchanges between readers and ICs start with one or more **Select** commands. ICs do not respond to the **Select** command.

Now, the **Inventory** group of commands can be used to initiate the singulation process, where each individual IC is identified and processed. Each **Inventory** round starts with a **Query** command being broadcast – this command passes a Q-value (0 to 15) from which each IC generates a slot counter number in the range (0, 2Q - 1). Most readers dynamically adjust the Q-value depending on the number of ICs in the field, thereby increasing the potential reading rate.

If an IC generates a slot counter value of zero, it is allowed to reply by sending a 16-bit random number and at the same time transitioning to the *Reply* state. The other ICs change state to *Arbitrate* and wait for further commands. If the ICs response is successfully received, the reader replies by sending an *ACK* command, together with the same 16-bit random number. This response now allows the IC to send back its Electronic Product Code<sup>TM</sup> (EPC) data and change state to *Acknowledged*.

Memory Organization

It is at this point that the reader is able to transition the IC to the **Open** (or **Secured**) state allowing operations such as Read, Write, Lock, and KILL (which are described in the following sections), but normally this exchange would terminate when the reader sends a **QueryAdjust** command and the IC switches state back to the **Ready** state and changes its inventoried flag to show it has been singulated. The **QueryAdjust** command also affects the other ICs, causing them to decrement their slot counters, and any IC whose counter is now zero is allowed to reply – so in this way, with successive **QueryAdjust** or **QueryRep** commands, all ICs will be found.

If two ICs reply at the same time, unless the reader is able to identify each one and send an *ACK* and the correct 16-bit random number, each one will time out, regenerate a slot counter value, and return to *Arbitrate*.

If further actions need to be performed on an IC, once the IC has returned its EPC number and is in the **Acknowledged** state, the reader sends a request random number (**Req\_RN**) command. The IC replies with a new 16-bit random number that is called the Handle and changes its state to **Open**. The Handle then becomes the token for further commands, such as **Reading**, **Writing** or **Killing**. If the **Lock** command is required and the ACCESS password is non-zero, the **Access** command (complete with ACCESS password) must be sent, to cause the IC to change to the **Secured** state. Once in **Secured** state, all commands are available.

# 1.5 Memory Organization

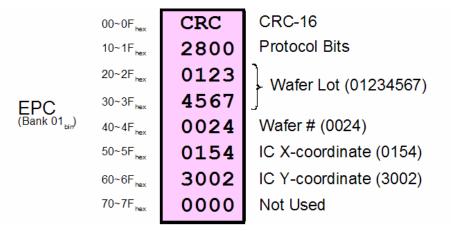

The memory structure conforms to the EPCglobal UHF Gen2 Specification Version 1.0.9. During manufacturing, TI probes each chip, and wafer lot information is programmed into the EPC field. Later, this information is overwritten when the IC is put into service but, in the meantime, it serves as a unique identifier of each chip.

| Data Bank                        | Address                                                              | Default IC Data <sub>hex</sub>   | Description            |

|----------------------------------|----------------------------------------------------------------------|----------------------------------|------------------------|

| Reserved                         | 00~1F <sub>hex</sub>                                                 | 00000000                         | KILL Password          |

|                                  | 20~3F <sub>hex</sub>                                                 | 00000000                         | ACCESS Password        |

| EPC<br>(Bank 01 <sub>bin</sub> ) | 00~1F <sub>hex</sub><br>20~3F <sub>hex</sub><br>40~5F <sub>hex</sub> | CRC 2800<br>01234567<br>00240154 | CRC-16 / Protocol Bits |

| TID                              | 60~7F <sub>hex</sub>                                                 | 30020000                         |                        |

| (Bank 10 <sub>bin</sub> )        |                                                                      | E2002000                         | TID Data               |

Figure 1-3. The Memory Structure

# 1.5.1 Reserved Memory

This data is Bank  $00_{binary}$  and contains the KILL password in locations 00 to  $1F_{hex}$  and the ACCESS password in locations 20 to  $3F_{hex}$ . These locations are shipped full of zeroes and unlocked. The passwords are only valid when programmed with non-zero values and (optionally) locked. When the passwords are locked, they become unreadable and unwriteable. If the ACCESS password is zero, the IC automatically transitions to the **Secured** state rather than the normal **Open** state.

# 1.5.2 Electronic Product Code™ (EPC) Memory

This data is Bank  $01_{binary}$  and contains a 16-bit CRC that is calculated by the chip on the rest of the data in the EPC memory – 16 bits that are the Protocol Control bits and 96 bits that contain the EPC number.

TI programs unique wafer data, similar to the following, into the EPC field:

Figure 1-4. Default EPC Data

# 1.5.3 TID Memory

This data is Bank 10<sub>binary</sub> and contains manufacture information. E2 is prescribed in the EPC Gen2 specification as a class identifier for EPCglobal; 002 identifies the manufacturer as Texas Instruments and 000 is the IC revision number. TID memory is permanently locked.

# 1.5.4 User Memory

There is no user memory.

Memory Organization

Chapter 2 SCBU001–JULY 2006

The TI Gen2 IC implements all mandatory and optional commands as defined in the EPCglobal Gen2 Specification Version 1.0.9.

| Торіс |             | Page |

|-------|-------------|------|

| 2.1   | Command Set | 16   |

# 2.1 Command Set

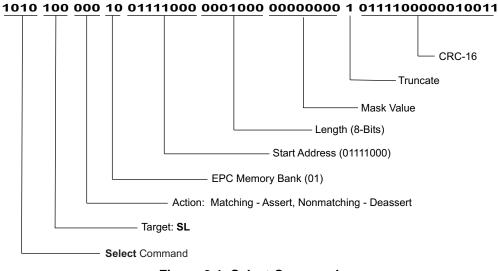

# 2.1.1 Select Command

| COMMAND     | CODE     | GROUP     | MANDATORY |  |

|-------------|----------|-----------|-----------|--|

| Select      | 1011     | SELECT    | Yes       |  |

| ACK         | 01       | INVENTORY | Yes       |  |

| NAK         | 11000000 | INVENTORY | Yes       |  |

| Query       | 1000     | INVENTORY | Yes       |  |

| QueryAdjust | 1001     | INVENTORY | Yes       |  |

| QueryRep    | 00       | INVENTORY | Yes       |  |

| Req_RN      | 11000001 | INVENTORY | Yes       |  |

| Read        | 11000010 | ACCESS    | Yes       |  |

| Write       | 11000011 | ACCESS    | Yes       |  |

| Kill        | 11000100 | ACCESS    | Yes       |  |

| Lock        | 11000101 | ACCESS    | Yes       |  |

| Access      | 11000110 | ACCESS    | No        |  |

| BlockWrite  | 11000111 | ACCESS    | No        |  |

| BlockErase  | 11001000 | ACCESS    | No        |  |

# Table 2-1. Command Set

The **Select** command is the first message that is sent to the IC. It contains user-defined criteria to allow the precise selection of groups of ICs. It also can set or reset the IC SL flag or change the Inventoried flag.

The following parameters are sent:

- Target: Instructs the IC to select one of four sessions and either the SL flag or the Inventoried flag associated with that session

- Action: How to set the selected flag

- MemBank: Selects a memory bank (EPC or TID)

- Pointer: Where to look in that memory bank

- Length: How many bits (0 to 255) from the memory bank

- Mask: Data string ("Length" bits long) that are compared with the data selected in the memory bank

- Truncate: If a **Query** command specifies Sel=10 or Sel=11, the response is truncated to only the EPC data after the mask and not the complete 96 bits.

- CRC-16: Checksum calculated on command string

For a more comprehensive description of this command, please consult the EPCglobal Gen2 specification.

Example:

Figure 2-1. Select Command

There is no response to a **Select** command.

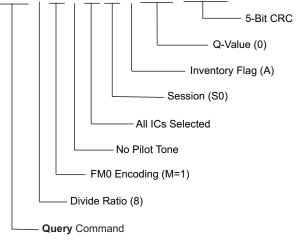

# 2.1.2 Query Command

The mandatory **Query** command initiates the **Inventory** process where individual ICs are identified. It takes the following parameters:

- DR (divide ratio): This is where the IC to reader link frequency is defined.

- M (cycles per second): Sets the IC to reader data rate and modulation format

- TRext: Switches the preamble pilot tone ON/OFF

- Sel: Chooses which ICs respond (all, SL, or ≈SL)

- Session: Selects a session (S0, S1, S2, or S3)

- Target: Selects between A and B Inventoried flags

- Q: Sets the number of slots for the Inventory round

- CRC-5: 5-bit checksum calculated on command string

Example:

#### 1000 0 00 0 00 00 0 0000 10000

Figure 2-2. Query Command

If an IC slot counter is zero, the response is a 16-bit random number similar to the following:

0100111111001000

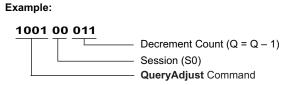

# 2.1.3 QueryAdjust Command

The mandatory **QueryAdjust** command instructs the IC to increment or decrement its slot counter value. It takes the following parameters:

- Session: By sending the session number (S0, S1, S2, or S3), it confirms to the IC that it is responding to the correct reader.

- UpDn: Instructs the IC to count up or down

Figure 2-3. QueryAdjust Command

If an IC slot counter value is zero as the result of the decrement, the response is a 16-bit random number similar to:

0000111111001000

# 2.1.4 QueryRep Command

The **QueryRep** command instructs ICs to decrement their slot counters and, if the resulting value is zero, backscatter a 16-bit random number to the reader.

There is only one parameter:

· Session: Confirms the session for this inventory round

Example:

Figure 2-4. QueryRep Command

If an IC slot counter value is zero as the result of the decrement, the response is a 16-bit random number similar to:

011111111001000

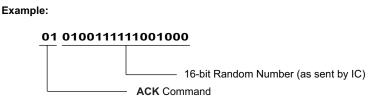

# 2.1.5 ACK Command

The mandatory **ACK** command is used to acknowledge the 16-bit random number response from a singulated IC.

Figure 2-5. ACK Command

When an IC receives the **ACK** command, it responds with its EPC data. This data may be truncated, if the Truncate bit is set in the **Select** command or nontruncated.

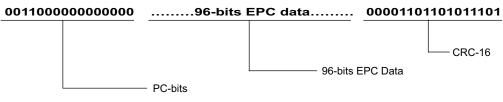

#### 2.1.5.1 Nontruncated

The general form is {PC-bits, 96-bits EPC, CRC-16}.

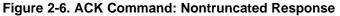

### 2.1.5.2 Truncated

The general form is {000002, truncated EPC data, CRC-16}.

Figure 2-7. ACK Command: Truncated Response

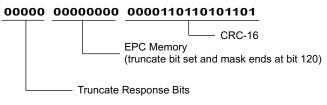

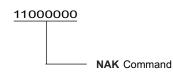

# 2.1.6 NAK Command

The mandatory NAK command is used to return all ICs back to the Arbitrate state.

Example:

Figure 2-8. NAK Command

There is no response to a **NAK** command.

Command Set

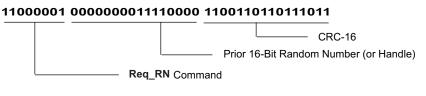

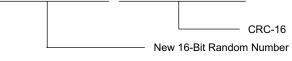

#### 2.1.7 Req\_RN Command

The mandatory **Req\_RN** command instructs the IC to generate and return a new 16-bit random number. The reader request and IC response depends on the state:

- **Acknowledged** state: The reader must include the last 16-bit random number with the request. In return, the IC sends a new 16-bit CRC called the Handle that will be the identifier between the IC and the reader for future commands. At the same time, the IC changes to the **Open** or **Secured** state, depending on the ACCESS password.

- ACCESS password = 0: IC changes to Secured state

- ACCESS password <> 0: IC changes to Open state

- Open or Secured state: The reader must send the Handle with the request. The state will remain as set.

Example:

Figure 2-9. Req\_RN Command

The response to the command is similar to:

#### 0000011110000111 1001101000001000

Figure 2-10. Req\_RN Response

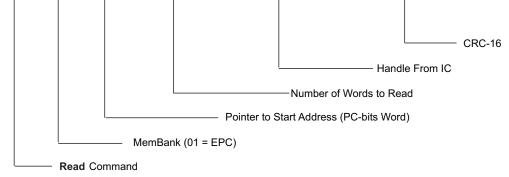

# 2.1.8 Read Command

The mandatory **Read** command allows reading of part or all of the IC memory. Data is read in multiples of 16-bit blocks. The command takes the following parameters:

- MemBank: Specifies which of the three memory areas (Reserved, EPC, or TID) to read

- WordPtr: Specifies the start word address, e.g., WordPtr = 00hex specifies the first word in the memory bank

- · WordCount: Specifies the number of 16-bit words to be read, starting at WordPtr

- Handle: Identifier used between IC and reader

- CRC-16: This checksum is calculated from the first command bit to the last handle bit.

Example:

####

#### Figure 2-11. Read Command

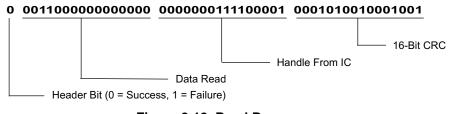

The response to a **Read** command is similar to:

Figure 2-12. Read Response

# 2.1.9 Write Command

The mandatory **Write** command allows a word of data to be written to any of the IC memory locations. Before a **Write** command can be sent, a new RN16 must be requested from the IC. The data is link cover coded by exclusive ORing the data with the RN16. The command takes the following parameters:

- MemBank: Specifies which memory bank to write

- WordPtr: Start address for the data to be written

- Data: 16 bits to be written (XORed with RN16)

- Handle: Identifier used between IC and reader

- CRC-16: 16-bit checksum calculated on the command string

Example:

#### Figure 2-13. Write Command

The response to a **Write** command is similar to:

Figure 2-14. Write Response

#### 2.1.10 KILL Command

The mandatory KILL command permanently disables the IC. This is a multistep command:

- Request a new 16-bit random number (RN16) from the IC.

- The 16 most significant bits (MSBs) of the KILL password are XORed with the RN16 (link cover coding) and sent to the IC.

- Request a new 16-bit random number (RN16) from the IC.

- The 16 least significant bits (LSBs) of the KILL password are XORed with new RN16 and sent to the IC.

For the **KILL** command to be accepted by the IC, the password must be written with a nonzero number and the state must be **Open** or **Secured**.

# 2.1.10.1 KILL 1 (Send 16 MSBs of KILL Password)

Figure 2-15. KILL 1 Command

#### 2.1.10.2 KILL 1 Response

#### 000000001111000 00011110101101111

Figure 2-16. KILL 1 Response

#### 2.1.10.3 Kill 2 (Send 16 LSBs of KILL Password)

Figure 2-17. KILL 2 Command

#### 2.1.10.4 KILL 2 Response

Figure 2-18. KILL 2 Response

After the second successful response, the IC has transitioned to the *Killed* state and the IC will not reply again.

# 2.1.11 Lock Command

The mandatory Lock command is used to:

- Lock individual passwords preventing or allowing subsequent reads and/or writes of that password

- Lock individual memory banks preventing or allowing subsequent writes to that memory bank

- Permalock make the lock status permanently unchangeable for a password or memory bank

For the **Lock** command to be accepted, the IC must be in the **Secured** state. If the ACCESS password is set to zero, the IC automatically changes to this state when a **Req\_RN** command is sent. If the ACCESS password is nonzero, the IC has to be forced into the **Secured** state by issuing an **Access** command with the ACCESS password. The **Lock** command takes the following parameters:

- Payload: 20-bit mask that indicates memory locations and the actions to be performed at those locations

- Handle: 16-bit random number used for mutual identification

- CRC-16: Checksum on the preceding data

The 20-bit **Lock** command payload comprises Mask and Action fields:

| 1            | 2 | 3 | 4          | 5        | 6 | 7        | 8         | 9 | 10        | 11        | 12 | 13         | 14 | 15        | 16         | 17        | 18         | 19 | 20         |

|--------------|---|---|------------|----------|---|----------|-----------|---|-----------|-----------|----|------------|----|-----------|------------|-----------|------------|----|------------|

| KILL<br>Mask |   |   | ESS<br>ask | EF<br>Ma | - | TI<br>Ma | ID<br>ask |   | ER<br>ask | KI<br>Act |    | ACC<br>Act |    | EF<br>Act | PC<br>tion | TI<br>Act | ID<br>tion |    | ER<br>tion |

The first ten payload bits are Mask bits and defined as:

- Mask = 0: Ignore this action, keep present settings.

- Mask = 1: Implement the associated Action field.

#### Table 2-3. Lock Command Mask Bits

| KILL Mask  |            | ACCES      | S Mask     | EPC        | Mask       | TID I      | Mask       | USER Mask |     |  |

|------------|------------|------------|------------|------------|------------|------------|------------|-----------|-----|--|

| 0          | 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8         | 9   |  |

| Skip/write | N/A       | N/A |  |

The second ten payload bits are Action bits and are defined as:

- Action = 0: Deassert lock for the associated location.

- Action = 1: Assert lock or permalock for the associated location.

# Table 2-4. Lock Command Action Bits

| KILL Action           |               | ACCESS Action         |               | EPC /        | Action        | TID A        | ction         | USER Action |     |  |

|-----------------------|---------------|-----------------------|---------------|--------------|---------------|--------------|---------------|-------------|-----|--|

| 0                     | 1             | 2                     | 3             | 4            | 5             | 6            | 7             | 8           | 9   |  |

| Pwd<br>read/<br>write | Perma<br>lock | Pwd<br>read/<br>write | Perma<br>lock | Pwd<br>write | Perma<br>lock | Pwd<br>write | Perma<br>lock | N/A         | N/A |  |

The combinations of Action bits are shown in Table 2-5.

| Pwd Write      | Perma Lock | DESCRIPTION                                                                                                              |  |

|----------------|------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 0              | 0          | Associated memory bank is writeable from either <b>Open</b> or <b>Secured</b> state.                                     |  |

| 0              | 1          | Associated memory bank is permanently writeable from either <b>Open</b> or <b>Secured</b> state and can never be locked. |  |

| 1              | 0          | Associated memory bank is writeable from the <b>Secured</b> state, but not from the <b>Open</b> state.                   |  |

| 1              | 1          | Associated memory bank is not writeable in any state.                                                                    |  |

| Pwd Read/Write | Perma Lock |                                                                                                                          |  |

| 0              | 0          | Associated password is readable and writeable from either <b>Open</b> or <b>Secured</b> state.                           |  |

| 0              | 1          | Associated password is permanently readable and writeable from either <b>Open</b> or <b>Secured</b> state.               |  |

| 1              | 0          | Associated password is only readable and writeable from the <b>Secured</b> state.                                        |  |

| 1              | 1          | Associated password is not readable or writeable in any state.                                                           |  |

Example:

The response from a **Lock** command is similar to:

Figure 2-20. Lock Response

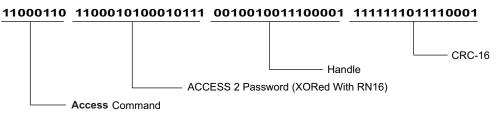

# 2.1.12 Access Command

The optional **Access** command is required when the ACCESS password is set (nonzero) and the IC has to be put into the **Secured** state, to allow the use of the **Lock** command. This is a multipart command requiring separate commands for each 16 bits for the 32-bit ACCESS password:

- Request a new 16-bit random number (RN16) from the IC.

- The 16 MSBs of the password are XORed with the RN16 (link cover coding) and sent to the IC.

- Request a new 16-bit random number (RN16) from the IC.

- The 16 LSBs of the password are XORed with the new RN16 and sent to the IC.

For the **Access** command to be accepted by the IC, the password must be written with a nonzero number.

# 2.1.12.1 Access 1 (Send 16 MSBs of ACCESS Password)

####

Figure 2-21. Access 1 Command

The response to the Access command is similar to:

#### 2.1.12.2 Access 1 Response

Figure 2-22. Access 1 Response

#### 2.1.12.3 Access 2 (Send 16 LSBs of ACCESS Password)

Figure 2-23. Access 2 Command

#### 2.1.12.4 Access 2 Response

#### 0010010011100001 1100010111011101

Figure 2-24. Access 2 Response

After the second successful response, the IC is in the **Secured** state.

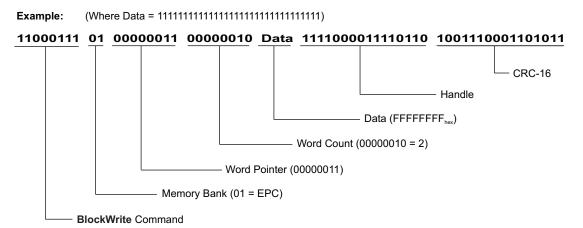

# 2.1.13 BlockWrite Command

The optional **BlockWrite** command allows multiple words to be written to the IC's reserved or EPC memory with a single command. Words are 16 bits long.

The command takes the following parameters:

- MemBank: Memory bank to be written (reserved, EPC)

- WordPtr: Starting word address for the data

- WordCount: Number of 16-bit words to be written

- Data: Data to be written

- Handle: Identifier between IC and reader

- CRC-16: Checksum calculated on the data string

Figure 2-25. BlockWrite Command

The BlockWrite command response is similar to:

Figure 2-26. BlockWrite Response

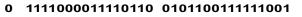

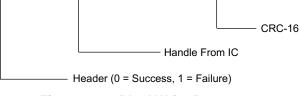

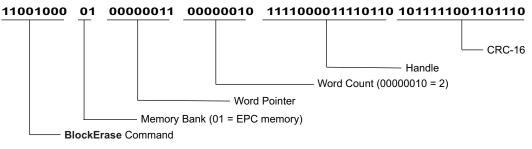

# 2.1.14 BlockErase Command

The optional **BlockErase** command allows the erasing of multiple words in a single command. The command takes the following parameters:

- MemBank: Memory bank to erase (reserved, EPC)

- WordPtr: Starting word address for deletion

- WordCount: Number of 16-bit words to be erased

- Handle: Identifier between IC and reader

- CRC-16: Checksum calculated on the data string

#### Example

Figure 2-27. BlockErase Command

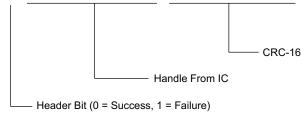

The **BlockErase** command response is similar to:

# 0 1111000011110110 0101100111111001

Topic

Page

# Regulatory, Safety, and Warranty Notices

| -    |                                            | -  |

|------|--------------------------------------------|----|

|      |                                            |    |

| 3.1  | Regulatory and Safety Notices              | 30 |

| 3.2  | Warranty and Liability                     | 30 |

| 3.3  | Hazards From Electrostatic Discharge (ESD) |    |

| •••• | ······································     |    |

# 3.1 Regulatory and Safety Notices

An RFID system comprises an RF transmission device and is, therefore, subject to national and international regulations.

Any system reading from or writing to a transponder created from an IC may only be operated under an experimental license or final approval issued by the relevant approval authority. Before any such device or system can be marketed, an equipment authorization must be obtained from the relevant approval authority.

TI Gen2 ICs have been manufactured using state-of-the-art technology and in accordance with the recognized safety rules.

Observe precautions in operating instructions:

- Condition for the safe processing, handling, and fault-free operation of TI Gen2 ICs is the knowledge of the basic safety regulations.

- All persons who handle TI Gen2 ICs must observe the guidelines and particularly the safety precautions outlined in this document.

- In addition, basic rules and regulations for accident prevention applicable to the operating site must also be considered.

# 3.2 Warranty and Liability

The "General Conditions of Sale and Delivery" of Texas Instruments Incorporated or a TI subsidiary apply.

#### CAUTION

TI's transponder ICs are 100% thoroughly tested. It is the responsibility of TI s customers to evaluate their equipment to ensure, through appropriate process controls, that machine and material parameters are met on an ongoing basis.

# 3.3 Hazards From Electrostatic Discharge (ESD)

During handling of ICs and wafers, due regard must be given to the buildup of electrostatic charges (see the data sheet).

# CAUTION

Electronic devices can be destroyed by electrostatic energy.

**Note:** TI does not accept warranty claims for material that has already undergone packaging or conversion process.

Appendix A SCBU001–JULY 2006

# Terms and Abbreviations

A list of the abbreviations and terms used in the various TI manuals can be found in a separate manual:

TI-RFID Product Manuals – Terms & Abbreviations (literature number 11-03-21-002)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products              |                        | Applications       |                           |

|-----------------------|------------------------|--------------------|---------------------------|

| Amplifiers            | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters       | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                   | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface             | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                 | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt            | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers      | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                  | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power<br>Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                       |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2007, Texas Instruments Incorporated