# UCD3138A64/UCD3138128 Programmer's Manual

SLUUB54B - April 2016

Copyright © 2016, Texas Instruments Incorporated

#### **Table of Contents**

| 1 Introduction                                                                      |    |

|-------------------------------------------------------------------------------------|----|

| 2 More Memory - Memory Map Changes for UCD3138A64                                   | 12 |

| 2.1 Memory Map Overview                                                             | 13 |

| 2.2 Memory Map Details – Flash Mode                                                 | 14 |

| 2.3 Memory Map Details – ROM Mode                                                   |    |

| 2.4 Register Changes for Program Flash Blocks                                       |    |

| 3 Changes to ROM Boot Program                                                       |    |

| 3.1 ROM Version                                                                     |    |

| 3.2 Flash Checksum Handling                                                         |    |

| 4 Two Enhanced I2C/PMBus Interfaces                                                 |    |

| 4.1 PMBus/I2C Register Names are Different on UCD3138064 and UCD3138A               |    |

| 21                                                                                  | 01 |

| 4.2 Automatic Acknowledgement of 2 Slave Addresses                                  | 21 |

| 4.3 Alert and Control Support on PMBus                                              |    |

| 4.4 Improved Clock High Timeout Handling                                            |    |

| 4.5 Improved Bit Counter Reset.                                                     |    |

| 4.6 Change in Test Mode Address                                                     |    |

| 5 External Clock Controlled Real-Time Clock                                         |    |

|                                                                                     |    |

| <ul><li>5.1 Trimming the External Frequency</li><li>5.2 RTC Calendar Data</li></ul> |    |

| 5.3 RTC Polling and Interrupts                                                      |    |

|                                                                                     |    |

| 6 Four Additional General Purpose I/O Pins                                          |    |

| 7 SPI Port Pins Move Around – JTAG_MUX_SEL Bit                                      |    |

| 8 One Additional Timer Capture Register                                             |    |

| 9 Support for Fixed Sampling Rates for LLC.                                         |    |

| 10 Information on Pulse Width in Peak Current Mode                                  |    |

| 11 Improvements to Fault Handling and Burst Mode                                    |    |

| 11.1 Fault Counter Changes from 5 to 7 Bits                                         |    |

| 11.2 Blanking for the Cycle-by-Cycle Fault Added                                    |    |

| 11.3 Improved Fault and Burst Mode with Edge Generator in Use                       |    |

| 12 Eighty Pins Instead of 64                                                        | 26 |

| 13 Disabling the <u>RESET</u> Pin                                                   | 26 |

| 14 Adjusting the Clock Speed                                                        | 26 |

| 15 No Write to HFO_LN_FILTER_EN                                                     |    |

| 16 Unused bits Removed from DPWM Registers                                          |    |

| 17 Sample and Hold Buffer Available on ADC even if Sample and Hold are Not Use      |    |

| 27                                                                                  | u  |

| 18 DAC Dither on Sample Trigger                                                     | 28 |

| 19 Consolidation of PCM Control Registers                                           |    |

| 20 Enhancements for UCD3138128                                                      |    |

| 20.1 Added Flash Memory                                                             |    |

| · · · · · · · · · · · · · · · · · · ·                                               |    |

| 20.2 Changes to ROM Boot Program<br>20.2.1 ROM Version                              |    |

|                                                                                     |    |

|                                                                                     |    |

| 20.3 Registers Added for '128                                                       |    |

| 20.4 Additional FLASH Keys                                                          |    |

| 21 UCD3138A64 Memory Map                                                            | 31 |

Copyright © 2014, Texas Instruments Incorporated

| 21.1 Loo | p Mux Registers                                                         |    |

|----------|-------------------------------------------------------------------------|----|

| 21.1.1   | Front End Control 0 Mux Register (FECTRL0MUX)                           | 31 |

| 21.1.2   | Front End Control 1 Mux Register (FECTRL1MUX)                           | 34 |

| 21.1.3   | Front End Control 2 Mux Register (FECTRL2MUX)                           | 36 |

| 21.1.4   | Sample Trigger Control Register (SAMPTRIGCTRL)                          |    |

| 21.1.5   | External DAC Control Register (EXTDACCTRL)                              | 39 |

| 21.1.6   | Filter Mux Register (FILTERMUX)                                         | 41 |

| 21.1.7   | Filter KComp A Register (FILTERKCOMPA)                                  | 43 |

| 21.1.8   | Filter KComp B Register (FILTERKCOMPB)                                  | 43 |

| 21.1.9   | DPWM Mux Register (DPWMMUX)<br>Constant Power Control Register (CPCTRL) | 43 |

| 21.1.10  | Constant Power Control Register (CPCTRL)                                | 46 |

| 21.1.11  | Constant Power Nominal Threshold Register (CPNOM)                       | 47 |

| 21.1.12  | Constant Power Max Threshold Register (CPMAX)                           | 47 |

| 21.1.13  | Constant Power Configuration Register (CPCONFIG)                        | 48 |

| 21.1.14  | Constant Power Max Power Register (CPMAXPWR)                            | 48 |

| 21.1.15  | Constant Power Integrator Threshold Register (CPINTTHRESH)              | 48 |

| 21.1.16  | Constant Power Firmware Divisor Register (CPFWDIVISOR)                  | 48 |

| 21.1.17  | Constant Power Status Register (CPSTAT)                                 | 49 |

| 21.1.18  | Cycle Adjustment Control Register (CYCADJCTRL)                          | 50 |

| 21.1.19  | Cycle Adjustment Limit Register (CYCADJLIM)                             | 51 |

| 21.1.20  | Cycle Adjustment Status Register (CYCADJSTAT)                           | 51 |

| 21.1.21  | Global Enable Register (GLBEN)                                          | 51 |

| 21.1.22  | PWM Global Period Register (PWMGLBPRD)                                  | 52 |

| 21.1.23  | Sync Control Register (SYNCCTRL)                                        | 53 |

| 21.1.24  | Light Load Control Register (LLCTRL)                                    | 53 |

| 21.1.25  | Light Load Enable Threshold Register (LLENTHRESH)                       |    |

| 21.1.26  | Light Load Disable Threshold Register (LLDISTHRESH)                     |    |

| 21.1.27  | Analog Peak Current Mode Control Register (APCMCTRL)                    | 54 |

| 21.2 Fau | It Mux Registers                                                        |    |

| 21.2.1   | Analog Comparator Control 0 Register (ACOMPCTRL0)                       |    |

| 21.2.2   | Analog Comparator Control 1 Register (ACOMPCTRL1)                       |    |

| 21.2.3   | Analog Comparator Control 2 Register (ACOMPCTRL2)                       |    |

| 21.2.4   | Analog Comparator Control 3 Register (ACOMPCTRL3)                       |    |

| 21.2.5   | External Fault Control Register (EXTFAULTCTRL)                          |    |

| 21.3 Fau | It Mux Interrupt Status Register (FAULTMUXINTSTAT)                      |    |

| 21.3.1   | Fault Mux Raw Status Register (FAULTMUXRAWSTAT)                         | 62 |

| 21.3.2   | Comparator Ramp Control 0 Register (COMPRAMP0)                          |    |

| 21.3.3   | Digital Comparator Control 0 Register (DCOMPCTRL0)                      |    |

| 21.3.4   | Digital Comparator Control 1 Register (DCOMPCTRL1)                      |    |

| 21.3.5   | Digital Comparator Control 2 Register (DCOMPCTRL2)                      |    |

| 21.3.6   | Digital Comparator Control 3 Register (DCOMPCTRL3)                      |    |

| 21.3.7   | Digital Comparator Counter Status Register (DCOMPCNTSTAT)               |    |

| 21.3.8   | DPWM 0 Current Limit Control Register (DPWM0CLIM)                       |    |

| 21.3.9   | DPWM 0 Fault AB Detection Register (DPWM0FLTABDET)                      |    |

| 21.3.10  | DPWM 0 Fault Detection Register (DPWM0FAULTDET)                         |    |

| 21.3.11  | DPWM 0 IDE Detection Register (DPWM0IDEDET)                             |    |

| 21.3.12  | DPWM 1 Current Limit Control Register (DPWM1CLIM)                       |    |

| 21.3.13  | DPWM 1 Fault AB Detection Register (DPWM1FLTABDET)                      |    |

| 21.3.14  | DPWM 1 Fault Detection Register (DPWM1FAULTDET)                         |    |

| 21.3.15  | DPWM 1 IDE Detection Register (DPWM1IDEDET)                             | 85 |

|   | 21.3.16 | DPWM 2 Current Limit Control Register (DPWM2CLIM)        | .86 |

|---|---------|----------------------------------------------------------|-----|

|   | 21.3.17 | DPWM 2 Fault AB Detection Register (DPWM2FLTABDET)       | .88 |

|   | 21.3.18 | DPWM 2 Fault Detection Register (DPWM2FAULTDET)          |     |

|   | 21.3.19 | DPWM 2 IDE Detection Register (DPWM2IDEDET)              |     |

|   | 21.3.20 | DPWM 3 Current Limit Control Register (DPWM3CLIM)        |     |

|   | 21.3.21 | DPWM 3 Fault AB Detection Register (DPWM3FLTABDET)       |     |

|   | 21.3.22 | DPWM 3 Fault Detection Register (DPWM3FAULTDET)          |     |

|   | 21.3.23 | DPWM 3 IDE Detection Register (DPWM3IDEDET)              |     |

|   | 21.3.24 | HFO Fail Detect Register (HFOFAILDET)                    |     |

|   | 21.3.25 | LFO Fail Detect Register (LFOFAILDET)                    | 104 |

|   | 21.3.26 | IDE Control Register (IDECTRL)                           |     |

| 2 |         | - Real Time Clock Interface                              |     |

|   | 21.4.1  | RTC Control Register (RTCCTRL)                           |     |

|   | 21.4.2  | RTC Counter Register (RTCCOUNT)                          |     |

|   | 21.4.3  | RTC Preset Register (RTCPRESET)                          |     |

|   | 21.4.4  | RTC Interrupt Enable Register (RTCINTEN)                 | 106 |

|   | 21.4.5  | RTC Interrupt Status Register (RTCINTSTAT)               | 106 |

|   | 21.4.6  | RTC Prescale Register (RTCPRESCALE)                      |     |

| 2 |         | - Serial Peripheral Interface                            |     |

|   | 21.5.1  | SPI Control Register (SPICTRL)                           |     |

|   | 21.5.2  | SPI Status Register (SPISTAT)                            | 108 |

|   | 21.5.3  | SPI Pin Function Register (SPIFUNC)                      | 108 |

|   | 21.5.4  | SPI Pin Direction Register (SPIDIR)                      |     |

|   | 21.5.5  | SPI Pin GP Out Register (SPIGPOUT)                       | 108 |

|   | 21.5.6  | SPI Pin GP In Register (SPIGPIN)                         | 108 |

|   | 21.5.7  | SPI TX Buffer Register (SPITX0)                          | 109 |

|   | 21.5.8  | SPI TX Buffer Register (SPITX1)                          | 109 |

|   | 21.5.9  | SPI Read Buffer Register (SPIRX0)                        | 109 |

|   | 21.5.10 | SPI Read Buffer Register (SPIRX1)                        |     |

|   | 21.5.11 | SPI Read Buffer Register (SPIRX2)                        |     |

|   | 21.5.12 | SPI Read Buffer Register (SPIRX3)                        | 109 |

| 2 |         | RT Registers                                             |     |

|   | 21.6.1  | UART Control Register 0 (UARTCTRL0)                      |     |

|   | 21.6.2  | UART Receive Status Register (UARTRXST)                  |     |

|   | 21.6.3  | UART Transmit Status Register (UARTTXST)                 |     |

|   | 21.6.4  | UART Control Register 3 (UARTCTRL3)                      | 111 |

|   | 21.6.5  | UART Interrupt Status Register (UARTINTST)               | 113 |

|   | 21.6.6  | UART Baud Divisor High Byte Register (UARTHBAUD)         |     |

|   | 21.6.7  | UART Baud Divisor Middle Byte Register (UARTMBAUD)       |     |

|   | 21.6.8  | UART Baud Divisor Low Byte Register (UARTLBAUD)          |     |

|   | 21.6.9  | UART Receive Buffer (UARTRXBUF)                          |     |

|   | 21.6.10 | UART Transmit Buffer (UARTTXBUF)                         |     |

|   | 21.6.11 | UART I/O Control Register (UARTIOCTRLSCLK, UARTIOCTRLRX, |     |

|   |         | CTRLTX)                                                  | 115 |

| 2 |         | Registers                                                |     |

| _ | 21.7.1  | ADC Control Register (ADCCTRL)                           | 116 |

|   | 21.7.2  | ADC Status Register (ADCSTAT)                            | 117 |

|   | 21.7.3  | ADC Test Control Register (ADCTSTCTRL)                   | 118 |

|   | 21.7.4  | ADC Sequence Select Register 0 (ADCSEQSEL0)              | 118 |

|   | -       | Copyright © 2014, Texas Instruments Incorpo              |     |

|   |         |                                                          |     |

| 21.7.5     | ADC Sequence Select Register 1 (ADCSEQSEL1)                   | 119 |

|------------|---------------------------------------------------------------|-----|

| 21.7.6     | ADC Sequence Select Register 2 (ADCSEQSEL2)                   | 120 |

| 21.7.7     | ADC Sequence Select Register 3 (ADCSEQSEL3)                   |     |

| 21.7.8     | ADC Result Registers 0-15 (ADCRESULTx, x=0:15)                |     |

| 21.7.9     | ADC Averaged Result Registers 0-5 (ADCAVGRESULTx, x=0:15)     |     |

| 21.7.9     | ADC Digital Compare Limits Register 0-5 (ADCCOMPLIMX, x=0.15) |     |

|            |                                                               |     |

| 21.7.11    | ADC Digital Compare Enable Register (ADCCOMPEN)               |     |

| 21.7.12    | ADC Digital Compare Results Register (ADCCOMPRESULT)          |     |

| 21.7.13    | ADC Averaging Control Register (ADCAVGCTRL)                   |     |

| 21.8 DPV   | VM 0-3 Registers                                              | 133 |

| 21.8.1     | DPWM Control Register 0 (DPWMCTRL0)                           | 133 |

| 21.8.2     | DPWM Control Register 1 (DPWMCTRL1)                           | 136 |

| 21.8.3     | DPWM Control Register 2 (DPWMCTRL2)                           | 139 |

| 21.8.4     | DPWM Period Register (DPWMPRD)                                |     |

| 21.8.5     | DPWM Event 1 Register (DPWMEV1)                               |     |

| 21.8.6     | DPWM Event 2 Register (DPWMEV2)                               |     |

| 21.8.7     | DPWM Event 3 Register (DPWMEV3)                               | 1/1 |

|            | DEVIVIE EVENIL 5 REGISTER (DEVIVIE V3)                        |     |

| 21.8.8     | DPWM Event 4 Register (DPWMEV4)                               |     |

| 21.8.9     | DPWM Sample Trigger 1 Register (DPWMSAMPTRIG1)                |     |

| 21.8.10    | DPWM Sample Trigger 2 Register (DPWMSAMPTRIG2)                |     |

| 21.8.11    | DPWM Phase Trigger Register (DPWMPHASETRIG)                   |     |

| 21.8.12    | DPWM Cycle Adjust A Register (DPWMCYCADJA)                    | 143 |

| 21.8.13    | DPWM Cycle Adjust B Register (DPWMCYCADJB)                    | 143 |

| 21.8.14    | DPWM Resonant Duty Register (DPWMRESDUTY)                     | 143 |

| 21.8.15    | DPWM Fault Control Register (DPWMFLTCTRL)                     |     |

| 21.8.16    | DPWM Overflow Register (DPWMOVERFLOW)                         | 145 |

| 21.8.17    | DPWM Interrupt Register (DPWMINT)                             | 146 |

| 21.8.18    | DPWM Counter Preset Register (DPWMCNTPRE)                     |     |

| 21.8.19    | DPWM Blanking A Begin Register (DPWMBLKABEG)                  |     |

|            |                                                               |     |

| 21.8.20    | DPWM Blanking A End Register (DPWMBLKAEND)                    |     |

| 21.8.21    | DPWM Blanking B Begin Register (DPWMBLKBBEG)                  |     |

| 21.8.22    | DPWM Blanking B End Register (DPWMBLKBEND)                    |     |

| 21.8.23    | DPWM Minimum Duty Cycle High Register (DPWMMINDUTYHI)         |     |

| 21.8.24    | DPWM Minimum Duty Cycle Low Register (DPWMMINDUTYLO)          |     |

| 21.8.25    | DPWM Adaptive Sample Register (DPWMADAPTIVE)                  |     |

| 21.8.26    | DPWM Fault Status (DPWMFLTSTAT)                               | 150 |

|            | DPWM Auto Switch High Upper Thresh Register                   |     |

|            | AUTOSWHIUPTHRESH)                                             | 151 |

|            | DPWM Auto Switch High Lower Thresh Register                   |     |

|            | AUTOSWHILOWTHRESH)                                            | 152 |

| 21 8 20    | DPWM Auto Switch Low Upper Thresh Register                    | 102 |

|            |                                                               | 150 |

|            | UTOSWLOUPTHRESH)                                              | 152 |

|            | DPWM Auto Switch Low Lower Thresh Register                    | 450 |

|            |                                                               | 153 |

|            | DPWM Auto Config Max Register (DPWMAUTOMAX)                   |     |

|            | DPWM Auto Config Mid Register (DPWMAUTOMID)                   |     |

|            | DPWM Edge PWM Generation Control Register (DPWMEDGEGEN)       |     |

| 21.8.34    | DPWM Filter Duty Read Register (DPWMFILTERDUTYREAD)           |     |

| 21.8.35    | DPWM CBC Location (DPWMCBCLOCATION)                           | 158 |

| 21.9 Filte | r Registers                                                   |     |

|            | -                                                             |     |

Copyright © 2016, Texas Instruments Incorporated

| 04.0.4           |                                                                   | 450              |

|------------------|-------------------------------------------------------------------|------------------|

| 21.9.1           | Filter Status Register (FILTERSTATUS)                             |                  |

| 21.9.2           | Filter Control Register (FILTERCTRL)                              |                  |

| 21.9.3           | CPU XN Register (CPUXN)<br>Filter XN Read Register (FILTERXNREAD) |                  |

| 21.9.4           | Filter KI_YN Read Register (FILTERKIYNREAD)                       |                  |

| 21.9.5<br>21.9.6 | Filter KD_YN Read Register (FILTERKITNREAD)                       |                  |

| 21.9.0           | Filter YN Read Register (FILTERYNREAD)                            |                  |

| 21.9.7           | Coefficient Configuration Register (COEFCONFIG)                   |                  |

| 21.9.8           | Filter KP Coefficient 0 Register (FILTERKPCOEF0)                  |                  |

| 21.9.9           | Filter KP Coefficient 1 Register (FILTERKPCOEF1)                  |                  |

| 21.9.10          | Filter KI Coefficient 0 Register (FILTERKICOEF0)                  |                  |

| 21.9.12          | Filter KI Coefficient 1 Register (FILTERKICOEF1)                  |                  |

| 21.9.12          | Filter KD Coefficient 0 Register (FILTERKDCOEF0)                  | 100              |

| 21.9.13          | Filter KD Coefficient 1 Register (FILTERKDCOEF1)                  | 167              |

| 21.9.15          | Filter KD Alpha Register (FILTERKDALPHA)                          |                  |

| 21.9.16          | Filter Nonlinear Limit Register 0 (FILTERNL0)                     |                  |

| 21.9.17          | Filter Nonlinear Limit Register 1 (FILTERNL1)                     |                  |

| 21.9.18          | Filter Nonlinear Limit Register 2 (FILTERNL2)                     |                  |

| 21.9.19          | Filter KI Feedback Clamp High Register (FILTERKICLPHI)            |                  |

| 21.9.20          | Filter KI Feedback Clamp Low Register (FILTERKICLPLO)             |                  |

| 21.9.21          | Filter YN Clamp High Register (FILTERYNCLPHI)                     |                  |

| 21.9.22          | Filter YN Clamp Low Register (FILTERYNCLPLO)                      |                  |

| 21.9.23          | Filter Output Clamp High Register (FILTEROCLPHI)                  |                  |

| 21.9.24          | Filter Output Clamp Low Register (FILTEROCLPLO)                   |                  |

| 21.9.25          | Filter Preset Register (FILTERPRESET)                             |                  |

| 21.10 F          | ront End Control Registers                                        |                  |

| 21.10.1          | Ramp Control Register (RAMPCTRL)                                  |                  |

| 21.10.2          | Ramp Status Register (RAMPSTAT)                                   |                  |

| 21.10.3          | Ramp Cycle Register (RAMPCYCLE)                                   |                  |

| 21.10.4          | EADC DAC Value Register (EADCDAC)                                 | 175              |

| 21.10.5          | Ramp DAC Ending Value Register (RAMPDACEND)                       | 175              |

| 21.10.6          | DAC Step Register (DACSTEP)                                       | 175              |

| 21.10.7          | DAC Saturation Step Register (DACSATSTEP)                         | 176              |

| 21.10.8          | EADC Control Register (EADCCTRL)                                  | 176              |

| 21.10.9          | Pre-Bias Control Register 0 (PREBIASCTRL0)                        |                  |

| 21.10.10         | 0 (                                                               |                  |

| 21.10.11         |                                                                   |                  |

| 21.10.12         |                                                                   | 181              |

| 21.10.13         |                                                                   | 181              |

| 21.10.14         | <b>J</b>                                                          | 182              |

| 21.10.15         | $\mathbf{J}$                                                      | 182              |

|                  | liscellaneous Analog Control                                      | 182              |

| 21.11.1          | Clock Trim Register (CLKTRIM)                                     | 182              |

| 21.11.2          | Package ID Register (PKGID)                                       |                  |

| 21.11.3          | Brownout Register (BROWNOUT)                                      |                  |

| 21.11.4          | Global I/O EN Register (GLBIOEN)                                  |                  |

| 21.11.5          | Global I/O OE Register (GLBIOOE)                                  |                  |

| 21.11.6          | Global I/O Open Drain Control Register (GLBIOOD)                  |                  |

| 21.11.7          | Global I/O Value Register (GLBIOVAL)                              |                  |

|                  | Copyright © 2014, Texas Instrumer                                 | its incorporated |

|                                                                                                                                       | 400  |

|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 21.11.8 Global I/O Read Register (GLBIOREAD)                                                                                          |      |

| 21.11.9 RTCCTRLI/O Mux Control Register (IOMUX)                                                                                       |      |

| 21.11.10 Current Sharing Control Register (CSCTRL)                                                                                    |      |

| 21.11.11 Temperature Reference Register (TEMPREF)                                                                                     |      |

| 21.11.12 Power Disable Control Register (PWRDISCTRL)                                                                                  | .191 |

| 21.12 PMBus Interface                                                                                                                 | .193 |

| 21.12.1 PMBUS Control Register 1 (PMBCTRL1)                                                                                           | .193 |

| 21.12.2 PMBus Transmit Data Buffer (PMBTXBUF)                                                                                         | .194 |

| 21.12.3 PMBus Receive Data Register (PMBRXBÚF)                                                                                        | .194 |

| 21.12.4 PMBus Acknowledge Register (PMBACK)                                                                                           | .194 |

| 21.12.5 PMBus Status Register (PMBST)                                                                                                 |      |

| 21.12.6 PMBus Interrupt Mask Register (PMBINTM)                                                                                       |      |

| 21.12.7 PMBus Control Register 2 (PMBCTRL2)                                                                                           |      |

| 21.12.8 PMBus Hold Slave Address Register (PMBHSA)                                                                                    | .199 |

| 21.12.9 PMBus Control Register 3 (PMBCTRL3)                                                                                           | .200 |

| 21.13 GIO – General Purpose Input/Output Module                                                                                       |      |

| 21.13.1 Fault IO Direction Register (FAULTDIR)                                                                                        |      |

| 21.13.2 Fault Input Register (FAULTIN)                                                                                                |      |

| 21.13.3 Fault Output Register (FAULTOUT)                                                                                              |      |

| 21.13.4 Fault Interrupt Enable Register (FAULTINTENA)                                                                                 | .206 |

| 21.13.5 Fault Interrupt Polarity Register (FAULTINTPOL)                                                                               |      |

| 21.13.6 Fault Interrupt Pending Register (FAULTINTPEND)                                                                               |      |

| 21.13.7 External Interrupt Direction Register (EXTINTDIR)                                                                             |      |

| 21.13.8 External Interrupt Input Register (EXTINTIN)                                                                                  |      |

| 21.13.9 External Interrupt Output Register (EXTINTOUT)                                                                                |      |

| 21.13.10 External Interrupt Enable Register (EXTINTENA)                                                                               |      |

| 21.13.11 External Interrupt Polarity Register (EXTINTPOL)                                                                             |      |

| 21.13.12 External Interrupt Pending Register (EXTINTPEND)                                                                             |      |

| 21.14 Timer Module<br>21.14.1 24-bit Counter Data Register (T24CNTDAT)                                                                |      |

| 21.14.1 24-bit Counter Data Register (T24CNTDAT)<br>21.14.2 24-bit Counter Control Register (T24CNTCTRL)                              |      |

|                                                                                                                                       |      |

| 21.14.3 24-bit Capture Channel Data Register x(T24CAPDATx)<br>21.14.4 24-bit Capture Channel Control Register x(T24CAPCTRLx)          |      |

|                                                                                                                                       |      |

| 21.14.5 24-bit Capture I/O Control and Data Register (T24CAPIO)<br>21.14.6 24-bit Output Compare Channel 0 Data Register (T24CMPDAT0) |      |

|                                                                                                                                       |      |

| ······································                                                                                                |      |

| 21.14.8 24-bit Output Compare Channel 0 Control Register (T24CMPCTRL0)                                                                |      |

| 21.14.9 24-bit Output Compare Channel 1 Control Register (T24CMPCTRL1)                                                                |      |

| 21.14.10 PWMx Counter Data Register (T16PWMxCNTDAT)                                                                                   |      |

| 21.14.11 PWMx Counter Control Register (T16PWMxCNTCTRL)<br>21.14.12 PWMx 16-bit Compare Channel 0-1 Data Register                     | .215 |

| (T16PWMxCMPyDAT)                                                                                                                      | 216  |

| 21.14.13 PWM Compare Control Register (T16PWMxCMPCTRL)                                                                                | .210 |

|                                                                                                                                       |      |

| 21.14.14 Watchdog Status (WDST)<br>21.14.15 Watchdog Control (WDCTRL)                                                                 | 210  |

| $\mathbf{U}$                                                                                                                          | 213  |

| 21.15 Memory Controller - MMC<br>21.15.1 Static Memory Control Register (SMCTRL)                                                      | .221 |

| 21.15.1 Static Memory Control Register (SMCTRL)                                                                                       | .221 |

| 21.15.2 Write Control Register (WCTRL)<br>21.15.3 Peripheral Control Register (PCTRL)                                                 |      |

| 21.15.3 Peripheral Location Register (PLOC)                                                                                           |      |

|                                                                                                                                       |      |

Copyright © 2016, Texas Instruments Incorporated

| 21.15.5 Peripheral Protection Register (PPROT)                     | 223      |

|--------------------------------------------------------------------|----------|

| 21.16 DEC – Address Manager                                        |          |

| 21.16.1 Memory Fine Base Address High Register 0 (MFBAHR0)         |          |

| 21.16.2 Memory Fine Base Address Low Register 0 (MFBALR0)          |          |

| 21.16.3 Memory Fine Base Address High Register 1-3,17-19 (MFBAHRx) |          |

| 21.16.4 Memory Fine Base Address Low Register 1-3,17-19 (MFBALRx)  |          |

| 21.16.5 Memory Fine Base Address High Register 4 (MFBAHR4)         |          |

| 21.16.6 Memory Fine Base Address Low Register 4-16 (MFBALRx)       |          |

|                                                                    |          |

| <b>, , , , , , , , , ,</b>                                         |          |

| 21.16.8 Memory Fine Base Address High Register 6 (MFBAHR6)         |          |

| 21.16.9 Memory Fine Base Address High Register 7 (MFBAHR7)         |          |

| 21.16.10 Memory Fine Base Address High Register 8 (MFBAHR8)        |          |

| 21.16.11 Memory Fine Base Address High Register 9 (MFBAHR9)        |          |

| 21.16.12 Memory Fine Base Address High Register 10 (MFBAHR10)      |          |

| 21.16.13 Memory Fine Base Address High Register 11 (MFBAHR11)      |          |

| 21.16.14 Memory Fine Base Address High Register 12 (MFBAHR12)      |          |

| 21.16.15 Memory Fine Base Address High Register 13 (MFBAHR13)      |          |

| 21.16.16 Memory Fine Base Address High Register 14 (MFBAHR14)      | 230      |

| 21.16.17 Memory Fine Base Address High Register 15 (MFBAHR15)      | 230      |

| 21.16.18 Memory Fine Base Address High Register 16 (MFBAHR16)      |          |

| 21.16.19 Program Flash Control Register 0-3 (PFLASHCTRL_x)         |          |

| 21.16.20 Data Flash Control Register (DFLASHCTRL)                  |          |

| 21.16.21 Flash Interlock Register (FLASHILOCK)                     |          |

| 21.17 CIM – Central Interrupt Module                               |          |

| 21.17.1 IRQ Index Offset Vector Register (IRQIVEC)                 | 232      |

| 21.17.2 FIQ Index Offset Vector Register (FIQIVEC)                 | 232      |

| 21.17.3 FIQ/IRQ Program Control Register (FIRQPR)                  |          |

| 21.17.4 Pending Interrupt Read Location Register (INTREQ)          |          |

| 21.17.5 Interrupt Mask Register (REQMASK)                          | 233      |

| 21.18 SYS – System Module                                          |          |

| 21.18.1 Clock Control Register (CLKCNTL)                           |          |

| 21.10.1 Clock Collicol Register (CLRCINTL)                         | 204      |

| 21.18.2 System Exception Control Register (SYSECR)                 | 235      |

| 21.18.3 System Exception Status Register (SYSESR)                  |          |

| 21.18.4 Abort Exception Status Register (ABRTESR)                  |          |

| 21.18.5 Global Status Register (GLBSTAT)                           |          |

| 21.18.6 Device Identification Register (DEV)                       |          |

| 21.18.7 System Software Interrupt Flag Register (SSIF)             |          |

| 21.18.8 System Software Interrupt Request Register (SSIR)          |          |

| 22 Converting UCD3138 programs to UCD3138A64                       |          |

| 22.1 Change Linker Addresses                                       |          |

| 22.2 Change Header Files Which Define Peripherals                  | 240      |

| 22.3 Changes to the Flash Control Registers                        | 240      |

| 22.4 Set BLANK_PCM_EN for Peak Current Mode                        |          |

| 22.5 Update Parm Info/Parm Value Pointers                          |          |

| 22.5.1 Changes in pmbus.h                                          |          |

| 22.5.2 Changes in Parm Info/Parm Value File                        |          |

| 22.6 Changes to load.asm                                           |          |

| 22.7 Changes to system_defines.h                                   |          |

| 22.8 Changes to Software Interrupt Addresses                       |          |

| Copyright © 2014, Texas Instruments Inco                           |          |

| 8                                                                  | rporateu |

#### D3138A64/UCD3138128 Programmer's Manual SLUUB54B-July 2014-Revised April 2016

| 2  | 2.9  | Changes to Data Flash Write in Software Interrupt |     |

|----|------|---------------------------------------------------|-----|

| 2  | 2.10 | Changes to Device ID                              | 244 |

| 2  | 2.11 | ÷                                                 |     |

| 2  | 2.12 | Change APCMCTRL to PCMCTRL                        |     |

| 2  | 2.13 | Changing to Fixed Frequency Sampling on LLC       |     |

|    |      | verting UCD3138064 Programs to UCD3138A64         |     |

|    |      | verting UCD3138A64 Programs to UCD3138128         |     |

| 25 | Refe | erences                                           |     |

# **Scope of this Document**

The following topics are covered in the UCD3138A64 Enhancements Programmer's Manual

- Memory Map Changes from UCD3138064

- Enhancement to I2C and PMBus Interfaces

- Real Time Clock added for a time and date reference

- Changes to IOMUX to support 80 pins

- Four Additional general purpose I/O lines

- One Additional Timer Capture Register

- Support for Fixed Sampling Rates for LLC

- Information on Pulse Width in Peak Current Mode

- Improvements to Fault Handling and Burst Mode

- Disabling the RESET pin

- How to migrate existing programs from UCD3138 and UCD3138064 to UCD3138A64.

- Adjusting the Clock Speed

- No Write to HFO\_LN\_FILTER\_EN required or recommended

- Unused bits removed from DPWM registers

- Sample and Hold Buffer Available on ADC even if Sample and Hold are Not Used

- DAC Dither on Sample Trigger

- Consolidation of PCM control registers

- UCD3138128 enhancements over UCD3138A64

- UCD3138A64/UCD3138128 Peripheral Memory Map

Other topics related to UCD3138A64 are covered in the additional documents listed below:

#### UCD3138 ARM and Digital System Programmer's Manual

- Boot ROM & Boot Flash

- BootROM Function

- o Memory Read/Write Functions

- o Checksum Functions

- o Flash Functions

- Avoiding Program Flash Lock-Up

- ARM7 Architecture

- Modes of Operation

- Hardware/Software Interrupts

- o Instruction Set

- Dual State Inter-working (Thumb 16-bit Mode/ARM 32-bit Mode)

- Memory & System Module

- o Address Decoder, DEC (Memory Mapping)

- Memory Controller (MMC)

- Central Interrupt Module

- Register Map for all of the above peripherals in UCD3138

#### UCD3138 Monitoring and Communications Programmer's Manual

- 1. ADC12

- Control, Conversion, Sequencing & Averaging

- Digital Comparators

- Temperature Sensor

- PMBUS Addressing

- Dual Sample & Hold

- 2. Miscellaneous Analog Controls (Current Sharing, Brown-Out, Clock-Gating)

- 3. PMBUS Interface

- 4. General Purpose Input Output (GPIO)

- 5. Timer Modules

- 6. Register Map for all of the above peripherals in UCD3138

#### UCD3138 Digital Power Peripheral Programmer's Manual

- 7. Digital Pulse Width Modulator (DPWM)

- Modes of Operation (Normal/Multi/Phase-shift/Resonant etc)

- Automatic Mode Switching

- DPWMC, Edge Generation & Intra-Mux

- 8. Front End

- Analog Front End

- Error ADC or EADC

- Front End DAC

- Ramp Module

- Successive Approximation Register Module

- 9. Filter

- Filter Math

- 10. Loop Mux

- Analog Peak Current Mode

- Constant Current/Constant Power (CCCP)

- Automatic Cycle Adjustment

- 11. Fault Mux

- Analog Comparators

- Digital Comparators

- Fault Pin functions

- DPWM Fault Action

- Ideal Diode Emulation (IDE), DCM Detection

- Oscillator Failure Detection

- 12. Register Map for all of the above peripherals in UCD3138

#### UCD3138064 Enhancements Programmer's Manual

- Memory Map Changes in UCD3138064 compared to UCD3138

- Added FLASH BLOCK

- Relocation of Fast Peripherals

- Relocation of ROM

- Added Interfaces for External EEPROM

- I2C Interface for External EEPROM

- SPI Interface for External EEPROM

- Other Changes in UCD3138064 compared to UCD3138

- Changes to IOMUX to support SPI and I2C pin multiplexing

- BLANK\_PCM\_ENABLE bit to optimize Peak Current Mode response time

- How to migrate firmware programs from UCD3138 to UCD3138064

For the most up to date product specifications please consult the UCD3138A64 Device datasheet (Lit # <u>SLUSBZ8</u>) available at www.ti.com.

\_

-

# 1 Introduction

The UCD3138A64 device is an 80-pin, 64kB product offering in TI's UCD3138 family of digital controllers for isolated power. It offers more RAM, higher pin count, a real-time clock, and enhancements to several peripherals, compared to the UCD3138064 devices which are available in 64-pin and 48-pin package options. The UCD3138128 is the same as the 'A64, except it offers twice the program flash – 128K bytes arranged in 4 independent 32K blocks.

This manual highlights the differences between the UCD3138064 and the UCD3138A64 devices. It describes the added features and changes to existing features. It also gives guidance on converting programs from the UCD3138 and the UCD3138064 to the UCD3138A64. The UCD3138 Programmer's Manuals (<u>SLUU994</u>, <u>SLUU995</u>, and <u>SLUU996</u>) and the UCD3138064 Enhancements Programmer's Manual (<u>SLUUAD8</u>) should be used for information on all elements that are common to these devices.

There are also sections on the describing the UCD3138128 enhancements, and how to convert programs to the '128.

Compared to the UCD3138064, the UCD3138A64 device is differentiated based on the following considerations:

- Faster checksum calculations in ROM for quick firmware startup

- 4K additional RAM for a total of 8K RAM

- Boot Flash based Dual Memory Image support for 'on-the-fly' firmware updates (vs ROM based support in UCD3138064)

- Instead of a PMBus and an I2C interface there are 2 enhanced PMBus/I2C interfaces

- Each interface now supports master and slave, I2C and PMBus

- o Each interface has enhanced recovery from bus faults

- Each interface supports automatic address acknowledge of a second address

- Real Time Clock for accurate time/date information.

- 4 additional General Purpose I/O lines

- 1 additional timer capture register

- Support for fixed sampling rates for LLC\*\*

- Information on PCM (Peak Current Mode) pulse width for each cycle

- This makes it much easier to measure average current on every cycle

- Enhanced Burst Mode and Fault Handling for PCM.

- Increased fault count from 32 to 128 consecutive faults before shut down.

- QFP-80 package for UCD3138A64, instead of QFN-64 & QFN-48 in UCD3138064

- Capability to disable the RESET pin under firmware control

- Clock Trim registers that make it possible to adjust the clock speed more easily

- Unused bits removed from DPWM registers

**\*\*NOTE**: Adding the fixed sample rate to LLC has lengthened the DPWM calculation time at the beginning of the period. It has increased from 72 nsec to 120 nsec. Moving DPWM edges in and out of this window could cause pulse extension and shoot through in some power supply topologies.

# 2 More Memory - Memory Map Changes for UCD3138A64

The larger 8K RAM requires changes to the addressing for the RAM and data FLASH.

#### 2.1 Memory Map Overview

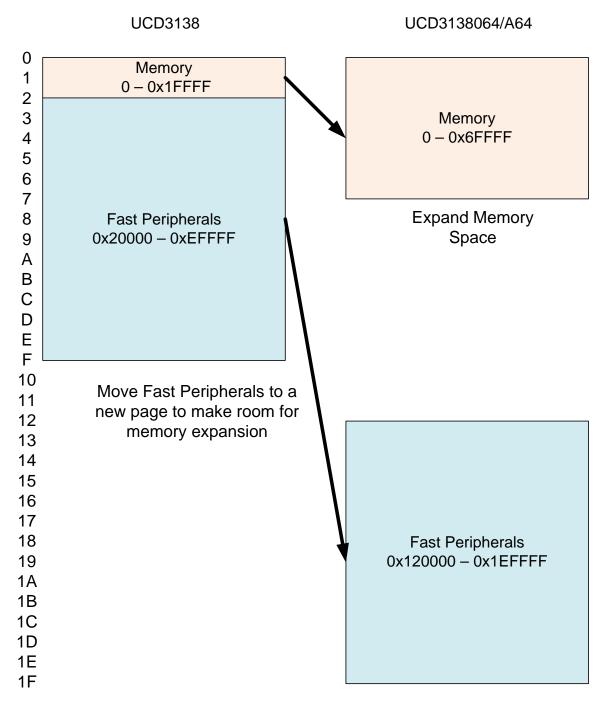

The memory map overview for the UCD3138A64 is the same as the overview of the UCD3138064. Compared with the UCD3138, the fast peripherals are moved up to make room for the larger FLASH.

**Overall Memory Map Changes**

The fast peripherals are moved up by 0x100000 bytes. This makes it very simple to calculate their new addresses. The slow peripherals, those mapped to 0xFFF7EC00 and above, are not moved at all, so they are not shown on the figure. The RTC is added at 0xFFF7E400. The SPI interface was added in the UCD3138064 at 0xFFF7E600, and is still the same on the UCD3138A64.

Fast peripherals use the same address decode scheme as memories. They have address mapping registers and run at the processor clock speed. Slow peripherals are on a separate I/O bus with no address mapping registers. The I/O bus and the slow peripherals run at half the processor clock speed.

## 2.2 *Memory Map Details – Flash Mode*

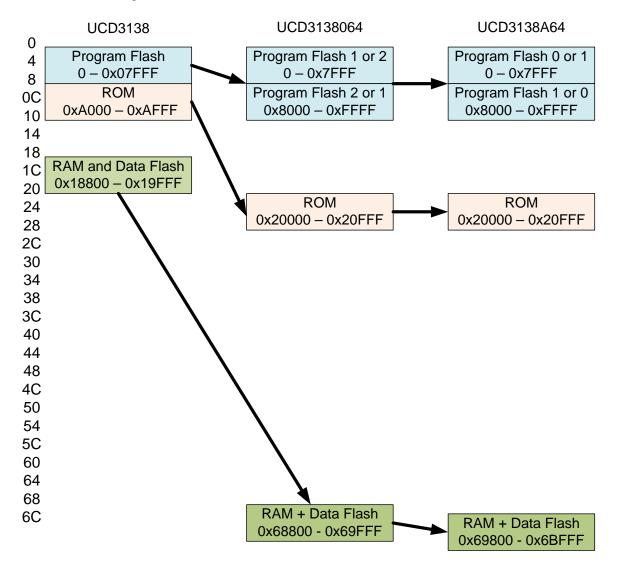

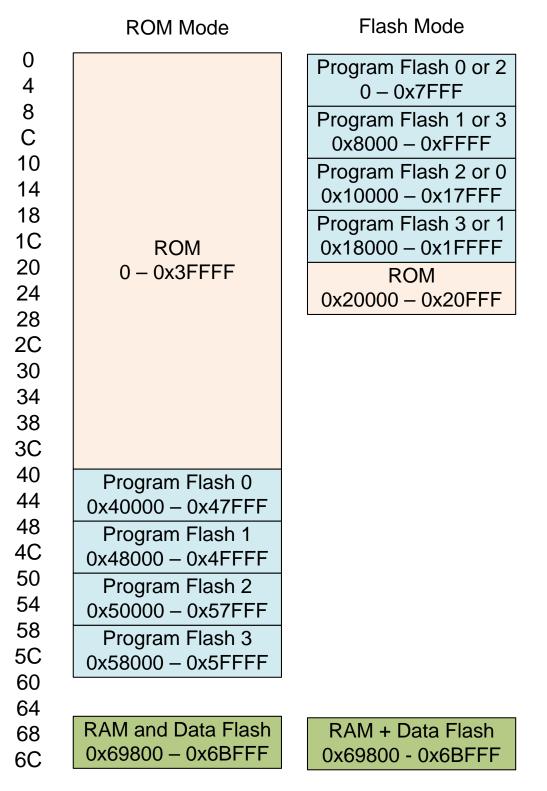

There are some changes, however, in the details between the UCD3138064 and UCD3138A64. Here is a block diagram:

**Detailed Memory Map Changes in FLASH Mode**

Copyright © 2014, Texas Instruments Incorporated

The numbering system for the flash blocks is changed. For the UCD3138064, the blocks are referred to as 1 and 2. On the UCD3138A64, they are numbered from 0 to 1.

The RAM is now 8K. The memory addressing logic requires that an 8K block be on an 8K boundary. This means that the RAM is moved from 0x69000 to 0x6A000. The data FLASH is moved from 0x68800 to 0x69800. It is kept next to the data FLASH so that a single CPU register can be used with an offset to access both memory blocks at the same time.

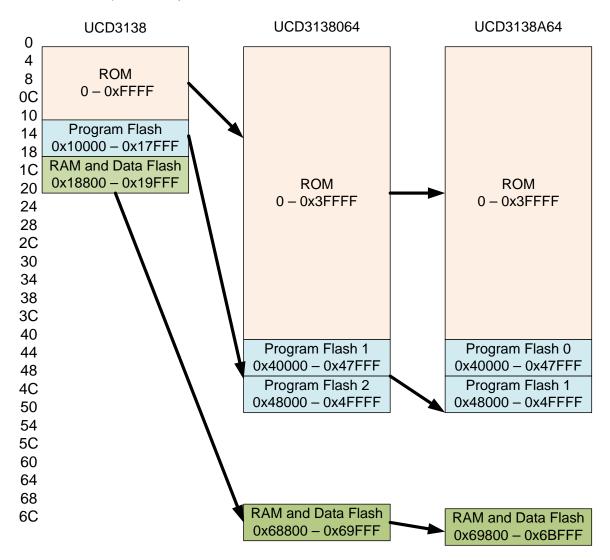

### 2.3 *Memory Map Details – ROM Mode*

The changes between the UCD3138064 and UCD3138A64 in ROM mode are similar to the changes in flash mode – the flash block names are changed, and the data FLASH and RAM are moved further up in memory.

Memory Map changes to ROM, RAM, and FLASH in ROM mode

In the ARM core, the reset and interrupt vectors start at location 0 in memory. At power up reset, the ROM must be at location 0 to provide the vectors. In flash mode, the flash must be at location 0 to control the interrupt vectors. This is accomplished by changing the addresses of the ROM and FLASH. In ROM mode, the ROM must extend from location 0 to the location where it will be in FLASH mode. In the UCD3138064 and UCD3138A64, this address is 0x20000. The ROM reset vectors jump to this area. This way, when flash mode is entered, the ROM simply remaps itself to the higher address. The program is already executing there. Then it remaps the flash to location 0 and jumps the vector at 0. The ROM on the UCD3138064 is 8K. That same 8K image is repeated throughout the entire memory space from 0 to 0x3FFFF in ROM mode. The ROM in

the UCD3138A64 is also 8K, but 4K is reserved for built in self test. Because of this, the sine and exponent tables in the UCD3138 and UCD3138064 ROM are not provided in the ROM. The UCD3138A64 has plenty of flash for any sine or exponent tables desired.

## 2.4 Register Changes for Program Flash Blocks

Each Flash block has 3 registers associated with it:

- DecRegs.PFLASHCTRLx page and mass erase and block busy status

- DecRegs.MFBAHRx sets high bits of address for flash block used for moving blocks

- DecRegs.MFBALRx sets lower bits of address and block size used for moving blocks

See the UCD3138 ARM and System manual for more information on these types of registers. The PFLASHCTRLx registers have different numbers depending on which device is being used. Here is a table of PFLASHCTRLx names across the 3 devices:

| Block Number on A64 | UCD3138    | UCD3138064  | UCD3138A64  |

|---------------------|------------|-------------|-------------|

| 0                   | PFLASHCTRL | PFLASHCTRL1 | PFLASHCTRL0 |

| 1                   |            | PFLASHCTRL2 | PFLASHCTRL1 |

Note that there is no block number for the single block in the UCD3138. On the UCD3138064, blocks are numbered 1 and 2, and on the UCD3138A64, blocks are numbered from 0 to 1.

The MFBAHR and MFBALR registers (Memory Fine Base Address High and Low) are numbered sequentially. Some of them are used for addressing the faster peripherals. This explains the numbers between the first flash block and subsequent flash blocks. Here is a table:

| Block | MFBAHR   | MFBALR   |

|-------|----------|----------|

| 0     | MFBAHR1  | MFBALR1  |

| 1     | MFBAHR17 | MFBALR17 |

There is only one DecRegs.FLASHILOCK register. It must have a key written to it before each write or erase to a flash block. Different values must be written to it depending on which flash block is being modified.

#### #define PROGRAM\_FLASH0\_INTERLOCK\_KEY 0x42DC157E #define PROGRAM\_FLASH1\_INTERLOCK\_KEY 0x6C97D0C5 #define DATA\_FLASH\_INTERLOCK\_KEY 0x42DC157E

These codes are the same as the ones on the UCD3138064.

See Section 20.16, DEC – Address Manager of this document for information on the detailed memory and bit maps for these registers.

# 3 Changes to ROM Boot Program

The ROM changes the response to the version command and it also changes the handling of flash checksums when it powers up.

#### 3.1 ROM Version

The UCD3138A64 will return a 0006 as the first half of the version, indicating the device. The first version of the ROM will return a 0001 as the second half of the version, indicating version 1 of the ROM. If other versions of the ROM are produced, the number will increment.

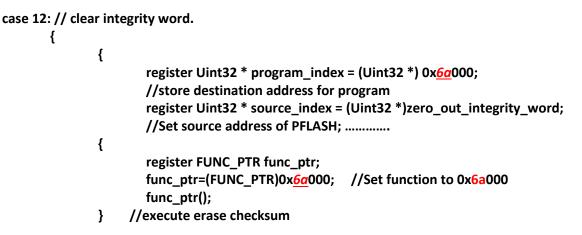

## 3.2 Flash Checksum Handling

The ROM program changes how it handles program startup. Instead of 2 possible checksum locations on the UCD3138, there are 4 on the UCD3138064, and 3 on the UCD3138A64. To speed up calculations on the UCD3138A64, the checksum changes from 4 to 8 bytes. Now it is a sum of the memory read as 32 bit words, rather than as 8 bit bytes. This makes the checksum calculation about 4 times faster. This means that the ROM can verify the checksum for 64 kbytes in about 5 msec while the UCD3138 takes 10 msec for 32 kbytes.

Here is the code for calculating the checksum:

```

void calculate_checksum(register Uint32 *start_address, register Uint32 *end_address)

{

```

register unsigned long long lcs = long\_checksum; //use local register variable for speed.

Two words are added each time through the loop to improve the speed by reducing the loop overhead.

The checksums and their locations are:

0x7f8 – Boot block for Block 0 0x7ff8 – Overall checksum for Block 0 0xfff8 – Overall checksum for a 64K program combining Blocks 0 and 1

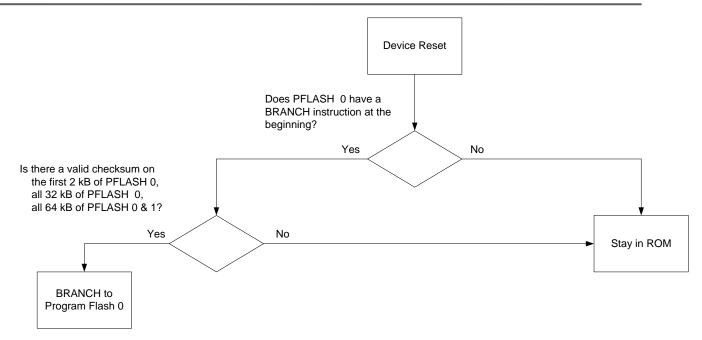

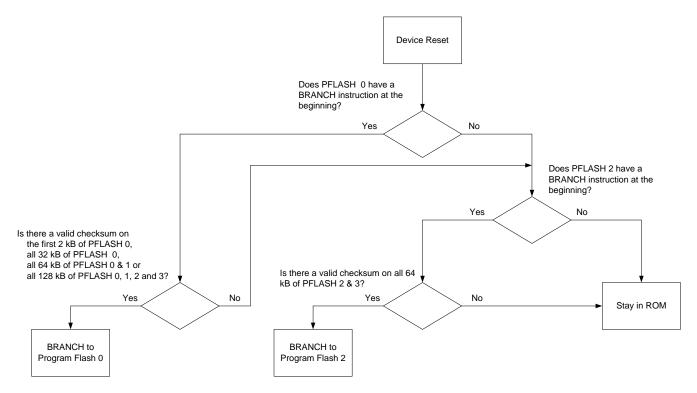

Here is a flowchart showing the order in which the ROM verifies the checksums:

}

The branch instruction check prevents the checksum program from looking at an empty block of memory. Otherwise a block filled with zeroes would pass the checksum test.

The UCD3138A64 doesn't have ROM support for putting 2 separate programs into flash, one in each flash block. This can still be done, however, using boot flash. Or the program in block 0 can be a fixed program, which checks the program in block 1 and jumps to it if appropriate.

# 4 Two Enhanced I2C/PMBus Interfaces

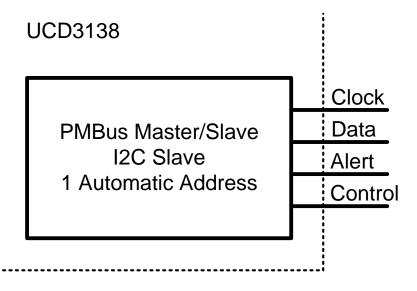

The UCD3138 has a single PMBus interface which supports master and slave modes for PMBus. It can also be used as an I2C slave.

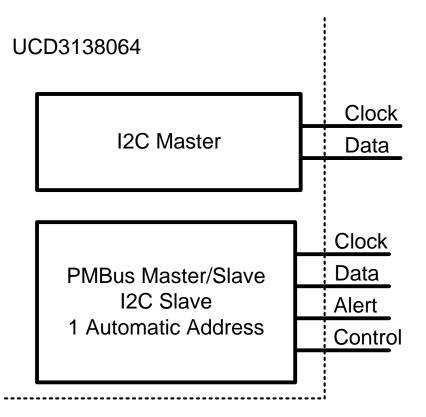

The UCD3138064 adds an I2C interface which can be used as a master for both I2C and PMBus. It does not support slave mode for either I2C or PMBus.

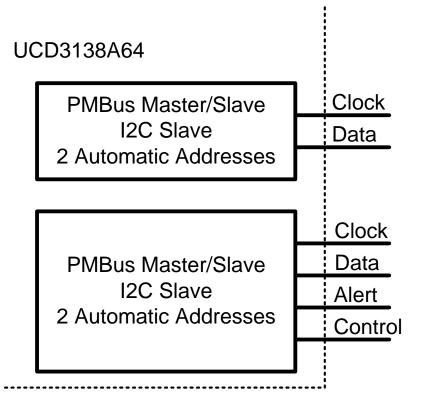

The UCD3138A64 has 2 essentially identical I2C/PMBus interfaces which support both master and slave modes. They also both support automatic acknowledgment of 2 addresses, making a total of 4 addresses in all. The previous devices only provided automatic acknowledgement of 1 address. The UCD3138A64 also provides enhanced fault handling for PMBus and I2C bus faults.

Only one of the interfaces supports the PMBus Alert and Control lines and IBIAS bits, but otherwise they are identical.

See the UCD3138 documentation for using the interfaces as PMBus slaves. The UCD3138064 manual describes how to use the I2C interface master mode with EEPROMS. Note that the I2C master mode is designed for use with EEPROMS. If other devices have unusual requirements for the placement of repeated start, they may not work.

#### 4.1 PMBus/I2C Register Names are Different on UCD3138064 and UCD3138A64

On the UCD3138064, the I2C port registers are called I2CRegs, and the individual register names have I2C in the first 3 letters, like "I2CCTRL1". The PMBus registers are very similar, except they are called PMBusRegs, and have PMB in the first 3 letters, like PMBCTRL1. The fields within the registers are very similar.

In the UCD3138A64, the registers are called PMBusRegs and PMBus1Regs, and all the register names start with PMB. To convert an I2C code from the UCD3138064 to the UCD3138A64, change all the "I2C"s to "PMB"s, and select either PMBus or PMBus1 regs. The bits related to Alert, Control, and IBIAS are duplicated in both register sets, but they are only implemented fully in PMBus. In PMBus1, they will not provide correct results, because they are not connected to pins.

#### 4.2 Automatic Acknowledgement of 2 Slave Addresses

The UCD3138A64 adds two additional bitfields to the PMBCTRL2 register, called SLAVE\_ADDR\_2\_EN and SLAVE\_ADDR\_2. If SLAVE\_ADDR\_2\_EN is set, the PMBus/I2C slave interface will acknowledge the address in SLAVE\_ADDR\_2 as well as the one in

SLAVE\_ADDR. To determine which address was acknowledged, read from the PMBHSA (PMBus Hold Slave Address) Register.

## 4.3 Alert and Control Support on PMBus

Both PMBus ports use the same register definitions for convenience, but on PMBus1 the bits relating to Alert and Control pins should be left in their default states. There is only one set of Alert and Control pins, and they are connected to PMBus 0.

### 4.4 Improved Clock High Timeout Handling

Reading the CLK\_HIGH\_TIMEOUT bit was not recommended in the earlier devices. On the UCD3138A64, this bit in the PMBST register will go high if the clock stays high for more than 55 milliseconds in the middle of a message. There is an added bit in the PMBINTM register as well to enable an interrupt for clock high timeout. There is also a CLK\_HI\_DIS bit in PMBCTRL3 which disables clock high timeout.

# 4.5 Improved Bit Counter Reset

On the UCD3138A64, messages can be stopped in the middle of a byte and the PMBus will recover. Anything which resets the PMBus state machine now resets the bit counter as well. Events which reset the state machine include: Start, Stop, Clock High Timeout, Clock Low Timeout, and setting the RESET bit in PMBCTRL3.

# 4.6 Change in Test Mode Address

On the UCD3138A64, there is still a PMBus/I2C address which will start to put the chip into test mode. On the earlier devices, the address is 0x7f. On the UCD3138A64, the address has been changed to 0x7e. This way if the clock line is active but the data line is released, the device will not go into test mode.

# 5 External Clock Controlled Real-Time Clock

The UCD3138064 adds a Real-Time clock controlled by an external 10 MHz clock source. This provides a precise reference for time measurement. It can also be used to adjust UART and DPWM frequencies for better frequency control. Here are the major features of the real time clock:

- Counts seconds, minutes, hours and days

- Digital trim of external frequency from -500 to +250 ppm in 0.8 ppm steps.

- Provides interrupts at 1 second, 10 seconds, 30 seconds and 60 seconds.

## 5.1 *Trimming the External Frequency*

The RTC is configured to count seconds based on a 10 MHz clock input. Changing the value in the RTCPRESCALE register can compensate for small variations in the clock frequency. The RTCPRESCALE register has a default value of 0x2CF. It can be varied from 0 to 0x3ff. Each step in the register value will compensate for a 0.8 ppm variation in the clock frequency.

Inside the RTC, the 10 MHz clock is first divided by 8, giving a nominal 1.25 MHz. This number is divided by 1,250,000 to give the 1 second interval. The number in the prescale register is actually 1,250,000 – 1. In hex, this is 0x1312CF. The PRESCALE register permits modification of the least significant 10 bits of this number. The higher bits are fixed. This permits digital compensation for crystal manufacturing variations.

The range goes from 0x131000 (9,994,240 Hz) to 0x1313FF (10,002,424 Hz). This provides +240, -570 ppm coverage for crystal variation.

## 5.2 RTC Calendar Data

The RTC provides simplified calendar data (seconds, minutes, hours, days) in the RTCCOUNT register. There are 11 bits for days, so up to 5.5 years of on-time can be recorded. If date, month and year are required, this is simple to determine in firmware.

The calendar data can be written to using the RTCPRESET register and the PRESET\_EN bit in the RTCCTRL register. Simply write the desired value to the RTCPRESET register and toggle the PRESET\_EN register high and then low. This will copy the value from the RTCPRESET to the RTCCOUNT register.

### 5.3 RTC Polling and Interrupts

The RTC has two registers for polling and interrupts:

RTCINTEN – enables interrupts

RTCINTSTAT - Shows which interrupts are active

The RTC sets bits in the RTCINTSTAT registers every 1, 10, 30, and 60 seconds. These bits are set even if the corresponding bits in the RTCINTEN register are not set. The RTCINTSTAT bits are clear on read.

There is a bit in the RTCINTEN register for every bit in the RTCINTSTAT register. If the bit in RTCINTEN is set, it enables an interrupt for the corresponding bit in RTCINTSTAT.

# 6 Four Additional General Purpose I/O Pins

The UCD3138A64 adds 4 General Purpose I/O pins, GPIOA through GPIOD. They are configured in the FAULTDIR, FAULTIN, and similar registers. They can be inputs or outputs, and can trigger interrupts just like fault pins. However, they cannot be used as fault inputs to the DPWMs. There are no bits associated with the GIO pins in the various FAULTDET registers. So they are best used as simple general purpose I/O registers.

# 7 SPI Port Pins Move Around – JTAG\_MUX\_SEL Bit

The TAG\_MUX\_SEL bit in the MiscAnalogRegs.IOMUX register provides a way to disable JTAG to preserve code security. It has a side effect of moving the SPI bits to different pins. There is a way to provide both code security and keep the SPI on the same pins.

If JTAG is disabled, the SPI bits are moved to the JTAG pins. Depending on the state of the flash at chip reset, this bit can be either a zero or a one.

1. If flash memory has a valid checksum and ROM jumps directly to flash, the bit will be a 1, JTAG will be disabled, and the SPI function will appear on the JTAG pins

TCK -> SPI\_CLK TMS -> SPI\_CS TDI -> SPI\_MISO TDO -> SPI\_MOSI

2. If flash memory does not have a valid checksum, the ROM will stay in ROM, and the bit will be a 0. JTAG will be enabled and the SPI function will appear on the SPI pins.

There is a way to keep the pinout the same for both cases and still preserve code security.

- 1. In the debug code, simply enable JTAG and use it for debugging

- 2. In the production code, use the GLBIO registers to map the JTAG pins as outputs before enabling JTAG. This way the SPI will stay on the SPI pins and the JTAG will be disabled.

# 8 One Additional Timer Capture Register

The UCD3138A64 adds a second timer capture register with its associated hardware This added register makes it much easier to measure pulse width (by setting one register to capture the rising edge and one to capture the falling edge). It makes it easier to measure the relationship of any edge to any other edge, or to measure two independent edges. This requires several changes to the timer registers:

- T24CAPDAT and T24CAPCTRL are duplicated and numbered 0 and 1.

- T24CAPIO gets additional bits to control TCAP1

# 9 Support for Fixed Sampling Rates for LLC

The UCD3138A64 has modified DPWM logic. With the earlier UCD31XX parts, LLC programs had to sample at the LLC switching frequency to avoid pulse extension. The UCD3138A64 permits sampling at a fixed rate, as high as 2 MHz, which permits consistent filter bandwidth across the load range. As a result of this change, however, the DPWM takes longer to calculate its edges for the current switching cycle. Moving edges into or out of this calculation window may result in pulse extension. This window is enlarged to 120 ns on the UCD3138A64.

For implementation details on fixed sample rates for LLC, please see the TI LLC Reference Program.

# **10** Information on Pulse Width in Peak Current Mode

The UCD3138A64 adds the DPWMCBCLOCATION register to the DPWM registers. In Peak Current mode, and in any other mode where the cycle-by-cycle (CBC) signal is used, this register will contain the DPWM period counter value at which the last CBC occurred. In Peak

Current mode, this will give the pulse width for the previous switching cycle. This counter value is in low resolution, meaning that each count represents 4 nsec.

This value can be used to place the sample trigger near the center of the FET on-time, making it possible to measure average current. See the EVM firmware for specific topologies for more information.

# 11 Improvements to Fault Handling and Burst Mode

The UCD3138A64 adds 3 enhancements to the UCD31xx fault handling:

- Fault counter goes from 5 bits to 7 bits

- Blanking can be extended to the CBC Fault by setting a bit.

- All DPWM lines are turned off by a fault, even if the Edge Generator is being used (PSFB topology, for example)

- This also helps with hardware burst mode for PSFB because it uses the same shut-down mechanism as the fault does.

### 11.1 Fault Counter Changes from 5 to 7 Bits

The UCD31XX family has sophisticated fault handling logic. For a detailed description of this logic, see the UCD3138 Digital Power Peripherals Programmer's Manual.

There are several fault signals which latch off the DPWM when a fault occurs. To restart the DPWM, the DPWM must be disabled and reenabled. All of these fault signals have a count value in a register. For the fault to be triggered, x consecutive switching cycles have to have the fault signal occur, where x is the value in the count register plus 1. On the UCD3138 and UCD3138064, the maximum count value is 32. On the UCD3138A64, the maximum value is 128. See Section 20.8.15 DPWM Fault Control Register (DPWMFLTCTRL) for the specific bitfields involved.

# 11.2 Blanking for the Cycle-by-Cycle Fault Added

In addition to the faults described above, there is also one signal called CBC (Cycle By Cycle), which turns the DPWM off for the remainder of the switching cycle, but permits it to turn on again at the beginning of the next cycle. Unlike the faults, the CBC does not latch the DPWM off permanently. This signal is typically used for current limiting, but is also used for peak current mode.

The CBC signal can be blanked with 2 blanking periods set by the blank a and blank b registers in the DPWM.

There is also something called the CBC fault. The CBC fault uses the same CBC signal which is used for the CBC non-latching DPWM shutdown. The CBC fault, however, has a count register and will latch the DPWM off when the count is exceeded. This is useful for two stage current limiting. The non-latching CBC can be used for a short time, but if it happens for (for example) for 100 consecutive switching cycles, the CBC fault can be used to latch the DPWM off.

On the UCD3138 and UCD3138064, the blanking only works on the non-latching CBC logic. The latching CBC fault has no blanking. With the UCD3138A64, setting the new CBC\_FAULT\_MODE bit in the DPWMFLTCTRL register enables blanking for the CBC fault too. Leaving CBC\_FAULT\_MODE as the default zero value makes the UCD3138A64 function just like the other UCD31xx parts, with no blanking for the latched CBC fault.

# 11.3 Improved Fault and Burst Mode with Edge Generator in Use

On previous devices, the fault logic worked on the DPWM outputs before the edge generator logic. This meant that sometimes one of the 4 FET control lines for PSFB (Phase Switching Full Bridge) would not be turned off right away, and firmware would be required to turn it off. The same was true of the hardware burst or light load mode. When the burst was over, sometimes one of the lines would not be turned off automatically.

Now the fault logic has been extended past the edge generation logic, so that all 4 lines are turned off immediately by a fault or by burst mode. There are no register changes associated with this enhancement.

# 12 Eighty Pins Instead of 64

The UCD3138A64 is available in an 80 pin package instead of a 64 pin one. This makes it possible to have 4 more general purpose I/O pins. In addition, the second PMBus/I2C bus and the SPI bus are no longer multiplexed, but now have dedicated pins. This has caused significant changes to the IOMUX register. Consult the IOMUX register reference below and the pinout in the data sheet for more information.

Pins have been added so that the output of Timers 2 and 3 are available for PWM and general purpose I/O. There is also a second capture pin to go with the second capture register

All of this has caused changes in the global I/O registers. The Timer 2 and 3 pins have been added to global I/O, as has the capture 1 pin. What was the capture pin has been renamed to be capture 0.

To make room for capture 1, the PMBus clock pin has been removed from global I/O. The PMBus data pin has been replaced by the I2C data pin in all the global I/O registers.

# 13 Disabling the RESET Pin

On the UCD3138A64, it is possible to disable the RESET pin. This may be useful in very noisy

systems. If the RESET pin is disabled, the only way to reset the UCD3138A64 with hardware is

to remove power from the device. Of course software reset, or reenabling the reset pin is possible in firmware. Here is the code to disable the reset:

MiscAnalogRegs.CLKTRIM.bit.RESET\_DISABLE = 1;

# 14 Adjusting the Clock Speed

The UCD3138A64 is designed to make it possible to change the clock speed for the processor and the peripherals. The main clock is called the HFO (High Frequency Oscillator), and all other clocks except for the RTC are derived from the HFO.

There are two clock speed control bitfields, HFO\_FINE\_TRIM and HFO\_COARSE\_TRIM. Here is how to write to them:

MiscAnalogRegs.CLKTRIM.bit.HFO\_COARSE\_TRIM = x; MiscAnalogRegs.CLKTRIM.bit.HFO\_FINE\_TRIM = y; When each device is tested, the correct values for these registers are determined. The device will power up with the optimal values. By adjusting the trim registers and comparing the HFO clock to the RTC clock or some other precise reference, it is possible to make the clock more accurate over the temperature range.

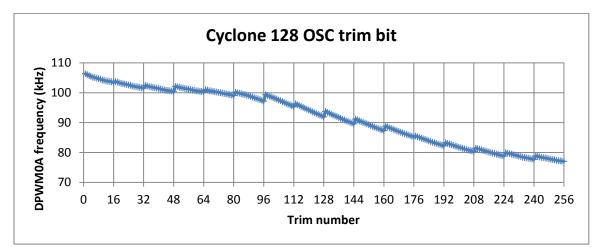

The coarse and fine trim registers are monotonic as individual registers, but the same does not apply if the coarse and fine trim registers are used together. The range of the fine trim register is bigger than the size of a coarse trim register step. And the two registers will not necessarily align the same way on different devices. Any firmware which modifies the clock trim fields will have to take this into account. The graph below shows an example of clock speed variation. The vertical axis is DPWM frequency with a nominal value of 100 KHz. The horizontal axis is a number which combines fine and coarse trim into one. Every 16 steps, the fine trim goes from its minimum to its maximum value, and the coarse trim is incremented by 1. Since the fine trim overlaps more than 1 coarse trim step, there is a non-monotonicity in the combined numbers. Clock adjustment firmware needs to account for this variation.

# 15 No Write to HFO\_LN\_FILTER\_EN

The clock filter logic has also been changed, so it is no longer necessary to put this statement into the program:

MiscAnalogRegs.CLKTRIM.bit.HFO\_LN\_FILTER\_EN = 0;

The clock filter is handled as part of the trim process, and should not be modified by the customer.

# 16 Unused bits Removed from DPWM Registers

There are several bits and mode settings which were removed from the DPWM registers. These bits were removed because they were always set to the same values in all applications. All writes to them in initialization codes from older devices can be removed.

# 17 Sample and Hold Buffer Available on ADC even if Sample and Hold are Not Used

The ADC12 has a small capacitor which is charged at the beginning of every sample. This means that the output impedance of anything driving the ADC has to be relatively low to ensure ADC accuracy. The sample and hold feature requires a larger sample and hold capacitor to be

charged to retain the voltage until the next sampling cycle. This is done to provide simultaneous sampling for functions like power measurement.

This function works exactly the same on the UCD3138A64 as it does on the earlier models of the UCD31xx.

On the new devices, it is possible to use the buffer even if the sample and hold function is not being used. This makes it possible to use 1 of 3 ADC inputs for a voltage source with a higher impedance. To use this, there are several steps:

- 3. Select the ADC channel which will be buffered by writing to the BYPASS\_EN bits in ADCCTRL.

- 011 = Channel 2

- 101 = Channel 1

- 110 = Channel 0

.

- 4. Make sure that there are no SEQx\_SH bits set

- 5. Set the ADC\_SH\_BUFFER\_EN bit in ADCTSTCTRL

This should provide a buffer on the selected channel, but no sample and hold functionality.

# **18 DAC Dither on Sample Trigger**

The UCD3138A64 devices add a new bit in the EADCDAC register called DAC\_DITHER\_ON\_SAMPLE. This bit causes the EADC DAC to dither on the sample trigger. Normally the DAC dithers on the frame sync, so dither takes place only once every switching cycle. This means that the dither frequency will be 1/16<sup>th</sup> the switching frequency. If the sample trigger is set to oversample, the dither could move to 8, 4, or 2 times the switching frequency, providing faster dither.

# **19 Consolidation of PCM Control Registers**

Earlier devices had a PCMCTRL register with only one bitfield in it – FILTER\_SEL. The other peak current mode bitfields were in APCMCTRL. Now all the relevant bits are in APCMCTRL, and PCMCTRL has been removed.

# 20 Enhancements for UCD3138128

The UCD3138128 is very similar to the UCD3138A64. The only difference is the addition of 2 more 32K byte Flash blocks along with the extra registers and boot ROM support for the 2 more blocks. The additional blocks of boot flash are called Block 2 and Block 3.

#### 20.1 Added Flash Memory

Blocks 2 and 3 are added after Blocks 0 and 1 in ROM mode. In Flash mode, either blocks 0 and 1 or blocks 2 and 3 can be placed starting at zero. The RAM and peripherals are all at the same addresses as they are on the A64. The Flash mapping options are shown below:

## 20.2 Changes to ROM Boot Program

The ROM changes the response to the version command, and it also changes the handling of flash checksums when it powers up.

#### 20.2.1 ROM Version

The UCD3138128 will return a 0005 as the first half of the version, indicating the device. The first version of the ROM will return a 0001 as the second half of the version, indicating version 1 of the ROM. If other versions of the ROM are produced, the number will increment.

#### 20.2.2 Flash Checksum Handling

The UCD3138128 does checksums for the first 2K, 32K and 64K of program flash just like the 'A64. It adds checksums for the second 64K and for the full 128K. This provides Boot ROM support for 2 independent versions of the firmware in a single device.

The checksums and their locations are:

0x7f8 – Boot block for Block 0 0x7ff8 – Overall checksum for Block 1 0xfff8 – Overall checksum for a 64K program combining Blocks 1 and 2 0x1fff8 – Overall checksum for a 128K program. This is also used for a 64K program using blocks 2 and 3.

The locations above assume that Block 0 is mapped to location 0, Block 1 is at 0x8000, Block 2 is at 0x10000, and Block 3 is mapped to 0x18000.

Here is a flowchart showing the order in which the ROM verifies the checksums:

The branch instruction check prevents the checksum program from looking at an empty block of memory. Otherwise a block filled with zeroes would pass the checksum test.

Copyright © 2014, Texas Instruments Incorporated

When the flowchart says "Branch to Program Flash 0", this means that it puts block 0 at location 0, block 1 at 0x8000, block 2 at 0x10000, and block 3 at 0x18000 and branches to location 0. For ""Branch to Program Flash 2", it puts Block 2 at 0, block 3 at 0x8000, block 0 at 0x10000, and block 1 at 0x18000. It always branches to zero.

The UCD3138 has a PMBus command code 0xF0 which causes the program to execute. On the UCD3138128, the same command causes Blocks 0 and 1 to be placed starting at address 0 and starts execution. A 0xF7 command has been added which puts Blocks 2 and 3 starting at location 0 and starts executing there.

### 20.3 Registers Added for '128

The addition of Blocks 2 and 3 also requires the addition of more registers to control those blocks. Here is a list of the registers:

| Register Name | Function                                  | Flash Block Controlled |

|---------------|-------------------------------------------|------------------------|

| PFLASHCTRL_2  | Program Flash Control Register 2          | 2                      |

| PFLASHCTRL_3  | Program Flash Control Register 3          | 3                      |

| MFBAHR18      | Memory Fine Base Address High Register 18 | 2                      |

| MFBALR18      | Memory Fine Base Address Low Register 18  | 2                      |

| MFBAHR19      | Memory Fine Base Address High Register 19 | 3                      |

| MFBALR19      | Memory Fine Base Address Low Register 19  | 3                      |

# 20.4 Additional FLASH Keys

There are additional flash keys for the two new blocks:

#### #define PROGRAM\_FLASH2\_INTERLOCK\_KEY 0x184219b3 #define PROGRAM\_FLASH3\_INTERLOCK\_KEY 0x5973ef21

These keys need to be written to the DecRegs.FLASHILOCK register before writing or erasing the respective flash blocks.

# 21 UCD3138A64 Memory Map

This section describes all the registers in the UCD3138A64 peripherals. Changes from the UCD3138064 are marked in green.

#### 21.1 Loop Mux Registers

#### 21.1.1 Front End Control 0 Mux Register (FECTRL0MUX)

| Address 00120000 |        |                     |

|------------------|--------|---------------------|

| Bit Number       | 13:12  | 11                  |

| Bit Name         | NL_SEL | DPWM3_FRAME_SYNC_EN |

| Access           | R/W    | R/W                 |

| Default          | 00     | 0                   |

| Bit Number | 10                  | 9                   |

|------------|---------------------|---------------------|

| Bit Name   | DPWM2_FRAME_SYNC_EN | DPWM1_FRAME_SYNC_EN |

Copyright © 2016, Texas Instruments Incorporated

Default

0

0

| Access     | R/W                 |      |             | R/W             |

|------------|---------------------|------|-------------|-----------------|

| Default    | 0                   |      | 0           |                 |

|            |                     |      |             |                 |

| Bit Number | 8                   |      | 7           | 6               |

| Bit Name   | DPWM0_FRAME_SYNC_EN | DPWN | 3_B_TRIG_EN | DPWM2_B_TRIG_EN |

| Access     | R/W                 |      | R/W         | R/W             |

| Bit Number | 5               | 4               | 3               |

|------------|-----------------|-----------------|-----------------|

| Bit Name   | DPWM1_B_TRIG_EN | DPWM0_B_TRIG_EN | DPWM3_A_TRIG_EN |

| Access     | R/W             | R/W             | R/W             |

| Default    | 0               | 0               | 0               |

| Bit Number | 2               | 1               | 0               |

|------------|-----------------|-----------------|-----------------|

| Bit Name   | DPWM2_A_TRIG_EN | DPWM1_A_TRIG_EN | DPWM0_A_TRIG_EN |

| Access     | R/W             | R/W             | R/W             |

| Default    | 0               | 0               | 0               |

**Bits 13-12: NL\_SEL** – Configures source of Non-Linear (NL) comparison results used in Automatic Gain Shifting

0 = Filter 0 NL Results used

0

1 = Filter 1 NL Results used

2 = Filter 2 NL Results used (Default)

**Bit 11: DPWM3\_FRAME\_SYNC\_EN** – Enables DPWM Trigger from DPWM 3 Frame Sync to Front End Control

0 = DPWM 3 Frame Sync not routed to Front End Control (Default)

1 = DPWM 3 Frame Sync routed to Front End Control

**Bit 10: DPWM2\_FRAME\_SYNC\_EN** – Enables DPWM Trigger from DPWM 2 Frame Sync to Front End Control