## TMS320C20x User's Guide

Literature Number: SPRU127C April 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

#### **Preface**

### **Read This First**

#### About This Manual

This user's guide describes the architecture, hardware, assembly language instructions, and general operation of the TMS320C20x† digital signal processors (DSPs). This manual can also be used as a reference guide for developing hardware and/or software applications. In this document, 'C20x† refers to any of the TMS320C20x devices, except where device-specific information is explicitly stated. When device-specific information is given, the device name may be abbreviated; for example, TMS320C203 will be abbreviated as 'C203. This manual covers 'C203, 'LC203, 'C206, 'LC206, and 'F206 devices. For pinouts, electrical characteristics, and timing diagrams, refer to the data sheets of the individual devices.

#### How to Use This Manual

Chapter 1, *Introduction*, summarizes the TMS320 family of products and then introduces the key features of the TMS320C20x generation of that family. Chapter 2, *Architectural Overview*, summarizes the 'C20x architecture, providing information about the CPU, bus structure, memory, on-chip peripherals, and scanning logic.

If you are reading this manual to learn about the 'C209, Chapter 11 is important for you. There are some notable differences between the 'C209 and other 'C20x devices, and Chapter 11 explains these differences. In addition, it shows how to use this manual to get a complete picture of the 'C209.

The following table points you to major topics.

<sup>†</sup> The generic name '2xx refers to all DSPs using the 2xLP DSP core. This user guide revision uses '20x, a subset of '2xx, to specifically reference the 'C/LC203, 'F206, and the C/LC206.

| For this information:                                                       | Look here:                                                                 |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Addressing modes (for addressing data memory)                               | Chapter 6, Addressing Modes                                                |

| Assembly language instructions                                              | Chapter 7, Assembly Language<br>Instructions                               |

| Assembly language instructions of TMS320C1x, 'C2x, 'C20x, and 'C5x compared | Appendix C,<br>TMS320C1x/C2x/C2xx/C5x<br>Instruction Set Comparison        |

| Boot loader                                                                 | Chapter 4, Memory and I/O Spaces                                           |

| Clock generator                                                             | Chapter 8, On-Chip Peripherals                                             |

| CPU                                                                         | Chapter 3, Central Processing Unit                                         |

| Custom ROM from TI                                                          | Appendix E, Submitting ROM Codes to TI                                     |

| Emulator                                                                    | Appendix F, Design Considerations for Using XDS510 Emulator                |

| Features                                                                    | Chapter 1, Introduction Chapter 2, Architectural Overview                  |

| Input/output ports                                                          | Chapter 4, Memory and I/O Spaces                                           |

| Interrupts                                                                  | Chapter 5, Program Control                                                 |

| Memory configuration                                                        | Chapter 4, Memory and I/O Spaces                                           |

| Memory interfacing                                                          | Chapter 4, Memory and I/O Spaces                                           |

| On-chip peripherals                                                         | Chapter 8, On-Chip Peripherals                                             |

| Pipeline                                                                    | Chapter 5, Program Control                                                 |

| Program control                                                             | Chapter 5, Program Control                                                 |

| Program examples                                                            | Appendix D, Program Examples                                               |

| Program-memory address generation                                           | Chapter 5, Program Control                                                 |

| Registers summarized                                                        | Appendix A, Register Summary                                               |

| Serial ports                                                                | Chapter 9, Synchronous Serial Port<br>Chapter 10, Asynchronous Serial Port |

| Stack                                                                       | Chapter 5, Program Control                                                 |

| Status registers                                                            | Chapter 5, Program Control                                                 |

| Timer                                                                       | Chapter 8, On-Chip Peripherals                                             |

| TMS320C209 differences and similarities                                     | Chapter 11, <i>TMS320C209</i>                                              |

| Wait-state generator                                                        | Chapter 8, On-Chip Peripherals                                             |

#### **Notational Conventions**

This document uses the following conventions:

Program listings and program examples are shown in a special typeface.

Here is a segment of a program listing:

```

OUTPUT LDP #6 ;select data page 6

BLDD #300, 20h ;move data at address 300h to 320h

RET

```

☐ In syntax descriptions, **bold** portions of a syntax should be entered as shown; *italic* portions of a syntax identify information that you specify. Here is an example of an instruction syntax:

**BLDD** source, destination

**BLDD** is the instruction mnemonic, which must be typed as shown. You specify the two parameters, *source* and *destination*.

□ Square brackets ([and]) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you do not type the brackets themselves. You separate each optional operand from required operands with a comma and a space. Here is a sample syntax:

BLDD source, destination [, ARn]

**BLDD** is the instruction. The two required operands are *source* and *destination*, and the optional operand is ARn. AR is bold and n is italic; if you choose to use ARn, you must type the letters A and R and then supply a chosen value for n (in this case, a value from 0 to 7). Here is an example:

```

BLDD *, #310h, AR3

```

#### Information About Cautions

This book contains cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

The information in a caution is provided for your protection. Please read each caution carefully.

#### Related Documentation From Texas Instruments

This section describes related TI<sup>™</sup> documents that can be ordered by calling the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the document by its title and literature number.

The following data sheets contain the electrical and timing specifications for the TMS320C20x devices, as well as signal descriptions and pinouts for all of the available packages:

TMS320C20x data sheets (literature number SPRS025 and SPRS065)

TMS320F20x data sheet (literature number SPRS050). This data sheet covers the TMS320F20x devices that have on-chip flash memory.

The books listed below provide additional information about using the TMS320C2xx devices and related support tools, as well as more general information about using the TMS320 family of DSPs.

- TMS320C1x/C2x/C2xx/C5x Code Generation Tools Getting Started Guide (literature number SPRU121) describes how to install the TMS320C1x, TMS320C2x, TMS320C2xx, and TMS320C5x assembly language tools and the C compiler for the 'C1x, 'C2x, 'C2xx, and 'C5x devices. The installation for MS-DOS™, OS/2™, SunOS™, and Solaris™ systems is covered.

- TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User's Guide (literature number SPRU018) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C1x, 'C2x, 'C2xx, and 'C5x generations of devices.

- TMS320C2x/C2xx/C5x Optimizing C Compiler User's Guide (literature number SPRU024) describes the 'C2x/C2xx/C5x C compiler. This C compiler accepts ANSI standard C source code and produces TMS320 assembly language source code for the 'C2x, 'C2xx, and 'C5x generations of devices.

- **TMS320C2xx PC Emulator Installation Guide** (literature number SPRU152) describes the installation of the XDS510 PC emulator and the C source debugger for OS/2 and MS-Windows operating systems.

- TMS320C2xx C Source Debugger User's Guide (literature number SPRU151) tells you how to invoke the 'C2xx emulator and simulator versions of the C source debugger interface. This book discusses various aspects of the debugger interface, including window management, command entry, code execution, data management, and breakpoints. It also includes a tutorial that introduces basic debugger functionality.

- TMS320C2xx Simulator Getting Started (literature number SPRU137) describes how to install the TMS320C2xx simulator and the C source debugger for the 'C2xx. The installation for MS-DOS™, PC-DOS™, SunOS™, Solaris™, and HP-UX™ systems is covered.

- **TMS320C2xx Emulator Getting Started Guide** (literature number SPRU209) tells you how to install the Windows™ 3.1 and Windows™ 95 versions of the 'C2xx emulator and C source debugger interface.

- **XDS51x** Emulator Installation Guide (literature number SPNU070) describes the installation of the XDS510<sup>™</sup>, XDS510PP<sup>™</sup>, and XDS510WS<sup>™</sup> emulator controllers. The installation of the XDS511<sup>™</sup> emulator is also described.

- JTAG/MPSD Emulation Technical Reference (literature number SPDU079) provides the design requirements of the XDS510™ emulator controller, discusses JTAG designs (based on the IEEE 1149.1 standard), and modular port scan device (MPSD) designs.

- TMS320 DSP Development Support Reference Guide (literature number SPRU011) describes the TMS320 family of digital signal processors and the tools that support these devices. Included are code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). Also covered are available documentation, seminars, the university program, and factory repair and exchange.

- Digital Signal Processing Applications with the TMS320 Family, Volumes 1, 2, and 3 (literature numbers SPRA012, SPRA016, SPRA017) Volumes 1 and 2 cover applications using the 'C10 and 'C20 families of fixed-point processors. Volume 3 documents applications using both fixed-point processors as well as the 'C30 floating-point processor.

- **TMS320 DSP Designer's Notebook: Volume 1** (literature number SPRT125). Presents solutions to common design problems using 'C2x, 'C3x, 'C4x, 'C5x, and other TI DSPs.

- TMS320 Third-Party Support Reference Guide (literature number SPRU052) alphabetically lists over 100 third parties that provide various products that serve the family of TMS320 digital signal processors. A myriad of products and applications are offered—software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

#### Related Articles

"A Greener World Through DSP Controllers", Panos Papamichalis, *DSP & Multimedia Technology*, September 1994.

"A Single-Chip Multiprocessor DSP for Image Processing—TMS320C80", Dr. Ing. Dung Tu, *Industrie Elektronik*, Germany, March 1995.

"Application Guide with DSP Leading-Edge Technology", Y. Nishikori, M. Hattori, T. Fukuhara, R.Tanaka, M. Shimoda, I. Kudo, A.Yanagitani, H. Miyaguchi, et al., *Electronics Engineering*, November 1995.

"Approaching the No-Power Barrier", Jon Bradley and Gene Frantz, *Electronic Design*, January 9, 1995.

"Beware of BAT: DSPs Add Brilliance to New Weapons Systems", Panos Papamichalis, DSP & Multimedia Technology, October 1994.

"Choose DSPs for PC Signal Processing", Panos Papamichalis, *DSP & Multimedia Technology*, January/February 1995.

"Developing Nations Take Shine to Wireless", Russell MacDonald, Kara Schmidt and Kim Higden, *EE Times*, October 2, 1995.

"Digital Signal Processing Solutions Target Vertical Application Markets", Ron Wages, *ECN*, September 1995.

"Digital Signal Processors Boost Drive Performance", Tim Adcock, *Data Storage*, September/October 1995.

"DSP and Speech Recognition, An Origin of the Species", Panos Papamichalis, *DSP & Multimedia Technology*, July 1994.

"DSP Design Takes Top-Down Approach", Andy Fritsch and Kim Asal, *DSP Series Part III*, *EE Times*, July 17, 1995.

"DSPs Advance Low-Cost 'Green' Control", Gregg Bennett, *DSP Series Part II*, *EE Times*, April 17, 1995.

"DSPs Do Best on Multimedia Applications", Doug Rasor, *Asian Computer World*, October 9–16, 1995.

"DSPs: Speech Recognition Technology Enablers", Gene Frantz and Gregg Bennett, *I&CS*, May 1995.

"Easing JTAG Testing of Parallel-Processor Projects", Tony Coomes, Andy Fritsch, and Reid Tatge, *Asian Electronics Engineer*, Manila, Philippines, November 1995.

"Fixed or Floating? A Pointed Question in DSPs", Jim Larimer and Daniel Chen, *EDN*, August 3, 1995.

"Function-Focused Chipsets: Up the DSP Integration Core", Panos Papamichalis, DSP & Multimedia Technology, March/April 1995.

"GSM: Standard, Strategien und Systemchips", Edgar Auslander, *Elektronik Praxis*, Germany, October 6, 1995.

"High Tech Copiers to Improve Images and Reduce Paperwork", Karl Guttag, *Document Management*, July/August 1995.

"Host-Enabled Multimedia: Brought to You by DSP Solutions", Panos Papamichalis, *DSP & Multimedia Technology*, September/October 1995.

"Integration Shrinks Digital Cellular Telephone Designs", Fred Cohen and Mike McMahan, *Wireless System Design*, November 1994.

"On-Chip Multiprocessing Melds DSPs", Karl Guttag and Doug Deao, *DSP Series Part III*, *EE Times*, July 18, 1994.

"Real-Time Control", Gregg Bennett, Appliance Manufacturer, May 1995.

"Speech Recognition", P.K. Rajasekaran and Mike McMahan, *Wireless Design & Development*, May 1995.

"Telecom Future Driven by Reduced Milliwatts per DSP Function", Panos Papamichalis, *DSP & Multimedia Technology*, May/June 1995.

"The Digital Signal Processor Development Environment", Greg Peake, *Embedded System Engineering*, United Kingdom, February 1995.

"The Growing Spectrum of Custom DSPs", Gene Frantz and Kun Lin, *DSP Series Part II*, *EE Times*, April 18, 1994.

"The Wide World of DSPs," Jim Larimer, Design News, June 27, 1994.

"Third-Party Support Drives DSP Development for Uninitiated and Experts Alike", Panos Papamichalis, *DSP & Multimedia Technology*, December 1994/January 1995.

"Toward an Era of Economical DSPs", John Cooper, *DSP Series Part I, EE Times*, Jan. 23, 1995.

#### **Trademarks**

TI, 320 Hotline On-line, XDS510, XDS510PP, XDS510WS, and XDS511 are trademarks of Texas Instruments Incorporated.

HP-UX is a trademark of Hewlett-Packard Company.

Intel is a trademark of Intel Corporation.

MS-DOS and Windows are registered trademarks of Microsoft Corporation.

PAL® is a registered trademark of Advanced Micro Devices, Inc.

OS/2, PC, and PC-DOS are trademarks of International Business Machines Corporation.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

#### If You Need Assistance. . .

| World-Wide Web Sites                                         |                      |                                                             |

|--------------------------------------------------------------|----------------------|-------------------------------------------------------------|

| TI Online                                                    | http://www.ti.com    | 2                                                           |

|                                                              | http://www.ti.con    | n/sc/docs/pic/home.htm                                      |

| Semiconductor Product Information Center (PIC) DSP Solutions | http://www.ti.con    | ·                                                           |

| 320 Hotline On-line™                                         |                      | n/sc/docs/dsps/support.htm                                  |

| 320 Hottille Off-life                                        | Tittp://www.ti.com   | n/sc/docs/dsps/support.nun                                  |

| North America, South America, Cer                            | ntral America        |                                                             |

| Product Information Center (PIC)                             | (972) 644-5580       |                                                             |

| TI Literature Response Center U.S.A.                         | (800) 477-8924       |                                                             |

| Software Registration/Upgrades                               | (214) 638-0333       | Fax: (214) 638-7742                                         |

| U.S.A. Factory Repair/Hardware Upgrades                      | (281) 274-2285       |                                                             |

| U.S. Technical Training Organization                         | (972) 644-5580       |                                                             |

| DSP Hotline                                                  |                      | Email: dsph@ti.com                                          |

| DSP Internet BBS via anonymous ftp to ftp://ftp              | .ti.com/pub/tms320   | 0bbs                                                        |

| Europe, Middle East, Africa                                  |                      |                                                             |

| European Product Information Center (EPIC) H                 | lotlines:            |                                                             |

| Multi-Language Support +                                     | 33 1 30 70 11 69     | Fax: +33 1 30 70 10 32                                      |

| Email: epic@ti.com                                           |                      |                                                             |

| Deutsch +49 8161 80 33 11 or +                               |                      |                                                             |

| 3 -                                                          | 33 1 30 70 11 65     |                                                             |

|                                                              | 33 1 30 70 11 64     |                                                             |

|                                                              | 33 1 30 70 11 67     |                                                             |

|                                                              | 33 1 30 70 11 99     |                                                             |

|                                                              | 33 4 93 22 25 40     | F 40.04.04.00.40.40                                         |

| Europe Customer Training Helpline                            |                      | Fax: +49 81 61 80 40 10                                     |

| Asia-Pacific                                                 |                      |                                                             |

| Literature Response Center                                   | +852 2 956 7288      | Fax: +852 2 956 2200                                        |

| Hong Kong DSP Hotline                                        | +852 2 956 7268      | Fax: +852 2 956 1002                                        |

| Korea DSP Hotline                                            | +82 2 551 2804       | Fax: +82 2 551 2828                                         |

| Korea DSP Modem BBS                                          | +82 2 551 2914       |                                                             |

| Singapore DSP Hotline                                        |                      | Fax: +65 390 7179                                           |

|                                                              | +886 2 377 1450      | Fax: +886 2 377 2718                                        |

|                                                              | +886 2 376 2592      |                                                             |

| Taiwan DSP Internet BBS via anonymous ftp to                 | ttp://dsp.ee.tit.edu | ı.tw/pub/TI/                                                |

| Japan                                                        |                      |                                                             |

| Product Information Center +0120-81-                         | -0026 (in Japan)     | Fax: +0120-81-0036 (in Japan)                               |

| +03-3457-0972 or (INTL                                       | ) 813-3457-0972      | Fax: +03-3457-1259 or (INTL) 813-3457-1259                  |

| DSP Hotline +03-3769-8735 or (INTL                           | ,                    | Fax: +03-3457-7071 or (INTL) 813-3457-7071                  |

| DSP BBS via Nifty-Serve                                      | Type "Go TIASP"      |                                                             |

| Documentation                                                |                      |                                                             |

| When making suggestions or reporting errors in               | documentation, ple   | ease include the following information that is on the title |

| page: the full title of the book, the publication da         |                      | S S S S S S S S S S S S S S S S S S S                       |

| Mail: Texas Instruments Incorporated                         |                      | Email: dsph@ti.com                                          |

| Technical Documentation Services, M                          | MS 702               |                                                             |

| P.O. Box 1443                                                |                      |                                                             |

| Houston, Texas 77251-1443                                    |                      |                                                             |

|                                                              |                      |                                                             |

**Note:** When calling a Literature Response Center to order documentation, please specify the literature number of the book.

## **Contents**

| 1 | Introduction                                                                                                                                                                                                               |                            |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1 TMS320 Family                                                                                                                                                                                                          | 1-4                        |

| 2 | Architectural Overview                                                                                                                                                                                                     |                            |

|   | 2.1 'C20x Bus Structure 2.2 Central Processing Unit 2.3 Memory and I/O Spaces 2.4 Program Control 2.5 On-Chip Peripherals 2.6 Scanning-Logic Circuitry                                                                     | 2-5<br>2-7<br>2-10<br>2-11 |

| 3 | Central Processing Unit                                                                                                                                                                                                    | ,                          |

|   | 3.1 Input Scaling Section                                                                                                                                                                                                  | 3-5<br>3-8<br>3-12         |

| 4 | Memory and I/O Spaces  Describes the configuration and use of the TMS320C20x memory and I/O spaces. Includes memory/address maps and descriptions of the HOLD (direct memory access) operation and the on-chip bootloader. | S                          |

|   | 4.1 Overview of the Memory and I/O Spaces 4.2 Program Memory 4.3 Local Data Memory 4.4 Global Data Memory 4.5 I/O Space 4.6 Direct Memory Access Using the HOLD Operation                                                  | 4-5<br>4-7<br>4-11<br>4-14 |

|   | 4.7 Device-Specific Information                                                                                                                                                                                            | 4-22<br>4-30               |

| 5 | Program Control                                                                                                                                                                                                               | οw,                                                |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 5.1 Program-Address Generation 5.2 Pipeline Operation 5.3 Branches, Calls, and Returns 5.4 Conditional Branches, Calls, and Returns 5.5 Repeating a Single Instruction 5.6 Interrupts 5.7 Reset Operation 5.8 Power-Down Mode | 5-7<br>5-8<br>. 5-10<br>. 5-14<br>. 5-15<br>. 5-35 |

| 6 | Addressing Modes  Describes the operation and use of the TMS320C20x data-memory addressing modes.                                                                                                                             | 6-1                                                |

|   | 6.1 Immediate Addressing Mode 6.2 Direct Addressing Mode 6.3 Indirect Addressing Mode                                                                                                                                         | 6-4                                                |

| 7 | Assembly Language Instructions                                                                                                                                                                                                |                                                    |

|   | 7.1 Instruction Set Summary                                                                                                                                                                                                   | . 7-12                                             |

| 8 | On-Chip Peripherals  Introduces the TMS320C20x on-chip peripherals. Describes the clock generator, to CLKOUT1-pin control register, the timer, the wait-state generator, and the general-purpose lipins.                      | he                                                 |

|   | 8.1 Control of On-Chip Peripherals 8.2 Clock Generator 8.3 CLKOUT1-Pin Control (CLK) Register 8.4 Timer 8.5 Wait-State Generator 8.6 General-Purpose I/O Pins                                                                 | 8-4<br>8-7<br>8-8<br>. 8-15                        |

| 9 | Synchronous Serial Port                                                                                                                                                                                                       | 9-1                                                |

|   | 9.1 Overview of the Synchronous Serial Port  9.2 Components and Basic Operation  9.3 Controlling and Resetting the Port  9.4 Managing the Contents of the FIFO Buffers  9.5 Transmitter Operation                             | 9-3<br>9-8                                         |

|    | 9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11 | Receiver Operation Troubleshooting Enhanced Synchronous Serial Port (ESSP) ESSP Pins ESSP Registers ESSP Register Programming Considerations                   | 9-25<br>9-29<br>9-30<br>9-32 |

|----|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 10 |                                          | chronous Serial Port                                                                                                                                           | 10-1                         |

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5     | Overview of the Asynchronous Serial Port Components and Basic Operation Controlling and Resetting the Port Transmitter Operation 1 Receiver Operation 1        | 10-3<br>10-7<br>10-19        |

| 11 |                                          | 320C209                                                                                                                                                        |                              |

|    |                                          | ribes how the TMS320C209 differs from other TMS320C20x devices and is a central re                                                                             | )-                           |

|    | <i>sourc</i> 11.1                        | re for all the TMS320C209-specific control registers and configuration information.  'C209 Versus Other 'C20x Devices                                          |                              |

|    | 11.2                                     | 'C209 Memory and I/O Spaces                                                                                                                                    |                              |

|    | 11.3<br>11.4                             | 'C209 Interrupts                                                                                                                                               |                              |

| Α  | Regis                                    | ster Summary                                                                                                                                                   |                              |

|    | Is a c                                   | concise, central resource for information about the TMS320C20x on-chip registers. In addresses, reset values, and descriptive illustrations for the registers. |                              |

|    | A.1<br>A.2                               | Addresses and Reset Values                                                                                                                                     |                              |

| В  | TMS3                                     | 320F206 Flash Serial Loader                                                                                                                                    | . B-1                        |

|    | Discu                                    | sses the TMS320F206 Flash Serial Loader.                                                                                                                       |                              |

|    | B.1<br>B.2                               | TMS320F206 Flash Serial Loader Features                                                                                                                        |                              |

|    | Б.2<br>В.3                               | Functional Description                                                                                                                                         |                              |

| С  |                                          | 320C1x/C2x/C20x/C5x Instruction Set Comparison                                                                                                                 |                              |

|    | Discu                                    | isses the compatibility of program code among the following devices: TMS320C1x320C2x, TMS320C20x, and TMS320C5x.                                               |                              |

|    |                                          | Using the Instruction Set Comparison Table                                                                                                                     |                              |

|    | C.2<br>C.3                               | Enhanced Instructions                                                                                                                                          |                              |

| n  |                                          | ram Examples                                                                                                                                                   |                              |

| D  | Prese                                    | ents examples of assembly language programs for the TMS320C20x, primarily example on-chip peripherals.                                                         |                              |

|    | D.1                                      | About These Program Examples                                                                                                                                   | . D-2                        |

|    | D.2                                      | Shared Program Code                                                                                                                                            | D-5                          |

|    | D.3                                      | Task-Specific Program Code                                                                                                                                     |                              |

|    | D 4                                      | Introduction to Generating Bootloader Code                                                                                                                     | D-23                         |

| E | Expla | nitting ROM Codes to TI                                            |                  |

|---|-------|--------------------------------------------------------------------|------------------|

| F | Desc  | gn Considerations for Using XDS510 Emulator                        |                  |

|   | F.1   | Designing Your Target System's Emulator Connector (14-Pin Header)  |                  |

|   | F.2   | Bus Protocol                                                       | F-4              |

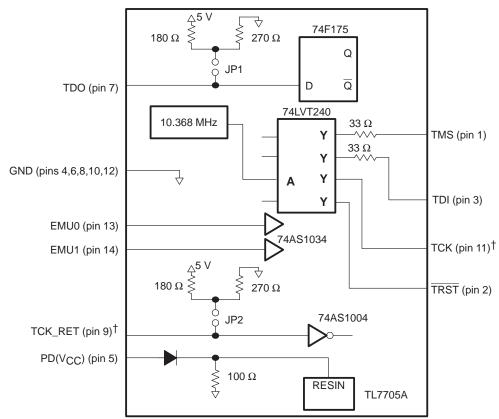

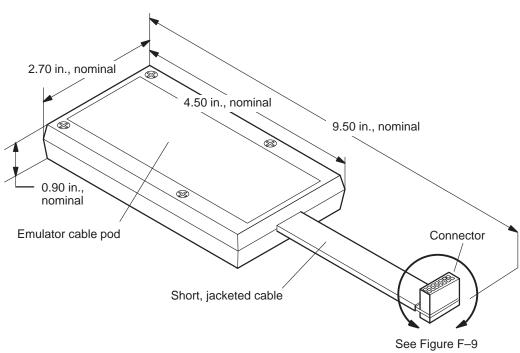

|   | F.3   | Emulator Cable Pod                                                 | F-5              |

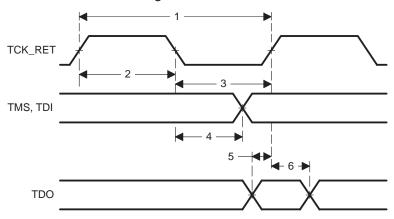

|   | F.4   | Emulator Cable Pod Signal Timing                                   | F-6              |

|   | F.5   | Emulation Timing Calculations                                      | F-7              |

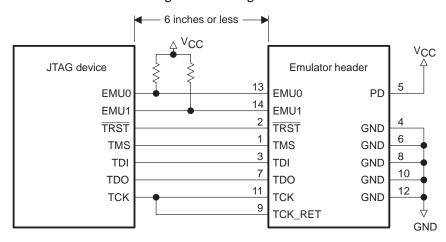

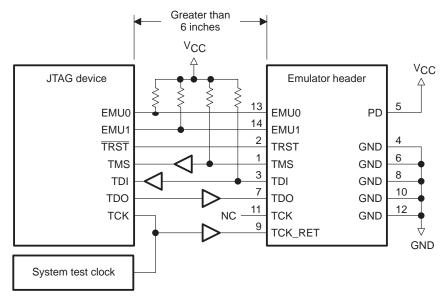

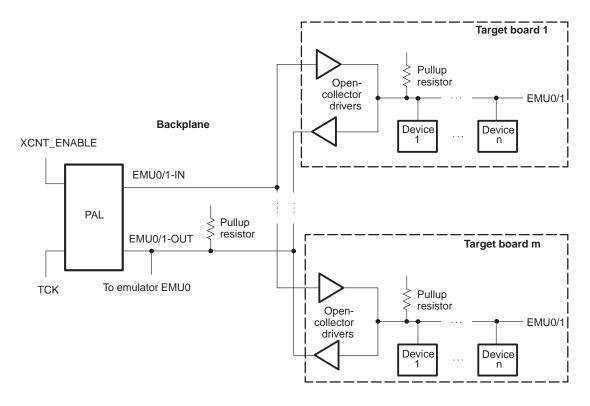

|   | F.6   | Connections Between the Emulator and the Target System F           | <del>-</del> -10 |

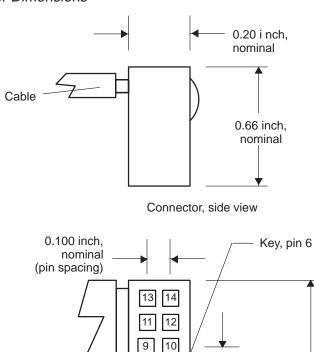

|   | F.7   | Physical Dimensions for the 14-Pin Emulator Connector F            | <del>-</del> -14 |

|   | F.8   | Emulation Design Considerations                                    |                  |

| G | Gloss | sary                                                               | G-1              |

|   | Expla | nins terms, abbreviations, and acronyms used throughout this book. |                  |

# Figures

| 2–1  | Overall Block Diagram of the 'C20x                                | 2-2  |

|------|-------------------------------------------------------------------|------|

| 2–2  | Bus Structure Block Diagram                                       |      |

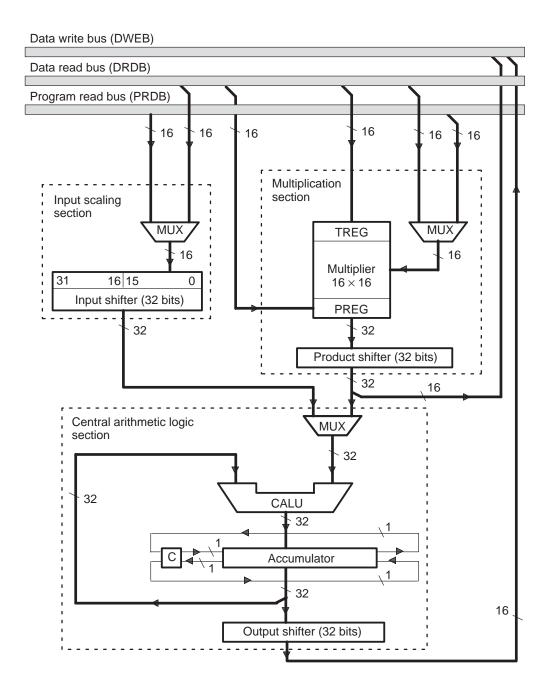

| 3–1  | Block Diagram of the Input Scaling, Central Arithmetic Logic, and |      |

|      | Multiplication Sections of the CPU                                | 3-2  |

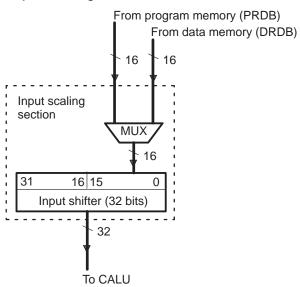

| 3–2  | Block Diagram of the Input Scaling Section                        |      |

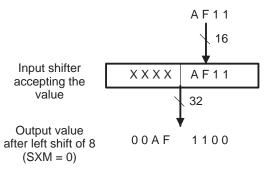

| 3–3  | Operation of the Input Shifter for SXM = 0                        |      |

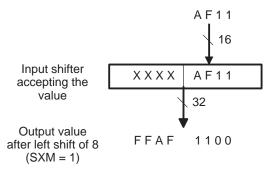

| 3–4  | Operation of the Input Shifter for SXM = 1                        |      |

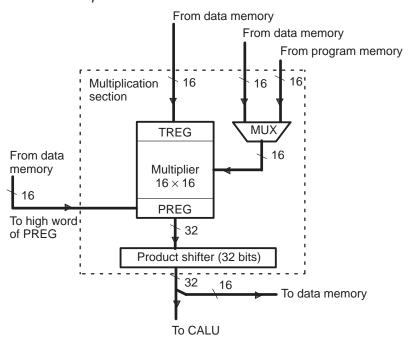

| 3–5  | Block Diagram of the Multiplication Section                       |      |

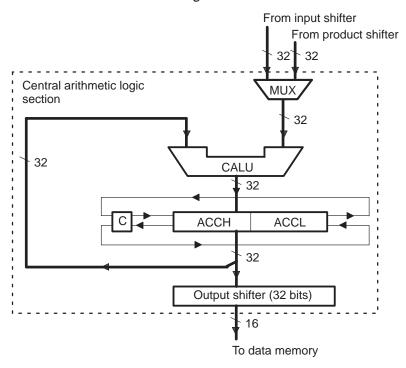

| 3–6  | Block Diagram of the Central Arithmetic Logic Section             |      |

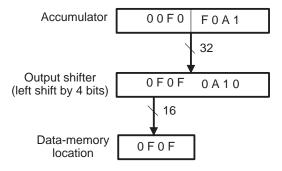

| 3–7  | Shifting and Storing the High Word of the Accumulator             |      |

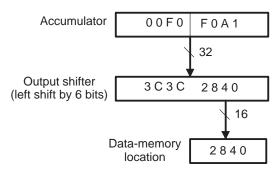

| 3–8  | Shifting and Storing the Low Word of the Accumulator              |      |

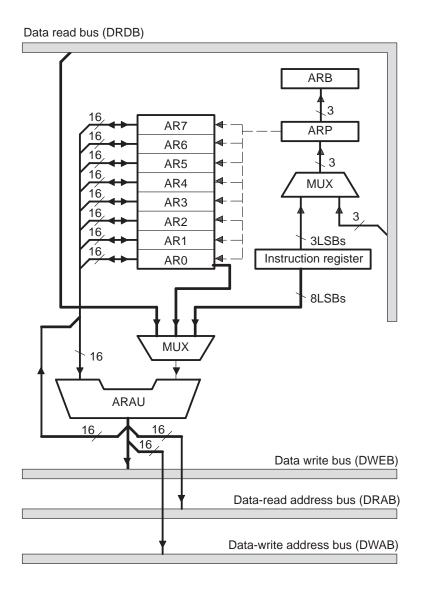

| 3–9  | ARAU and Related Logic                                            | 3-12 |

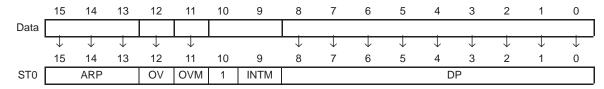

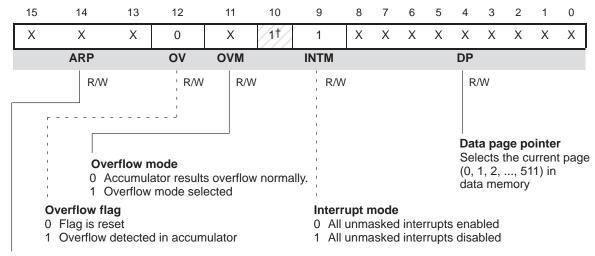

| 3–10 | Status Register ST0                                               | 3-15 |

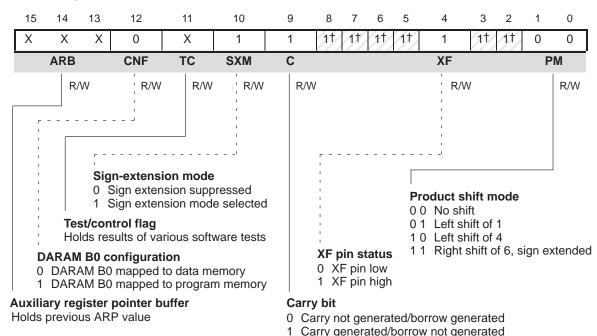

| 3–11 | Status Register ST1                                               | 3-15 |

| 4–1  | Interface With External Program Memory                            | 4-6  |

| 4–2  | Pages of Data Memory                                              | 4-7  |

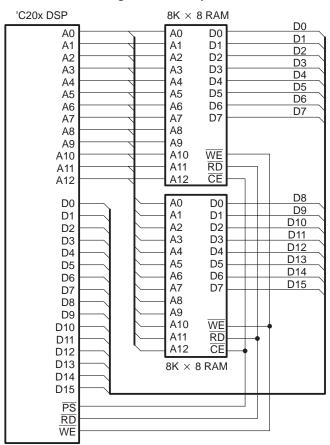

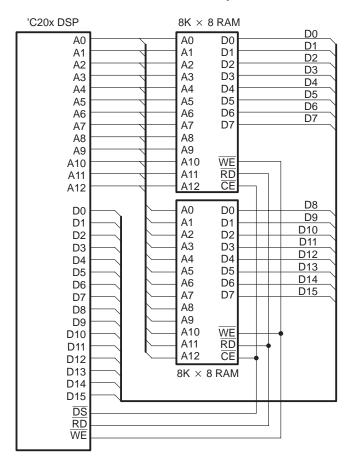

| 4–3  | Interface With External Local Data Memory                         | 4-10 |

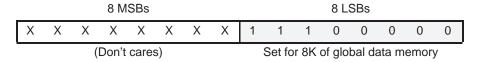

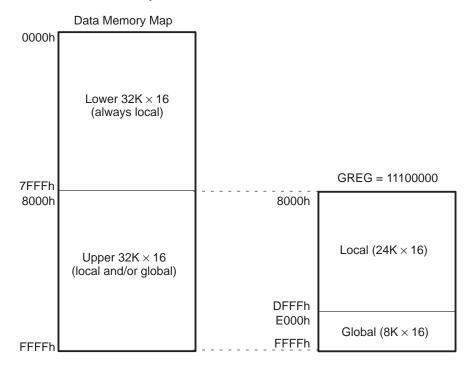

| 4–4  | GREG Register Set to Configure 8K for Global Data Memory          | 4-12 |

| 4–5  | Global and Local Data Memory for GREG = 11100000                  | 4-12 |

| 4–6  | Using 8000h–FFFFh for Local and Global External Memory            | 4-13 |

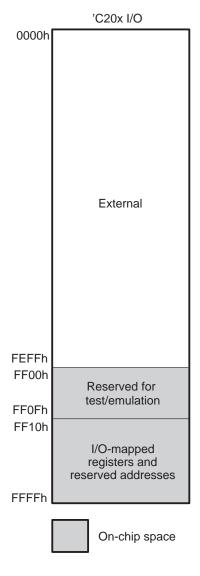

| 4–7  | I/O Address Map for the 'C20x                                     | 4-14 |

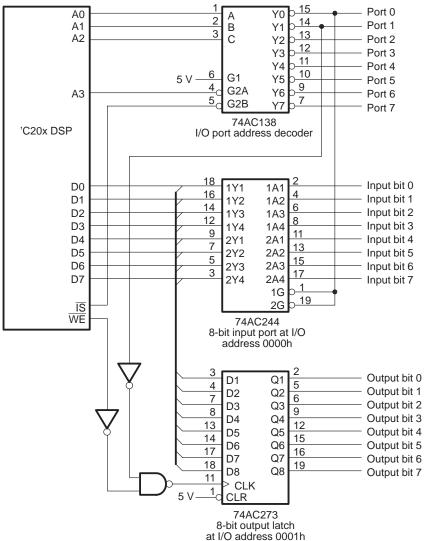

| 4–8  | I/O Port Interface Circuitry                                      | 4-17 |

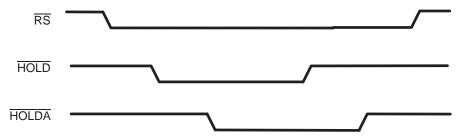

| 4–9  | HOLD Deasserted Before Reset Deasserted                           | 4-20 |

| 4–10 | Reset Deasserted Before HOLD Deasserted                           | 4-21 |

| 4–11 | 'C203 Address Map                                                 | 4-23 |

| 4–12 | TMS320C206, TMS320LC206 Memory Map Configurations                 |      |

| 4–13 | TMS320F206 Memory Map Configuration                               |      |

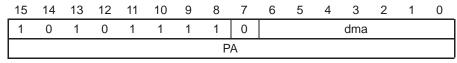

| 4–14 | PMST Register Selection for RD                                    |      |

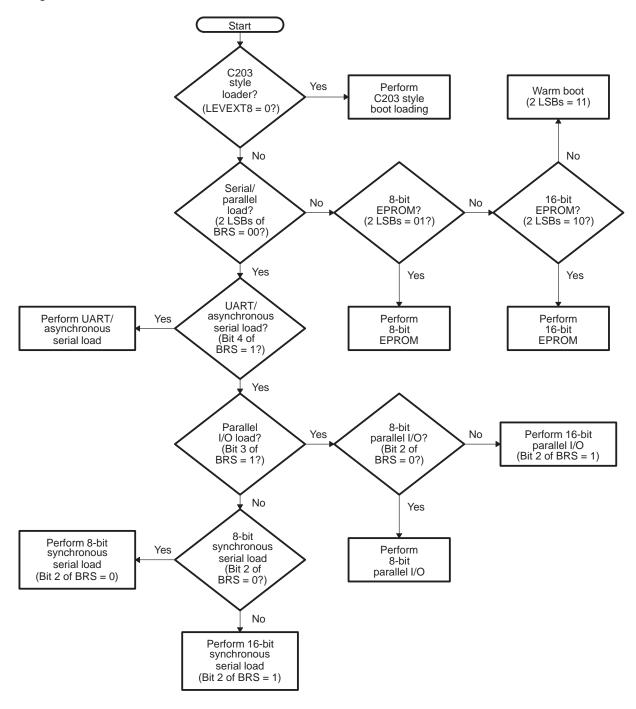

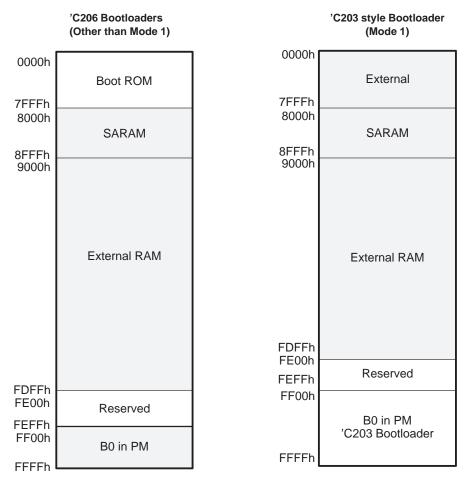

| 4–15 | Simplified Block Diagram of Bootloader Operation                  | 4-30 |

| 4–16 | Connecting the EPROM to the Processor                             |      |

| 4–17 | Storing the Program in the EPROM                                  |      |

| 4–18 | Program Code Transferred From 8-Bit EPROM to 16-Bit RAM           |      |

| 4–19 | Interrupt Vectors Transferred First During Boot Load              |      |

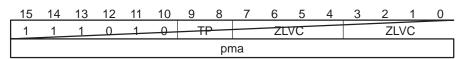

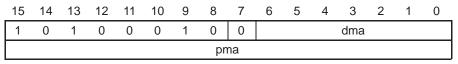

| 4–20 | Program Memory Status (PMST) Register – (I/O space FFE4h)         |      |

| 4–21 | Enhanced 'C206 Bootloader Options                                 |      |

| 4–22 | Boot-load Flowchart                                               |      |

| 4–23 | Destination Address Space for Programs in Program Memory                     | . 4-44 |

|------|------------------------------------------------------------------------------|--------|

| 4–24 | 16-Bit Word Transfer                                                         | . 4-47 |

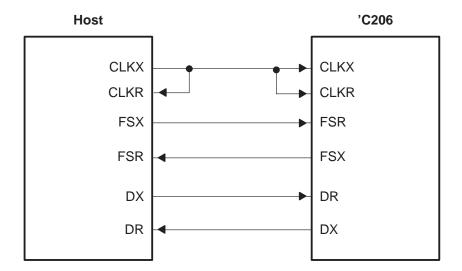

| 4–25 | Host-'C206 Interface for SSP Boot-load Option                                | . 4-48 |

| 4–26 | Figure 9. 8-Bit Word Transfer                                                | . 4-49 |

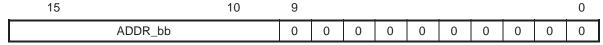

| 4–27 | 16-Bit Source Address for Parallel EPROM Boot Mode                           | . 4-51 |

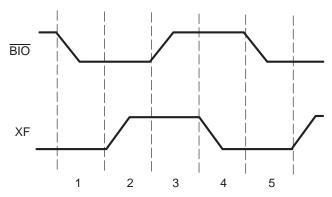

| 4–28 | Handshake Protocol                                                           |        |

| 4–29 | 16-Bit Entry Address for Warm-Boot Mode                                      | . 4-54 |

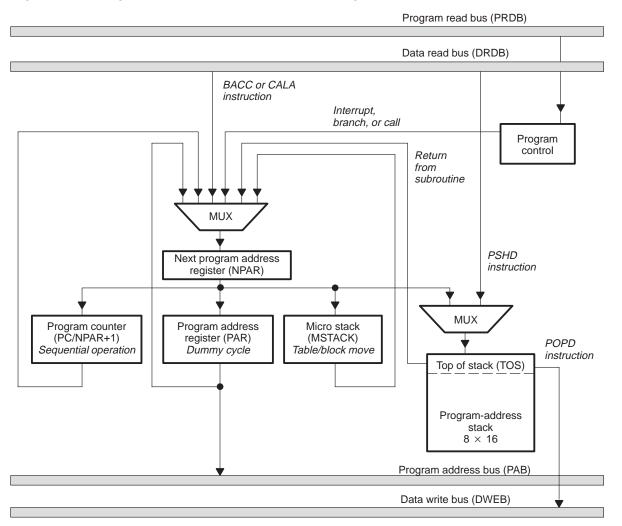

| 5–1  | Program-Address Generation Block Diagram                                     | 5-2    |

| 5–2  | A Push Operation                                                             | 5-5    |

| 5–3  | A Pop Operation                                                              | 5-6    |

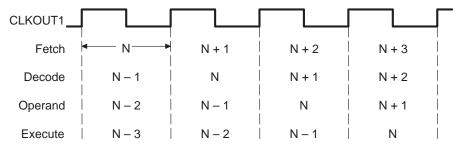

| 5–4  | 4-Level Pipeline Operation                                                   | 5-7    |

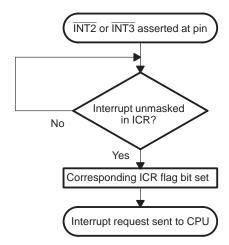

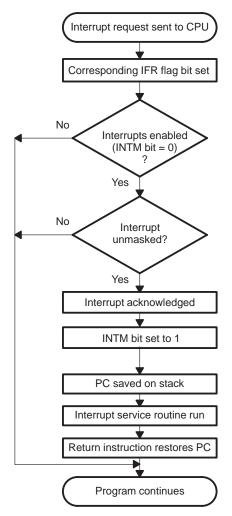

| 5–5  | INT2/INT3 Request Flow Chart                                                 | . 5-18 |

| 5–6  | Maskable Interrupt Operation Flow Chart                                      | . 5-20 |

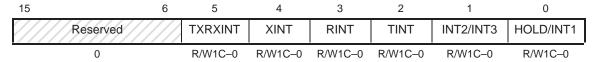

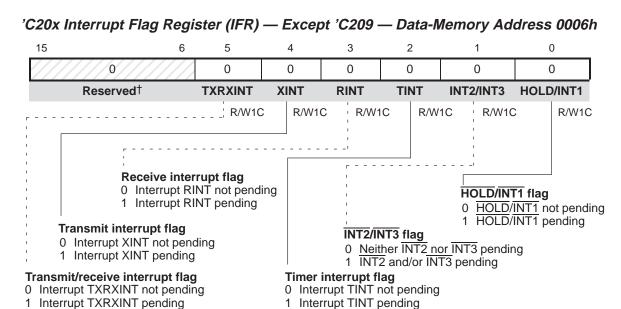

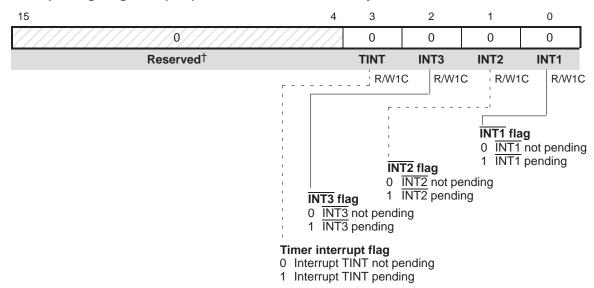

| 5–7  | 'C20x Interrupt Flag Register (IFR) — Data-Memory Address 0006h              | . 5-21 |

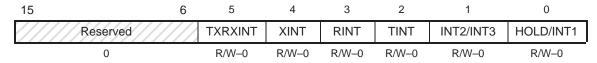

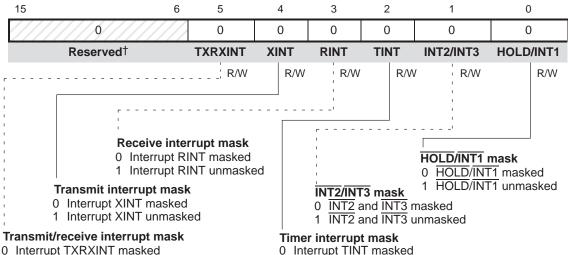

| 5–8  | 'C20x Interrupt Mask Register (IMR) — Data-Memory Address 0004h              | . 5-23 |

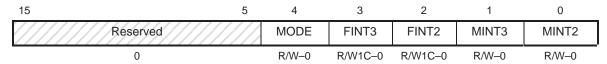

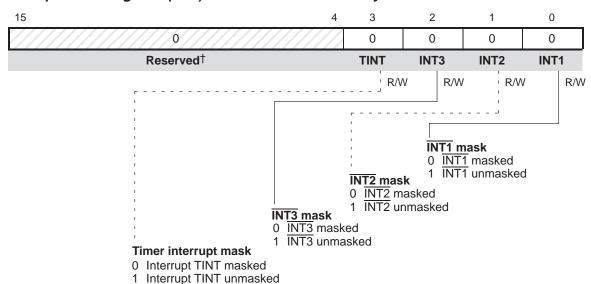

| 5–9  | 'C20x Interrupt Control Register (ICR) — I/O-Space Address FFECh             |        |

| 5–10 | Nonmaskable Interrupt Operation Flow Chart                                   |        |

| 5–11 | Direct Addressing Context Save                                               | . 5-33 |

| 5–12 | Indirect Addressing Context Save                                             |        |

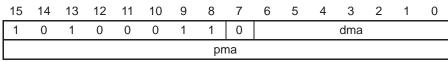

| 6–1  | Instruction Register Contents for Example 6–1                                | 6-2    |

| 6–2  | Two Words Loaded Consecutively to the Instruction Register in Example 6–2    | 6-3    |

| 6–3  | Pages of Data Memory                                                         |        |

| 6–4  | Instruction Register (IR) Contents in Direct Addressing Mode                 |        |

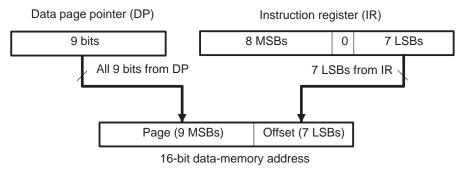

| 6–5  | Generation of Data Addresses in Direct Addressing Mode                       | 6-5    |

| 6–6  | Instruction Register Content in Indirect Addressing                          | . 6-12 |

| 7–1  | Bit Numbers and Their Corresponding Bit Codes for BIT Instruction            |        |

| 7–2  | Bit Numbers and Their Corresponding Bit Codes for BITT Instruction           |        |

| 7–3  | LST #0 Operation                                                             |        |

| 7–4  | LST #1 Operation                                                             |        |

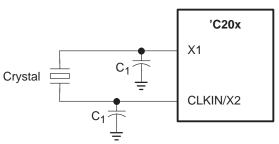

| 8–1  | Using the Internal Oscillator                                                |        |

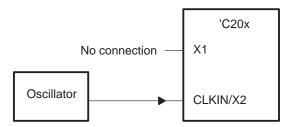

| 8–2  | Using an External Oscillator                                                 |        |

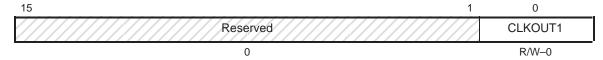

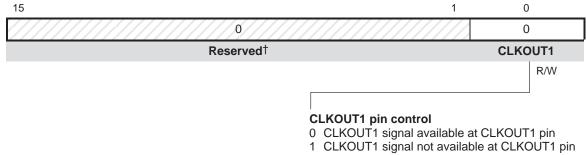

| 8–3  | 'C20x CLK Register — I/O-Space Address FFE8h                                 |        |

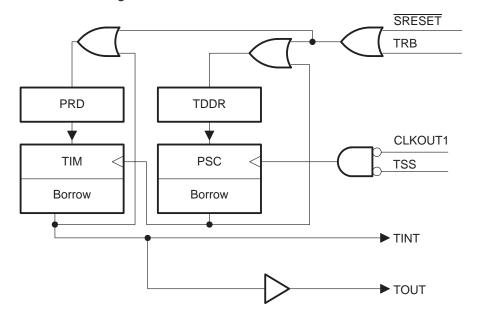

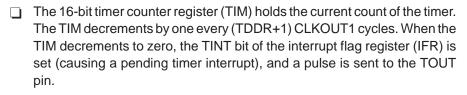

| 8–4  | Timer Functional Block Diagram                                               |        |

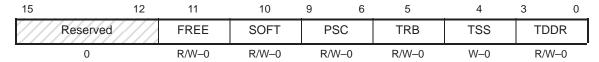

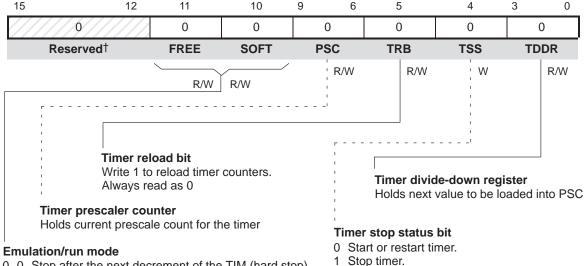

| 8–5  | 'C20x Timer Control Register (TCR) — I/O-Space Address FFF8h                 | . 8-11 |

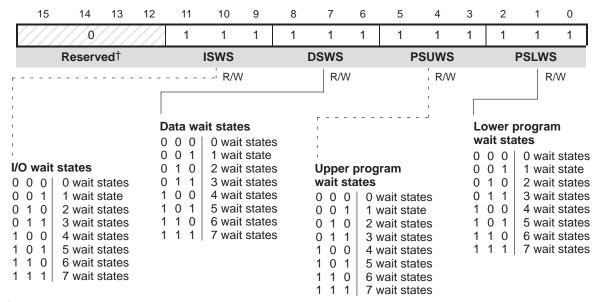

| 8–6  | 'C20x Wait-State Generator Control Register (WSGR) — I/O-Space Address FFFCh | . 8-16 |

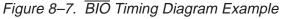

| 8–7  | BIO Timing Diagram Example                                                   |        |

| 9–1  | Synchronous Serial Port Block Diagram                                        |        |

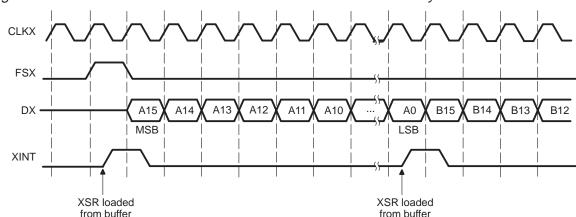

| 9–2  | 2-Way Serial Port Transfer With External Frame Sync and External Clock       |        |

| 9–3  | Synchronous Serial Port Control Register (SSPCR) — I/O-Space FFF1h           |        |

| 9–4  | Burst Mode Transmission With Internal Frame Sync and                         |        |

|      | Multiple Words in the Buffer                                                 |        |

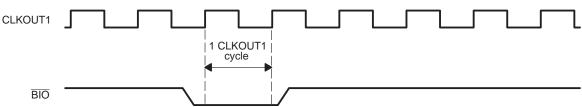

| 9–5  | Burst Mode Transmission With External Frame Sync                             |        |

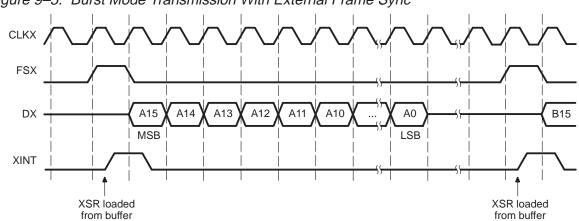

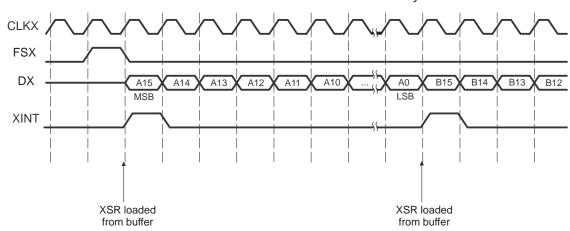

| 9–6  | Continuous Mode Transmission With Internal Frame Sync                        | . 9-20 |

| 9–7  | Continuous Mode Transmission With External Frame Sync                                           | 9-21  |

|------|-------------------------------------------------------------------------------------------------|-------|

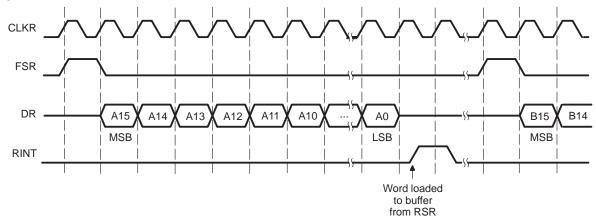

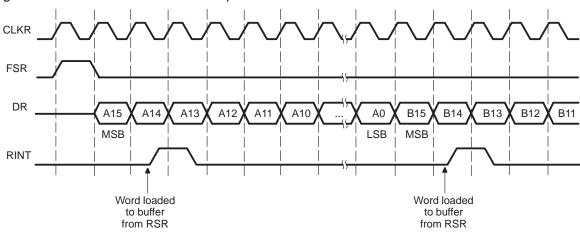

| 9–8  | Burst Mode Reception                                                                            |       |

| 9–9  | Continuous Mode Reception                                                                       | 9-24  |

| 9–10 | Test Bits in the SSPCR                                                                          | 9-25  |

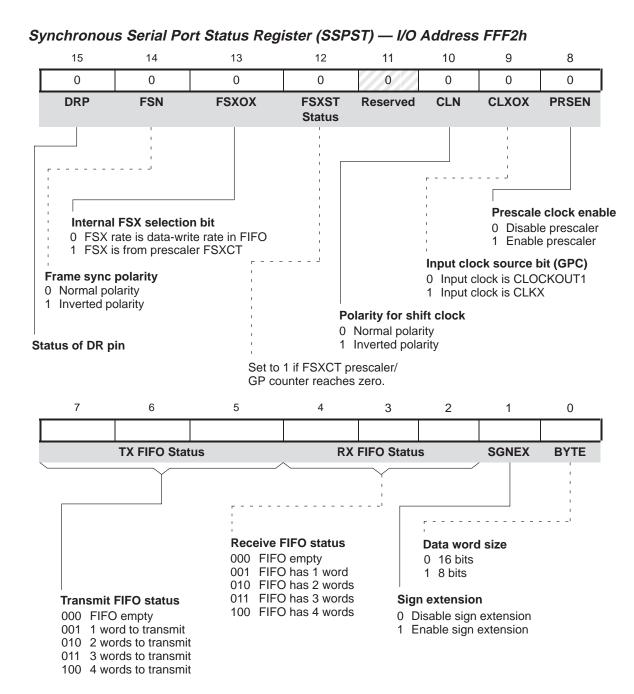

| 9–11 | Synchronous Serial Port Status (SSPST) Register — I/O address FFF2h                             | 9-32  |

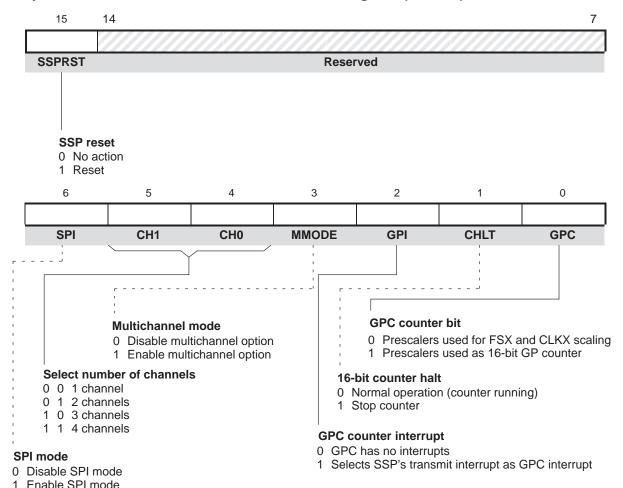

| 9–12 | Synchronous Serial Port Multichannel (SSPMC) Register — FFF3h                                   | 9-34  |

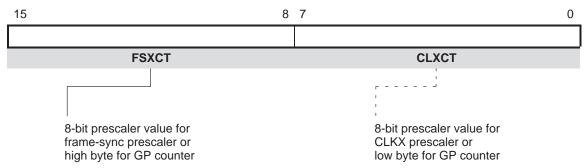

| 9–13 | Synchronous Serial Port Count (SSPCT) Register — FFFBh                                          | 9-38  |

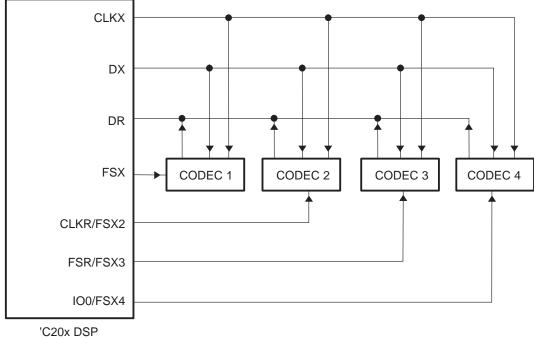

| 9–14 | Typical Four-Channel Codec Interface                                                            | 9-41  |

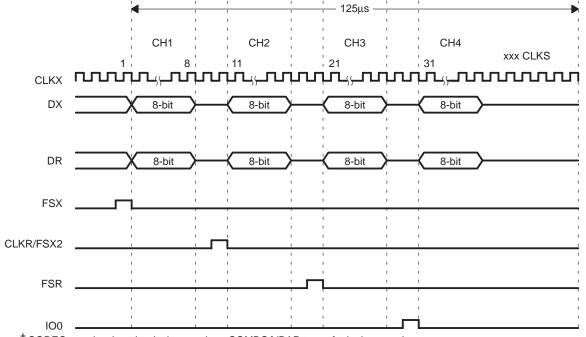

| 9–15 | Four-Channel 8-Bit CODEC Interface Timing Example                                               | 9-41  |

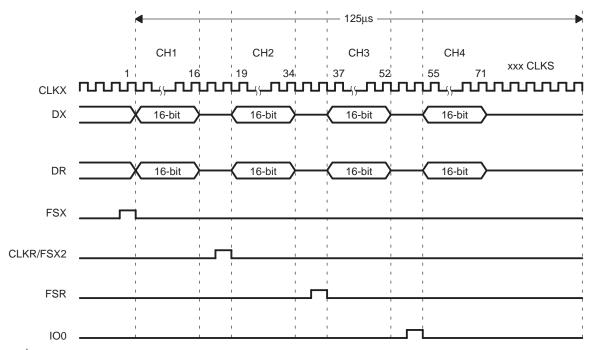

| 9–16 | Four-Channel 16-Bit CODEC Interface Timing Example                                              | 9-42  |

| 10–1 | Asynchronous Serial Port Block Diagram                                                          | 10-3  |

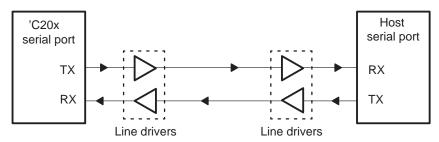

| 10–2 | Typical Serial Link Between a 'C20x Device and a Host CPU                                       | 10-6  |

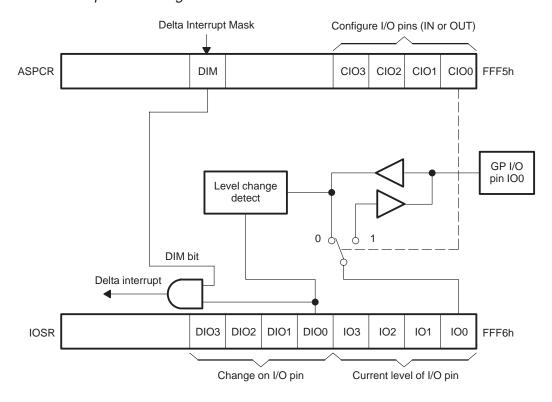

| 10–3 | Asynchronous Serial Port Control Register (ASPCR) — I/O-Space Address FFF5h                     | 10-7  |

| 10-4 | I/O Status Register (IOSR) — I/O-Space Address FFF6h                                            |       |

| 10–5 | Example of the Logic for Pins IO0–IO3                                                           | 10-15 |

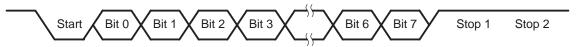

| 10–6 | Data Transmit                                                                                   | 10-19 |

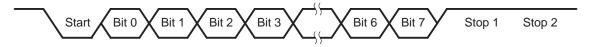

| 10–7 | Data Receive                                                                                    | 10-20 |

| 11–1 | 'C209 Address Maps                                                                              | 11-6  |

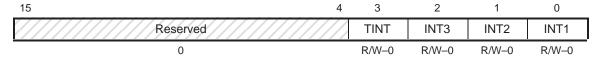

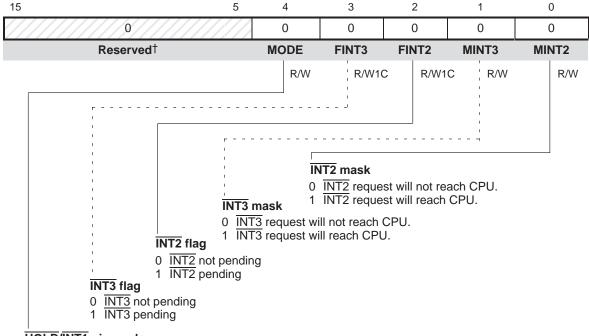

| 11–2 | 'C209 Interrupt Flag Register (IFR) — Data-Memory Address 0006h                                 | 11-12 |

| 11–3 | 'C209 Interrupt Mask Register (IMR) — Data-Memory Address 0004h                                 | 11-13 |

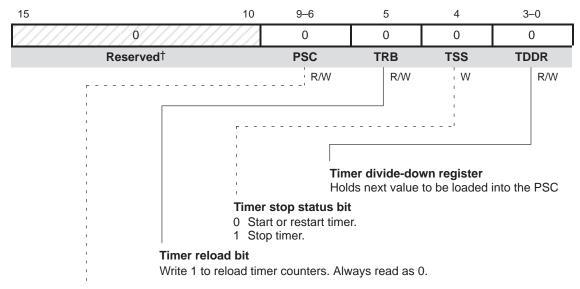

| 11–4 | 'C209 Timer Control Register (TCR) — I/O Address FFFCh                                          | 11-16 |

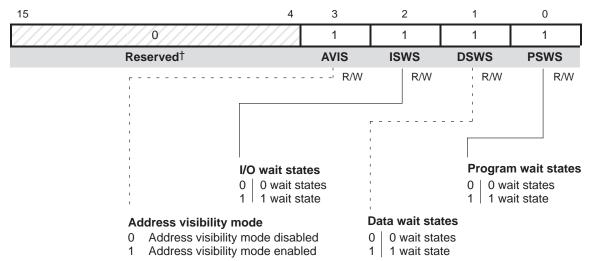

| 11–5 | 'C209 Wait-State Generator Control Register (WSGR) — I/O Address FFFFh                          | 11-18 |

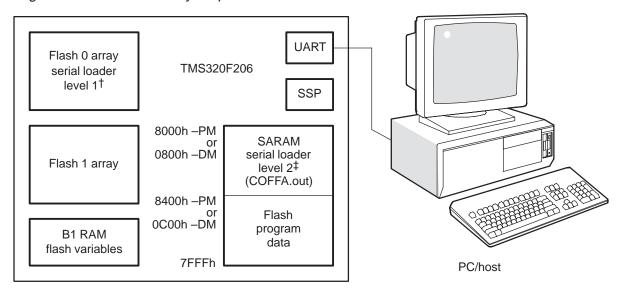

| B-1  | 'F206 Memory Map and Serial Port Connections                                                    | B-2   |

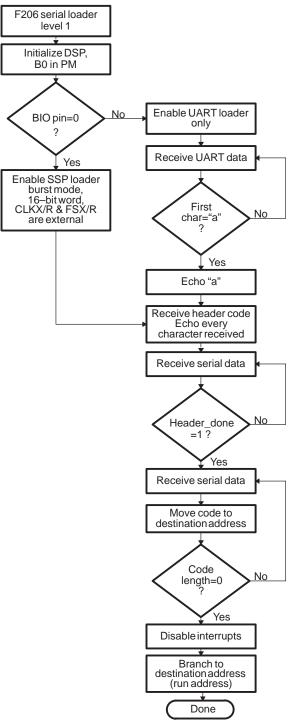

| B-2  | TMS320F206 Flash Serial Loader – 'F206 Level 1 Flow Chart                                       | B-5   |

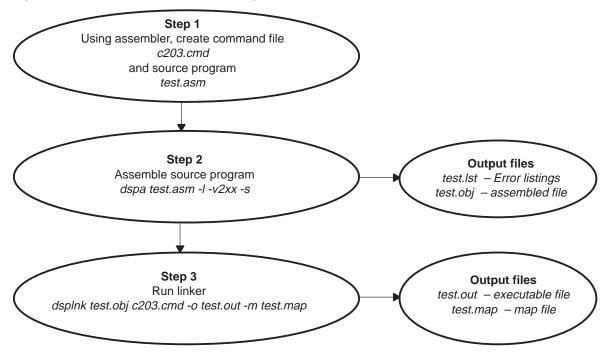

| D-1  | Procedure for Generating Executable Files                                                       | D-2   |

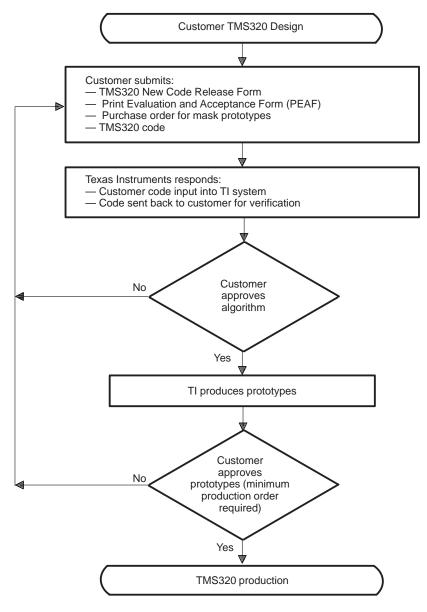

| E-1  | TMS320 ROM Code Submittal Flow Chart                                                            | E-2   |

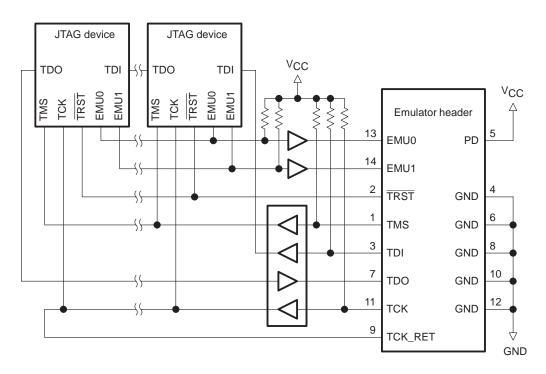

| F-1  | 14-Pin Header Signals and Header Dimensions                                                     | F-2   |

| F-2  | Emulator Cable Pod Interface                                                                    | F-5   |

| F-3  | Emulator Cable Pod Timings                                                                      | F-6   |

| F-4  | Emulator Connections Without Signal Buffering                                                   | F-10  |

| F-5  | Emulator Connections With Signal Buffering                                                      | F-11  |

| F-6  | Target-System-Generated Test Clock                                                              | F-12  |

| F-7  | Multiprocessor Connections                                                                      | F-13  |

| F-8  | Pod/Connector Dimensions                                                                        | F-14  |

| F-9  | 14-Pin Connector Dimensions                                                                     | F-15  |

| F-10 | Connecting a Secondary JTAG Scan Path to a Scan Path Linker                                     | F-17  |

| F-11 | EMU0/1 Configuration to Meet Timing Requirements of Less Than 25 ns                             | F-21  |

| F-12 | Suggested Timings for the EMU0 and EMU1 Signals                                                 |       |

| F-13 | EMU0/1 Configuration With Additional AND Gate to Meet Timing Requirements of Greater Than 25 ns | F-23  |

| F-14 | EMU0/1 Configuration Without Global Stop                                                        |       |

| F-15 | TBC Emulation Connections for n JTAG Scan Paths                                                 |       |

|      |                                                                                                 |       |

## **Tables**

| 1–1  | Typical Applications for TMS320 DSPs                      | 1-3   |

|------|-----------------------------------------------------------|-------|

| 1–2  | C20x Generation Summary                                   |       |

| 2–1  | Program and Data Memory on the TMS320C20x Devices         |       |

| 2–2  | Serial Ports on the 'C20x Devices                         |       |

| 3–1  | Product Shift Modes for the Product-Scaling Shifter       | 3-7   |

| 3–2  | Bit Fields of Status Registers ST0 and ST1                | 3-16  |

| 4–1  | Pins for Interfacing With External Memory and I/O Spaces  |       |

| 4–2  | Data Page 0 Address Map                                   | 4-8   |

| 4–3  | Global Data Memory Configurations                         | 4-11  |

| 4–4  | On-Chip Registers Mapped to I/O Space                     | 4-16  |

| 4–5  | 'C203 Program-Memory Configuration Options                | 4-24  |

| 4–6  | 'C203 Data-Memory Configuration Options                   | 4-25  |

| 4–7  | PMST Register Bit Descriptions                            | 4-40  |

| 4–8  | Bootloader-Pin Configuration                              | 4-41  |

| 5–1  | Program-Address Generation Summary                        | 5-3   |

| 5–2  | Address Loading to the Program Counter                    |       |

| 5–3  | Conditions for Conditional Branches, Calls, and Returns   | 5-10  |

| 5–4  | Groupings of Conditions                                   | 5-11  |

| 5–5  | 'C20x Interrupt Locations and Priorities                  | 5-16  |

| 5–6  | 'C20x IFR — Data-Memory Address 0006h Bit Descriptions    | 5-21  |

| 5–7  | 'C20x IMR — Data-Memory Address 0004h Bit Descriptions    | 5-23  |

| 5–8  | 'C20x ICR — I/O-Space Address FFECh Bit Descriptions      | 5-26  |

| 5–9  | Reset Values of On-Chip Registers Mapped to Data Space    | 5-37  |

| 5–10 | Reset Values of On-Chip Registers Mapped to I/O Space     | 5-37  |

| 5–11 | Reset Conditions for the 'C206/'LC206                     | 5-38  |

| 6–1  | Indirect Addressing Operands                              | 6-10  |

| 6–2  | Effects of the ARU Code on the Current Auxiliary Register | 6-13  |

| 6–3  | Field Bits and Notation for Indirect Addressing           | 6-14  |

| 7–1  | Accumulator, Arithmetic, and Logic Instructions           | 7-4   |

| 7–2  | Auxiliary Register Instructions                           | 7-7   |

| 7–3  | TREG, PREG, and Multiply Instructions                     | 7-8   |

| 7–4  | Branch Instructions                                       | 7-9   |

| 7–5  | Control Instructions                                      | 7-9   |

| 7–6  | I/O and Memory Instructions                               | 7-11  |

| 7–7  | Product Shift Modes                                       | 7-37  |

| 7–8  | Product Shift Modes                                       | 7-167 |

| 8–1  | Peripheral Register Locations and Reset Conditions                      | 8-2     |

|------|-------------------------------------------------------------------------|---------|

| 8–2  | 'C20x Input Clock Modes                                                 | 8-6     |

| 8–3  | 'C20x TCR — I/O Space Address FFF8h Bit Descriptions                    | 8-11    |

| 8–4  | 'C20x WSGR — I/O Space Address FFFCh Bit Descriptions                   | 8-16    |

| 8–5  | Setting the Number of Wait States With the 'C20x WSGR Bits              | 8-17    |

| 9–1  | SSP Interface Pins                                                      | 9-4     |

| 9–2  | SSPCR — I/O-Space Address FFF1h Bit Descriptions                        | 9-9     |

| 9–3  | Selecting Transmit Clock and Frame Sync Sources                         | 9-13    |

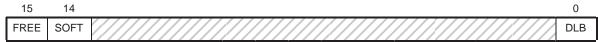

| 9–4  | Run and Emulation Modes                                                 | 9-26    |

| 9–5  | TMS320C20x Enhanced Synchronous Serial Port Interface Signals           | 9-30    |

| 9–6  | ESSP Registers                                                          | 9-32    |

| 9–7  | SSPST Register — I/O address FFF2h Bit Descriptions                     | 9-33    |

| 9–8  | SSPMC Register — FFF3h Bit Descriptions                                 | 9-35    |

| 9–9  | Typical CLKX/FSX Rates and Their Prescaler Values                       | 9-38    |

| 9–10 | Options/Functions for Burst Mode and Continuous Mode                    | 9-43    |

| 9–11 | Serial Port Configuration – Burst Mode                                  | 9-44    |

| 9–12 | Serial Port Configuration – Continuous Mode                             | 9-45    |

| 10–1 | Asynchronous Serial Port Interface Pins                                 | 10-4    |

| 10–2 | ASPCR — I/O Space Address FFF5h Bit Descriptions                        | 10-7    |

| 10–3 | IOSR — I/O Space Address FFF6h Bit Descriptions                         | . 10-10 |

| 10–4 | Common Baud Rates and the Corresponding BRD Values                      | . 10-14 |

| 10–5 | Configuring Pins IO0–IO3 with ASPCR Bits CIO0–CIO3                      | . 10-16 |

| 10–6 | Viewing the Status of Pins IO0–IO3 With IOSR Bits IO0–IO3 and DIO0–DIO3 | . 10-17 |

| 11–1 | 'C209 Program-Memory Configuration Options                              | 11-8    |

| 11–2 | 'C209 Data-Memory Configuration Options                                 | 11-9    |

| 11–3 | 'C209 On-Chip Registers Mapped to I/O Space                             | 11-9    |

| 11–4 | C209 Interrupt Locations and Priorities                                 | . 11-10 |

| 11–5 | 'C209 IFR — Data Memory Address 0006h Bit Descriptions                  | . 11-12 |

| 11–6 | 'C209 IMR — Data Memory Address 0004h Bit Descriptions                  | . 11-13 |

| 11–7 | 'C209 Input Clock Modes                                                 |         |

| 11–8 | 'C209 TCR — I/O Address FFFCh Bit Descriptions                          | . 11-16 |

| 11–9 | 'C209 WSGR — I/O Address FFFFh Bit Descriptions                         |         |

| A-1  | Reset Values of the Status Registers                                    | A-2     |

| A-2  | Addresses and Reset Values of On-Chip Registers Mapped to Data Space    |         |

| A-3  | Addresses and Reset Values of On-Chip Registers Mapped to I/O Space     | A-2     |

| C-1  | Symbols and Acronyms Used in the Instruction Set Comparison Table       | C-3     |

| C-2  | Summary of Enhanced Instructions                                        | C-5     |

| D-1  | Shared Programs in This Appendix                                        | D-3     |

| D-2  | Task-Specific Programs in This Appendix                                 | D-3     |

| F-1  | 14-Pin Header Signal Descriptions                                       | F-3     |

| F-2  | Emulator Cable Pod Timing Parameters                                    | F-6     |

|      |                                                                         |         |

# **Examples**

| 4–1  | An Interrupt Service Routine Supporting INT1 and HOLD                                | 4-19 |

|------|--------------------------------------------------------------------------------------|------|

| 6–1  | RPT Instruction Using Short-Immediate Addressing                                     |      |

| 6–2  | ADD Instruction Using Long-Immediate Addressing                                      | 6-3  |

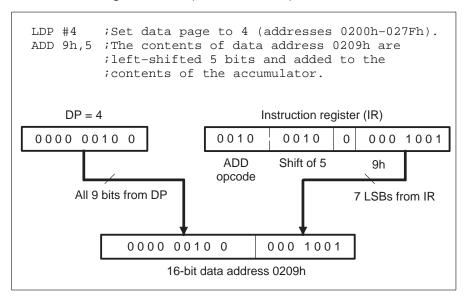

| 6–3  | Using Direct Addressing with ADD (Shift of 0 to 15)                                  |      |

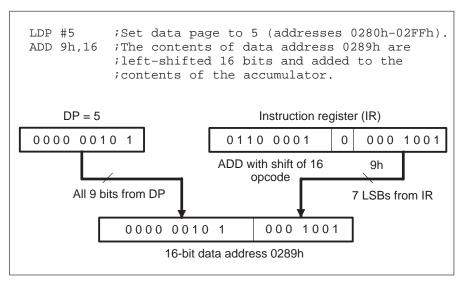

| 6–4  | Using Direct Addressing with ADD (Shift of 16)                                       | 6-7  |

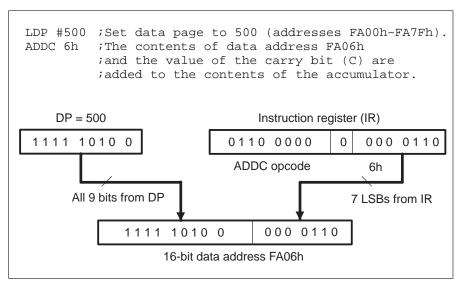

| 6–5  | Using Direct Addressing with ADDC                                                    | 6-8  |

| 6–6  | Selecting a New Current Auxiliary Register                                           | 6-12 |

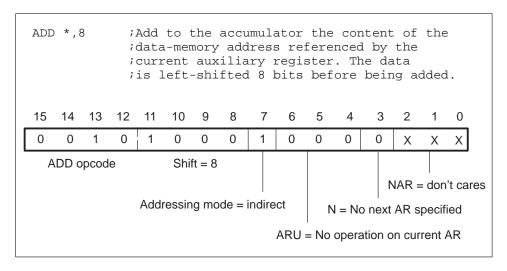

| 6–7  | No Increment or Decrement                                                            | 6-15 |

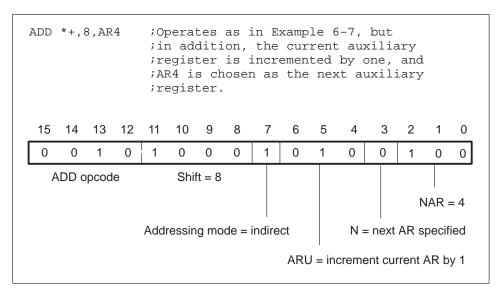

| 6–8  | Increment by 1                                                                       | 6-15 |

| 6–9  | Decrement by 1                                                                       | 6-16 |

| 6–10 | Increment by Index Amount                                                            | 6-16 |

| 6–11 | Decrement by Index Amount                                                            |      |

| 6–12 | Increment by Index Amount With Reverse Carry Propagation                             | 6-16 |

| 6–13 | Decrement by Index Amount With Reverse Carry Propagation                             |      |

| D-1  | Generic Command File (c203.cmd)                                                      | D-5  |

| D-2  | Header File With I/O Register Declarations (init.h)                                  |      |

| D-3  | Header File With Interrupt Vector Declarations (vector.h)                            |      |

| D-4  | Implementing Simple Delay Loops (delay.asm)                                          | D-8  |

| D-5  | Testing and Using the Timer (timer.asm)                                              | D-9  |

| D–6  | Testing and Using Interrupt INT1 (intr1.asm)                                         | D-10 |

| D-7  | Implementing a HOLD Operation (hold.asm)                                             | D-11 |

| D–8  | Testing and Using Interrupts INT2 and INT3 (intr23.asm)                              | D-12 |

| D-9  | Asynchronous Serial Port Transmission (uart.asm)                                     | D-13 |

| D-10 | Loopback to Verify Transmissions of Asynchronous Serial Port (echo.asm)              | D-14 |

| D-11 | Testing and Using Automatic Baud-Rate Detection on                                   |      |

|      | Asynchronous Serial Port (autobaud.asm)                                              |      |

| D-12 | Testing and Using Asynchronous Serial Port Delta Interrupts (bitio.asm)              |      |

| D-13 | Synchronous Serial Port Continuous Mode Transmission (ssp.asm)                       |      |

| D–14 | Using Synchronous Serial Port With Codec Device (ad55.asm)                           |      |

| D–15 | Linker Command File                                                                  |      |

| D-16 | Hex Conversion Utility Command File                                                  |      |

| F–1  | Key Timing for a Single-Processor System Without Buffers                             | F-8  |

| F–2  | Key Timing for a Single- or Multiple-Processor System With Buffered Input and Output | F-8  |

| F-3  | Key Timing for a Single-Processor System Without Buffering (SPL)                     |      |

| F–4  | Key Timing for a Single- or Multiprocessor-System With                               |      |

|      | Buffered Input and Output (SPL)                                                      | F-19 |

## Chapter 1

## Introduction

The TMS320C20x ('C20x) is one of several fixed-point generations of DSPs in the TMS320 family. The 'C20x is source-code compatible with the TMS320C2x. Much of the code written for the 'C2x can be reassembled to run on a 'C20x device. In addition, the 'C20x generation is upward compatible with the 'C5x generation of DSPs.

| Topi | C Pa                           | ıge |

|------|--------------------------------|-----|

| 1.1  | TMS320 Family                  | 1-2 |

| 1.2  | TMS320C20x Generation          | 1-4 |

| 1.3  | Key Features of the TMS320C20x | 1-5 |

#### 1.1 TMS320 Family

The TMS320 family consists of fixed-point, floating-point, and multiprocessor digital signal processors (DSPs). TMS320 DSPs have an architecture designed specifically for real-time signal processing. The following characteristics make this family the ideal choice for a wide range of processing applications:

| Flexible instruction sets         |

|-----------------------------------|

| High-speed performance            |

| Innovative parallel architectures |

| Cost effectiveness                |

#### 1.1.1 History, Development, and Advantages of TMS320 DSPs

In 1982, Texas Instruments introduced the TMS32010, the first fixed-point DSP in the TMS320 family. Before the end of the year, *Electronic Products* magazine awarded the TMS32010 the "Product of the Year" title. The next generation devices continue meeting new performance levels for TI DSPs.

Devices within a generation of the TMS320 family have the same CPU structure but different on-chip memory and peripheral configurations. Spin-off devices use new combinations of on-chip memory and peripherals to satisfy a wide range of needs in the worldwide electronics market. By integrating memory and peripherals onto a single chip, TMS320 devices reduce system cost and save circuit board space.

#### 1.1.2 Typical Applications for the TMS320 Family

Table 1–1 lists some typical applications for the TMS320 family of DSPs. The TMS320 DSPs offer adaptable approaches to traditional signal-processing problems such as filtering and vocoding. They also support complex applications that often require multiple operations to be performed simultaneously.

Table 1–1. Typical Applications for TMS320 DSPs

| Automotive                                                                                                                                              | Consumer                                                                                                                                                  | Control                                                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Adaptive ride control Antiskid brakes Cellular telephones Digital radios Engine control Global positioning Navigation Vibration analysis Voice commands | Digital radios/TVs Educational toys Music synthesizers Pagers Power tools Radar detectors Solid-state answering machines                                  | Disk drive control Engine control Laser printer control Motor control Robotics control Servo control                               |  |

| General-Purpose                                                                                                                                         | Graphics/Imaging                                                                                                                                          | Industrial                                                                                                                         |  |

| Adaptive filtering Convolution Correlation Digital filtering Fast Fourier transforms Hilbert transforms Waveform generation Windowing                   | 3-D rotation Animation/digital maps Homomorphic processing Image compression/transmission Image enhancement Pattern recognition Robot vision Workstations | Numeric control Power-line monitoring Robotics Security access                                                                     |  |

| Instrumentation                                                                                                                                         | Medical                                                                                                                                                   | Military                                                                                                                           |  |

| Digital filtering Function generation Pattern matching Phase-locked loops Seismic processing Spectrum analysis Transient analysis                       | Diagnostic equipment Fetal monitoring Hearing aids Patient monitoring Prosthetics Ultrasound equipment                                                    | Image processing Missile guidance Navigation Radar processing Radio frequency modems Secure communications Sonar processing        |  |

| Telecomn                                                                                                                                                | nunications                                                                                                                                               | Voice/Speech                                                                                                                       |  |

| 1200- to 28 800-bps modems<br>Adaptive equalizers<br>ADPCM transcoders<br>Cellular telephones                                                           | Faxing Line repeaters Personal communications systems (PCS)                                                                                               | Speaker verification Speech enhancement Speech recognition Speech synthesis Speech vocoding Text-to-speech applications Voice mail |  |

#### 1.2 TMS320C20x Generation

Texas Instruments uses static CMOS integrated-circuit technology to fabricate the TMS320C20x DSPs. The architectural design of the 'C20x is based on that of the 'C5x. The operational flexibility and speed of the 'C20x and 'C5x are a result of an advanced, modified Harvard architecture (which has separate buses for program and data memory), a multilevel pipeline, on-chip peripherals, on-chip memory, and a highly specialized instruction set. The 'C20x performs up to 40 MIPS (million instructions per second).

The 'C20x generation offers the following benefits:

- ☐ Enhanced TMS320 architectural design for increased performance and versatility

- Modular architectural design for fast development of additional spin-off devices

- ☐ Advanced IC processing technology for increased performance

- ☐ Fast and easy performance upgrades for 'C1x and 'C2x source code, which is upward compatible with 'C20x source code

- ☐ Enhanced instruction set for faster algorithms and for optimized high-level language operation

- ☐ New static design techniques for minimizing power consumption

Table 1–2 provides an overview of the basic features of the 'C20x DSPs.

Table 1–2. 'C20x Generation Summary

|             | Cyclo                 | Operating                     |      | hip M | emory | MEM          | Seria | l Ports | I/O      | )    |        |                       |

|-------------|-----------------------|-------------------------------|------|-------|-------|--------------|-------|---------|----------|------|--------|-----------------------|

| Device      | Cycle<br>Time<br>(ns) | Operating<br>Voltage<br>(Vdd) |      | ROM   | Flash | Off-<br>Chip | Sync  | Async   | PAR      | DMA  | Timers | Package               |

| TMS320C203  | 25/35/50              | 5V                            | 544  | -     | -     | 192K         | 1     | 1       | 64K x 16 | Ext. | 1      | 100 TQFP†             |

| TMS320LC203 | 50                    | 3.3V                          | 544  | -     | _     | 192K         | 1     | 1       | 64K x 16 | Ext. | 1      | 100 TQFP <sup>†</sup> |

| TMS320F206  | 50                    | 5V                            | 4.5K | -     | 32K   | 192K         | 1     | 1       | 64K x 16 | Ext. | 1      | 100 TQFP <sup>†</sup> |

| TMS320C209  | 35/50                 | 5V                            | 4.5K | 4K    | -     | 192K         | -     | -       | 64K x 16 | Ext. | 1      | 80 TQFP <sup>†</sup>  |

| TMS320C206  | 25                    | 3.3V                          | 4.5K | 32K   | -     | 192K         | 1     | 1       | 64K x 16 | Ext. | 1      | 100 TQFP <sup>†</sup> |

| TMS320LC206 | 25                    | 3.3V                          | 4.5K | 32K   | -     | 192K         | 1     | 1       | 64K x 16 | Ext. | 1      | 100 TQFP <sup>†</sup> |

<sup>†</sup>TQFP = Thin quad flat pack

### 1.3 Key Features of the TMS320C20x

| Key | features on the various 'C20x devices are:                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Speed:                                                                                                                                                |

|     | ■ 50-, 35-, or 25-ns execution time of a single-cycle instruction                                                                                     |

|     | ■ 20, 28.5, or 40 MIPS                                                                                                                                |

|     | Code compatibility with other TMS320 fixed-point devices:                                                                                             |

|     | ■ Source-code compatible with all 'C1x and 'C2x devices                                                                                               |

|     | ■ Upward compatible with the 'C5x devices                                                                                                             |

|     | Memory:                                                                                                                                               |

|     | ■ 224K words of addressable memory space (64K words of program space, 64K words of data space, 64K words of I/O space, and 32K words of global space) |

|     | ■ 544 words of dual-access on-chip RAM (288 words for data and 256 words for program/data)                                                            |

|     | ■ 32K words on-chip ROM or 32K words on-chip flash memory (on 'C206 and 'F206)                                                                        |

|     | ■ 4K words of single-access on-chip RAM (on 'C206 and 'F206)                                                                                          |

|     | CPU:                                                                                                                                                  |

|     | ■ 32-bit arithmetic logic unit (CALU)                                                                                                                 |

|     | ■ 32-bit accumulator                                                                                                                                  |

|     | ■ 16-bit × 16-bit parallel multiplier with 32-bit product capability                                                                                  |

|     | ■ Three scaling shifters                                                                                                                              |

|     | ■ Eight 16-bit auxiliary registers with a dedicated arithmetic unit for indirect addressing of data memory                                            |

|     | Program control:                                                                                                                                      |

|     | ■ 4-level pipeline operation                                                                                                                          |

|     | ■ 8-level hardware stack                                                                                                                              |

|     | ■ User-maskable interrupt lines                                                                                                                       |

|                                                 | Ins                                                                                                                                                  | Instruction set:                                                                        |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|                                                 | Single-instruction repeat operation                                                                                                                  |                                                                                         |  |  |  |  |  |  |  |  |  |

| ■ Single-cycle multiply/accumulate instructions |                                                                                                                                                      |                                                                                         |  |  |  |  |  |  |  |  |  |

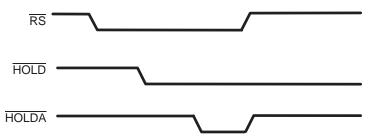

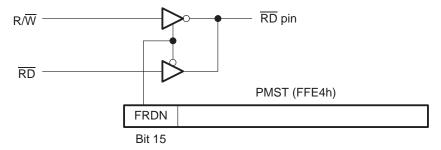

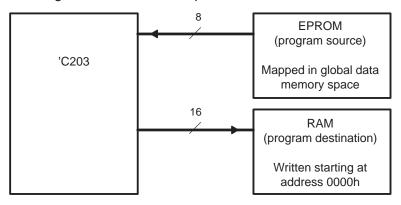

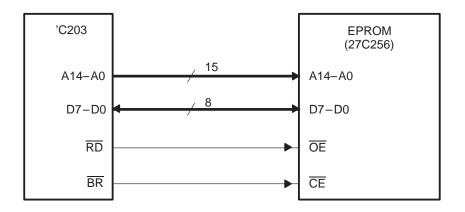

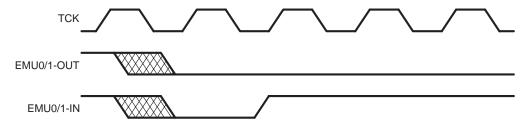

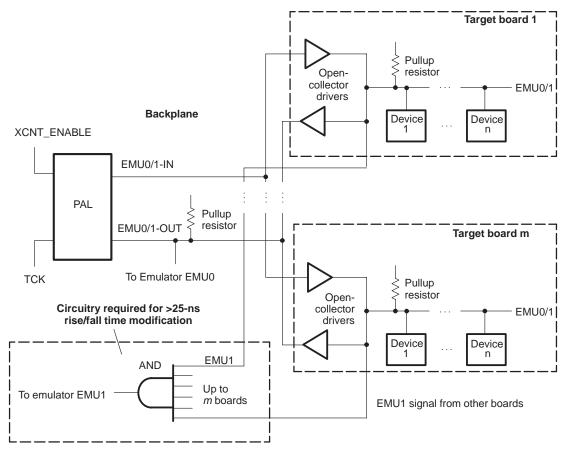

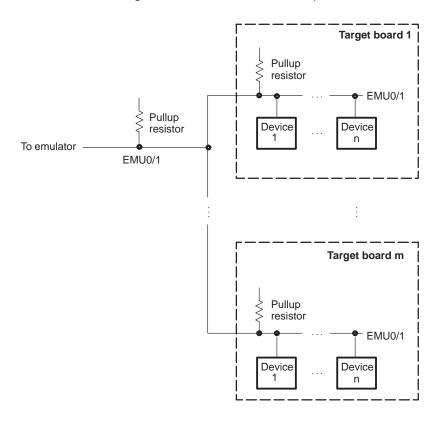

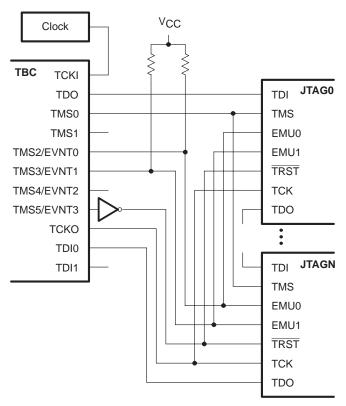

|                                                 |                                                                                                                                                      | Memory block move instructions for better program/data management                       |  |  |  |  |  |  |  |  |  |