### TMS320VC5501/5502 DSP Universal Asynchronous Receiver/Transmitter (UART) Reference Guide

SPRU597B November 2002 Revised March 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

### Preface

### **Read This First**

#### About This Manual

This manual describes the features and operation of the universal asynchronous receiver/transmitter (UART) that is on the TMS320VC5501 and TMS320VC5502 digital signal processors (DSPs) in the TMS320C55x<sup>TM</sup> (C55x<sup>TM</sup>) DSP generation.

#### Notational Conventions

This document uses the following conventions.

- The device number TMS320C55x is often abbreviated as C55x.

- In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers often are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

☐ If a signal or pin is active low, it has an overbar. For example, the RESET signal is active low.

#### **Related Documentation From Texas Instruments**

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

**TMS320C55x Technical Overview** (literature number SPRU393). This overview is an introduction to the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- *TMS320C55x DSP Peripherals Reference Guide* (literature number SPRU317) describes the peripherals, interfaces, and related hardware that are available on TMS320C55x DSPs.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- **TMS320C55x DSP Mnemonic Instruction Set Reference Guide** (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x<sup>™</sup> C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- **TMS320C55x DSP Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

#### Trademarks

TMS320, TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

## Contents

| 1 | <b>Intro</b><br>1.1<br>1.2 | duction to the UART<br>Transmission<br>Reception  | . 4        |

|---|----------------------------|---------------------------------------------------|------------|

| 2 | Prog                       | rammable Baud Generator                           | . 5        |

| 3 | Interr                     | upt Requests and DMA Events Generated by the UART | . 9        |

|   | 3.1                        | UART Interrupt Requests                           | . 9        |

|   | 3.2                        | UART DMA Events                                   | 12         |

| 4 | FIFO                       | Modes                                             | 13         |

|   | 4.1                        | FIFO Interrupt Mode                               | 13         |

|   | 4.2                        | FIFO Poll Mode                                    |            |

| 5 | Powe                       | r, Emulation, and Reset Considerations            | 16         |

| • | 5.1                        | Conserving Power                                  |            |

|   | 5.2                        | Emulation Mode                                    |            |

|   | 5.3                        | Emulator Access Support                           |            |

|   | 5.4                        | Resetting the UART                                |            |

| 6 | UAR                        | ۲ Registers                                       | 18         |

| • | 6.1                        | Receiver Buffer Register (URRBR)                  |            |

|   | 6.2                        | Transmitter Holding Register (URTHR)              |            |

|   | 6.3                        | Divisor Latch Registers (URDLL and URDLM)         |            |

|   | 6.4                        | Interrupt Enable Register (URIER)                 |            |

|   | 6.5                        | Interrupt Identification Register (URIIR)         |            |

|   | 6.6                        | FIFO Control Register (URFCR)                     | 29         |

|   | 6.7                        | Line Control Register (URLCR)                     | 30         |

|   | 6.8                        | Modem Control Register (URMCR)                    | 34         |

|   | 6.9                        | Line Status Register (URLSR)                      |            |

|   | 6.10                       | Scratch Register (URSCR)                          | 39         |

|   | 6.11                       | Power and Emulation Control Register (URPECR)     | 39         |

| Α | Revis                      | sion History                                      | <b>۱-۱</b> |

# Figures

| 1.  | UART Functional Block Diagram                            | 3 |

|-----|----------------------------------------------------------|---|

| 2.  | UART Clock Generation Diagram                            | 5 |

| 3.  | Relationships Among Data Bit, BCLK, and UART Input Clock | 6 |

| 4.  | Enable Paths of the UART Interrupt Requests              |   |

| 5.  | Receiver Buffer Register (URRBR)                         |   |

| 6.  | Transmitter Holding Register (URTHR)                     |   |

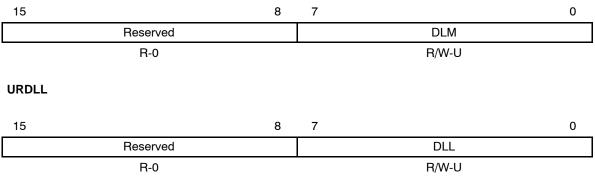

| 7.  | Divisor Latch Registers (URDLM and URDLL)                |   |

| 8.  | Interrupt Enable Register (URIER)                        |   |

| 9.  | Interrupt Identification Register (URIIR)                |   |

| 10. | FIFO Control Register (URFCR)                            |   |

| 11. | Line Control Register (URLCR)                            |   |

| 12. | Modem Control Register (URMCR)                           |   |

| 13. | Line Status Register (URLSR)                             |   |

| 14. | Scratch Register (URSCR)                                 |   |

| 15. | Power and Emulation Control Register (URPECR)            |   |

|     |                                                          |   |

## **Tables**

| 1.  | Baud Rates Using 1.8432 MHz for the UART Input Clock                       | 7  |

|-----|----------------------------------------------------------------------------|----|

| 2.  | Baud Rates Using 3.072 MHz for the UART Input Clock                        | 8  |

| 3.  | Descriptions of the UART Interrupt Requests                                | 10 |

| 4.  | Default State of Registers and TX Signal                                   |    |

| 5.  | UART Registers                                                             |    |

| 6.  | Visual Summary of the UART Registers                                       |    |

| 7.  | Receiver Buffer Register (URRBR) Field Descriptions                        | 21 |

| 8.  | Transmitter Holding Register (URTHR) Field Descriptions                    |    |

| 9.  | Divisor Latch Register – Most Significant Bits (URDLM) Field Descriptions  |    |

| 10. | Divisor Latch Register - Least Significant Bits (URDLL) Field Descriptions | 24 |

| 11. | Interrupt Enable Register (URIER) Field Descriptions                       | 25 |

| 12. | Interrupt Identification Register (URIIR) Field Descriptions               |    |

| 13. | Interrupt Identification and Interrupt Clearing Information                | 28 |

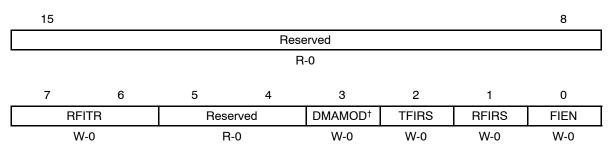

| 14. | FIFO Control Register (URFCR) Field Descriptions                           | 29 |

| 15. | Line Control Register (URLCR) Field Descriptions                           |    |

| 16. | Relationship Among STPAR, EPS, and PEN bits of URLCR                       |    |

| 17. | Number of Stop Bits Generated                                              |    |

| 18. | Modem Control Register (URMCR) Field Descriptions                          | 34 |

| 19. | Line Status Register (URLSR) Field Descriptions                            | 35 |

| 20. | Scratch Register (URSCR) Field Descriptions                                |    |

| 21. | Power and Emulation Control Register (URPECR) Field Descriptions           |    |

| 22. | Document Revision History                                                  |    |

|     |                                                                            |    |

## Universal Asynchronous Receiver/Transmitter (UART)

This chapter describes the features and operation of the universal asynchronous receiver/transmitter (UART) that is on the TMS320VC5501 and TMS320VC5502 digital signal processors (DSPs) in the TMS320C55x<sup>TM</sup> (C55x<sup>TM</sup>) DSP generation.

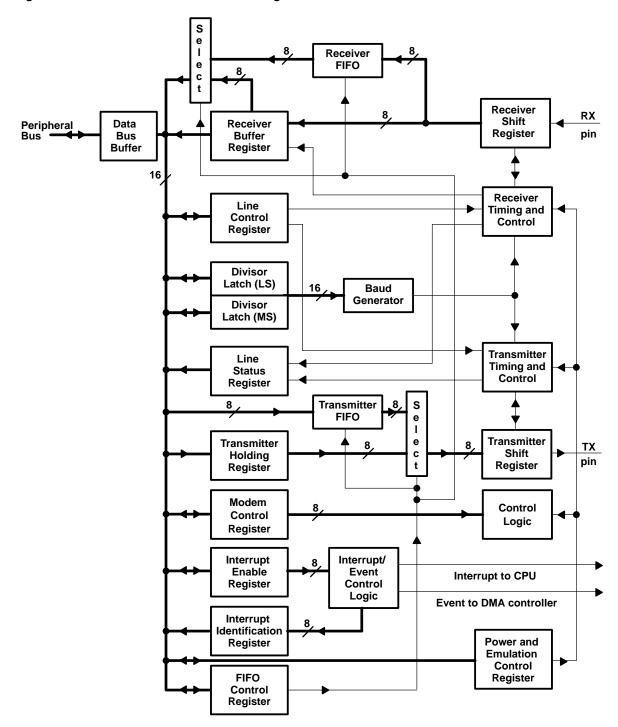

#### 1 Introduction to the UART

The UART peripheral is based on the industry-standard TL16C550 asynchronous communications element, which in turn is a functional upgrade of the TL16C450. Functionally similar to the TL16C450 on power up (single-character or TL16C450 mode), the UART can be placed in an alternate FIFO (TL16C550) mode. This relieves the CPU of excessive software overhead by buffering received and transmitted characters. The receiver and transmitter FIFOs store up to 16 bytes including three additional bits of error status per byte for the receiver FIFO.

The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU. The CPU can read the UART status at any time. The UART includes control capability and a processor interrupt system that can be tailored to minimize software management of the communications link.

The UART includes a programmable baud generator capable of dividing the UART input clock by divisors from 1 to 65535 and producing a  $16 \times$  reference clock for the internal transmitter and receiver logic. For detailed timing specifications for the UART, see the data manuals for the TMS320VC5501 and TMS320VC5502 devices.

Figure 1 is a block diagram of the UART.

Figure 1. UART Functional Block Diagram

Universal Asynchronous Receiver/Transmitter (UART)

SPRU597B

#### 1.1 Transmission

The UART transmitter section includes a transmitter hold register (URTHR) and a transmitter shift register (URTSR). When the UART is in the FIFO mode, URTHR is a 16-byte FIFO. Transmitter section control is a function of the UART line control register (URLCR). Based on the settings chosen in URLCR, the UART transmitter sends the following to the receiving device:

1 start bit

5, 6, 7, or 8 data bits

1 parity bit (optional)

1, 1.5, or 2 stop bits

URTHR receives data from the internal data bus, and when URTSR is ready, the UART moves the data from URTHR to URTSR. The UART serializes the data in URTSR and transmits the data on the TX pin.

In the non-FIFO mode, if URTHR is empty and the THR-empty interrupt is enabled in the interrupt enable register (URIER), an interrupt is generated. This interrupt is cleared when a character is loaded into URTHR. In the FIFO mode, the interrupt is generated when the transmitter FIFO is empty, and it is cleared when at least one byte is loaded into the FIFO.

#### 1.2 Reception

The UART receiver section includes a receiver shift register (URRSR) and a receive buffer register (URRBR). When the UART is in the FIFO mode, URRBR is a 16-byte FIFO. Timing is supplied by the 16× receiver clock. Receiver section control is a function of the UART line control register (URLCR). Based on the settings chosen in URLCR, the UART receiver accepts the following from the transmitting device:

1 start bit

5, 6, 7, or 8 data bits

1 parity bit (optional)

1 stop bit (any other stop bits transferred with the above data are not detected)

URRSR receives the data bits from the RX pin. Then URRSR concatenates the data bits and moves the resulting value into URRBR (or the receiver FIFO). The UART also stores three bits of error status information next to each received character, to record a parity error, framing error, or break.

In the non-FIFO mode, when a character is placed in URRBR and the receiver data-ready interrupt is enabled in the interrupt enable register (URIER), an interrupt is generated. This interrupt is cleared when the character is read from URRBR. In the FIFO mode, the interrupt is generated when the FIFO is filled to the trigger level selected in the FIFO control register (URFCR), and it is cleared when the FIFO contents drop below the trigger level.

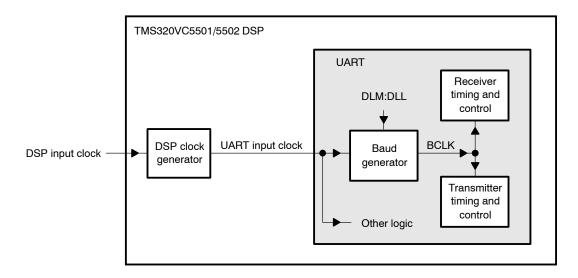

#### 2 Programmable Baud Generator

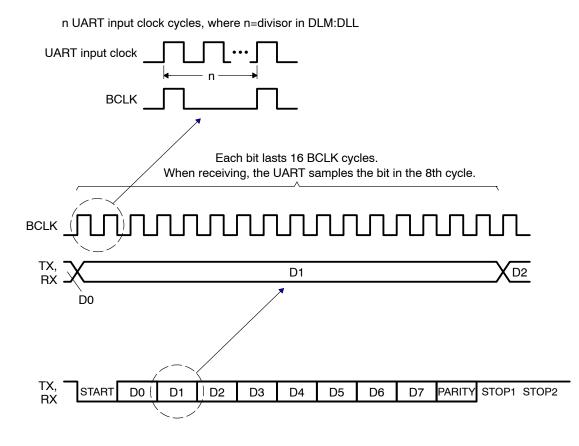

Figure 2 is a conceptual clock generation diagram for the UART. The DSP clock generator receives a signal from an external clock source and produces a **UART input clock** with a programmed frequency. Please refer to the device specific data manual for more information regarding the UART input clock. The UART contains a programmable baud generator that takes an input clock and divides it by a divisor in the range between 1 and  $(2^{16}-1)$  to produce a **baud clock (BCLK)**. The frequency of BCLK is sixteen times  $(16\times)$  the baud rate; each received or transmitted bit lasts 16 BCLK cycles. When the UART is receiving, the bit is sampled in the 8th BCLK cycle. The formula to calculate the divisor is:

$Divisor = \frac{UART \text{ input clock frequency}}{Desired \text{ baud rate } \times 16}$

Two 8-bit register fields (DLM and DLL), called divisor latches, hold this 16-bit divisor. DLM holds the most significant bits of the divisor, and DLL holds the least significant bits of the divisor. For information about these register fields, see section 6.3 on page 23. These divisor latches must be loaded during initialization of the UART in order to ensure desired operation of the baud generator. Writing to the divisor latches results in two wait states being inserted during the write access while the baud generator is loaded with the new value.

Figure 2. UART Clock Generation Diagram

Figure 3 summarizes the relationships among the transferred data bit, BCLK, and the UART input clock.

Figure 3. Relationships Among Data Bit, BCLK, and UART Input Clock

Table 1 and Table 2 illustrate the use of the baud generator with UART input clock frequencies of 1.8432 MHz and 3.072 MHz respectively. For baud rates of 38.4 kbits/s and below, the error obtained is very small. The accuracy of the selected baud rate is dependent on the selected clock frequency.

#### Note:

6

The clock rates in Table 1 and Table 2 are shown as examples only, to illustrate the relationship of clock rate and divisor value to baud rate and baud rate error. Typically, higher clock rates will be used, and error values will differ accordingly.

| Desired<br>Baud Rate | Divisor Used<br>to Generate<br>16 × Clock | Percent Error<br>Difference Between<br>Desired and Actual |

|----------------------|-------------------------------------------|-----------------------------------------------------------|

| 50                   | 2304                                      |                                                           |

| 75                   | 1536                                      |                                                           |

| 110                  | 1047                                      | 0.026                                                     |

| 134.5                | 857                                       | 0.058                                                     |

| 150                  | 768                                       |                                                           |

| 300                  | 384                                       |                                                           |

| 600                  | 192                                       |                                                           |

| 1200                 | 96                                        |                                                           |

| 1800                 | 64                                        |                                                           |

| 2000                 | 58                                        | 0.69                                                      |

| 2400                 | 48                                        |                                                           |

| 3600                 | 32                                        |                                                           |

| 4800                 | 24                                        |                                                           |

| 7200                 | 16                                        |                                                           |

| 9600                 | 12                                        |                                                           |

| 19200                | 6                                         |                                                           |

| 38400                | 3                                         |                                                           |

| 56000                | 2                                         | 2.86                                                      |

| Table 1. Baud Rates Using 1.8432 MHz for the UART Input Clock |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

#### Programmable Baud Generator

| Desired<br>Baud Rate | Divisor Used<br>to Generate<br>16 × Clock | Percent Error<br>Difference Between<br>Desired and Actual |

|----------------------|-------------------------------------------|-----------------------------------------------------------|

| 50                   | 3840                                      |                                                           |

| 75                   | 2560                                      |                                                           |

| 110                  | 1745                                      | 0.026                                                     |

| 134.5                | 1428                                      | 0.034                                                     |

| 150                  | 1280                                      |                                                           |

| 300                  | 640                                       |                                                           |

| 600                  | 320                                       |                                                           |

| 1200                 | 160                                       |                                                           |

| 1800                 | 107                                       | 0.312                                                     |

| 2000                 | 96                                        |                                                           |

| 2400                 | 80                                        |                                                           |

| 3600                 | 53                                        | 0.628                                                     |

| 4800                 | 40                                        |                                                           |

| 7200                 | 27                                        | 1.23                                                      |

| 9600                 | 20                                        |                                                           |

| 19200                | 10                                        |                                                           |

| 38400                | 5                                         |                                                           |

Table 2. Baud Rates Using 3.072 MHz for the UART Input Clock

#### 3 Interrupt Requests and DMA Events Generated by the UART

The UART can generate the types of interrupt request described in section 3.1. Two of these can tell the CPU when to write transmit data and when to read receive data. If you want the DMA controller to handle transmit and receive data in the FIFO mode, you can use the two DMA events described in section 3.2.

#### 3.1 UART Interrupt Requests

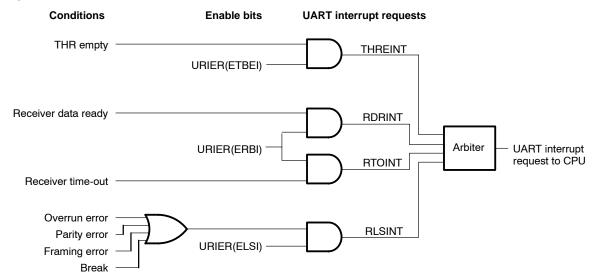

The UART generates the interrupt requests described in Table 3. As shown in Figure 4 (page 12), all requests are multiplexed through an arbiter to a single UART interrupt request to the CPU. Each of interrupt requests has an enable bit in the interrupt enable register (URIER) and can be recorded in the interrupt identification register (URIIR).

If an interrupt occurs and the corresponding enable bit is 1, the interrupt request is recorded in URIIR and is forwarded to the CPU. The recording in URIIR has two parts:

- The code for the interrupt request is written to the interrupt identification (IID) field. If multiple interrupt requests are enabled and they are generated simultaneously, the highest priority request is the one that is recorded in IID. A recorded code remains in IID until it is changed by one of the following events, whichever occurs first:

- The condition that caused the interrupt is cleared. IID is filled with the code 000b.

- Another interrupt occurs. IID is filled with the code for the new interrupt.

- A hardware reset occurs. IID is filled with the code 000b.

- The interrupt pending (IP) bit is made active (0) if it is not already active due to previous pending interrupts. IP remains 0 until all conditions that generated pending interrupts are cleared or until a hardware reset occurs.

If an interrupt occurs and the corresponding enable bit is 0, the interrupt request is blocked. The interrupt request is neither recorded in URIIR nor forwarded to the CPU.

The UART interrupt is one of the maskable interrupts of the CPU. As with any maskable interrupt, if it is properly enabled in the CPU, the CPU executes the corresponding interrupt service routine (ISR). The ISR for the UART interrupt can determine the interrupt source by reading the IID field of URIIR. Then the ISR can branch to the appropriate subroutine.

When multiple interrupts might be pending, the ISR can also store a copy of the line status register (URLSR). With only two exceptions, the operational events that generate interrupts also set status bits in URLSR. The exceptions are a receiver time-out event and the event of reaching the trigger level in the receiver FIFO; neither of these events has an associated status bit.

|                                                                        | -                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART<br>Interrupt<br>Request                                           | Interrupt Source                                                                                                                                                                               | Comments                                                                                                                                                                                                                                                                                                              |

| THREINT                                                                | THR-empty condition: The transmitter holding register (URTHR) or the transmitter FIFO is empty. All of the data has been copied from URTHR to the transmitter shift register (URTSR).          | If THREINT is enabled in the interrupt enable register<br>(URIER), it is recorded in the interrupt identification<br>register (URIIR). For more details about the THR-empty<br>condition, including the event that clears it, see Table 13<br>on page 28.<br>As an alternative to using THREINT, the CPU can poll the |

| This c<br>ready<br>buffer<br>the trig<br>receive<br>times <sup>†</sup> | Receiver data-ready condition:<br>This condition exists when data is<br>ready to be read from the receiver                                                                                     | THRE bit of the line status register, URLSR (see page 34).<br>If RDRINT is enabled in URIER, it is recorded in URIIR. For<br>more details about the receiver data-ready condition,<br>including the event that clears it, see Table 13 on page 28.                                                                    |

|                                                                        | buffer register (URRBR) or when<br>the trigger level is reached in the<br>receiver FIFO. If four character<br>times <sup>†</sup> pass with no access of the<br>FIFO, RDRINT is asserted again. | As an alternative to using RDRINT, the CPU can poll the DR bit of URLSR. In the FIFO mode, this is not a functionally equivalent alternative because the DR bit does not respond to the FIFO trigger level. The DR bit only indicates the presence or absence of unread characters.                                   |

Table 3.

Descriptions of the UART Interrupt Requests

<sup>†</sup> A character time is the time allotted for 1 start bit, n data bits, 1 parity bit, and 1 stop bit, where n depends on the word length selected with the WLS bits of URLCR:

| Word Length | Character Time   | Four Character Times |

|-------------|------------------|----------------------|

| n = 5       | Time for 8 bits  | Time for 32 bits     |

| n = 6       | Time for 9 bits  | Time for 36 bits     |

| n = 7       | Time for 10 bits | Time for 40 bits     |

| n= 8        | Time for 11 bits | Time for 44 bits     |

| UART<br>Interrupt<br>Request | Interrupt Source                                                                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                      |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTOINT                       | Receiver time-out condition (in the<br>FIFO mode only): No characters<br>have been removed from or input to<br>the receiver FIFO during the last<br>four character times <sup>†</sup> , and there is<br>at least one character in the<br>receiver FIFO during this time. | The receiver time-out interrupt prevents the UART from waiting indefinitely in the case when the receiver FIFO level is below the trigger level and thus does not generate a receiver data-ready interrupt.                                                                   |

|                              |                                                                                                                                                                                                                                                                          | If RTOINT is enabled in URIER, it is recorded in URIIR. For<br>more details about the receiver time-out condition,<br>including the events that clear it, see Table 13 on page 28.                                                                                            |

|                              |                                                                                                                                                                                                                                                                          | There is no status bit to reflect the occurrence of a time-out condition.                                                                                                                                                                                                     |

| RLSINT                       | Receiver line status condition: An overrun error, parity error, framing error, or break has occurred.                                                                                                                                                                    | If RLSINT is enabled in URIER, it is recorded in URIIR. For<br>more details about the receiver line status condition,<br>including the events that clear it, see Table 13 on page 28.                                                                                         |

|                              |                                                                                                                                                                                                                                                                          | As an alternative to using RLSINT, the CPU can poll the following bits of URLSR: overrun error indicator (OE), parity error indicator (PE), framing error indicator (FE), and break indicator (BI). <b>Note:</b> As soon as the CPU reads URLSR, OE is automatically cleared. |

Table 3.

Descriptions of the UART Interrupt Requests (Continued)

<sup>†</sup> A character time is the time allotted for 1 start bit, n data bits, 1 parity bit, and 1 stop bit, where n depends on the word length selected with the WLS bits of URLCR:

| Word Length | Character Time   | Four Character Times |

|-------------|------------------|----------------------|

| n = 5       | Time for 8 bits  | Time for 32 bits     |

| n = 6       | Time for 9 bits  | Time for 36 bits     |

| n = 7       | Time for 10 bits | Time for 40 bits     |

| n= 8        | Time for 11 bits | Time for 44 bits     |

#### Figure 4. Enable Paths of the UART Interrupt Requests

#### 3.2 UART DMA Events

In the FIFO mode, the UART generates the following two DMA events. Activity in DMA channels can be synchronized to these events. In the non–FIFO mode, the UART generates no DMA events.

- Receive event (REVT): The trigger level for the receiver FIFO (1, 4, 8, or 14 characters) is set with the RFITR bits of URFCR (see section 6.6 on page 29). Every time the trigger level is reached or a receiver time-out occurs, the UART sends a receive event to the DMA controller. In response, the DMA controller can read the data from the receiver FIFO via URRBR.

- Transmit event (XEVT): When the transmitter FIFO is empty (when the last byte in the transmitter FIFO has been copied to the transmitter shift register), the UART sends an XEVT signal to the DMA controller. In response, the DMA controller can refill the transmitter FIFO via URTHR. The XEVT signal is also sent to the DMA controller when the UART is taken out of reset using the URST bit of the URPECR.

Any DMA channel synchronized to either of these events must be enabled at the time the UART event is generated. Otherwise, the DMA channel will miss the event and, unless the UART generates a new event, no data transfer will occur.

#### 4 FIFO Modes

The following two modes can be used for servicing each of the FIFOs (transmitter FIFO and receiver FIFO):

- □ FIFO interrupt mode. The FIFO is enabled and the associated interrupts are enabled. Interrupts are sent to the CPU to indicate when specific events occur.

- FIFO poll mode. The FIFO is enabled but the associated interrupts are disabled. The CPU polls status bits to detect specific events.

Because the receiver FIFO and the transmitter FIFO are controlled separately, either one or both can be placed into the interrupt mode or the poll mode.

#### 4.1 FIFO Interrupt Mode

When the receiver FIFO is enabled in URFCR and the receiver interrupts are enabled in URIER, the interrupt mode is selected for the receiver FIFO. The following are important points about the receiver interrupts:

- The receiver data-ready interrupt is issued to the CPU when the FIFO has reached the trigger level that is programmed in URFCR. It is cleared when the CPU or the DMA controller reads enough characters from the FIFO such that the FIFO drops below its programmed trigger level.

- The receiver line status interrupt is generated in response to an overrun error, a parity error, a framing error, or a break. This interrupt has higher priority than the receiver data-ready interrupt. For details, see Table 13 on page 28.

- The data-ready bit (DR) of URLSR indicates the presence or absence of characters in the receiver FIFO. The DR bit is set when a character is transferred from the receiver shift register (URRSR) to the empty receiver FIFO. The bit remains set until the FIFO is empty again.

- A receiver time-out interrupt occurs if all of the following conditions exist:

- At least one character is in the FIFO,

- The most recent character was received more than four continuous character times ago. A character time is the time allotted for 1 start bit, n data bits, 1 parity bit, and 1 stop bit, where n depends on the word length selected with the WLS bits of URLCR:

| Word Length | Character Time   | Four Character Times |

|-------------|------------------|----------------------|

| n = 5       | Time for 8 bits  | Time for 32 bits     |

| n = 6       | Time for 9 bits  | Time for 36 bits     |

| n = 7       | Time for 10 bits | Time for 40 bits     |

| n= 8        | Time for 11 bits | Time for 44 bits     |

- The most recent DSP read of the FIFO has occurred more than four continuous character times before.

- Character times are calculated by using the baud rate.

- When a receiver time-out interrupt has occurred, it is cleared and the timeout timer is cleared when the CPU or the DMA controller reads one character from the receiver FIFO. The interrupt is also cleared if a new character is received in the FIFO or if the URST bit is cleared in the power and emulation control register (URPECR).

- ☐ If a receiver time-out interrupt has not occurred, the time-out timer is cleared after a new character is received or after the DSP reads the receiver FIFO.

When the transmitter FIFO is enabled in URFCR and the transmitter holding register empty interrupt is enabled in URIER, the interrupt mode is selected for the transmitter FIFO. The transmitter holding register empty interrupt occurs when the transmitter FIFO is empty. It is cleared when URTHR is loaded (1 to 16 characters may be written to the transmitter FIFO while servicing this interrupt).

#### 4.2 FIFO Poll Mode

When the receiver FIFO is enabled in URFCR and the receiver interrupts are disabled in URIER, the poll mode is selected for the receiver FIFO. Similarly, when the transmitter FIFO is enabled and the transmitter interrupts are disabled, the transmitted FIFO is in the poll mode. In the poll mode, the CPU detects events by checking bits in the line status register (URLSR):

- The RFIER bit indicates whether there are any errors in the receiver FIFO.

- □ The TEMT bit indicates that both the transmitter holding register (URTHR) and the transmitter shift register (URTSR) are empty.

- The THRE bit indicates when URTHR is empty.

- □ The BI (break), FE (framing error), PE (parity error), and OE (overrun error) bits specify which error or errors have occurred.

- The DR (data-ready) bit is set as long as there is at least one byte in the receiver FIFO.

Also, in the FIFO poll mode:

- URIIR is not affected by any events because the interrupts are disabled.

- ☐ The UART does not indicate when the receiver FIFO trigger level is reached or when a receiver time-out occurs.

#### 5 Power, Emulation, and Reset Considerations

#### 5.1 Conserving Power

The DSP is divided into a number of idle domains. To minimize power consumption, you can choose which domains are active and which domains are idle at any given time. The current state of all domains is collectively called the *idle configuration*. If a particular idle configuration turns off the peripherals domain, the UART may enter an inactive, low-power mode, depending on other factors described in the device-specific data manual. When the UART is successfully requested to enter this idle mode:

- If a data transfer is in progress, the UART first completes the transfer and generates any interrupts and/or DMA events that it is programmed to generate. Then the UART enters its idle mode.

- If no data is being transferred, the UART enters its idle mode immediately.

Keep in mind that idle domains other than the peripherals domain can affect the UART. If the clock generator domain is idle, the UART has no clocks for operation, and if the DMA domain is idle, the DMA controller cannot respond to DMA events from the UART.

#### 5.2 Emulation Mode

The FREE bit of the power and emulation control register (URPECR) determines how the UART responds to an emulator-related operation such as a debugger breakpoint. If FREE = 0 and a transmission is in progress, the UART stops after completing the one-word transmission. If FREE = 0 and a transmission is not in progress, the UART stops immediately. If FREE = 1, the UART does not stop.

#### 5.3 Emulator Access Support

The UART supports non-intrusive emulator access; that is, an emulator can access the UART without affecting any of the UART register values.

#### 5.4 Resetting the UART

The UART can be reset in two ways:

- UART reset. Write 0 to the UART reset bit (URST) in the power and emulation control register (URPECR). This action resets the UART state machine but does not affect the UART registers.

- DSP reset. Drive the RESET pin low. The entire DSP is reset and is held in the reset state until you drive the pin high. As part of a DSP reset, the UART state machine is reset, and the UART registers are forced to their default states. The default states of the registers and of the data transmit (TX) signal are listed in Table 4.

#### Notes:

- The divisor latch registers (URDLM and URDLL) are not affected during a hardware reset or by a UART software reset and **must be loaded after power up**. Make sure the correct divisor is in these registers (to provide the desired baud rate) before initiating serial communications.

- For proper operation of the UART, the 16-bit divisor in URDLM and URDLL must be greater than 0.

- 3) For proper communication between the UART and the DMA controller, the DMA mode (DMAMOD) bit of URFCR must be 1. Always write 1 to DMAMOD, and after a hardware reset, change DMAMOD from 0 to 1.

Table 4. Default State of Registers and TX Signal

| Register/Signal                               | Default State                               |

|-----------------------------------------------|---------------------------------------------|

| Interrupt enable register (URIER)             | All bits cleared                            |

| Interrupt identification register (URIIR)     | Bit 0 is set. All other bits cleared        |

| FIFO control register (URFCR)                 | All bits cleared                            |

| Line control register (URLCR)                 | All bits cleared                            |

| Modem control register (URMCR)                | All bits cleared                            |

| Line status register (URLSR)                  | Bit 5 and 6 are set, all other bits cleared |

| Receiver buffer register (URRBR)              | Pointer logic for receiver FIFO cleared     |

| Transmitter holding register (URTHR)          | Pointer logic for transmitter FIFO cleared  |

| Scratch register (URSCR)                      | (Not affected by reset)                     |

| Divisor latch registers (URDLL and URDLM)     | (Not affected by reset)                     |

| Power and emulation control register (URPECR) | Bit 1 is set. All other bits cleared        |

| TX signal                                     | High                                        |

#### 6 UART Registers

The system programmer has access to and control over any of the UART registers that are summarized in Table 5. A visual summary of the registers and their contents follows in Table 6. These registers, which control UART operations, receive data, and transmit data, are available at 16-bit addresses in the I/O space of the DSP. As on the industry-standard TL16C550 asynchronous communications element:

- URRBR, URTHR, and URDLL share one address. When the DLAB bit of URLCR is 0, reading from the address gives the content of URRBR, and writing to the address modifies URTHR. When DLAB = 1, all accesses at the address read or modify URDLL.

- URIER and URDLM share one address. When DLAB = 0, all accesses read or modify URIER. When DLAB = 1, all accesses read or modify URDLM.

- URIIR and URFCR share one address. Regardless of the value of the DLAB bit, reading from the address gives the content of URIIR, and writing to the address modifies URFCR.

URDLL and URDLM also have dedicated addresses. If you use the dedicated addresses, you can keep the DLAB bit cleared, so that URRBR, URTHR, and URIER are always selected at the shared addresses.

#### Note:

Do not write to the control registers while a serial transfer is in progress. The UART expects the contents of the control registers to be static during a serial transfer.

|                                        | •                                                                                                                                                      |                                                       |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Register                               | Description                                                                                                                                            | Access Information                                    |

| URRBR/<br>URTHR/<br>URDLL <sup>†</sup> | Receiver buffer register (see page 21)/<br>Transmitter holding register (see page 22)/<br>Divisor latch register, least significant bits (see page 23) | If DLAB = 0:<br>Read only: URRBR<br>Write only: URTHR |

|                                        |                                                                                                                                                        | If DLAB = 1:<br>Read/Write: URDLL                     |

| URIER/<br>URDLM‡                       | Interrupt enable register (see page 24)/<br>Divisor latch register, most significant bits (see page 23)                                                | If DLAB = 0:<br>Read/Write: URIER                     |

|                                        |                                                                                                                                                        | If DLAB = 1:<br>Read/Write: URDLM                     |

| URIIR/<br>URFCR§                       | Interrupt identification register (see page 25)/<br>FIFO control register (see page 29)                                                                | Read only: URIIR<br>Write only: URFCR                 |

| URLCR                                  | Line control register (see page 30)                                                                                                                    | Read/Write: URLCR                                     |

| URMCR                                  | Modem control register (see page 34)                                                                                                                   | Read/Write: URMCR                                     |

| URLSR                                  | Line status register (see page 34)                                                                                                                     | Read only: URLSR                                      |

| URSCR                                  | Scratch register (see page 39)                                                                                                                         | Read/Write: URSCR                                     |

| URDLL <sup>†</sup>                     | Divisor latch register, least significant bits (see page 23)                                                                                           | Read/Write: URDLL                                     |

| URDLM <sup>‡</sup>                     | Divisor latch register, most significant bits (see page 23)                                                                                            | Read/Write: URDLM                                     |

| URPECR                                 | Power and emulation control register (see page 39)                                                                                                     | Read/Write: URPECR                                    |

#### Table 5. UART Registers

<sup>†</sup> The registers URRBR, URTHR, and URDLL share one address. URDLL also has a dedicated address. If you use the dedicated address, you can keep the DLAB bit cleared, so that URRBR and URTHR are always selected at the shared address.

<sup>‡</sup> The registers URIER and URDLM share one address. URDLM also has a dedicated address. If you use the dedicated address, you can keep the DLAB bit cleared, so that URIER is always selected at the shared address.

<sup>§</sup> The registers URIIR and URFCR share one address.

|     |                                                | Register                                         |     |                                  |                    |                                   |                                    |       |       |       |       |        |

|-----|------------------------------------------------|--------------------------------------------------|-----|----------------------------------|--------------------|-----------------------------------|------------------------------------|-------|-------|-------|-------|--------|

| Bit | URRBR <sup>†</sup><br>(DLAB = 0;<br>Read only) | URTHR <sup>†</sup><br>(DLAB = 0);<br>Write only) |     | URIER <sup>‡</sup><br>(DLAB = 0) | urdlm <sup>‡</sup> | URIIR <sup>§</sup><br>(Read only) | URFCR <sup>§</sup><br>(Write only) | URLCR | URMCR | URLSR | URSCR | URPECR |

| 15  | _                                              | _                                                | _   | _                                | _                  | _                                 | _                                  | —     | —     | —     | —     | URST   |

| 14  | _                                              | _                                                | _   | _                                | _                  | _                                 | _                                  | _     | —     | —     | —     | _      |

| 13  | _                                              | _                                                | —   | _                                | —                  | _                                 | _                                  | _     | —     | —     | —     | —      |

| 12  | _                                              | _                                                | _   | —                                | _                  | _                                 | _                                  | _     | —     | —     | —     | _      |

| 11  | _                                              | _                                                | _   | _                                | _                  | _                                 | _                                  | —     | —     | —     | —     | —      |

| 10  |                                                |                                                  | _   | _                                | _                  | _                                 | _                                  | _     | —     | —     | —     | _      |

| 9   |                                                |                                                  | _   | —                                | _                  | _                                 | _                                  | _     | —     | _     | _     | —      |

| 8   | _                                              | _                                                | _   | _                                | _                  | _                                 | _                                  | —     | _     | _     | _     | —      |

| 7   |                                                |                                                  |     | _                                |                    |                                   | DEITO                              | DLAB  | —     | RFIER |       | —      |

| 6   |                                                |                                                  |     | —                                |                    | FIENR                             | RFITR                              | BC    | _     | TEMT  |       | _      |

| 5   |                                                |                                                  |     | _                                |                    | _                                 | _                                  | STPAR | _¶    | THRE  |       | —      |

| 4   | DATA                                           | DATA                                             | DLL | _                                | DLM                | _                                 | _                                  | EPS   | LOOP  | ВІ    | SCR   | _      |

| 3   | DAIA                                           | DAIA                                             | DLL | _¶                               | DLIVI              |                                   | DMAMOD <sup>#</sup>                | PEN   | _¶    | FE    | 30n   | _      |

| 2   |                                                |                                                  |     | ELSI                             |                    | IID                               | TFIRS                              | STB   | _¶    | PE    |       | _      |

| 1   |                                                |                                                  |     | ETBEI                            |                    |                                   | RFIRS                              | WLS   | _¶    | OE    |       | _      |

| 0   |                                                |                                                  |     | ERBI                             |                    | IP                                | FIEN                               | vvLS  | _¶    | DR    |       | FREE   |

#### Table 6. Visual Summary of the UART Registers

Note: A dash (---) indicates a reserved bit.

<sup>†</sup> URRBR, URTHR, and URDLL share one address, and URDLL also has a dedicated address. To access URRBR and URTHR, you must clear the DLAB bit of URLCR and use the shared address. For URDLL, you can use the shared address when DLAB = 1, or you can use the dedicated address.

<sup>‡</sup> URIER and URDLM share one address, and URDLM also has a dedicated address. To access URIER, you must clear the DLAB bit of URLCR and use the shared address. For URDLM, you can use the shared address when DLAB = 1, or you can use the dedicated address.

§ URIIR and URFCR share one address. Reading from the shared address returns the content of URIIR. Writing to the shared address modifies the content of URFCR.

<sup>¶</sup> Always write 0 to these reserved bits.

<sup>#</sup> Always write 1 to DMAMOD. After a hardware reset, change this bit from 0 to 1. DMAMOD = 1 is required for proper communication between the UART and the DMA controller.

#### 6.1 Receiver Buffer Register (URRBR)

The UART receiver section consists of a receiver shift register (URRSR) and a receive buffer register (URRBR). The bit fields of URRBR are shown in Figure 5 and summarized in Table 7. When the UART is in the FIFO (TL16C550) mode, URRBR is a 16-byte FIFO. Timing is supplied by the  $16 \times$  receiver clock. Receiver section control is a function of the line control register (URLCR).

URRSR receives serial data from the RX pin. Then URRSR concatenates the data and moves it into URRBR (or the receiver FIFO). In the non-FIFO (TL16C450) mode, when a character is placed in URRBR and the receiver data-ready interrupt is enabled (DR = 1 in URIER), an interrupt is generated. This interrupt is cleared when the character is read from URRBR. In the FIFO mode, the interrupt is generated when the FIFO is filled to the trigger level selected in the FIFO control register (URFCR), and it is cleared when the FIFO contents drop below the trigger level.

Access considerations. URRBR, URTHR, and URDLL share one address. To read URRBR, write 0 to the DLAB bit of URLCR, and read from the shared address. When DLAB = 0, writing to the shared address modifies URTHR. When DLAB = 1, all accesses at the shared address read or modify URDLL.

URDLL also has a dedicated address. If you use the dedicated address, you can keep DLAB = 0, so that URRBR and URTHR are always selected at the shared address.

Figure 5. Receiver Buffer Register (URRBR)

| 15       | 8 | 7    | 0 |

|----------|---|------|---|

| Reserved |   | DATA |   |

| R-0      |   | R-U  |   |

**Legend:** R = Read; -n = Value after reset; -U = Value unchanged by reset

Table 7. Receiver Buffer Register (URRBR) Field Descriptions

| Bit  | Field    | Value   | Description                                                                                                                                              |

|------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8 | Reserved |         | Reading this field returns 0s. Writing to this field has no effect.                                                                                      |

| 7–0  | DATA     | 00h-FFh | Received data. Once a data value has been shifted into the receiver shift register (URRSR), it is transferred to URRBR, where it can be read by the DSP. |

|      |          |         |                                                                                                                                                          |

#### 6.2 Transmitter Holding Register (URTHR)

The UART transmitter section consists of a transmitter hold register (URTHR) and a transmitter shift register (URTSR). The bit fields of URTHR are shown in Figure 6 and summarized in Table 8. When the UART is in the FIFO (TL16C550) mode, URTHR is a 16-byte FIFO. Transmitter section control is a function of the UART line control register (URLCR).

URTHR receives data from the internal data bus and when URTSR is idle, the UART moves the data from URTHR to URTSR. The UART serializes the data in URTSR and transmits the data on the TX pin. In the non-FIFO (TL16C450) mode, if URTHR is empty and the THR-empty (THRE) interrupt is enabled (ETBEI = 1 in URIER), an interrupt is generated. This interrupt is cleared when a character is loaded into URTHR. In the FIFO mode, the interrupt is generated when the transmitter FIFO is empty, and it is cleared when at least one byte is loaded into the FIFO.

Access considerations. URRBR, URTHR, and URDLL share one address. To load URTHR, write 0 to the DLAB bit of URLCR, and write to the shared address. When DLAB = 0, reading from the shared address gives the content of URRBR. When DLAB = 1, all accesses at the address read or modify URDLL.

URDLL also has a dedicated address. If you use the dedicated address, you can keep DLAB = 0, so that URRBR and URTHR are always selected at the shared address.

| Figure 6. | Transmitter Holding Register (URTHR) |  |

|-----------|--------------------------------------|--|

|           |                                      |  |

| 15 8     | 7 0  |

|----------|------|

| Reserved | DATA |

| R-0      | W-U  |

Legend: R = Read; W = Write; -n = Value after reset; -U = Value unchanged by reset

| Table 8. | Transmitter I | Holdina Reaister | (URTHR) | Field Descriptions |

|----------|---------------|------------------|---------|--------------------|

|          |               |                  |         |                    |

| Bit  | Field    | Value   | Description                                                                                                                                                                     |

|------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8 | Reserved |         | Reading this field returns 0s. Writing to this field has no effect.                                                                                                             |

| 7–0  | DATA     | 00h-FFh | Transmit data. To transmit data, the DSP must write the data to this field.<br>When the transmitter shift register (URTSR) is idle, the content of URTHR<br>is copied to URTSR. |

Universal Asynchronous Receiver/Transmitter (UART)

23

#### 6.3 Divisor Latch Registers (URDLL and URDLM)

Two 8-bit register fields (DLM and DLL), called divisor latches, store the 16-bit divisor for generation of the baud clock in the baud generator. The latches are in registers URDLM and URDLL (see Figure 7, Table 9, and Table 10). DLM holds the most significant bits of the divisor, and DLL holds the least significant bits of the divisor. These divisor latches must be loaded during initialization of the UART in order to ensure desired operation of the baud generator. Writing to the divisor latches results in two wait states being inserted during the write access while the baud generator is loaded with the new value.

#### Notes:

- The divisor latch registers are not affected during a hardware reset or by a UART software reset and **must be loaded after power up**. Make sure the correct divisor is in these registers (to provide the desired baud rate) before initiating serial communications.

- 2) For proper operation of the UART, the 16-bit divisor in the divisor latch registers must be greater than 0.

**Access considerations.** As on the industry standard TL16C550 asynchronous communications element:

- URRBR, URTHR, and URDLL share one address. When DLAB = 1 in URLCR, all accesses at the shared address are accesses to URDLL.

When DLAB = 0, reading from the shared address gives the content of URRBR, and writing to the shared address modifies URTHR.

- URIER and URDLM share one address. When DLAB = 1 in URLCR, accesses to the shared address read or modify to URDLM. When DLAB = 0, all accesses at the shared address read or modify URIER.

URDLL and URDLM also have dedicated addresses. If you use the dedicated addresses, you can keep the DLAB bit cleared, so that URRBR, URTHR, and URIER are always selected at the shared addresses.

#### Figure 7. Divisor Latch Registers (URDLM and URDLL)

#### URDLM

Legend: R = Read; W = Write; -n - Value after reset; -U = Value unchanged by reset

Table 9. Divisor Latch Register – Most Significant Bits (URDLM) Field Descriptions

| Bit  | Field    | Value   | Value Description                                                      |  |  |

|------|----------|---------|------------------------------------------------------------------------|--|--|

| 15–8 | Reserved |         | Reading this field returns 0s. Writing to this field has no effect.    |  |  |

| 7–0  | DLM      | 00h-FFh | Use DLM to program the most significant bits of the baud rate divisor. |  |  |

Table 10. Divisor Latch Register – Least Significant Bits (URDLL) Field Descriptions

| Bit  | Field    | Value   | Description                                                             |

|------|----------|---------|-------------------------------------------------------------------------|

| 15–8 | Reserved |         | Reading this field returns 0s. Writing to this field has no effect.     |

| 7–0  | DLL      | 00h-FFh | Use DLL to program the least significant bits of the baud rate divisor. |

#### 6.4 Interrupt Enable Register (URIER)

URIER is used to individually enable or disable each type of interrupt request that can be generated by the UART. Each interrupt request that is enabled in URIER is forwarded to the CPU. The content of URIER is shown in Figure 8 and summarized in Table 11.

Access considerations. URIER and URDLM share one address. To read or modify URIER, write 0 to the DLAB bit of URLCR. When DLAB = 1, all accesses at the shared address read or modify URDLM.

URDLM also has a dedicated address. If you use the dedicated address, you can keep DLAB = 0, so that URIER is always selected at the shared address.

24 Universal Asynchronous Receiver/Transmitter (UART)

#### Figure 8. Interrupt Enable Register (URIER)

| 15 4     | 3                     | 2     | 1     | 0     |

|----------|-----------------------|-------|-------|-------|

| Reserved | Reserved <sup>†</sup> | ELSI  | ETBEI | ERBI  |

| R-0      | R/W-0                 | R/W-0 | R/W-0 | R/W-0 |

**Legend:** R = Read; W = Write; -n = Value after reset <sup>†</sup> Write 0 to bit 3.

| Bit  | Field    | Value | Description                                                                                          |  |

|------|----------|-------|------------------------------------------------------------------------------------------------------|--|

| 15–4 | Reserved | 0     | Reading this field returns 0s. Writing to this field has no effect.                                  |  |

| 3    | Reserved | 0     | Always write 0 to this bit.                                                                          |  |

| 2    | ELSI     |       | Enable bit for the receiver line status interrupt request                                            |  |

|      |          | 0     | Interrupt request disabled                                                                           |  |

|      |          | 1     | Interrupt request enabled                                                                            |  |

| 1    | ETBEI    |       | Enable bit for the THR-empty interrupt request                                                       |  |

|      |          | 0     | Interrupt request disabled                                                                           |  |

|      |          | 1     | Interrupt request enabled                                                                            |  |

| 0    | ERBI     |       | Enable bit for the receiver data-ready interrupt request and the receiver time-out interrupt request |  |

|      |          | 0     | Interrupt request disabled                                                                           |  |

|      |          | 1     | Interrupt request enabled                                                                            |  |

#### Table 11. Interrupt Enable Register (URIER) Field Descriptions

#### 6.5 Interrupt Identification Register (URIIR)

The UART has an on-chip interrupt generation and prioritization capability that permits flexible communication with the CPU.

The UART provides three priority levels of interrupts:

- Priority 1 Receiver line status (highest priority)

- Priority 2 Receiver data ready or receiver time-out

- Priority 3 Transmitter holding register empty

When an interrupt is generated and is enabled in URIER, the interrupt identification register (URIIR) indicates that an interrupt is pending in the IP bit and encodes the type of interrupt in the IID field.

The FIENR bit in this register can be checked to determine whether the UART is in the FIFO mode or the non-FIFO mode.

SPRU597B

Universal Asynchronous Receiver/Transmitter (UART) 25

The content of URIIR is shown in Figure 9 and summarized in Table 12. Table 13 explains how to interpret bits 3–0 of URIIR.

Access consideration. URIIR and URFCR share one address. Regardless of the value of the DLAB bit of URLCR, reading from the address gives the content of URIIR, and writing to the address modifies URFCR.

| 15  |          |   |          |     |     |   | 8   |  |

|-----|----------|---|----------|-----|-----|---|-----|--|

|     | Reserved |   |          |     |     |   |     |  |

|     | R-0      |   |          |     |     |   |     |  |

| 7   | 6        | 5 | 4        | 3   |     | 1 | 0   |  |

| FIE | FIENR    |   | Reserved |     | IID |   | IP  |  |

| R   | R-0      |   | -0       | R-0 |     |   | R-1 |  |

Figure 9. Interrupt Identification Register (URIIR)

**Legend:** R = Read; -n = Value after reset

Table 12. Interrupt Identification Register (URIIR) Field Descriptions

| Bit  | Field    | Value | Description                                                         |  |

|------|----------|-------|---------------------------------------------------------------------|--|

| 15–8 | Reserved | 0     | Reading this field returns 0s. Writing to this field has no effect. |  |

| 7–6  | FIENR    |       | FIFO status bit                                                     |  |

|      |          | 00b   | The non-FIFO (TL16C450) mode is selected (FIEN = 0 in URFCR).       |  |

|      |          | 01b   | Reserved                                                            |  |

|      |          | 10b   | Reserved                                                            |  |

|      |          | 11b   | The FIFO mode is selected (FIEN = 1 in URFCR).                      |  |

| 5–4  | Reserved | 0     | Reading this field returns 0s. Writing to this field has no effect. |  |

| Bit | Field | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3–1 | IID   |       | Interrupt identification field. When a UART interrupt is generated and is<br>enabled in URIER, the type of interrupt is encoded in IID as shown in<br>Table 13. If multiple interrupt requests are enabled and they are gener-<br>ated simultaneously, the highest priority request is the one that is re-<br>corded in IID. A recorded code remains in IID until it is changed by one<br>of the following events, whichever occurs first: |  |  |

|     |       |       | ☐ The condition that caused the interrupt is cleared. IID is filled with the code 000b.                                                                                                                                                                                                                                                                                                                                                    |  |  |

|     |       |       | Another interrupt occurs. IID is filled with the code for the new inter-<br>rupt.                                                                                                                                                                                                                                                                                                                                                          |  |  |

|     |       |       | A hardware reset occurs. IID is filled with the code 000b.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|     |       | 011b  | Receiver line status interrupt (priority 1)                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|     |       | 010b  | Receiver data-ready interrupt (priority 2)<br>Receiver time-out interrupt (priority 2)                                                                                                                                                                                                                                                                                                                                                     |  |  |

|     |       | 110b  |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|     |       | 001b  | Transmitter holding register empty interrupt (priority 3)                                                                                                                                                                                                                                                                                                                                                                                  |  |  |