### OMAP5910 Dual-Core Processor Clock Generation and System Reset Management Reference Guide

Literature Number: SPRU678A October 2003 – Revised July 2005

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

t Office Day OFFOOD Dallas Tava

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

### Preface

### **Read This First**

#### About This Manual

This document describes clock generation and system reset for the OMAP5910 multimedia processor.

#### Notational Conventions

This document uses the following conventions.

Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

*OMAP5910 Dual-Core Processor MPU Subsystem Reference Guide* (literature number SPRU671)

**OMAP5910 Dual-Core Processor DSP Subsystem Reference Guide** (literature number SPRU672)

*OMAP5910 Dual-Core Processor Memory Interface Traffic Controller Reference Guide* (literature number SPRU673)

**OMAP5910 Dual-Core Processor System DMA Controller Reference Guide** (literature number SPRU674)

*OMAP5910 Dual-Core Processor LCD Controller Reference Guide* (literature number SPRU675)

OMAP5910 Dual-Core Processor Universal Asynchronous Receiver/Transmitter (UART) Devices Reference Guide (literature number SPRU676)

SPRU678A

OMAP5910 5

OMAP5910 Dual-Core Processor Universal Serial Bus (USB) and Frame Adjustment Counter (FAC) Reference Guide (literature number SPRU677)

OMAP5910 Dual-Core Processor Clock Generation and System Reset Management Reference Guide (literature number SPRU678)

OMAP5910 Dual-Core Processor General-Purpose Input/Output (GPIO) Reference Guide (literature number SPRU679)

*OMAP5910 Dual-Core Processor MMC/SD Reference Guide* (literature number SPRU680)

*OMAP5910 Dual-Core Processor Inter-Integrated Circuit (I2C) Controller Reference Guide* (literature number SPRU681)

**OMAP5910 Dual-Core Processor Timer Reference Guide** (literature number SPRU682)

*OMAP5910 Dual-Core Processor Inter-Processor Communication Reference Guide* (literature number SPRU683)

**OMAP5910 Dual-Core Processor Camera Interface Reference Guide** (literature number SPRU684)

OMAP5905 Dual-Core Processor Multichannel Serial Interface (MCSI) Reference Guide (literature number SPRU685)

**OMAP5910 Dual-Core Processor Micro-Wire Interface Reference Guide** (literature number SPRU686)

OMAP5910 Dual-Core Processor Real-Time Clock (RTC) Reference Guide (literature number SPRU687)

OMAP5910 Dual-Core Processor HDQ/1-Wire Interface Reference Guide (literature number SPRU688)

*OMAP5910 Dual-Core Processor PWL, PWT, and LED Peripheral Reference Guide* (literature number SPRU689)

*OMAP5910 Dual-Core Processor Multichannel Buffered Serial Port (McBSP) Reference Guide* (literature number SPRU708)

#### Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

6 *OMAP5910*

## **Contents**

| 1 |       |                |                                                              |    |

|---|-------|----------------|--------------------------------------------------------------|----|

|   | 1.1   |                | Generation and System Reset Control                          |    |

|   |       | 1.1.1<br>1.1.2 | ULPD Module                                                  |    |

|   |       | 1.1.2          | Reset Module          Clock-Generation and Management Module |    |

|   |       | 1.1.3          |                                                              |    |

|   |       | 1.1.4          | Memory-Mapped Registers                                      |    |

|   |       | 1.1.5          |                                                              | 19 |

| 2 | Clock | Gener          | ation                                                        | 20 |

|   | 2.1   | Clockir        | ng Schemes                                                   | 20 |

|   | 2.2   | Operat         | ing Modes                                                    | 21 |

|   | 2.3   | Extern         | al-Master Mode                                               | 23 |

|   | 2.4   | CLKM           | 1                                                            | 24 |

|   | 2.5   | CLKM2          | 2                                                            | 25 |

|   | 2.6   | CLKM:          | 3                                                            | 28 |

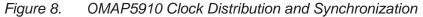

|   | 2.7   | Clock I        | Distribution and Synchronization                             | 30 |

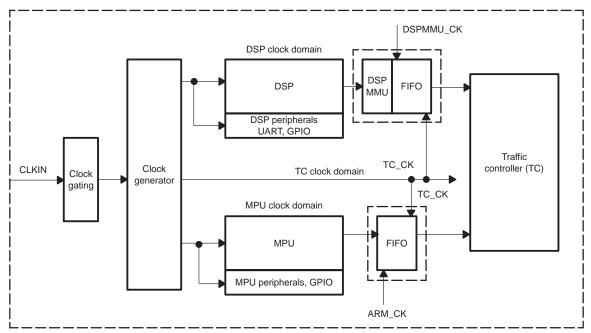

|   | 2.8   | Low-P          | ower Mode                                                    | 31 |

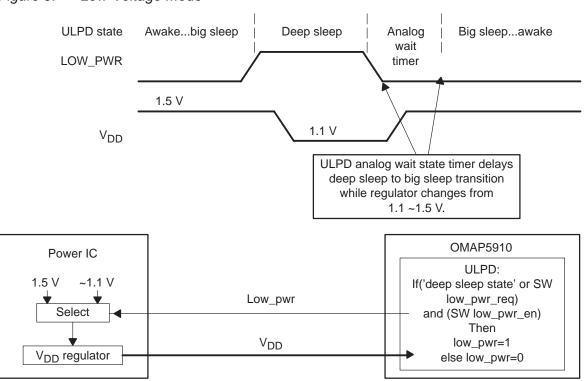

| 3 | Powe  | r Mana         | gement                                                       | 32 |

| Ŭ | 3.1   |                | lle Modes                                                    |    |

|   | 0.1   | 3.1.1          | Putting the DSP in IDLE                                      |    |

|   | 3.2   | MPU-I          | dle Modes                                                    |    |

|   | 0.2   | 3.2.1          | MPU Subdomain (MPU + MPU Interrupt Handler)                  |    |

|   |       | 3.2.2          | DPLL Subdomain                                               |    |

|   |       | 3.2.3          | Peripheral Subdomain                                         |    |

|   | 3.3   | Traffic-       | Controller-Idle Modes                                        |    |

|   |       | 3.3.1          | DPLL-Idle Procedure                                          |    |

|   | 3.4   |                | lle and Wake-Up Control                                      |    |

|   |       | 3.4.1          | Chip-Idle Mode                                               |    |

|   |       | 3.4.2          | Chip-Idle Procedure                                          |    |

|   |       | 3.4.3          | Wake-Up Procedure                                            |    |

|   | 3.5   | Power          | -Saving Capability                                           |    |

|   | 3.6   |                | Power-Management State Machine                               |    |

|   |       | 3.6.1          | Gauging the 32-kHz Oscillator                                |    |

|   |       | 3.6.2          | Gauging Versus the High-Frequency Clock                      |    |

|   |       | 3.6.3          | Control of the 32-kHz Oscillator                             |    |

|   |       | 3.6.4    | Battery Failed                               | . 53 |

|---|-------|----------|----------------------------------------------|------|

|   |       | 3.6.5    | Big-Sleep and Deep-Sleep Mode                | . 54 |

|   |       | 3.6.6    | Power-On Reset                               | . 54 |

|   |       | 3.6.7    | Interrupt Wake-Up                            | . 54 |

|   |       | 3.6.8    | Functional Reset Generation                  | . 54 |

|   | 3.7   | 32-kHz   | Oscillator                                   | . 54 |

|   | 3.8   | 12- or 1 | 13-MHz Oscillator                            | . 55 |

|   | 3.9   | Reset I  | Protocol                                     | . 55 |

|   |       | 3.9.1    | Cold Reset                                   | . 57 |

|   |       | 3.9.2    | Warm Reset                                   |      |

|   |       | 3.9.3    | Watchdog Reset (DSP and MPU)                 | . 58 |

|   |       | 3.9.4    | Warm Reset via MPU_RST                       | . 58 |

|   | 3.10  | Power    | Control for External Devices                 | . 60 |

|   | 3.11  | Configu  | uring Clocks After a Reset                   | . 61 |

| 4 | Clock | Genera   | ation and Reset-Control Registers            | 62   |

| • | 4.1   |          | Dperation Mode Registers                     |      |

|   |       | 4.1.1    | To Switch From DPLL Bypass to DPLL Lock Mode |      |

|   |       | 4.1.2    |                                              |      |

| 5 | Switc | hina Cl  | ock Modes                                    | . 96 |

|   | 5.1   | -        | ng Procedure                                 |      |

|   | 5.2   |          | ode                                          |      |

|   | 5.3   |          | Procedure                                    |      |

| Α | Revis | ion His  | tory                                         | A-1  |

| - | A.1   |          | es Made in This Revision                     |      |

|   |       | 3        |                                              |      |

# Figures

| 1.  | OMARENAL Review Cleak and Report Management     | 4.4 |

|-----|-------------------------------------------------|-----|

|     | OMAP5910 Device Clock and Reset Management      |     |

| 2.  | OMAP5910 Clock Scheme                           |     |

| 3.  | Modules Controlling Clock and Reset Management  | 16  |

| 4.  | Clock Generation and System Reset Module        | 20  |

| 5.  | MPU Clock Distribution                          |     |

| 6.  | DSP Clock Distribution                          | 26  |

| 7.  | Traffic Controller Clock Distribution           | 29  |

| 8.  | OMAP5910 Clock Distribution and Synchronization | 31  |

| 9.  | Low-Voltage Mode                                | 32  |

| 10. | Power Management State Machine                  | 34  |

| 11. | Wake-up Control Module                          |     |

| 12. | Code Example                                    |     |

| 13. | Chip Idle and Wake-Up Control                   | 44  |

| 14. | ULPD Controlled Wake-Up Sequences               | 49  |

| 15. | External Power Control During A Reset Sequence  | 57  |

# **Tables**

| 1.         | Clocking Scheme Selection                                              | 21  |

|------------|------------------------------------------------------------------------|-----|

| 2.         | CLKM–Source Selection—Set via the MPU–System–Status Register           | 21  |

| 3.         | OMAP5910 Wake-Up Peripherals and External Signals                      | 35  |

| 4.         | Recommended Control-Switch Settings                                    |     |

| 5.         | MPU-Clock/Reset/Power Mode-Control Registers – Base Address: FFFE:CE00 | 63  |

| 6.         | MPU-Clock-Control Register (ARM_CKCTL)                                 |     |

| 7.         | TC_CK and LCD_CK Frequency Selections                                  |     |

| 8.         | DSP_CK Frequency Selections                                            |     |

| 9.         | ARM_CK and MPUPER_CK Frequency Selections                              |     |

| 10.        | MPU-Idle-Mode-Entry-1 Register (ARM_IDLECT1)                           |     |

| 11.        | MPU-Idle-Mod-Entry-2 Register (ARM_IDLECT2)                            |     |

| 12.        | MPU-External-Wake-up Register (ARM_EWUPCT)                             |     |

| 13.        | MPU-Reset-Control-1 Register (ARM_RSTCT1)                              |     |

| 14.        | MPU-Reset-Control-2 Register (ARM_RSTCT2)                              |     |

| 15.        | MPU-System-Status-Register (ARM_SYSST)                                 |     |

| 16.        | Clocking Schemes for OMAP5910                                          |     |

| 17.        | DSP-Clock/Reset/Power Mode-Control Registers                           |     |

| 18.        | DSP-Clock -Control Register (DSP_CKCTL) — Offset Address: 0x00         |     |

| 19.        | GPIO CK Selections                                                     |     |

| 20.        | DSP-Idle-Mod-Entry-1 Register (DSP_IDLECT1) – Offset Address: 0x04     |     |

| 21.        | DSP-Idle-Mode-Entry-2 Register (DSP_IDLECT2) – Offset Address: 0x08    | ••• |

|            |                                                                        |     |

|            | 78                                                                     |     |

| 22.        | DSP-Reset-Control-2 Register (DSP_RSTCT2) – Offset Address: 0x14       | 79  |

| 23.        | DSP-System-Status Register (DSP_SYSST) – Offset Address: 0x18          |     |

|            | 80                                                                     |     |

| 24.        | DPLL-Control Registers                                                 | 84  |

| 25.        | DPLL-Control Register (CTL_REG)                                        |     |

| 26.        | ULPD Registers – MPU Base Address: FFFE:0800                           |     |

| 20.<br>27. | Counter-32-LSB Register (COUNTER_32_LSB_REG)                           |     |

| 28.        | Counter-32-LSB Register (COUNTER_32_LSB_REG)                           |     |

| 20.<br>29. | Counter-High-Frequency-LSB Register (COUNTER_HIGH_FREQ_LSB_REG)        |     |

| 29.<br>30. | Counter-High-Frequency-MSB Register (COUNTER_HIGH_FREQ_MSB_REG)        |     |

| 30.<br>31. | Gauging-Control Register (GAUGING_CTRL_REG)                            |     |

| 31.<br>32. | Setup-Analog-Cell-ULPD1 Register (SETUP_ANALOG_CELL3_ULPD1_REG)        |     |

|            |                                                                        |     |

| 33.        | Interrupt-Status Register (IT_STATUS_REG)                              | ØΫ  |

10

| 34. | Clock-Control Register (CLOCK_CTRL_REG)        | 88 |

|-----|------------------------------------------------|----|

| 35. | Software-Clock-Request Register (SOFT_REQ_REG) | 89 |

| 36. | Counter-32-FIQ Register (COUNTER_32_FIQ_REG)   | 89 |

| 37. | DPLL-Control Register (DPLL_CTRL_REG)          | 90 |

| 38. | Status-Request Register (STATUS_REQ_REG)       | 91 |

| 39. | Lock-Time Register (LOCK_TIME)                 | 92 |

| 40. | APLL-Control Register (APLL_CTRL_REG)          | 92 |

| 41. | Power-Control Register (POWER_CTRL_REG)        | 93 |

| 42. | DSP-Idle Registers                             | 94 |

| 43. | DSP-Idle-Configuration Register (ICR)          | 94 |

| 44. | DSP-Idle-Status Register (ISR)                 | 95 |

Tables

This page intentionally left blank.

### Clock Generation and System Reset Management

This document describes clock generation and system reset for the OMAP5910 multimedia processor.

#### 1 Introduction

The clock generator and reset management module supplies clocks and resets to the entire OMAP5910 device.

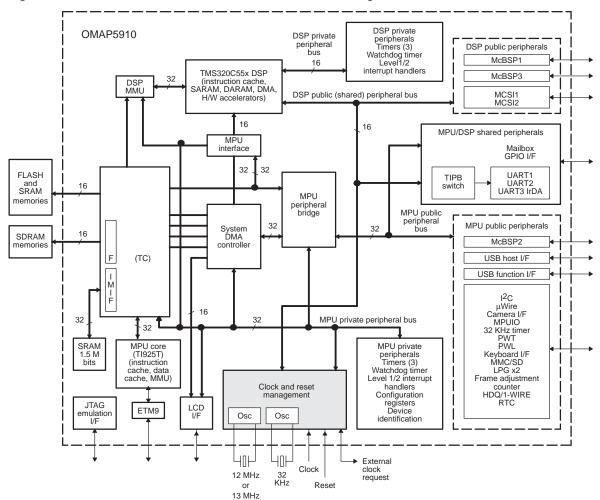

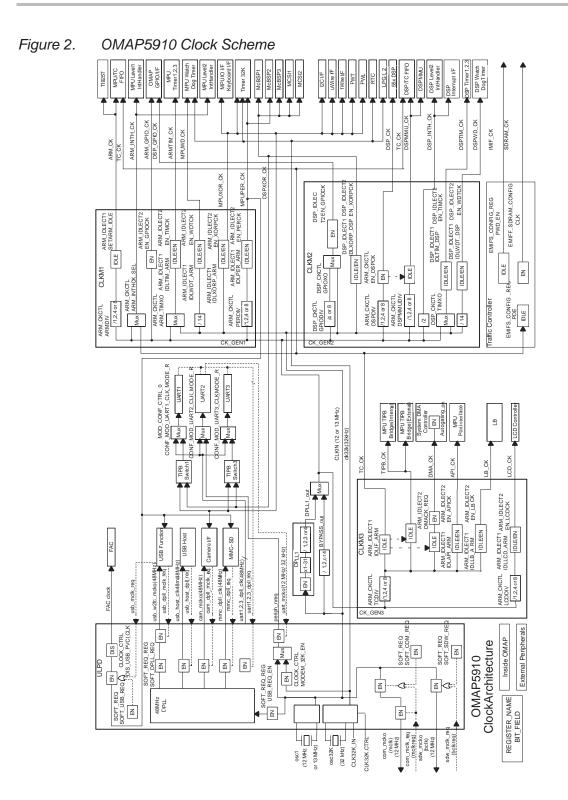

Figure 1 shows the OMAP5910 device with the clock generator and reset-management area highlighted. Figure 2 shows the OMAP5910 clock scheme.

#### 1.1 Clock Generation and System Reset Control

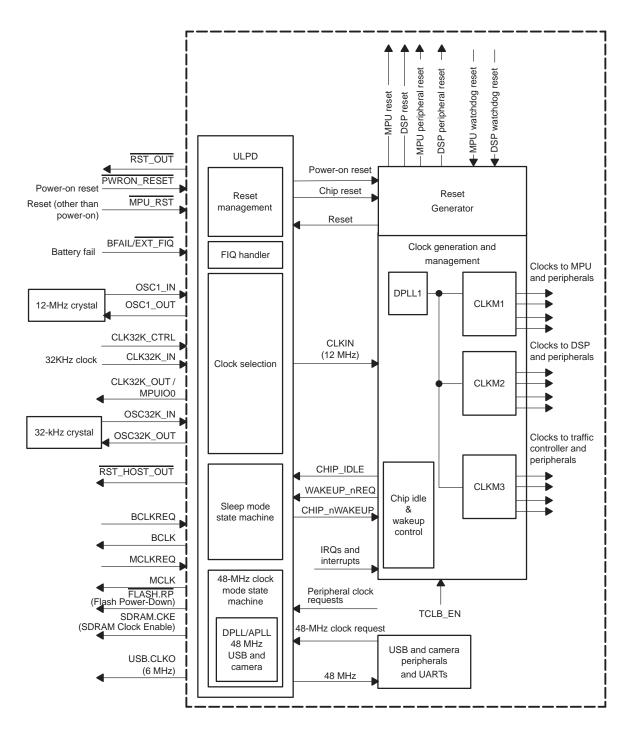

In the OMAP5910 device, clock generation and system reset are controlled by several modules, as shown in Figure 3.

There are three major components of this circuitry: the ultralow-power device (ULPD), the reset-management module, and the clock-generation and management module.

#### Figure 1. OMAP5910 Device Clock and Reset Management

#### Figure 3. Modules Controlling Clock and Reset Management

16

#### 1.1.1 ULPD Module

The ULPD module is an embedded peripheral controlled by the internal MPU with the following functions:

- Performs the state transition of the different power modes:

- Awake: The 32-kHz and 12-MHz clocks are on, and 12 MHz is fed into the clock-generation module (those PLLs can be turned on or off).

- Big-sleep mode: The 32-kHz and 12-MHz clocks are on, 12 MHz is not fed into the clock-generation module, and the PLLs are off.

- Deep-sleep mode: The 32-kHz clock is on, and the 12-MHz clock and the PLLs are off.

- Performs the power-on reset of the chip

- Calibrates an external quartz-based oscillator (32 kHz)

- Performs the wake up of the 12-MHz OSC1 oscillator to provide the OSC1 clock to an external device. An external-clock request or peripheral-wake-up request turns on the OSC1 oscillator but neither request is not treated as an interrupt.

- Performs a 12-MHz/32-kHz switch for the peripherals that need to switch to 32 kHz

- Generates the functional-reset signal used by the reset module

- Manages the 48-MHz DPLL and the APLL on/off

- Processes the battery-failed signal to generate the external-shutdown signal (RST\_HOST\_OUT)

#### 1.1.2 Reset Module

The reset module has the following functions:

- Provides the internal-global reset and the software reset

- Performs the reset control for the peripheral-bus peripherals

- Monitors the internal and the external reset (for example, the watchdog-timer time-out)

- Monitors the system and reset status

#### 1.1.3 Clock-Generation and Management Module

The clock-generation and management module provides the following features:

- Programmable-clocking scheme (synchronous and synchronous scalable modes) and power-up defaults to the fully-synchronous mode

- Setup and configuration can be controlled by both the DSP and the MPU processors

- A single reference-clock input to one DPLL from an external source (CLKIN). The PLL modes are configurable as follows: lock, bypass, and idle.

- Programmable clock, from the CLKM1 (see Section 1.1.5, Clock Domains), with the clock and idle-control capability to the MPU and its subsystem:

- GPIO

- Timers

- Other peripherals

- Programmable clock, from the CLKM2 (see Section 1.1.5, Clock Domains), with the clock and idle-control capability to the DSP and its subsystem:

- GPIO

- Timers

- Other peripherals

- Programmable clock, from the CLKM3 (see Section 1.1.5, Clock Domains), with the clock and idle-control capability to the memory-interface traffic controller (TC), including the following modules:

- MPU interface (MPUI)

- System DMA controller

- LCD controller

- Local bus

- MPU peripheral bridges

- Two internal MPU-TI-peripheral bridges to minimize access latency

- Programmable power-saving and idle-mode controls for the MPU, the DSP, the TC, and their respective subdomains

- Low-frequency clocks (reference clock/14) to supply the watchdog timers for the DSP and MPU

- DMA clock-request mechanism (provides the DMA clock during data transfer only)

- Power control for an external device reset/power on (flash)

- □ Idle-sequence controls (MPU-clock domain, DSP-clock domain, and TC-clock domain)

- Programmable idle modes (MPU and DSP) for different applications

- □ Wake up is initiated by interrupts (MPU, DSP, and TCLB\_EN pin) or DMA requests (TC and peripheral bus) in the idle mode

- Unmasked-interrupt events are enabled to wake up the device during idle modes

#### 1.1.4 Memory-Mapped Registers

The application program controls the clock generation, reset, and power-saving modes via a set of memory-mapped registers (nine 16-bit registers for the MPU subsystem and seven 16-bit registers for the DSP subsystem). These registers are accessible by the MPU or the DSP processors.

The MPU is the master of the OMAP5910 device at all times, and it controls the activities in the MPU, the DSP, and the TC domains.

The DSP controls the DSP's peripheral activities.

#### 1.1.5 Clock Domains

The OMAP5910 device is partitioned into three clock domains, each with its own clock manager:

- □ MPU domain (CLKM1)

- DSP domain (CLKM2)

- TC domain (CLKM3)

The three clock domains use a common DPLL to provide a synchronous clock. The different clocking configurations are discussed in detail later in this document.

The external clock-source (OSC1\_IN) frequency must be 12 MHz to ensure proper operation of the USB.

#### 2 Clock Generation

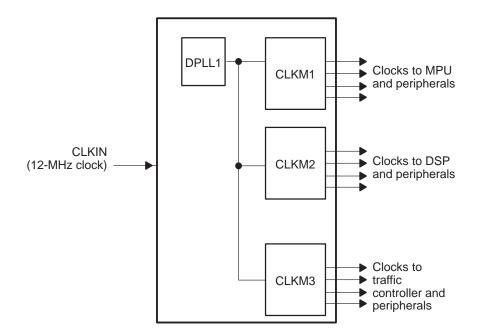

Figure 4 shows the basic building blocks of the clock-generator and system reset module. This module consists of:

- One DPLL—frequency synthesizer (frequency locked but not phase locked)

- Control register file (CLKREG)—clock generator, system reset, idle, and wake-up controls

- Three CLKMs—clock generation and wake-up controls

Figure 4. Clock Generation and System Reset Module

#### 2.1 Clocking Schemes

The clock generator supports two clocking schemes to provide performance flexibility and power-saving capabilities to the system. The clocking schemes are programmable. The power-up mode defaults to the fully-synchronous mode. Table 1 shows the clocking-scheme selection, and Table 2 shows the CLKM-source selection.

| Clock_Select | Clocking Scheme      | Remarks                                                                                 |

|--------------|----------------------|-----------------------------------------------------------------------------------------|

| 000          | Full synchronous     | Default, bypass the FIFO logic. TC=DSPMMU=MPU,<br>DSP = 1x or 2x of the DSPMMU          |

| 001          | Reserved             | Do not use this setting                                                                 |

| 010          | Synchronous scalable | Use the FIFO logic between the MPU and the TC, the DSP MMU and the TC $\ensuremath{TC}$ |

| Others       | Reserved             | Do not use these settings                                                               |

Table 1. Clocking Scheme Selection

Note: In all of the above cases, the frequency of the DSP can be 1x or 2x that of the DSP MMU.

#### Table 2. CLKM–Source Selection—Set via the MPU–System–Status Register

| Clock<br>Select | Operating Mode       | CLKM1<br>Input Clock<br>Source | CLKM2<br>Input Clock<br>Source | CLKM3<br>Input Clock<br>Source | Remarks       |

|-----------------|----------------------|--------------------------------|--------------------------------|--------------------------------|---------------|

| 000             | Fully synchronous    | DPLL1/N                        | DPLL1/O                        | DPLL1/N                        | Notes 1, 2, 4 |

| 010             | Synchronous scalable | DPLL1/M                        | DPLL1/N                        | DPLL1/O                        | Notes 3, 4    |

**Notes:** 1) If the fully–synchronous mode is selected, the divide-down bits must be programmed so that the MPUDIV, the DSPMMUDIV and the TCDIV are all equal. Further, the DSPMMUDIV must be 1x or 1/2x that of the DSPDIV.

2) CLKGEN1 = CLKGEN3 = DPLL1/N, CLKGEN2 = CLKGEN1 or 2\*CLKGEN1 = DPLL1/O

3) M, N =< O, and O is a multiple (1, 2, 4, 8) of M, N.

4) The DSP MMU cannot run above the maximum speed of the TC.

#### 2.2 Operating Modes

The OMAP5910 device supports the following operating modes:

Fully synchronous

The MPU, DSP MMU, and TC run at the same clock period, and the DSP MMU is 1x or 1/2x of the DSP. For example, the DPLL1 output can be 120 MHz; the MPU, DSP MMU, and TC can be 60 MHz; and the DSP can be 120 MHz.

On power up, the OMAP5910 device is always in the fully–synchronous mode, where the MPU, DSP MMU, TC, and DSP are all at the same speed.

Synchronous scalable

The MPU, DSP MMU, and TC are synchronous, but the MPU and DSP MMU are multiples (1x, 2x, 4x, or 8x) of the TC. The DSP must be 1x or 2x of the DSP MMU. For example, the DPLL1 clock can be 120 MHz, the MPU can run at 120 MHz, the DSP MMU can run at 60 MHz, the TC can run at 30 MHz, and the DSP can run at 60 MHz or 120 MHz. In this mode, the clock-feeding mechanism (to each respective domain) is similar to that of the fully-synchronous mode, with the exception that the clocks are synchronous but are multiples of each other. The input clock is from the DPLL1, and the clock is multiplied/divided by the CLKM (1, 2, 3) as in the following example (assuming that the output of the DPLL1 is 120 MHz):

- CLKM1 output: 120 MHz/2

- CLKM2 output: 120 MHz/1

- CLKM3 output: 120 MHz/4

Divider circuitry is implemented in each CLKM.

#### Note:

In synchronous-scalable mode, the traffic controller clock must have the same or a slower frequency as the MPU and the DSPMMU clocks.

At reset, the fully-synchronous mode is selected (default). After the OMAP5910 device is up and running, the application software can write to the control registers via the CLOCK\_SELECT[2:0] bits in the MPU-system-status register (ARM\_SYSST) to switch to a desired mode of operation. However, system software should be used to save the context before switching modes. For information about the switching procedure, see Section 5, *Switching Clock Modes*.

The DSP\_MMU clock must obey all of the following rules:

- 1) The TC-clock frequency always must be equal to or less than the DSP, DSPMMU, and MPU clocks.

- 2) The DSP\_MMU clock must be 1x or 1/2x of the DSP clocks.

- 3) The DSPMMU\_DIV can be /1, /2, /4, /8, but the TC\_DIV and DSP\_DIV must obey rules 1) and 2) immediately above.

- The DSP\_MMU-clock frequency cannot be more than the maximum speed of the TC.

#### 2.3 External-Master Mode

This mode allows a bypass of the 12-Mhz on-chip oscillator in systems where the 12-MHz clock is provided externally by a master device. The procedure for utilizing this mode is as follows:

- 1) During the power-on reset, the OMAP5910 device is in the deep-sleep mode:

- The 12-MHz on-chip oscillator is disabled.

- The MCLKREQ pin is an input.

- 2) After the power-on reset, the OMAP5910 device is awake.

- The 12-MHz oscillator is bypassed.

- The MCLKREQ pin is an input.

- The 12-Mhz clock is provided externally.

- Switch to external-master mode by setting FUNC\_MUX\_CTRL\_B[20:18] = 001.

- The 12-MHz oscillator is bypassed (disabled).

- The MCLKREQ pin is now the EXT\_MASTER\_REQ pin, which drives to 1.

- The 12-Mhz clock is provided externally.

- 4) If the OMAP5910 device switches into the deep-sleep mode:

- The EXT\_MASTER\_REQ drives to 0 to indicate that the external 12-MHz clock is not needed.

- The 12-MHz clock can then be switched off externally.

#### 2.4 CLKM1

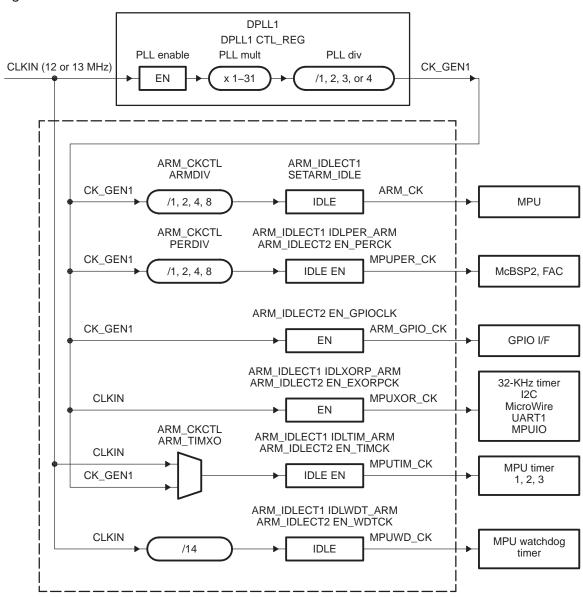

The CLKM1 controls the clock distribution and idle modes of the MPU subsystem, plus the associated private and public peripherals (see Figure 5).

Figure 5. MPU Clock Distribution

24

The MPU clock (see Figure 5) has the following domains (CLKM1):

- The MPU-processor clock: ARM\_CK, which is CLK\_GEN1 divided by 1, 2, 4, or 8, as programmed via the ARMDIV bits of the MPU-clock-control register (ARM\_CKCTL). The idle mode of the MPU is controlled by the SETARM\_IDLE bit of the MPU-idle-mode-entry-1 register (ARM\_ IDLECT1).

- The MPU-peripheral clocks are:

- The MPUXOR\_CK, which is derived from CLKIN

- The MPUPER\_CK, which is CLK\_GEN1 divided by 1, 2, 4 or 8, as programmed via the PERDIV bits of the MPU-clock-control register (ARM\_CKCTL)

The MPUPER\_CLK clock is enabled by the EN\_PERCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2) and the MPUX-OR\_CK clock by the EN\_XORPCK bit.

- The MPU-watchdog-timer clock (low frequency, derived from CLKIN/14): called either CK\_CLKIN14 or MPUWD\_CK. This clock is enabled by the EN\_WDTCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2). The idle mode is controlled by the IDLWDT\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1). The clock cannot be disabled or idled while in the watchdog mode.

- The MPU-internal-timers clock: MPUTIM\_CK, which is derived from either the CK\_GEN1 or the CLKIN, as selected by the ARM\_TIMXO bit of the MPU-clock-control register (ARM\_CKCTL). The idle mode of the MPU timers is controlled by the IDLTIM\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) and is enabled by the EN\_TIMCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2).

- □ The MPU GPIO clock, MPU\_GPIO\_CLK, which is equal to the CK\_GEN1. This clock is enabled by the EN\_GPIOCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2).

#### 2.5 CLKM2

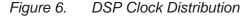

The CLKM2 controls the clock distribution and idle modes of the DSP subsystem plus the associated private and shared peripherals. As shown in Figure 6, the CLKM2 circuitry provides separate clock signals for the DSP internal peripherals (GPIO, watchdog timer, and timers) and the public peripherals.

#### Note:

The CK\_GEN2 represents the output of the DPLL1 or the CLKIN, depending on the clocking mode enabled.

The clock signals for each clock domain of the DSP subsystem are as follows:

- □ MPU-controlled:

- The DSP-processor clock: DSP\_CK, which is CK\_GEN2 divided by 1, 2, 4, or 8, as programmed via the DSPDIV bits of the MPU clock control register (ARM\_CKCTL). The enabling of the DSP\_CK while the DSP is in the reset state is controlled by the EN\_DSPCK bit of the MPU-clock-control register (ARM\_CKCTL).

- The DSP-MMU clock: DSPMMU\_CK, as derived from the CK\_GEN2 divided by 1, 2, 4, 8, as programmed by the DSPMMUDIV bits of the MPU-clock-control register (ARM\_CKCTL). Take care in selecting clocking schemes so as not to exceed the maximum frequency of the DSP MMU. See the OMAP5910 device datasheet for absolute timing limits.

- DSP-controlled:

- The DSP GPIO (DSP\_GPIO\_CK), as derived from the CK\_GEN2 divided by 1, 2, 4, 8 (as programmed by the DSP\_CKCTL GPIODIV) or CLKIN, as selected by the GPIOXO bit of the DSP-clock-control register (DSP\_CKCTL). The clock is enabled by the EN\_GPIOCLK bit of the DSP-idle-mode-entry-2 register (DSP\_IDLECT2).

- The DSP-public peripherals (McBSPs, MCSIs): DSPXOR\_CK, which is derived from the CLKIN. The clock is enabled by the EN\_XORPCK bit of the DSP-idle-mode-entry-2 register (DSP\_IDLECT2). The idle mode is controlled by the IDLXORP\_DSP bit of the DSP-idle-mode-entry-1 register (DSP\_IDLECT1).

- The DSP-internal timer: DSPTIM\_CK, is selected from either the CK\_GEN2/2 or the CLKIN via the DSP\_TIMXO bit of the DSP-clock-control register (DSP\_CKCTL). The clock is enabled by the EN\_TIMCLK bit of the DSP-idle-mode-entry-2 register (DSP\_IDLECT2). The idle mode is controlled by the IDLTIM\_DSP bit of the DSP-idle-mode-entry-1 register (DSP\_IDLECT1).

- The DSP-watchdog timer (low frequency, derived from CLKIN divided by 14): DSPWD\_CK. The clock is enabled by the EN\_WDCLK bit of the DSP-idle-mode-entry-2 register (DSP\_IDLECT2). The idle mode is controlled by the IDLWDT\_DSP bit of the DSP-idle-mode-entry-1 register (DSP\_IDLECT1). The watchdog-timer clock can only be disabled or idled when not in the watchdog mode.

After reset, the highest-frequency option (CK\_GEN2 divided by 1) is selected for the GPIO and the DSPPER clocks. The software-application program can alter these divisors at any time during operation by writing to the GPIODIV or the DSP\_PERDIV bits in the DSP-clock-control register (DSP\_CKCTL).

The clock-generator output (CK\_GEN2) delivers a 50%-duty cycle to the DSP subsystem clock-distribution module (CLKM2). This module provides additional clock scaling, routing, and idle/reset control to the DSP to individual components in the DSP clock domain.

The CK\_GEN2 clock works in conjunction with the idle and the wake-up control logic to produce the DSP\_CK-clock signal that drives the DSP subsystem, the DSP MMU, and the DSP interrupt modules.

At reset, the CK\_GEN2 is in the bypass mode, so it supplies (CLKM2) a clock of the same 12- or 13-MHz frequency as the CLKIN. After the global-reset period, the MPU application program can change the clock frequency through the CK\_GEN2 control register.

The DSP\_CK is enabled at reset until the DSP is in the reset state. The EN\_DSPCK bit (located in the clock-control register ARM\_CKCTL) allows the MPU to turn off the DSP\_CK while the DSP is held in a reset state.

A free-running counter/divider receives the CK\_GEN2 signal and makes available four taps where a 50%-duty-cycle clock and the clock divided by 1, 2, 4, and 8 can be selected. A multiplexer set, through the DSPDIV bits in the clock-control register (ARM\_CKCTL), selects the clock frequency that applies to the DSP clock domain.

At reset, the higher frequency (divide by 1) is selected. The software-application program (accessing the control-register file) can change the divider ratio by writing to the DSPDIV [1-0] bits at any time while the OMAP5910 device is running. A synchronization mechanism is implemented to remove any spikes while the clock frequency is changing (disable the clock first, change the DSPDIV bits, and then enable the clock).

#### 2.6 CLKM3

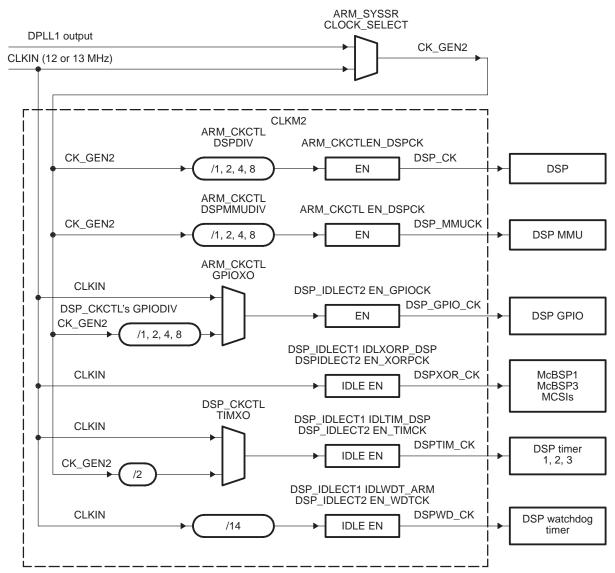

The CLKM3 controls the clock-distribution and idle modes of the traffic controller and various system-level-clock domains. The traffic-controller clock, CLKM3 (see Figure 7), has the following domains.

Figure 7. Traffic Controller Clock Distribution

Many of the following clocks are the same as the traffic-controller clock (TC\_CK) in terms of their frequencies, but not their IDLE controls. Each of the clocks has separate IDLE control logic.

The traffic-controller clock, TC\_CK, is derived from CK\_GEN3 divided by 1, 2, 4, or 8, as programmed via the TCDIV bits of the MPU-clock-control register (ARM\_CKCTL). The MPU interrupt handler uses the TC\_CK clock, as set by the ARM\_INTHCK\_SEL bit of the MPU-clock-control register (ARM\_CKCTL). The idle mode is controlled by the IDLIF\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1).

- The local-bus and local-bus-MMU clock, LB\_CK, is the same as the TC\_CK. The idle mode is controlled by the IDLLB\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1). The LB\_CK is enabled by the EN\_LBCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2).

- The MPU-port-interface (MPUI) clock is dependent not only on the IDLAPI\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1), but also on DSP\_IDLE.

- □ The system-DMA-controller clock, DMA\_CK, is the same as the TC\_CK. The idle mode is controlled by the IDLIF\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1), and the clock is enabled by the DMACK\_REQ bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2).

- ☐ The MPU-peripheral-bridge clock, TIPB\_CK, is the same as TC\_CK. The idle mode is controlled by the IDLIF\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1).

- The LCD-controller clock, LCD\_CK, is derived from CK\_GEN3 divided by 1, 2, 4, or 8, as programmed via the LCDDIV bit of the MPU-clock-control register (ARM\_CKCTL). This clock is enabled by the EN\_LCDCK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2). The idle mode is controlled by the IDLLCD\_ARM bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1).

#### 2.7 Clock Distribution and Synchronization

When any of the clock domains are running at different frequencies with respect to each other, the FIFOs are used to buffer data being transferred between domains (see Figure 8). This is necessary to ensure that data being sent from a faster domain is buffered as a slower domain receives it. This buffering introduces latencies as data is passed between the domains. Thus, this buffering can be bypassed if it is not needed (that is, when the domains are running at the same speeds).

- For the fully-synchronous-clocking scheme, ARM\_CK = DSPMMU\_CK = TC\_CK; the FIFO logic is bypassed between the TC and MPU, and the TC and DSPMMU.

- For the synchronous-scalable-clocking scheme, the FIFO logic is used for both processors.

#### Note:

The TC\_CK clock must be slower than or equal to the ARM\_CK and DSP MMU clock speed.

#### 2.8 Low-Power Mode

The OMAP5910 LOW\_PWR I/O is an active-high request for the LOW\_PWR mode (see Figure 9). It automatically requests external regulators to go to standby (low-power mode) or to lower the VDD core voltage during the deep-sleep mode. A software request, through bit 1 of the power-control register (POWER\_CTRL\_REG), is available for debugging and future support of the low-voltage operational mode.

The LOW\_PWR signal is multiplexed on the MPUIO5 ball. To get the signal on this ball, bits [14:12] of the FUNC\_MUX\_CTRL\_7 register must be set to 001.

Figure 9. Low-Voltage Mode

#### 3 Power Management

There are three clock domains in the OMAP5910 device. Each clock domain has its own clock-management unit and can be put into idle mode (power-saving mode) when unused without affecting the rest of OMAP5910 functionality. In addition, the ULPD provides the low-power modes that affect the entire device, not just the individual domains (see Figure 10).

A chip idle occurs when the DSP is idled, the MPU requests an idle, and the TC domain has no remaining transactions. A chip idle causes the ULPD to initiate the big-sleep mode. In the big-sleep mode, the DPLL 1 is turned off, but the 12-MHz clock is still active. If the 12-MHz clock is not needed, then the ULPD can initiate a further transition to the deep-sleep mode, which turns the 12-MHz clock off internally.

When an unmasked-interrupt event occurs, a request is performed by the wake-up-control module. When receiving the request, if the device is in deep-sleep mode, the ULPD brings the device out of the deep-sleep mode. Once the 12-MHz clock is stable, the ULPD brings the device into the awake mode.

To reduce the wake-up time, a special hardware request is implemented in parallel to interrupts to wake-up the ULPD whenever an interrupt occurs. This request is generated by peripherals such as the USB or UART. When receiving the hardware request, the ULPD brings the device out of the deep-sleep mode to wake-up the 12-MHz clock. When the clock is awake, the ULPD goes into the big-sleep mode and awakes if a request is received from the wake-up-control module. Figure 11 shows the wake-up-control module.

The deep-sleep mode is the entry state of the device when a power-on reset occurs. Such a reset acts as a wake-up request, causing the device to transition to the awake state.

The 12-MHz clock may be required to clock signals out of the device (such as the MCLK pin) or to the ULPD DPLL (used for the USB and other internal peripherals) in either the big-sleep or awake states. The deep-sleep state can not be entered if there is need for the 12-MHz clock.

The power-management state machine runs at 32 kHz. All control signals of this state machine are resynchronized on the 32-kHz clock. The 32-kHz clock is always on.

Table 3 lists the peripherals and external signals which can wake up the OMAP5910 device from the deep-sleep mode.

#### Figure 10. Power Management State Machine

Figure 11. Wake-up Control Module

| Requestor                                                         | Mechanism                                         | Transition from Deep Sleep to ?            |

|-------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|

| Power on reset (external signal)                                  | Cold reset                                        | AWAKE                                      |

| MPU_RESET (external signal)                                       | Warm reset                                        | AWAKE                                      |

| MPUIO keyboard                                                    | MPU interrupt                                     | AWAKE                                      |

| MPUIO GPIO                                                        | MPU interrupt                                     | AWAKE                                      |

| Timer32K                                                          | MPU interrupt                                     | AWAKE                                      |

| UART2 RX detection                                                | Peripheral request generated to ULPD              | AWAKE                                      |

| RTC                                                               | MPU interrupt                                     | AWAKE                                      |

| USB cable insertion                                               | USB request to ULPD which generates MPU interrupt | BIG SLEEP then AWAKE via the MPU interrupt |

| UART1/2/3 (wait for a falling edge on the RX, DSR or CTS signals) | MPU/DSP interrupt                                 | AWAKE                                      |

| MCLK_REQ (external signal)                                        | Request to ULPD                                   | BIG SLEEP                                  |

| BCLK_REQ (external signal)                                        | Request to ULPD                                   | BIG SLEEP                                  |

| External DMA request (external signal)                            | Asynchronous request from TC                      | AWAKE                                      |

Table 3. OMAP5910 Wake-Up Peripherals and External Signals

#### 3.1 DSP-Idle Modes

Two DSP registers are used to configure and check the idle modes for the DSP subdomains.

- ☐ The idle-configuration register (ICR) specifies which clock domains get put into idle by the next execution of the IDLE instruction.

- The idle-status register (ISR) indicates which subdomains are currently in IDLE mode.

The six different subdomains are:

- The DSP-core subdomain (DSP CORE/SARAM/DARAM): ICR and ISR bit 0

- The DSP-DMA-controller subdomain (DMA/SARAM/DARAM): ICR and ISR bit 1

- The I-cache subdomain (I-cache): ICR and ISR bit 2

The Peripherals subdomain (peripherals outside the DSP): ICR and ISR bit 3:

Peripherals can be individually controlled (shut off/enabled) by programming the control registers in the clock-generation-management module (CLKM). To maximize power conservation, seven different peripheral-idle modes are defined (UART, GPIO, timers, watchdog timer). Each one can be individually activated and deactivated by software.

Two different strategies are used to control the clock that feeds the DSP peripherals:

- The clock is shut off/activated according to the DSP-idle mode or the application-specific environment (disable the peripheral clocks when the DSP in not in idle). Peripherals connected to this clock cannot request DMA transfers during the DSP-idle mode.

- The clock is never shut off (input reference clock).

In either case, the DSP peripheral clocks are directly shut off/activated by the DSP software.

The DPLL subdomain (DSP input clock + DSP interrupt handler): ICR and ISR bit 4

Setting up the DSP-DPLL-idle mode sends a DSP\_IDLE signal to the clock-generation-management module (CLKM), which disables the input clock to the DSP.

The DSP-EMIF subdomain: ICR and ISR bit 5

#### 3.1.1 Putting the DSP in IDLE

Perform this procedure to put the DSP in idle mode:

- 1) Turn off the DSP-peripheral clocks.

- 2) Disable the DSP-watchdog timer.

- 3) Enable the desired DSP interrupts (interrupt mask).

- 4) Enable the DSP-global interrupt (INTM bit), if required.

- 5) Switch the DSP to shared-access mode (SAM) (it is in the SAM mode, but switch the mode to signal the CPU). In the SAM mode, the public peripheral bus is shared between the MPU and DSP.

- 6) Write to the ICR registers to disable all clock domains or a particular clock domain (write a 1 to disable).

36

- Switch the DSP back to host-only mode (HOM). In the HOM mode, the public-peripheral bus is owned exclusively by the MPU (usually because the DSP is in idle mode or about to go to idle mode).

- 8) Execute the IDLE instruction.

The DSP goes to sleep. If INTM is set, the ISR is not executed after wake up; the interrupt simply wakes the DSP up. The program continues just after the IDLE instruction; otherwise, the ISR is executed.

When the DSP is awakened (by an enabled interrupt or an external event such as reset), perform the following procedure:

- 1) Disable the global interrupt (INTM), if required.

- Switch the DSP to the SAM mode. The public-peripheral bus is now shared by the DSP and MPU.

- 3) Write a 0 to the respective ICR bit to clear the idle bit.

- 4) Execute the IDLE instruction.

#### Note:

To set the DPLL subdomain to idle, switch off the other clock domains (CPU, DMA cache); otherwise, the DSP peripheral cancels the idle request with a bus error indicating that the configuration is not allowed.

#### 3.2 MPU-Idle Modes

A clock-management register, the MPU-idle-mode-entry-1 register (ARM\_IDLECT1), controls the different clock domains (clock enables) during the idle state and allows the user to put different parts of the MPU clock domain into the idle mode, if desired.

Three different subdomains are defined: the MPU subdomain, the DPLL subdomain, and the MPU peripheral subdomain.

#### 3.2.1 MPU Subdomain (MPU + MPU Interrupt Handler)

The MPU can go into the idle mode in two ways:

- By executing the CP15, wait-for-interrupt, instruction: Executed by an OS kernel. By configuration, this instruction provokes an Idle1 or an Idle2 mode.

- By setting the SETARM\_IDLE bit (ARM\_IDLECT1[11], (the idle-control register in the clock-generator and system-reset module): Programmed

by a process application. Setting these bits (active) allows the MPU to enter in an Idle1 or an Idle2 mode. This is the recommended method to use.

The MPU clock restarts upon an enabled-interrupt request or system reset.

#### Wait-For-Interrupt Instruction

When the MPU CP15 instruction is used, the system software does not need to take care of adding any extra cycles to wait after the instruction being executed (the MPU itself takes care of this). When this instruction is executed, the MPU stops its ongoing operations and sends a sleep acknowledge signal to the OMAP5910 clock reset module to request stopping the clock. The MPU does not execute any other access after executing the wait-for-interrupt instruction. The MPU wakes up when an interrupt occurs and executes the subsequent instructions after servicing the interrupt.

#### Set SETARM\_IDLE (ARM\_IDLECT1[11])

After SETARM\_IDLE is set through software, the software must wait for a certain number of cycles to ensure no other MPU requests occur before the MPU is idled. This is because there is a latency between the MPU-TIPB write to the IDLECT1 register and the time when the MPU-sleep request to the MPU core actually goes high. Also, the software must account for the clock cycles required for the MPU to send an acknowledge signal back to the OMAP clock reset module, depending on what operations it was performing.

The following rules ensure that sufficient time is allowed:

- The clock-reset module needs at least four reference-clock cycles (12-MHz clock) and two MPU-clock cycles to send a sleep request to the MPU.

- The MPU needs at least three MPU-clock cycles to send back an acknowledge after receiving the sleep request. This is true even if there are no access requests coming from the MPU before or after the sleep request. The sleep request is generated from the register write to the IDLECT1 Bit 11.

- Add NOP instructions to make sure there is no request coming from the MPU by considering the worst-case scenario. This scenario is: MMU and I-cache are enabled, a MMU-TLB miss (requiring a L1 and L2 fetch), and an I-cache miss, as follows:

- Four read strobes for the instruction fetch (a line load of 4 words)

- One read strobe for the TLB-Miss-L1-descriptor fetch

- One read strobe for the TLB-Miss-L2-descriptor fetch

This requires six read strobes, which need N number of MPU clock cycles. N depends on the type of memory from which the reads are being made.

There is a software solution to avoid these extra N MPU-clock cycles due to the read strobes. This solution requires that only I-Cache be enabled. By changing the loop-count value (CMP R2), the number of cycles can be increased/decreased, as shown in Figure 12.

Figure 12. Code Example

```

; thumb mode

.state16

.ref edata

; defined by armas

.global $arm_idle

$arm_idle:

push

\{lr\}

push \{r1-r7\}

r4, into_32_bis

adr

bx

r

nop

nop

nop

.state32

; arm mode

into 32 bis:

LDR

R1,ARM IDLECT1

MOV

R3,#1

MOV

R3,R3,LSL # 11

MOV

R2,#0

LDR

R0,[R1]

R0,R0,R3

ORR

; This is the loop that will wait for at least 100 cycles

; before issuing next request from ARM. On the first run of the loop only Icache

; gets loaded with the loop and the next 2 instructions but write to SYSST does

not occur

; In the 2nd run of the loop only write to IDLE_CT1 happens and after that ARM

runs the loop from

;Icache so no request goes out

LOOP CMP

R2,#1

STREQ R0, [R1]

R2,R2,#1

ADD

CMP

R2,#16

BNE

LOOP

```

Figure 12. Code Example (Continued)

```

the_end:

adrr2, into_16_bis + 1

bx r2

.state16

into_16_bis:

nop

\{r1-r7\}

рор

{pc}

рор

CONSTANT TABLE

;

ARM IDLECT1

.long 0xFFFECE04

```

Example:

- If the reference-clock speed = 12 MHz, then the MPU-clock speed = 96 MHz

- If the above routine is used after the write to the ARM\_IDLECT1 register, 4 \* 96/12 + 2 + 3 = 37 clock cycles are needed

To achieve this, run the loop seven times.

## 3.2.2 DPLL Subdomain

The DPLL1 is disabled when all of the clock domains using the DPLL1 are disabled.

Setting up the IDLDPLL\_ARM bit enables the DPLL1 to enter the idle mode when the following conditions are met; otherwise, the DPLL1 remains active.

SPRU678A

- The DSP is set in the global-idle mode.

- ☐ The MPU is set in the idle mode (either from a request or from a wait-for-interrupt instruction).

- There is no active DMA transaction and there is no activity on the internal local bus, as indicated by the internal TCLB\_EN signal

- No peripheral post write is queued.

- The peripheral clocks are stopped.

- There are no pending interrupts.

### 3.2.3 Peripheral Subdomain

Two clocks feed the MPU peripherals:

- The clock that is shut off/activated according to the MPU-idle mode. Peripherals connected to this clock cannot request DMA transfers during the MPU-idle mode.

- The clock that is never shut off (input reference clock)

In either case, the MPU peripheral clocks are directly shut off/activated by the MPU software.

## 3.3 Traffic-Controller-Idle Modes

A clock-management register, ARM\_IDLECT1, controls the different clock subdomains (clock enables) during the idle state and allows the user to put different parts of the traffic controller into idle mode, if desired.

Several different subdomains are defined.

System-DMA subdomain

To optimize power consumption, the system-DMA-controller clock (DMA\_CK) can be shut off/activated according to the DMA activity (provides the clock during data transfer only) or it can be shut off only when the MPU goes to idle.

Traffic-controller subdomain

The traffic-controller clock (TC\_CK) is shut off if the MPU and the DSP DPLLs are in idle mode and there is no DMA transfer. When the clock must be shut off, the memory interface completes the current memory transaction before notifying the CLKM3 to shut off a clock. The SDRAM is placed in self-refresh mode before shutting off the SDCLK\_EN clock, and there is no internal local-bus activity, as indicated by the internal TCLB\_EN signal.

MPU-peripheral-bridge domain

The MPU-peripheral-bridge clock (TIPB\_CK) is shut off if the MPU is in the idle mode and there is no DMA transfer.

LCD domain

The LCD clock (LCD\_CK) is shut off/activated according to the traffic-controller-idle mode or forced off with the enable bit.

MPU-MPUI domain

The MPUI clock (API\_CK) is shut off if the MPU and the DSP DPLLs are in the idle mode and there is no DMA transfer (when the clock is required to be shut off, the memory interface completes the current memory transaction before notifying the CLKM3 to shut off the clock). The MPUI clock can also be forced off with the enable bit (the MPUI clock can only be shut off by the enable bit in current implementation).

#### Note:

To idle the traffic controller, the system software must ensure that the current transfers are completed and their clock domains are turned off before going to idle.

The traffic-controller clock restarts upon either an MPU or DSP interrupt request, a DMA request, or activity on the internal buses.

## 3.3.1 DPLL-Idle Procedure

In the event that only the input-reference clock is needed (that is, only timer/watchdog are active), then the DPLL can be set to idle mode. This procedure applies to DPLL. The DPLL clock is stopped if all the domains that use it as a source are stopped.

Setting the IDLDPLL\_ARM bits (in ARM\_IDLECT1 register) to logic 1 forces the corresponding DPLL to enter the idle mode whenever the DPLL output clocks (*CK\_GEN1, CK\_GEN2, CK\_GEN3*) are not being used.

The DPLL-idle control logic receives signals from clock-generation modules, indicating when the output clock can be stopped. The DPLL-idle mode is entered when the IDLDPLL\_ARM bits in the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) are set to logic 1.

## 3.4 Chip Idle and Wake-Up Control

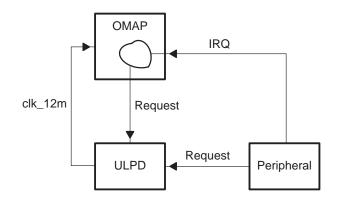

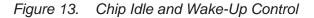

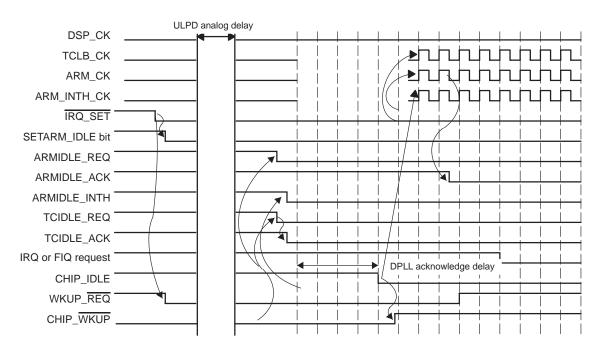

In the status-request register (STATUS\_REQ\_REG), both the CHIP\_IDLE and WAKEUP\_nREQ signals can be used by the ULPD idle logic to control the input-clock source. The CHIP\_IDLE signal remains high until the DPLLs acknowledge that they have entered the IDLE mode. The WAKEUP\_nREQ signal goes active as soon as one of the chip-wake-up conditions occurs (MPU or DSP interrupt, DMA request, or local-bus activity). The CHIP\_IDLE signal can be used by the ULPD to decide when to stop the CLKIN (CLKIN) to the clock-generation module, and it uses the WAKEUP\_nREQ signal to restart the clock (see Figure 13).

In the status-request register (STATUS\_REQ\_REG), the following signals are used in chip idle and wake-up control:

- □ CHIP\_nWAKEUP: CHIP\_nWAKEUP is the acknowledge of the ULPD when the CHIP\_IDLE signal is active. It indicates to the clock-management module that the ULPD has left the awake mode and the 12-MHz clock, CLKIN, is off.

- □ When CHIP\_IDLE becomes inactive, the ULPD releases the CHIP\_nWAKEUP signal to indicate that the ULPD is in the awake mode and the CLKIN is back on. This signal provides the ULPD with more control of the OMAP5910 device wake-up.

- When the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) WKUP\_ MODE field = 0, the OMAP5910 device does not wake up, even if one of the above wake-up conditions occurs, until the CHIP\_nWAKEUP goes active.

- MPU interrupt

- DSP interrupt

- Internal local-bus activity (TCLB\_EN signal = 1)

In the chip-idle mode, if this signal is inactive (high), the OMAP5910 device does not wake up (prevent from waking up), even if one of the above wakeup conditions has occurred. This signal has no effect when the OMAP5910 device is not in the chip-idle mode. When the MPU-idle-modeentry-1 register (ARM\_IDLECT1) WKUP\_MODE = 0, the OMAP5910 device does not wake up, even if one of the above wake-up conditions has occurred.

- WAKEUP\_nREQ: request to the ULPD to wake up the chip. This signal is looked at only when the CHIP\_IDLE signal is high. Note that WAKEUP\_nREQ is asserted by the OMAP5910 device whenever any wake-up condition occurs, even when the OMAP5910 device is not in CHIP\_IDLE.

- FLASH.RP and SDRAM.CKE: Power control for external devices (for example, flash and SDRAM)

- Power-on reset: Must be valid until the power and input clocks are stable

- CHIP\_IDLE: Chip-idle mode. Indicates that all internal clocks are stopped. This internal signal is active regardless of the state of the external wake-up-control feature. This pin is asserted (high) when all DPLL ACKs are returned and all the peripherals using CLKIN are disabled.

- TCLB\_EN: TC local bus enable, enables the restart of the clock to the TC when the idle mode is set.

- DSP interrupts (internal signal is DSP\_nIRQ): Interrupt request from the DSP-interrupt handler. Asserts when an unmasked interrupt has been asserted.

- MPU IRQ (internal signal is nIRQ\_SET): Interrupt request from the MPU-interrupt handler. Asserts when an unmasked interrupt has been asserted. When the MPU is awake, must remain low until the MPU clock restarts.

- DSP\_IDLE—DSP-idle command

- MPU\_IDLE—MPU-idle command

## 3.4.1 Chip-Idle Mode

In the event that no clock signal is necessary (chip idle), all clock domains generated either from the CK\_GEN (1,2,3) or CLKIN are stopped. The external reference-clock source can be stopped as well.

The CHIP\_IDLE signal is asserted when all internal system clocks are disabled and after the DPLL idle state has been acknowledged. It is deasserted when a wake-up condition is detected (CHIP\_nWAKEUP and one of the wake-up conditions is active when the external wake-up control is enabled or just one of the wake-up conditions is active when the wake-up control is not enabled). It takes some synchronization CLKINs for the CHIP\_IDLE to go low after a wake-up condition is detected.

#### Note:

In addition to the DPLL timing, the clock source start-up time can affect the OMAP5910 system response. Use the deep-sleep mode for long sleep-periods only.

## 3.4.2 Chip-Idle Procedure

- 1) Set TC\_EMIF\_SLOW\_IF\_CONFIG\_REG = 0x0000000C and TC\_EMIF\_FAST\_SDRAM\_CONFIG\_REG = 0x0C618800

- Disable the MPU watchdog timer by first writing 0x00f5 to the WDTIMER\_TIMER\_MODE\_REG and then writing 0x00A0 (this is to prevent a watchdog reset from being generated that results in a global reset.)

- 3) Set up the MPU interface (write to the MPUI-control-setup and DSP-boot registers).

- 4) Set API\_SIZE\_REG = 0x0000 (only need to set the bits that correspond to the SARAMs with DSP code to 0).

- 5) Enable the MPU interrupts and unmask these interrupts by writing a 0 to the corresponding bit in the MIR-mask-interrupt register in the MPU-interrupt handler. Write to the corresponding interrupt-level register (ILR) to set the priority, edge sensitivity, and whether the interrupt is routed to the IRQ or FIQ. Besides the interrupt that is used to wake up the MPU out of idle, a DSP-mailbox interrupt to the MPU can also be enabled. This DSP2MPU-mailbox interrupt service routine is used to put the MPU into idle. The reason to use this mailbox interrupt is that the MPUI clock is needed by the DSP to switch between the SAM/HOM modes. The MPU

cannot go to idle until this is done, because only the MPU can write to the EN\_APICK bit of the MPU-idle-mode-entry-2 register (ARM\_IDLECT2).

- 6) Take the DSP out of reset. First, write the MPU-reset-control-1 register (ARM\_RSTCT1) DSP\_RST field = 1. Set the MPU-reset-control-1 register (ARM\_RSTCT1) DSP\_EN to = 1. The DSP\_RST bit controls the MCU reset, and the DSP\_EN bit controls the reset signal of the DSP.

- 7) In the DSP code, enable and unmask the DSP interrupts.

- Disable the DSP-watchdog timer (that is, take it out of the watchdog mode) and disable the DSP-peripheral clocks setting the DSP-idle-mode-entry-2 register (DSP\_IDLECT2) to 0x0000.

- 9) Write to the DSP-mailbox registers to generate the interrupt to the MPU. In the corresponding MPU-interrupt service routine, add a wait loop to make sure the DSP has gone to idle before disabling the MPUI clock.

- 10) In the MPU-interrupt service routine, clear the DSP2MPU-mailbox interrupt, then disable the ARMGPIO\_CK, LB\_CK, and LCD\_CK by writing the MPU-idle-mode-entry-2 register (ARM\_IDLECT2) = 0x0087 (can also write 0x0000, which disables the MPU peripheral clocks instead of letting them go to IDLE, only after the MPU goes to IDLE using the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) IDL\_ARM). Put the MPU into idle mode by writing the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) = 0x0FFF, which sets the SETARM\_IDLE bit. This also sets the IDLIF bits, which allow the MPU peripherals to go to idle when the MPU goes to idle, and sets the IDLDPLL\_ARM bit, which allows the DPLLs to go to idle.

- 11) Back in the DSP code, after writing to the DSP-mailbox register in step 10, switch the DSP TIPB and MPUI to the SAM mode. Then, write 0xFF to the DSP ICR register. Switch the DSP back to the HOM mode and execute the IDLE instruction. See the section on putting the DSP in idle mode for descriptions of the SAM and HOM modes.

The DSP and MPU domains go to idle, and then the TC also goes to idle. Then all 3 DPLLs go to idle, and the CHIP\_IDLE signal goes active high, which indicates to the external system that the OMAP5910 input clock can be disabled, assuming there are no wake-up conditions at that time indicated by the WAKEUP\_nREQ signal.

## 3.4.3 Wake-Up Procedure

An interrupt request (not masked) (either to the MPU or to the DSP), a DMA clock request, or a logical 1 at the TCLB\_EN signal exits the idle mode. In

addition, when all internal clocks are stopped (chip-idle mode), the wake-up procedure can be controlled via the ULPD. The WKUP\_MODE bit of the MPU-idle-mode-entry-1 register (ARM\_IDLECT1) defines this wake-up option.

To give the ULPD wake-up control, the WKUP\_MODE bit must be cleared to 0 before entering the idle mode.

In the OMAP5910 device, the WKUP\_MODE bit is controlled by the MPU in the MPU-idle-mode-entry-1 register (ARM\_IDLECT1). The DSP has no control of this bit.

When the WKUP\_MODE-bit value is set to logic 1, a single wake-up condition (as defined in the following list) initiates a chip wake-up procedure.

- nIRQ\_SET: Upon an interrupt request, the MPU-interrupt handler initiates the restart of the ARM\_CK, ARM\_INTH\_CK, TIPB\_CKs, DMA\_CK, and TC\_CK clocks (depending on the setting of the MPU-idle-mode-entry- 1/2 registers (ARM\_IDLECT1/2), peripherals clocks can also restart). If the idle mode was entered from the SETARM\_IDLE bit, then the bit is cleared to 0.

- DSP\_nIRQ: Upon an interrupt request, the DSP-interrupt handler initiates the restarting of the MPUI clock (if MPUICK\_EN is not set to 0), DSP\_CK, DSP\_INTH\_CK, TC\_CK clocks (depending on the setting of the MPU-idle-mode-entry-1/2 registers (ARM\_IDLECT1/2), peripheral clocks can also restart).

- TCLB\_EN signal: When the internal TCLB\_EN signal goes active, the TC\_CK and LB\_CK clocks restart. The TC\_CK/LB\_CK clocks keep running as long as the local-bus activity occurs.

- 4) When the system-DMA controller receives an asynchronous request from the traffic controller, the DMA\_CK/TC\_CK/LB\_CK and DMA\_CK/TC\_CK/LB\_CK are enabled to keep running as long as the DMA operates.

- 5) When the system-DMA controller receives a request from the TIPB bridge, it enables the TC\_CK/TIPB\_CKs/DMA\_CK and TC\_CK/TIPB\_CKs/D MA\_CK to keep running as long as the DMA operates.

#### Note:

The internal signals that cause the wake-ups are asynchronous and do not need a running clock to be activated. When the WKUP\_MODE bit value is a logical 0 and the CHIP\_IDLE signal is active, this condition indicates the entire chip is in the deep-sleep mode. The combination of one of the above conditions and a CHIP\_NWAKEUP request from the ULPD is required to exit the chip-idle mode. If WKUP\_MODE = 1, then the ULPD is not required to exit the chip-idle mode, only one of the above wake-up conditions.

If the CHIP\_IDLE signal is inactive (and at least one of the internal clocks is running), the CHIP\_nWAKEUP signal is disabled and a single wake-up condition (not ULPD controlled) brings the DSP or MPU system out of idle mode. A global-system reset brings the OMAP5910 device out of the idle mode, regardless of the WAKEUP\_MODE bit value, ULPD control, or the interrupt status.

Figure 14 illustrates a ULPD-controlled wake-up sequence (assuming the DSP and the MPU clock domains have the same clock frequency, CLKIN). The wake-up is initiated from an interrupt to the MPU, whereas the DSP remains in the idle mode.

SPRU678A

## 3.5 Power-Saving Capability

The OMAP5910 device has several power-saving modes that help to reduce the operating current by stopping the clock signals of the unused (inactive) domain(s). The idle controls to the DSP, the MPU, and the traffic controller provide a flexible and an efficient power-saving mechanism. The following list of power-saving modes is given as an example only, because other modes are possible. The system software can program the OMAP5910 device to operate in any of these modes for a specific application.

- Mode 0: The DSP is partially in the idle mode (see the DSP idle protocol).

- Mode 1: The DSP is in the global-idle mode.

- Mode 2: The MPU is in the idle mode (the DSP is still running) for both:

- System DMA controller is active.

- System DMA controller is not active.

- Mode 3: Both the MPU and DSP are set in the idle mode (peripherals are still active) for both:

- System DMA controller is active.

- System DMA controller is not active.

- Mode 4: The MPU, the DSP, and traffic controller are stopped (the traffic controller can be stopped only if both the MPU and the DSP are in idle) for both:

- Peripheral modules are individually stopped.

- All peripherals are stopped.

- □ Mode 5: The MPU, the DSP, the peripherals, and the DPLL (1) are stopped; however, the timer/watchdog (or OS-timer) is still active.

- Mode 6 (chip idle): The MPU, the DSP, the peripherals, the DPLL (1), and timers are stopped, while the ULPD clock source remains the only active clock signal.

- Mode 7 (deep sleep): All internal system clocks (the MPU, the DSP, the peripherals, the DPLL (1) and the timers) and the ULPD reference-clock source are stopped, leaving the OMAP5910 device in a static state in which it consumes the lowest-possible power.

In all power-saving modes, the OMAP5910 device retains all RAM data (keeps the memory data), and the register configuration values (for example, the frequency selection is maintained, etc.). The data to output terminals is also maintained, and input terminals are set to logic low or logic high (not floating) to reduce the current from flowing through the input logic.

50

The OMAP5910 device exits from the power-saving modes by means of a reset or any interrupt (with or without additional external control from the CHIP\_nWAKEUP pin). A wake-up interrupt must be enabled (not masked off) to bring the OMAP5910 device out of the power-saving mode.

## 3.6 ULPD Power-Management State Machine

The power-management function of the ultra low-power module (ULPD), handles the high-frequency oscillator on/off sequences. It is a state machine that can stop the oscillator and restart it on a wake-up signal. Set-up times of the oscillator are taken into account in order to stop/restart internal clocks in a clean manner. The ULPD state-machine uses the 32-kHz clock.

- □ The ULPD DPLL and APLL for the 48-MHz USB clock are handled in the ULPD module.

- ULPD DPLL is a x4 digital PLL.

- APLL is a x48 analog PLL. The input clock reference is 1 MHz, based on either a 12-MHz system clock divided by 12 or optionally on a 13-MHz system clock divided by 13.

- The switch between the DPLL and APLL is controlled by software through a TIPB register of the ULPD.

### 3.6.1 Gauging the 32-kHz Oscillator

As the 32-kHz oscillator exact frequency is unknown, it can be gauged by comparing the 32-kHz oscillator with a high-frequency clock (12-MHz oscillator, ULPD DPLL, or external clock) during any active period. Gauging is only necessary in specific applications where it is important to know the exact frequency of the 32-kHz oscillator.

There is a software limitation: the counter is not resynchronized on the TIPB strobe. Therefore, the value is not readable while the counter is running (when gauging is enabled). The gauging (GAUGING\_CTRL\_REG[0] = 0) must first be disabled, then read the high-frequency counter and the 32-kHz counter value.

## 3.6.2 Gauging Versus the High-Frequency Clock

To gauge the 32-kHz oscillator, two counters clocked on the 32-kHz clock and the high-frequency clock are concurrently running during the gauging period. The high-frequency clock is selected among the 12-MHz clock, the DPLL, and the external clock. At the end of the gauging period, the number of 32-kHz clocks and the number of high-frequency clocks are calculated as follows:

- □ Nb\_32kHz = counter\_32\_msb \* 65536 + counter\_32\_lsb:

- counter\_32\_msb is the MSB value of 32-kHz counter.

- counter\_32\_lsb is the LSB value of 32-kHz counter.

- Nb\_hi\_freq = counter\_hi\_freq\_msb \* 65536 + counter\_hi\_freq\_lsb:

- counter\_hi\_freq\_msb is the MSB value of high-frequency counter.

- counter\_hi\_freq\_lsb is the LSB value of high-frequency counter.

Use the following procedure to gauge the 32-kHz clock versus the high-frequency clock:

- 1) Select gauging versus the high-frequency clock:

- Write the gauging\_ctrl[0] = 0 to select gauging versus the 12-MHz clock.

or

- Write the gauging\_ctrl[0] = 1 to select gauging versus the external or DPLL clock.

- Start gauging by writing the gauging\_ctrl[1] = 0.

- 3) Wait a few seconds.

- On reception of the gauging interrupt (low-level sensitive interrupt), stop gauging by writing the gauging\_ctrl[1] = 0.

- 5) Check the overflow of the 32-kHz counter:

Read it\_status[2].

6) Check the overflow of the high-frequency counter:

Read it\_status[1].

- 7) If an overflow occurred during the process, then return to step 3 to restart the gauging and reduce the waiting time. Else continue to the next step.

- 8) Read the 32-kHz counter value:

Read the counter\_32\_msb and counter\_32\_lsb registers.

9) Read the hi\_freq counter value:

Read the counter\_hi\_freq\_msb and counter\_hi\_freq\_lsb registers.

10) Compare the values of the counter and proceed with calibration of the 32-kHz counter.

At the end of the gauging operation, an END\_GAUGING interrupt informs the MCU that gauging is stopped and values of the counters are ready to be read.

This interrupt is low-level sensitive. It is cleared on the reading of these registers.

Two other low-level-sensitive interrupts indicate whether an overflow occurred on one of the two counters during the gauging operation. One interrupt is dedicated for the 32-kHz counter, the second one for the high-frequency counter. They are also cleared on the read of the interrupt-status register.

## 3.6.3 Control of the 32-kHz Oscillator

The 32-kHz oscillator start-up time is configurable via the MOD\_32KOSC\_SW\_R bits of the module-configuration-control-0 register (MOD\_CONF\_CTRL\_0).

The 32kHz-clock source can come from either the on-chip 32-kHz oscillator or from an external 32-kHz-clock oscillator providing a clock onto the CLK32K\_IN-input pin. Clock source selection depends upon the state of the CLK32K\_CTRL-input pin. If this pin is driven (or tied) high, the on-chip 32-kHz oscillator is enabled as the clock source. If the pin is driven (or tied) low, then the clock must be provided externally on the CLK32K\_IN pin.

The MOD\_32KOSC\_SW\_R is a 4-bit field that sets the performance control switches of the 32-kHz oscillator (SW1, SW2, SW3, SW4). Table 4 lists the recommended control-switch settings:

## Table 4. Recommended Control-Switch Settings

| Oscillator Performance | SW4 | SW3 | SW2 | SW1 |

|------------------------|-----|-----|-----|-----|

| Least current          | 1   | 0   | 0   | 0   |

| Fast startup           | 1   | 0   | 1   | 1   |

## 3.6.4 Battery Failed

A battery-failed event is indicated via the BFAIL/EXT\_FIQ signal connected to the ULPD, which performs a power-down action. The ULPD processes the incoming BFAIL/EXT\_FIQ signal to an external device (via RST\_HOST\_OUT) to decrease a programmable counter and to generate a shutdown signal when the counter reaches zero. It also creates an interrupt on the MPU level 1. The release of the RST\_HOST\_OUT is controlled by software. The SW\_NSHUTDOWN bit in the power-control register (POWER\_CTRL\_REG) can be used to toggle the state of the RST\_HOST\_OUT pin to high or low level. A power-on reset condition also causes RST\_HOST\_OUT to be active low.

## 3.6.5 Big-Sleep and Deep-Sleep Mode

To go into deep-sleep mode, the MPU and DSP must release and unmask all interrupts that can awake the chip during this mode and they must mask all interrupts that do not awake the chip during the deep-sleep mode. Then the MPU enters the big-sleep mode. When the device reaches the idle state, it informs power management to enter into the sleep mode by setting the CHIP\_IDLE signal. The state machine cuts the 12-MHz OSC1 oscillator only if the external devices do not request the oscillator clock.

## 3.6.6 Power-On Reset

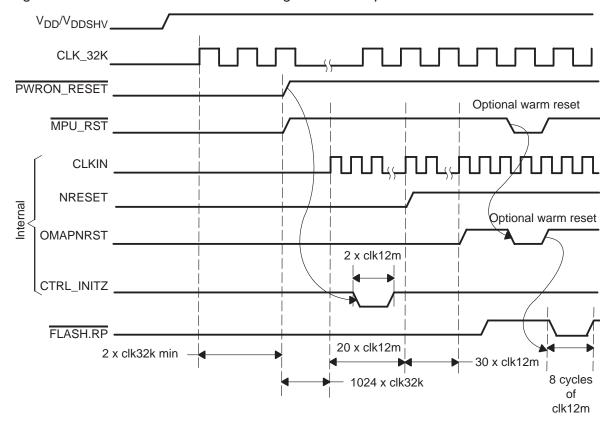

The PWRON\_RESET signal is used to reset the entire device. This signal is resynchronized on the 32-kHz oscillator to achieve a clean reset. Then the ULPD module initiates the internal-reset sequence (a minimum of two full 32-kHz clock periods is recommended). The 32-kHz logic within the ULPD module is reset asynchronously.

## 3.6.7 Interrupt Wake-Up

When at least one unmask interrupt has occurred during the deep-sleep mode, a wake-up sequence is performed. In this case, the chip must leave the deep-sleep mode as soon as possible to process this interrupt. To respect the schedule of the clock enables, the following wake-up sequence is processed: