## TI Designs: TIDA-00313 –48-V Telecom Current, Voltage, and Power Sense With Isolation Reference Design

# TEXAS INSTRUMENTS

## Description

This verified design can accurately measure current, voltage, and power on a bus that carries –48 V and is able to provide this data using an I<sup>2</sup>C-compatible interface. This design is targeted for telecom applications because this negative supply voltage is used with the most common of telecom equipment. This design uses the INA226 and ISO1541 devices. The INA226 is a current shunt and power monitor with an I<sup>2</sup>C-compatible interface. This device can make these precise measurements and uses the ISO1541 device to translate the negative voltage to ground-referenced signals. The ISO1541 is a low-power, bidirectional I<sup>2</sup>C-compatible isolator.

## Resources

TIDA-00313Design FolderINA226Product FolderINA226EVMProduct FolderISO1541Product FolderTINA-TITMProduct Folder

## Features

- –48-V Common Mode for Current Shunt Monitoring

- Measure Differential Shunt Voltages up to ±80 mV

- Reports Current, Bus Voltage, Shunt Voltage, and Power Measurements

- Power Isolated

- Low Power

- I<sup>2</sup>C Compatibility

### Applications

- Current Shunt Monitoring of Standard Telecom Equipment

- Telecom Infrastructure

R, R, (INA) (USE DIG) 12.1 k 35.7 k 13.1 k 35.7 k

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

## 1 System Description

The challenges that developers of telecom DC/DC power supplies face today include achieving high efficiency, high integration, low system cost, ease of development, and product differentiation. Customers demand additional features such as more sophisticated fault diagnosis, power measurement, and more extensive status reporting over the I<sup>2</sup>C or CAN interface. Texas Instruments has digital current shunt monitors capable of reporting current, voltage, and power when a positive power supply is applied to the input; however, most common telecom equipment use a negative supply range of –48 V. The goal of this reference design is to provide these status and monitoring features for a negative voltage bus. This design offers a solution using TI products for telecom companies that wish to monitor current and power in their applications.

## 1.1 Key System Specifications

| PARAMETER                      | DESCRIPTION                                                           | SPECIFICATIONS                                        |

|--------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|

| Bus voltage                    | Bus voltage of the current sense resistor in common telecom equipment | -48 V                                                 |

| Measurable shunt voltage range | Range of differential shunt voltages that system can measure          | ±80 mV                                                |

| Measurements                   | What the system can measure and report                                | Shunt voltage (and current), bus voltage ( and power) |

| Communication                  | System communication protocol                                         | I <sup>2</sup> C compatible                           |

## Table 1. Key System Specifications

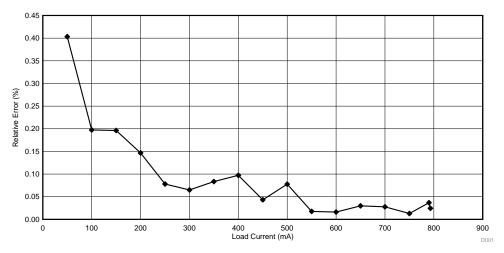

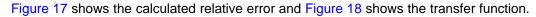

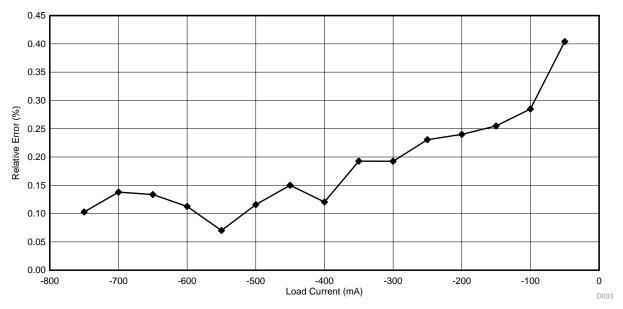

Table 2 summarizes the design goals and performance. Figure 1 shows the measurement accuracy of the design.

| Table 2. Comparison of Design Goals and Measured |  |  |

|--------------------------------------------------|--|--|

| Performance                                      |  |  |

| RELATIVE ERROR               | GOAL   | MEASURED |

|------------------------------|--------|----------|

| I <sub>load</sub> = 50 mA    | 0.510% | 0.403%   |

| $I_{load} = -50 \text{ mA}$  | 0.51%  | 0.404%   |

| I <sub>load</sub> = 750 mA   | 0.114% | 0.013%   |

| $I_{load} = -750 \text{ mA}$ | 0.114% | 0.103%   |

Figure 1. Measured Relative Error with  $R_{shunt}$  = 100 m $\Omega$  and  $I_{load}$  = 50 mA to 750 mA

## 2 System Overview

## 2.1 Block Diagram

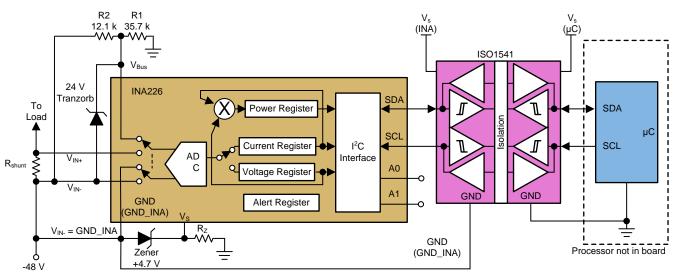

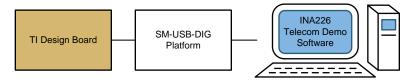

Figure 2 shows the basic idea of the design, which comprises three stages. The first stage uses a TI INA226 current shunt monitor to measure the load current while the device is floating at the –48-V rail. The second stage incorporates a low-power bidirectional isolator (ISO1541) with I<sup>2</sup>C communication capabilities. This isolator translates these –48-V reference signals to ground reference signals. The third stage uses the TI SM-USB-DIG Platform and INA226EVM software to display the data collected by the INA226 device.

Copyright © 2017, Texas Instruments Incorporated

Figure 2. TIDA-00313 Basic Block Diagram

## 2.2 Design Considerations

## 2.2.1 First Stage—INA226 Connections and External Components

The first stage of the circuit uses the INA226 device to monitor the shunt voltage and the bus supply voltage. The INA226 is limited to a bus input voltage range of 0 V to 36 V. This design is intended for use at -48 V, outside the INA226 input voltage capabilities. The following changes are required to enable the INA226 device to monitor the shunt and the -48-V bus supply voltage:

- Connect a 4.7-V Zener diode between the GND and the V<sub>s</sub> pins of the INA226. The potential generated by the voltage drop across the Zener diode and referenced to the negative rail (–48 V) powers the INA226 device. This action provides the positive supply voltage (V<sub>s</sub>) that the INA226 device requires to operate.

- Incorporate a voltage divider on the V<sub>bus</sub> pin input. Doing so helps to limit the input voltage of the V<sub>bus</sub> to 36 V maximum, even though –48 V has been applied to the input.

(2)

#### System Overview

### 2.2.2 INA226 Referenced to Negative Rail

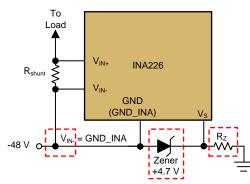

A separate supply that can range from 2.7 V to 5.5 V typically powers the INA226 device. For this design, connect a 4.7-V Zener diode between the GND (GND\_INA) and V<sub>s</sub> pins of the INA226. Also, the INA226 ground pin (GND) is tied to the V<sub>in</sub> pin of the INA226 (see Figure 3). This configuration powers the device using the potential generated by the voltage drop across the Zener diode and references the device to the -48-V rail.

Copyright © 2017, Texas Instruments Incorporated

Figure 3. Connections for Negative Voltage Reference

A power resistor (R<sub>z</sub>) is required in series with the Zener diode. Equation 1 calculates the resistor value and Figure 4 shows a TINA-TI<sup>TM</sup> DC simulation with the circuit configuration, calculated values, and results. For this calculation, the designer must consider the Zener bias current and the INA226 quiescent current. From the INA226 data sheet specifications, the maximum quiescent current is 420  $\mu$ A with V<sub>s</sub> = 3.3 V. Because this design specifies to power the device with +4.7 V, estimate the INA226 quiescent current to be approximately 600  $\mu$ A, maximum.

$$R_{z} = \frac{|V_{in-} - V_{zener}|}{I_{zener} + I_{INA226}} = \frac{|48 \text{ V} - (-4.7 \text{ V})|}{5 \text{ mA} + 600 \text{ }\mu\text{A}} = 7.73 \text{ k}\Omega$$

(1)

Equation 2 shows the power consumption calculation, which is required to determine the power rating of the  $R_z$  resistor.

Power =

$$\frac{V^2}{R} = \frac{|V_{in-} - V_{zener}|^2}{R_z} = \frac{|-48 \text{ V} - (-4.7 \text{ V})|^2}{7.73 \text{ k}\Omega} = 0.2425 \text{ W}$$

Vzener -4.69V

Vzener -4.69V

Vzener -4.69V

Vzener -4.69V

Vzener -4.69V

Vzener -4.69V

Current 5.6mA

Copyright © 2017, Texas Instruments Incorporated

**Figure 4. Power Resistor Selection Simulation**

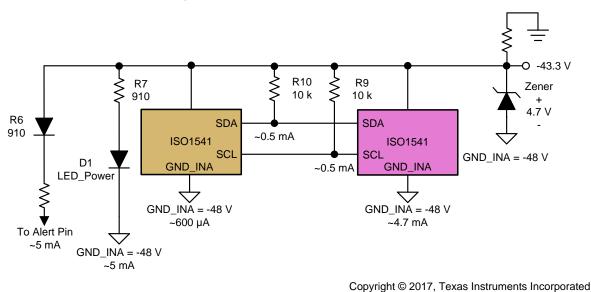

The INA226 has more devices connected to the  $V_s$  pin, such as the ISO1541 isolator and some lightemitting diodes (LEDs) which are included on this design. These other devices increase the current flowing through this resistor. For this reason, the  $R_z$  resistor value requires modification. Figure 5 shows all devices connected to the  $V_s$  pin.

Figure 5. Devices Connected to INA226  $V_s$  Pin

Table 3 lists the current expected to flow through the  $R_z$  resistor.

| •                                   | • -                           |

|-------------------------------------|-------------------------------|

| DEVICE                              | CURRENT                       |

| D2 (LED diode for the alert pin)    | 5.0 mA                        |

| D1 (LED diode for power, $V_s$ pin) | 5.0 mA                        |

| INA226                              | 0.6 mA                        |

| ISO1541                             | 4.7 mA                        |

| SDA pullup                          | 0.5 mA                        |

| SCL pullup                          | 0.5 mA                        |

| Zener diode                         | 5.0 mA                        |

|                                     | I <sub>TOTAL</sub> = ≈21.3 mA |

Table 3. Expected Current to Flow Through R<sub>z</sub>

Approximating  $I_{TOTAL}$  to be 24 mA, calculate the new  $R_z$  and its required power rating (see Equation 3).

$$R_{z} = \frac{|V_{in} - V_{zener}|}{I_{TOTAL}} = \frac{|-48 \text{ V} - (-4.7 \text{ V})|}{24 \text{ mA}} = 1.8 \text{ k}\Omega$$

$$Power = \frac{V^{2}}{R} = \frac{|V_{in-} - V_{zener}|^{2}}{R_{z}} = \frac{|-48 \text{ V} - (-4.7 \text{ V})|^{2}}{1.8 \text{ k}\Omega} = 1.04 \text{ W}$$

(3)

System Overview

### 2.2.3 Limiting Input Voltage of V<sub>bus</sub>

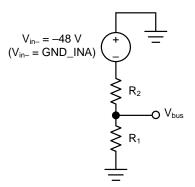

The INA226  $V_{bus}$  pin is limited to 36 V. This design uses voltages greater than 36 V; therefore, a voltage divider is required at the input of the bus voltage pin. Note that the INA226 device measures the bus voltage,  $V_{bus}$ , with respect to GND\_INA. Figure 6 shows the voltage divider and Equation 4 shows the basic voltage divider equation.

### Figure 6. Voltage Divider

$$V_{\text{bus}} = \frac{R_2}{R_1 + R_2} \times V_{\text{in}-} \tag{4}$$

Target a voltage divider ratio of 4:1 (4  $V_{bus} = V_{in-}$ ), as Equation 5 shows.

$$V_{\text{bus}} = \frac{1}{4} \times V_{\text{in}-} \tag{5}$$

Combine Figure 6 and Equation 5 to obtain Equation 6.

$$\frac{R_2}{R_1 + R_2} = \frac{1}{4}$$

(6)

Rearrange Equation 6 to define the relation for  $R_1$  and  $R_2$  in Equation 7.

$$\frac{\mathsf{R}_1}{\mathsf{R}_2} = 3 \tag{7}$$

Another important detail to consider is that the V<sub>bus</sub> pin has an input impedance of 830 k $\Omega$ . The 830-k $\Omega$  impedance, R<sub>Vbus</sub>, is connected in reference to GND\_INA, which means it will be in parallel with R<sub>2</sub>. Now calculate Equation 8 as:

$$\frac{R_1}{R_2 / / R_{Vbus}} = 3 \tag{8}$$

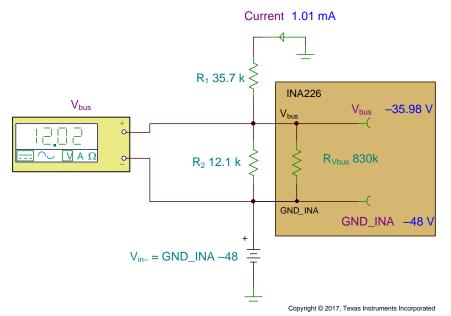

For this design, choose  $R_1 = 35.7 \text{ k}\Omega$  and  $R_2 = 12.1 \text{ k}\Omega$ . With this combination of resistors and with  $V_{\text{in-}}$  at -48 V, the  $V_{\text{bus}}$  has 12.02 in reference to GND\_INA (see Equation 9). Also, just 1 mA of current will flow in that path. If the designer were to select lower resistor values, such as  $R_1 = 3 \text{ k}\Omega$  and  $R_2 = 1 \text{ k}\Omega$ , around 10 mA of current would be driven. The lower the resistor value, the larger the current that flows in that path.

$$V_{\text{bus}} = \frac{R_2}{R_1 + R_2} \times V_{\text{in}-} = \frac{12.1k}{35.7k + 12.1k} \times -48 \text{ V} = -12.02 \text{ V}$$

(9)

7

Figure 7 shows a simple simulation in TINA-TI<sup>TM</sup> that shows the position and value of the selected resistors, how  $V_{bus}$  is measured, and how much current to expect with these resistors values.

Figure 7. TINA-TI<sup>™</sup> Simulation of Voltage Divider

A TVS (transient voltage suppressor) diode provides protection against surge at the  $V_{bus}$  input. TVS devices are ideal for the protection of I/O interfaces, the VCC bus, and other vulnerable circuits for use in telecom applications. With the bus voltage maximum specified as 36 V, the TVS diode must have a breakdown voltage slightly lower than 36 V. The SMBJ24A is selected to protect the INA226 device.

Note that with the V<sub>bus</sub> connected to the V<sub>in</sub> pin (through R<sub>2</sub>), V<sub>bus</sub> measurements will reflect the divideddown voltage of the bus line source. Thus, the power readings of the INA226 will be the power of the entire system. If knowing the power supplied to the load was desired, then V<sub>bus</sub> should be connected to the V<sub>in+</sub> pin (through R<sub>2</sub>). In this case, V<sub>bus</sub> measurements would reflect the divided-down voltage of the load.

Also, note that if the absolute bus voltage of the system is within the  $V_{bus}$  input operating voltage range (0 V to 36 V), then the resistor divider is not required and the user can connect the  $V_{bus}$  directly to the earth ground of the system.

8

#### 2.2.4 **INA226 Filtering and Input Considerations**

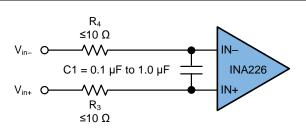

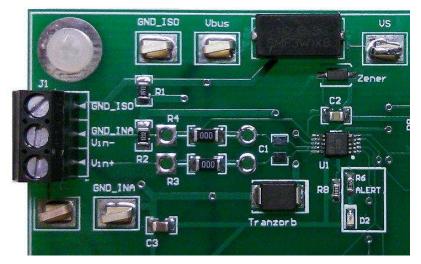

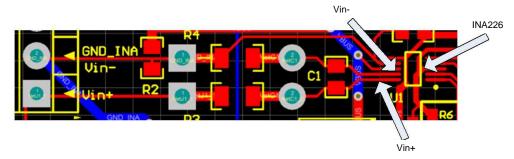

The TIDA-00313 board has an optional input filter to remove high-frequency noise from the inputs V<sub>in+</sub> and  $V_{in-}$ . The default values for  $R_3$  and  $R_4$  are 0- $\Omega$  resistors. Figure 8 shows the recommended values for the filter. Figure 9 shows the location of the filter in the board. The board comes populated with two 0-Ω resistors (R<sub>3</sub> and R<sub>4</sub>). However, the filter capacitor does not come preinstalled. If a filter is required, use the lowest possible series resistance (typically 10  $\Omega$  or less) and a ceramic capacitor. The recommended values for this capacitor are 0.1  $\mu$ F to 1.0  $\mu$ F. In many cases, a filter is not necessary.

**NOTE:** Make sure the  $0-\Omega$  resistors are populated on the board; otherwise, the input of the INA226 device remains open.

Copyright © 2017, Texas Instruments Incorporated

**Figure 8. Input Filter Schematic**

Figure 9. Location of Input Filter in TIDA-00313 Board

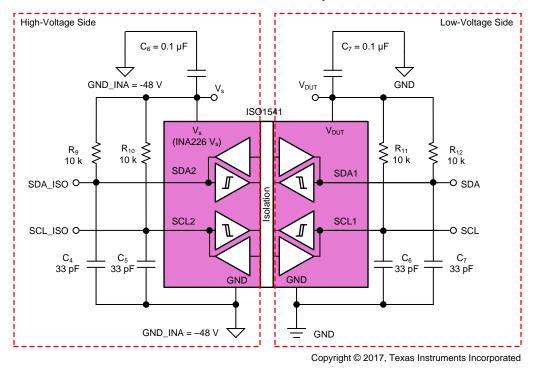

## 2.2.5 Second Stage—ISO1541 Connections and External Components

The second stage of the circuit uses the ISO1541. The ISO1541 is a low-power, bidirectional  $I^2C$ compatible bus isolator. For more information about how the ISO1541 operates, see *ISO154x Low-Power Bidirectional I*<sup>2</sup>*C Isolators* (SLLSEB6).

The ISO1541 device requires pullup resistors on the SCL and SDA pins. Pullup resistors of 10 k $\Omega$  are selected for this design. Capacitors (C<sub>4</sub>, C<sub>5</sub>, C<sub>6</sub>, and C<sub>7</sub>) have also been connected to match the test diagram shown in the ISO1541 data sheet, but these are *optional*. TI recommends a 0.01-µF bypass capacitor on the supply. Figure 10 shows how the ISO1541 is incorporated in this design. The high-voltage side is connected to the INA226 V<sub>s</sub>, GND, SCL, and SDA pins. The low-voltage side is connected to the data collected by the INA226 device.

Figure 10. ISO1541 Connections

## 2.2.6 Third Stage—SM-USB-DIG Platform and INA226 Software

The third stage uses the TI SM-USB-DIG Platform and INA226EVM software to display the data collected by the INA226 device. Figure 11 shows the overall system setup for the TIDA-00313 system. The PC runs software (INA226 Telecom Demo Software) that communicates with the SM-USB-DIG Platform. The SM-USB-DIG Platform provides the supply voltage for the low-voltage side of the ISO1541 device and generates digital signals used to communicate with the TIDA-00313 board. Connectors on the board allow the user to connect to the system under test and monitor the power, current, and voltage.

Figure 11. TIDA-00313 System Setup

For more information about the SM-USB-Dig Platform, see *SM-USB-DIG Platform* (SBOU098). For a quick tutorial on the INA226EVM software, see *INA226EVM Evaluation Board and Software Tutorial* (SBOU113).

## 2.3 Highlighted Products

### 2.3.1 INA226

The function of this design calls for a current shunt monitor with a wide common-mode range; high accuracy; the ability to report current, voltage, and power; and the capability to perform I<sup>2</sup>C interface communications. The chosen current shunt monitor for this application is the INA226. This device not only has the resolution and accuracy required to achieve the design goals, but also features all the internal subsystems required to realize the current, voltage, and power calculations.

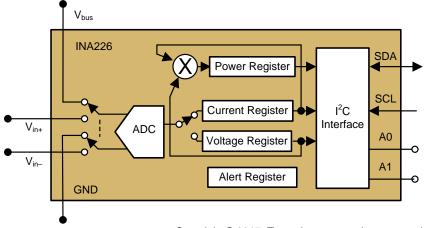

The INA226 is a digital current shunt monitor with an I<sup>2</sup>C interface. The device takes two measurements: shunt voltage and bus voltage. Figure 12 shows a basic block diagram of INA226. For more information about INA226 features, see *INA226 High-Side or Low-Side Measurement, Bi-Directional Current and Power Monitor with PC Compatible Interface* (SBOS547).

Copyright © 2017, Texas Instruments Incorporated

Figure 12. INA226 Basic Block Diagram

## 2.3.2 ISO1541

10

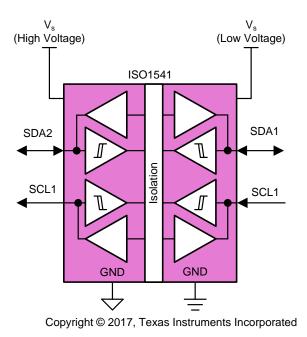

In this design the INA226 device is referenced to the –48-V rail. This task requires a device that is capable of translating a –48-V reference into ground referenced signals. Additional requirements consist of low power consumption, compatibility with I<sup>2</sup>C interfaces, and a 3.3-V to 5-V supply voltage range. The device selected for this task is the ISO1541.

The ISO1541 is a low-power, bidirectional  $I^2C$  bus isolator. The ISO1541 has its logic input and output buffers separated by TI's capacitive isolation technology using a silicon dioxide (SiO<sub>2</sub>) barrier. This isolation technology provides for function, performance, size, and power consumption advantages when compared to optocouplers. The ISO1541 has a bidirectional data and a unidirectional clock channel. The device is compatible with I<sup>2</sup>C interfaces and its supply range, 3 V to 5.5 V, meets the supply requirements of this design. Figure 13 shows a basic block diagram of ISO1541. For more information about the ISO1541, see *ISO154x Low-Power Bidirectional f<sup>2</sup>C Isolators* (SLLSEB6).

Figure 13. ISO1541 Block Diagram

## 3 Hardware, Software, and Test Results

## 3.1 Required Hardware and Software

## 3.1.1 Hardware

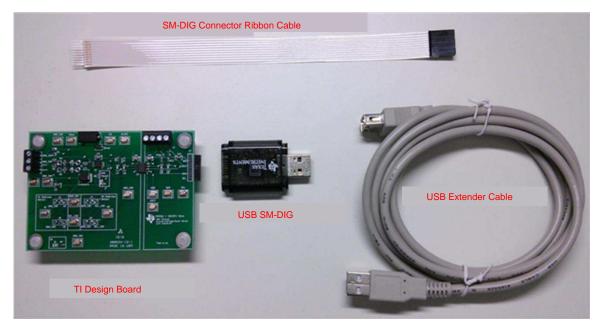

The contents of the reference design kit are as follows:

- TIDA-00313 board

- USB SM-DIG Platform PCB

- USB extender cable

- SM-Dig connector ribbon cable

Figure 14 shows the included hardware.

Figure 14. Required Hardware for TIDA-00313 Evaluation

## 3.1.1.1 INA226 Telecom Demo Hardware Setup

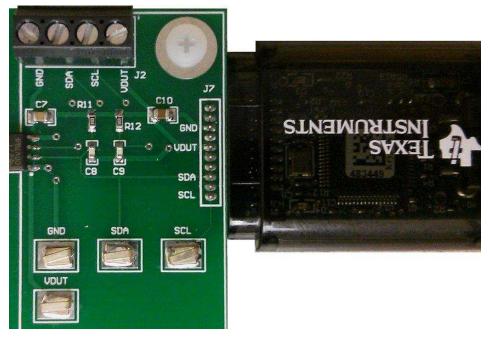

Connect the INA226 Telecom Demo and the USB SM-DIG Platform together. Make sure that the two connectors are completely pushed together; loose connections may cause intermittent operation. Figure 15 shows the board connected to the platform (the Texas Instruments logo should be upside down).

Figure 15. How to Connect TIDA-00313 Board and USB SM-DIG Platform

After the INA226 Telecom Demo board and SM-DIG are connected as shown in Figure 15, connect the desired bus voltage and shunt configuration intended to be measured. For this, connect an external DC power supply of –48 V to the  $V_{in-}$  (GND\_INA) pin referenced to the GND\_ISO pin on terminal block J1. Also, connect a shunt resistor between the  $V_{in+}$  and  $V_{in-}$  terminals. When connecting a load, attach it to the  $V_{in+}$  pin at terminal block J1. See Figure 24 for a layer reference.

## 3.1.1.2 INA226 Telecom Demo Jumper Settings

Jumpers 3 through 6 (J3-J6) control the I<sup>2</sup>C address pin for the INA226; these jumpers can set the address for A0 and A1 to either high, low, SCL, or SDA. Make sure to only connect one jumper at a time for each address control; for example, connecting only J3 and not J4. Failure to properly connect jumpers can cause shorts or interruptions in the communication lines. For more information on the INA226 addressing, see *INA226 High-Side or Low-Side Measurement*, *Bi-Directional Current and Power Monitor with PC Compatible Interface* (SBOS547). Table 4 summarizes the function of the TIDA-00313 board jumpers.

| JUMPER | DEFAULT | PURPOSE                                                                                                                                                                                                                          |

|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J3/J4  | GND     | This jumper selects $I^2C$ AO address selection for A0. The designer can select from four separate $I^2C$ addresses depending on whether J3 has been set to high or low or if J4 has been set to SDA or SCL.                     |

| J5/J6  | GND     | This jumper selects I <sup>2</sup> C AO address selection for A1. The designer can select from four separate I <sup>2</sup> C addresses depending on whether J5 has been set to high or low or if J6 has been set to SDA or SCL. |

| Table 4. TIDA-00313 Jumper Function |

|-------------------------------------|

|-------------------------------------|

### 3.1.1.3 INA226 Telecom Demo Features

This section describes some of the hardware features present on the TIDA-00313 board.

• J3 and J4 – I<sup>2</sup>C address hardware setting (A0):

Use jumper J3 and J4 to configure the hardware settings for the A0 I<sup>2</sup>C address pin on the INA226. Using J3, the A0 address can be set to either a logic "1" or a logic "0". Using J4, the A0 address can be set to either the SCL or SDA communication line. Make sure to only have either J3 or J4 connected individually; failure to keep these lines separate can lead to board shorts and problems with the I<sup>2</sup>C communication lines. For more information on how to configure the INA226EVM software to match the J3 and J4 hardware setting, see the section regarding I<sup>2</sup>C address selection in *INA226EVM Evaluation Board and Software Tutorial* (SBOU113).

• J5 and J6 – I<sup>2</sup>C address hardware setting (A1):

Use jumper J5 and J6 to configure the hardware settings for the A1 I<sup>2</sup>C address pin on the INA226. Using J3, the A1 address can be set to either a logic "1" or a logic "0". Using J4, the A1 address can be set to either the SCL or SDA communication line. Make sure to only have either J5 or J6 connected individually; failure to keep these lines separate can lead to board shorts and problems with the I<sup>2</sup>C communication lines. For more information on how to configure the INA226EVM software to match the J5 and J6 hardware setting, see the section regarding I<sup>2</sup>C address selection in *INA226EVM Evaluation Board and Software Tutorial* (SBOU113).

• External I<sup>2</sup>C lines and terminal block J2:

The I<sup>2</sup>C communication lines on the TIDA-00313 board are tied to two sources: The internal I<sup>2</sup>C communication lines from the SM-DIG (J7) and the terminal block J2. In the event the user wants to add an external signal separate from the SM-DIG, simply disconnect the SM-DIG from the TIDA-00313 board and hook up the required SDA, SCL, and GND lines. Also, remember to apply an external DVDD to the lines that are compatible with the I<sup>2</sup>C communication device in use.

## 3.1.2 Software

A modified version of the INA226EVM software has been released which is only for this demonstration of this reference design. This new version is known as the INA226 Telecom Demo Software and it allows the user to modify the least significant bit (LSB) step size of the bus voltage, a feature not available in the INA226EVM software. The LSB step-size value requires modification due to dividing the bus voltage by 4 (with the voltage divider), which is done to meet the voltage specifications of the INA226 input bus.

Currently, the INA226EVM software uses 1.25 mV as the LSB step size for the bus voltage. The user must note the importance of taking this LSB number and multiplying it by the voltage divider ratio, 4. Failure to property set the LSB step size results in incorrect bus voltage readings.

The new LSB value is 5 mV (see Equation 10). This 5-mV value has been set as the default in the INA226 Telecom Demo Software.

New  $LSB = (Vbus _Divider) \times (Old _LSB) = 4 \times 1.25 \text{ mV} = 5 \text{ mV}$

(10)

where,

- New\_LSB: New LSB step size (bus voltage),

- Old\_LSB: Old LSB step size (bus voltage),

- Vbus\_Divider: V<sub>bus</sub> voltage divider ratio.

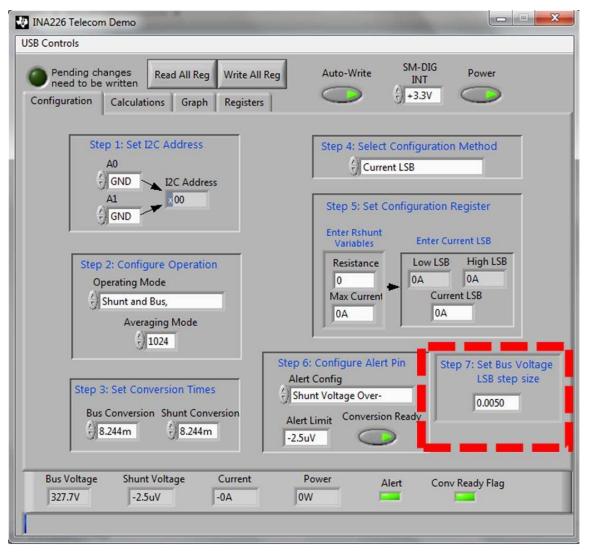

Figure 16 shows the graphical user interface (GUI) of the INA226 Telecom Demo. Note "Step 7" enclosed in the red-dotted box. This step is not included in the INA226EVM software GUI. Use Step 7 to set the step-size value for the bus voltage LSB. This exclusion is the only modification that has been made to the INA226EVM GUI. For software configuration and GUI instructions, see *INA226EVM Evaluation Board and Software Tutorial* (SBOU113).

Figure 16. INA226 Telecom Demo GUI

No simulation models are available for the INA226 device, so it is currently not possible to simulate the full functionality of the system.

#### 3.2 Testing and Results—Measuring System DC Transfer Function

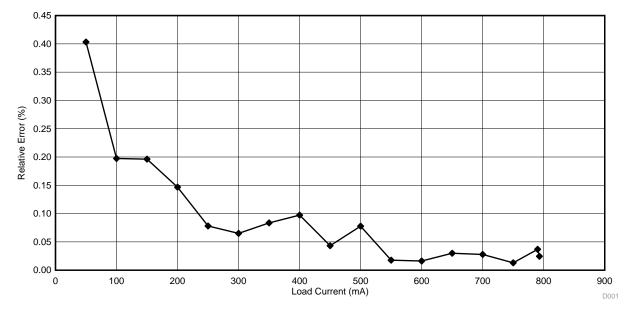

#### 3.2.1 Data Collected With $R_{shunt}$ = 100 m $\Omega$ and $I_{load}$ = 50 mA to 750 mA

Data was collected by sweeping the load current from 50 mA to 750 mA and measuring the shunt voltage of the INA226 device across a 100-m $\Omega$  shunt resistor. Table 5 shows the collected data. Vshunt<sub>REAL</sub> is the actual differential voltage that is applied to the differential input and a precision voltmeter measures this voltage at the inputs of the INA226 device. Vshunt<sub>INA226</sub> is the V<sub>shunt</sub> reported by the INA226 device.

The relative error has been calculated using Equation 11.

$% Reletive\_Error = \frac{Vshunt_{REAL} - Vshunt_{INA226}}{Vshunt_{REAL}} \times 100$

(11)

### Hardware, Software, and Test Results

www.ti.com

|                         |                   | Shunc                       | 1044                          |         |

|-------------------------|-------------------|-----------------------------|-------------------------------|---------|

| R <sub>shunt</sub> (mΩ) | LOAD CURRENT (mA) | VSHUNT <sub>REAL</sub> (mV) | VSHUNT <sub>INA226</sub> (mV) | % ERROR |

| 100                     | 50                | 4.96                        | 4.94                          | 0.403   |

| 100                     | 100               | 10.13                       | 10.11                         | 0.197   |

| 100                     | 150               | 15.29                       | 15.26                         | 0.196   |

| 100                     | 200               | 20.45                       | 20.42                         | 0.147   |

| 100                     | 250               | 25.61                       | 25.59                         | 0.078   |

| 100                     | 300               | 30.78                       | 30.76                         | 0.065   |

| 100                     | 350               | 35.94                       | 35.91                         | 0.083   |

| 100                     | 400               | 41.11                       | 41.07                         | 0.097   |

| 100                     | 450               | 46.27                       | 46.25                         | 0.043   |

| 100                     | 500               | 51.43                       | 51.39                         | 0.078   |

| 100                     | 550               | 56.6                        | 56.59                         | 0.018   |

| 100                     | 600               | 61.78                       | 61.77                         | 0.016   |

| 100                     | 650               | 66.97                       | 66.95                         | 0.030   |

| 100                     | 700               | 72.13                       | 72.11                         | 0.028   |

| 100                     | 750               | 77.29                       | 77.3                          | 0.013   |

## Table 5. Data Collected With $R_{shunt}$ = 100 m $\Omega$ and $I_{load}$ = 50 mA to 750 mA

Figure 18. Measured DC Transfer Function (V<sub>shunt</sub> vs I<sub>IN</sub>) With R<sub>shunt</sub> = 100 m $\Omega$  and I<sub>load</sub> = 50 mA to 750 mA

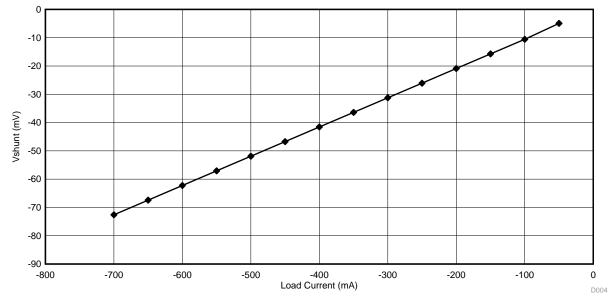

## 3.2.2 Data Collected With $R_{shunt} = 100 \text{ m}\Omega$ and $I_{load} = -50 \text{ mA to } -750 \text{ mA}$

A new set of data was collected by sweeping the load current from -50 mA to -750 mA and measuring the shunt voltage of the INA226 device across a 100-m $\Omega$  shunt resistor. Table 6 shows the collected data.

| R <sub>shunt</sub> (mΩ) | LOAD CURRENT (mA) | VSHUNT <sub>REAL</sub> (mV) | VSHUNT <sub>INA226</sub> (mV) | % ERROR |

|-------------------------|-------------------|-----------------------------|-------------------------------|---------|

| 100                     | -50               | -4.95                       | -4.93                         | 0.404   |

| 100                     | -100              | -10.53                      | -10.56                        | 0.285   |

| 100                     | -150              | -15.69                      | -15.73                        | 0.255   |

| 100                     | -200              | -20.84                      | -20.89                        | 0.240   |

| 100                     | -250              | -26.01                      | -26.07                        | 0.231   |

| 100                     | -300              | -31.17                      | -31.23                        | 0.192   |

| 100                     | -350              | -36.33                      | -36.4                         | 0.193   |

| 100                     | -400              | -41.5                       | -41.55                        | 0.120   |

| 100                     | -450              | -46.66                      | -46.73                        | 0.150   |

| 100                     | -500              | -51.83                      | -51.89                        | 0.116   |

| 100                     | -550              | -57.01                      | -57.05                        | 0.070   |

| 100                     | -600              | -62.17                      | -62.24                        | 0.113   |

| 100                     | -650              | -67.33                      | -67.42                        | 0.134   |

| 100                     | -700              | -72.51                      | -72.61                        | 0.138   |

| 100                     | -750              | -77.78                      | -77.86                        | 0.103   |

Table 6. Data Collected With  $R_{shunt} = 100 \text{ m}\Omega$  and  $I_{load} = -50 \text{ mA}$  to -750 mA

### Hardware, Software, and Test Results

Figure 19 shows the calculated relative error and Figure 20 shows the transfer function.

Figure 20. Measured DC Transfer Function (V<sub>shunt</sub> vs I<sub>IN</sub>) With R<sub>shunt</sub> = 100 m $\Omega$  and I<sub>load</sub> = -50 mA to -750 mA

## 3.3 Maximum Shunt Voltage Error Analysis

To set the design goals, the main influences of maximum shunt voltage errors are identified as follows:

- Input offset voltage (V<sub>os</sub>) of the INA226

- Shunt voltage gain error

- Common-mode rejection (CMR) of the INA226

- Power supply rejection (PSR) of the INA226

- Input offset current (I<sub>os</sub>)

- Shunt resistor tolerance

## 3.3.1 Errors at Small Values of Load Current

When the load current is small, there is a corresponding small input voltage to the INA226. Thus, errors will be dominated primarily by the input-offset-related errors. Determining the errors associated with each parameter is straightforward and the following subsections address this process.

## 3.3.2 Initial Offset Voltage Error

Take the maximum error due to input offset voltage directly from the INA226 device specification. The maximum input offset voltage is given as 10  $\mu$ V at 25°C. This error is calculated with respect to the ideal voltage across the shunt (V<sub>shunt</sub>). The ideal shunt voltage is the product of the load current and ideal shunt resistor value. The system nominal current is 50 mA and the ideal shunt resistor value is 100 m $\Omega$  (see Equation 12).

$$e_{V_{os}} = \frac{V_{os(max)}}{V_{shunt}} \times 100 = \frac{V_{os(max)}}{I_{load} \times R_{shunt}} \times 100 = \frac{10 \,\mu V}{50 \,\text{mA} \times 100 \,\text{m}\Omega} \times 100 = 0.20\%$$

(12)

## 3.3.3 Initial CMR Error

Calculate the maximum input offset error due to the common-mode rejection of the INA226 by determining the actual common-mode voltage as applied to the INA226 with a reference to the ground pin of the INA226. The INA226 device specification gives the common-mode rejection ratio minimum as 126 dB (0.501  $\mu$ V/V). The offset voltage in the data sheet is specified with a common-mode voltage that is 12 V higher than what is known as GND\_INA, -48 V. This means that the datasheet specification of 12-V bus voltage is the same as -36 V in this application, V<sub>cm-pds</sub> = -36 V. The resulting common-mode error is determined as calculated in Equation 13:

$$e_{CMRR} = \frac{\left(V_{cm-pds} - V_{cm-sys}\right) \times CMRR_{INA226}}{V_{shunt}} \times 100 = \frac{\left(-36 \ V - (-48 \ V)\right) \times 0.501 \frac{\mu v}{V}}{50 \ mA \times 100 \ m\Omega} \times 100 = 0.120\%$$

(13)

## 3.3.4 Initial PSR Error

Error due to power supply rejection ratio (PSRR) can be calculated in a manner similar to common-mode rejection ratio (CMRR). The INA226 device specification gives the specified power supply voltage for the input offset voltage specification as 3.3 V. Any deviation from 3.3 V applied between the INA226 V+ pin and ground pin results in an additional error. The INA226 device specification gives the PSRR minimum as 2.5  $\mu$ V/V. Equation 14 calculates the PSR error:

$$e_{PSRR} = \frac{\left( \left| V_{s-pds} - V_{s-sys} \right| \right) \times PSRR_{INA226}}{V_{shunt}} \times 100 = \frac{\left( \left| 3.3 \text{ V} - \left( -4.7 \text{ V} \right) \right| \right) \times 2.5 \frac{\mu V}{V}}{50 \text{ mA} \times 100 \text{ m}\Omega} \times 100 = 0.07\%$$

(14)

• •

#### 3.3.5 Input Bias Current Error

The input bias current is given as 10 µA at 25°C. This error is calculated with respect to the ideal voltage across the shunt (V<sub>shunt</sub>). The ideal shunt voltage is the product of the load current and ideal shunt resistor value. The system nominal current is 50 mA and the ideal shunt resistor value is 100 m $\Omega$ .

$$\mathbf{e}_{\mathbf{I}_{B}} = \frac{\mathbf{I}_{B} \times \mathbf{R}_{shunt}}{\mathbf{V}_{shunt}} \times 100 = \frac{10 \ \mu A \times 100 \ m\Omega}{50 \ mA \times 100 \ m\Omega} \times 100 = \frac{1 \ \mu V}{5 \ mV} \times 100 = 0.02\%$$

(15)

#### 3.3.6 Shunt Voltage Gain Error

The INA226 device specification gives the shunt voltage gain error as 0.1%.

#### 3.3.7 **Total Error at Small Currents**

Equation 16 calculates the worst-case total error at small load currents.

$$e_{\text{total-worst-case}}(\%) = \sum_{1}^{n} e_{n} = 0.20 + 0.120 + 0.07 + 0.02 + 0.1 = 0.510\%$$

(16)

#### 3.3.8 Errors at Large Values of Load Current

At large load currents, the input voltage that develops across the shunt resistor will be at its maximum. This condition minimizes the percentage contribution of the errors from the previously-described initial error sources. The dominant errors sources for large inputs are:

- Shunt voltage gain error from the INA226

- Shunt resistor accuracy •

#### 3.3.9 INA226 Shunt Voltage Gain Error

The INA226 device specification gives the shunt voltage gain error as 0.1%.

#### 3.3.10 Shunt Resistor Error

The assumption in this design is that the shunt resistor tolerance (accuracy) is 1.0%; however, disregard this value because the differential voltage that is reported in the previous results has been measured at the inputs of the INA226 with a precision voltmeter. Measuring at the inputs of the INA226 eliminates the shunt resistor error contribution in these results.

#### 3.3.11 CMR, PSR, and V<sub>os</sub> Errors

The total error at a large load current also include the errors due to CMR, PSR, Vos, and input bias current with respect to the maximum load current (750 mA). Equation 17, Equation 18, and Equation 19 calculate the errors as follows:

$$e_{CMRR} = \frac{\left(V_{cm-pds} - V_{cm-sys}\right) \times CMRR_{INA226}}{V_{shunt}} \times 100 = \frac{\left(-36 \ V - (-48 \ V)\right) \times 0.501 \frac{\mu V}{V}}{750 \ mA \times 100 \ m\Omega} \times 100 = 0.0080\%$$

(17)

$$e_{PSRR} = \frac{\left( \left| V_{s-pds} - V_{s-sys} \right| \right) \times PSRR_{INA226}}{V_{shunt}} \times 100 = \frac{\left( \left| 3.3 \ V - 4.7 \ V \right| \right) \times 2.5 \frac{\mu V}{V}}{750 \ mA \times 100 \ m\Omega} \times 100 = 0.0047\%$$

(18)

$$\mathbf{e}_{\mathbf{I}_{B}} = \frac{\mathbf{I}_{B} \times \mathbf{R}_{shunt}}{\mathbf{V}_{shunt}} \times 100 = \frac{10 \ \mu A \times 100 \ \mathrm{m}\Omega}{\mathbf{I}_{load} \times \mathbf{R}_{shunt}} \times 100 = \frac{1 \ \mu V}{750 \ \mathrm{m}A \times 100 \ \mathrm{m}\Omega} \times 100 = 0.0013\%$$

(19)

#### 3.3.12 **Total Error at High Currents**

Equation 20 calculates the worst-case total error at high load currents.

$$\mathbf{e}_{\text{total-worst-case}}(\%) = \sum_{1}^{n} \mathbf{e}_{n} = 0.1 + 0.0080 + 0.0047 + 0.0013 = 0.1140\%$$

(20)

## 3.4 Measured Results Summary

Table 7 summarizes the measured performance results.

| RELATIVE ERROR               | GOAL   | MEASURED |

|------------------------------|--------|----------|

| I <sub>load</sub> = 50 mA    | 0.510% | 0.403%   |

| $I_{load} = -50 \text{ mA}$  | 0.510% | 0.404%   |

| I <sub>load</sub> = 750 mA   | 0.114% | 0.013%   |

| $I_{load} = -750 \text{ mA}$ | 0.114% | 0.103%   |

## 3.5 V<sub>bus</sub> Range

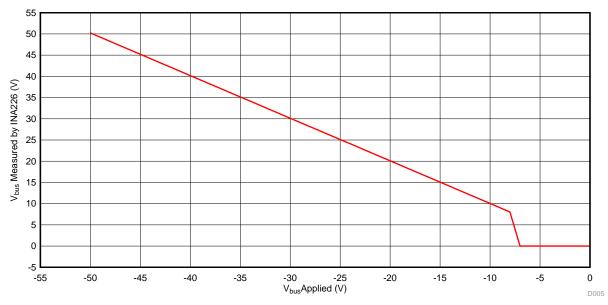

The targeted bus voltage for this reference design was -48 V. The results shown in Table 5 and Table 6 prove that, while using this TIDA-00313 board, the INA226 device is able to collect data at the -48-V rail. The  $V_{bus}$  range was verified by sweeping the bus voltage from 0 V to -50 V. Results showed that the INA226 is not able to collect data with  $V_{bus}$  values from 0 V to -7 V. At this voltage range, the potential generated by the voltage drop across the Zener diode is not enough to power the device. Using this TIDA-00313 board the INA226 device is able to measure bus voltage and shunt voltage when the  $V_{bus}$  is -8 V to -50 V, which Figure 21 shows.

Figure 21. V<sub>bus</sub> Range Accepted by TIDA-00313 Board

TEXAS INSTRUMENTS

www.ti.com

Design Files

## 4 Design Files

## 4.1 Schematics

To download the schematics, see the design files at TIDA-00313.

## 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00313.

## 4.3 PCB Layout Prints

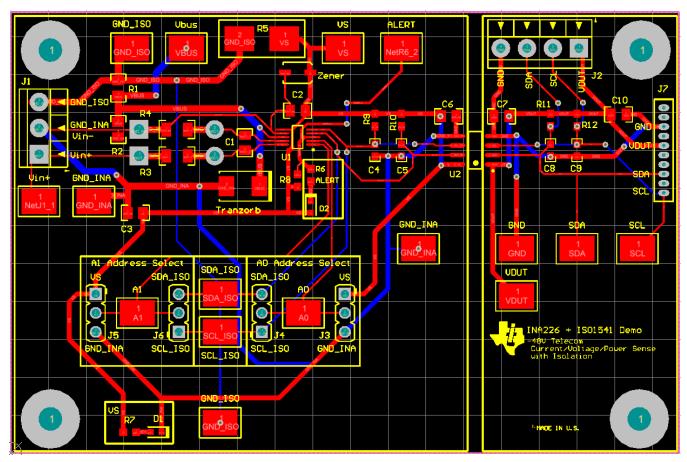

The two-layer printed circuit board (PCB) used in this design measures 3.54 in × 2.33 in. The PCB layout adheres to the following guidelines:

The input signal has a simple and clean path to the INA226, V<sub>in+</sub>, and V<sub>in-</sub> pins (see Figure 22). The terminal block J1 for the input current and power supply share a common ground (GND\_ISO) connection at the left side of the board. This shared connection shortens the path of the load current on the PCB.

Figure 22. INA226 Path for Input Pins

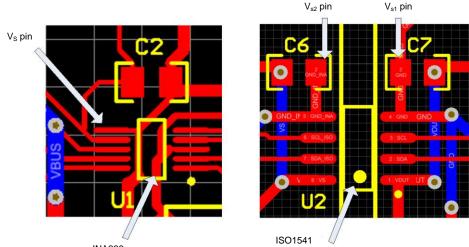

2. The power supply bypass capacitors are placed close to the supply pins of the device (see Figure 23).

INA226

Figure 23. Bypass Capacitors

The terminal block J7 has all the connections required for the SM-USB-DIG device and is located in close proximity to the ISO1541 SDA, SCL, V<sub>s</sub>, and GND low-voltage side pins. Some users may desire to use an alternate I<sup>2</sup>C interface communication and supply voltage. For this purpose, another block terminal, J2, has been placed near the ISO1541 low-voltage side pins.

22 –48-V Telecom Current, Voltage, and Power Sense With Isolation Reference TIDU361A–September 2014–Revised October 2017 Design Submit Documentation Feedback

4. The board should have two ground sides: one ground side for the high-voltage connections (-48 V) and the other side for the USB DIG low-voltage connections. The board has been divided in two sections and marked with silkscreen boundaries (see Figure 24).

Figure 24. PCB Layout

To download the layer plots, see the design files at TIDA-00313.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-00313.

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00313.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00313.

**Related Documentation**

#### 5 **Related Documentation**

- 1. EETimes.com, Semig, Peter; Wells, Collin; A Current Sensing Tutorial Parts 1-4, Design How-To (http://www.eetimes.com/design/industrial-control)

- 2. Texas Instruments, INA226 High-Side or Low-Side Measurement, Bi-Directional Current and Power Monitor with I<sup>2</sup>C Compatible Interface, INA226 Data Sheet (SBOS547)

- 3. Texas Instruments, SM-USB-DIG-Platform, User's Guide (SBOU098)

- 4. Texas Instruments, INA226EVM Evaluation Board and Software Tutorial, INA226EVM User's Guide (SBOU113)

- 5. Texas Instruments, ISO154x Low-Power Bidirectional PC Isolators, ISO154x Data Sheet (SLLSEB6)

- 6. Texas Instruments, Power: Telecom DC/DC Module: Analog, TI Applications Page

- 7. Texas Instruments, Getting Started with Current Sense Amplifiers, TI Current Sense Amplifier Video **Training Series**

#### 5.1 Trademarks

TINA-TI is a trademark of Texas Instruments.

#### 6 About the Author

MAYRIM VERDEJO is an applications engineer at Texas Instruments where she supports current shunt monitors and temperature sensors. Mayrim graduated from the University of Puerto Rico, Mayagüez where she earned a Bachelor of Science in Electrical Engineering with emphasis on Digital Signal Processing.

#### 7 Acknowledgments

The author wishes to acknowledge Scott Hills and Ed Mullins for their ideas, support, and assistance with this reference design.

TEXAS INSTRUMENTS

www.ti.com

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Original (September 2014) to A Revision

Page

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated