Design Guide: TIDA-020014

# HEV/EV Traction Inverter Power Stage With 3 Types of IGBT/SiC Bias-Supply Solutions Reference Design

# **Description**

This reference design presents a traction inverter single-phase power stage with three 12-V car battery inputs, 4.2-W bias supply solutions for hybrid electric vehicle and electric vehicle (HEV/EV) systems. All bias-supply solutions accept a wide input range of 4.5 V to 42 V DC from a 12-V car battery, and generate outputs as +15 V, -8 V or +20 V, -4 V configurable and up to 180-mA output current. The power stage includes the isolated gate drivers with 5.7-kV<sub>RMS</sub> reinforced isolation and designed in 100-mm x 62-mm form factor fitting on SiC/IGBT half bridge modules. It includes isolated DC bus sensing, isolated temperature sensing, logic shoot-through protection and diagnostic features. Apart from startup, efficiency, load regulation tests under low voltage input, all bias supplies are also connected with power stage and IGBT module for CMTI, double pulse, and short-circuit tests under high voltages.

### Resources

| TIDA-020014            | Design Folder  |

|------------------------|----------------|

| TIDA-020015            | Design Folder  |

| LM5180-Q1              | Product Folder |

| TPS40210-Q1            | Product Folder |

| LM46002-Q1             | Product Folder |

| SN6505B-Q1             | Product Folder |

| ISO5852S-Q1            | Product Folder |

| AMC1311-Q1, AMC1301-Q1 | Product Folder |

|                        |                |

ASK Our E2E™ Experts

### **Features**

- Traction-inverter, single-phase, power-stage design includes dual-channel isolated gate driver, isolated DC bus voltage sensing, and isolated temperature sensing.

- Three types of SiC/IGBT bias-supply solutions for IGBT/SiC isolated gate drivers

- Wide-V<sub>IN</sub> converters over the input voltage of 4.5-V to 42-V DC

- Output configurable as +15 V, -8 V or +20 V, -4 V at loads up to 180 mA for driving Si IGBT and SiC MOSFET modules

- Protection for clamping high-voltage conducted transients to safe levels for downstream circuitry

- Primary-side regulation with no optocoupler for extended lifetime and small form factor

### **Applications**

- Inverter and motor control

- Onboard (OBC) and wireless charger

- Gasoline and diesel engine platform

- DC/DC converter

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

This reference design presents an HEV, EV traction inverter, single-phase power-stage with three biassupply solutions. The supply solutions power a single channel of the IGBT/SiC isolated gate driver, and could be driven directly from the 12-V car battery with a wide input range of 4.5-V to 42-V DC. The bias supplies provide +15-V and -8-V isolated rails up to 180-mA output current. The architecture follows:

- Bias supply solution 1: Compact, primary-side regulated (PSR) flyback converter (based on the LM5180-Q1 device) with integrated switch and internal compensation.

- Bias supply solution 2: Low-cost, primary-side regulated (PSR) flyback converter (based on the TPS40210-Q1 device) with external switch and external compensation.

- Bias supply solution 3: Two stage approach of using two buck converters in redundancy as the front stage, and a push-pull transformer driver supply as the following stage (based on the LM46002-Q1 and SN6505-Q1 devices).

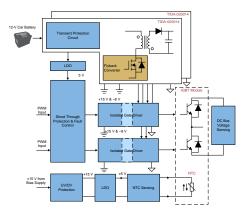

This design targets at powering IGBT/SiC isolated gate drivers implemented in hybrid electric vehicle and electric vehicle (HEV/EV) systems. Figure 1 shows a traction inverter reference diagram where the positions of the TIDA-020014 design are highlighted. The isolated gate drivers galvanically isolate the high-voltage power switches from the low-voltage control signals. Each isolated gate driver requires a pair of positive-supply and negative-supply rails to fully turn on and off the IGBT/SIC power modules.

www.ti.com System Description

Galvanic Isolation DC/DC Reverse High Voltage DC/DC Polarity Protection Non-Isolated DC/DC Power Supplies Isolated Bias Supply Input Power Protection Loads Bias 12 V Supply DC/DC Isolated Bias Supply Power Stage Driver DC/DC S O Half Μ Bridge SENSE Diagnostics LDOs Pos. HS Power Stage Power Management (PMIC) CAN PWM ISO Safet & Glue Logic **GPIOs** MCU Core ADC Current and Voltage Sense Digital Processing Sensors (V,T,I %..) ADC Position Sensing S VRFF Rotor Position Sensing Self Diagnostics/Monitoring Signal Isolation

Figure 1. HEV/EV Traction Inverter Reference Block Diagram and the Position of TIDA-020014

Do not leave the device powered when unattended.

High voltage! There are accessible high voltages present on the board. Electric shock is possible. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled. Use the equipment with necessary caution and appropriate safeguards to avoid injury or damage to property. For safety, use of isolated equipment with overvoltage and overcurrent is highly recommended. TI considers it the user's responsibility to confirm that the voltages and isolation requirements are identified and understood before energizing the board or simulation. When energized, do not touch the design or components connected to the design.

Hot surface! Contact may cause burns. Do not touch! Some components may reach high temperatures > 55°C when the board is powered on. The user must not touch the board at any point during operation or immediately after operating, as high temperatures may be present.

System Description www.ti.com

# 1.1 Key System Specifications

Table 1 details the key system specifications of the bias supplies.

**Table 1. Key System Specifications**

| PARAMETER        |                     | COMMENTS                                                                                                                                                         | MIN  | TYP  | MAX  | UNIT |

|------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| System Inp       | out                 |                                                                                                                                                                  |      |      |      | !    |

| V <sub>IN</sub>  | Input voltage       | Battery voltage range (DC)                                                                                                                                       | 4.5  | 13.5 | 42   | V    |

| F <sub>sw</sub>  | Switching frequency | Solution 1                                                                                                                                                       | 10   | 350  | 350  | kHz  |

| F <sub>sw</sub>  | Switching frequency | Solution 2                                                                                                                                                       |      | 100  |      | kHz  |

| F <sub>sw</sub>  | Switching frequency | Solution 3                                                                                                                                                       |      | 450  |      | kHz  |

| Output Volt      | tage                |                                                                                                                                                                  |      |      | •    | •    |

|                  | V <sub>OUT1</sub>   | System output voltage, across load                                                                                                                               | +13  | +15  | +17  | V    |

|                  | V <sub>OUT2</sub>   | System output voltage, across load                                                                                                                               | -6.5 | -8   | -8.2 | V    |

| Output Cur       | rent                |                                                                                                                                                                  |      |      | 1    |      |

| І <sub>оит</sub> |                     | Maximum output current. Drawing more than 180 mA is not recommended for thermal reasons. See the Thermal Images testing to see the temperature rise at full load |      | 180  |      | mA   |

# 2 System Overview

# 2.1 Block Diagram

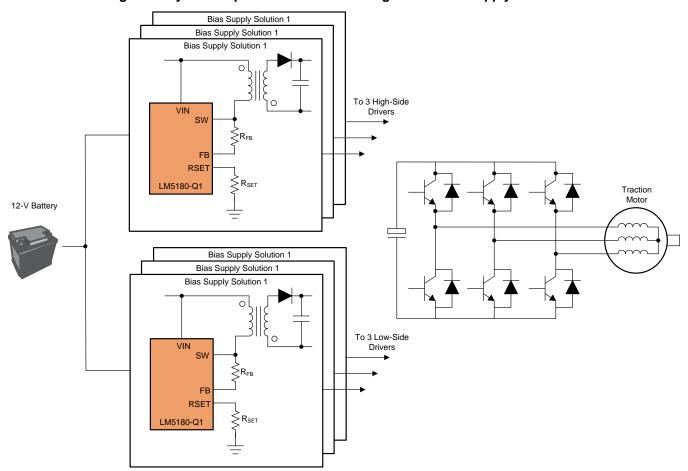

## 2.1.1 Bias Supply Solution 1

Figure 2 shows the system implementation block diagram of the bias supply solution 1. The three-phase traction inverter requires six IGBT/SiC switches through isolated gate drivers that galvanically isolate the high-voltage gate driver outputs from the low-voltage PWM signals. Hence six times of this design are required to power all six gate drivers: each power supply is connected to each and every gate driver, respectively. The input can be fed directly from a 12-V car battery. The output voltage levels can be configured to the required voltage levels for driving IGBT or SiC MOSFETs.

Figure 2. System Implementation Block Diagram of Bias Supply Solution 1

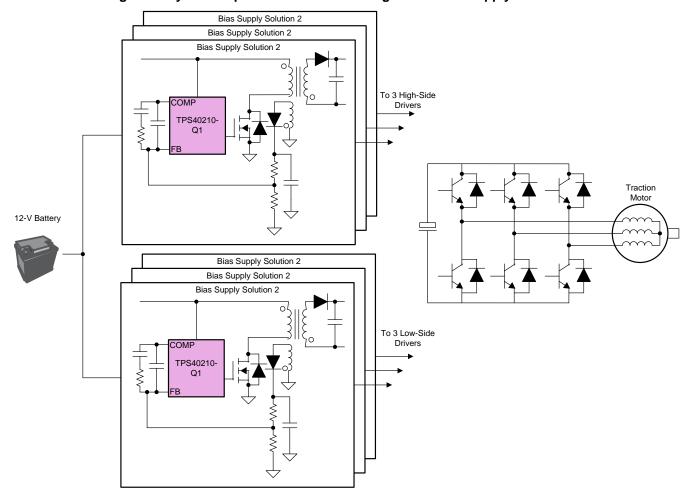

# 2.1.2 Bias Supply Solution 2

Figure 3 shows the system implementation block diagram of the bias supply solution 2. A flyback converter with an external MOSFET and compensation network has been used. The same traction inverter block diagram is shown.

Figure 3. System Implementation Block Diagram of Bias Supply Solution 2

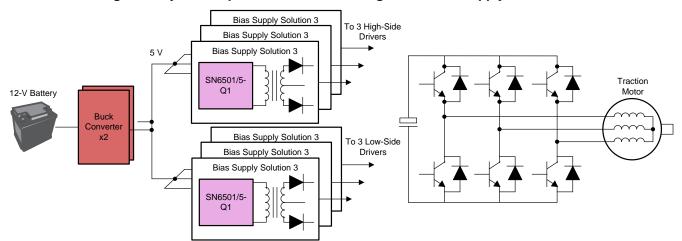

# 2.1.3 Bias Supply Solution 3

Figure 4 shows the system implementation block diagram of the bias supply solution 3 which is the two-stage architecture in redundancy for an increased level of safety. Two buck converters are connected in parallel and convert the 12-V battery input to 5-V output. Then the 5-V rail is fed into the push-pull transformer driver supply where the isolation is provided. The same traction inverter block diagram is shown.

Figure 4. System Implementation Block Diagram of Bias Supply Solution 3

# 2.1.4 Inverter Power Stage Block Diagram

The power stage board is designed in a compact form factor. It includes gate drive, bias voltages, protection, and diagnostic needed for half-bridge SiC MOSFET and Si IGBT power modules housed in 150-mm × 62-mm × 17-mm packages. It consists of the high-side and low-side isolated gate drivers, the DC bus voltage sensing, the shoot-through protection and fault control, the high voltage input LDO, and the NTC sensing circuit. The connectors allow for plug-in connection to the gate drivers for easy evaluation. Figure 5 shows the power stage board block diagram. The features are listed as follows:

- 20-A peak split sink and source drive current from external buffer to optimize turn on and turn off switching time

- Robust noise-immune solution with CMTI >100 V/ns

- Supports 5 kV<sub>RMS</sub> reinforced isolation for input rail up to 1700 V

- · Programmable short-circuit sensing and soft turn-off protection with the de-saturation circuit

- 2-A active Miller clamp

- Output short-circuit clamp

- · Fault feedback with reset

- NTC temperature and DC bus voltage sensing

TIDA-020014 TIDA-020014 12-V Car Battery **Transient Protection** Circuit LDO Flyback Converter 5 V IGBT Module +15 V & -8 V **PWM** Input Isolated Gate Driver Shoot Through DC Bus Protection & Fault Control Voltage Sensing +15 V & -8 V PWM Input Isolated Gate Driver NTC +5 V -15 V +15 V from Bias Supply UV/OV LDO **NTC Sensing** Protection

Figure 5. TIDA-020014 Power Stage Block Diagram

# 2.2 Highlighted Products

The TIDA-020014 reference design features the following Texas Instruments devices.

### 2.2.1 LM5180-Q1

The LM5180-Q1 device is a primary-side regulated (PSR) flyback converter with high efficiency over a wide input voltage range of 4.5 V to 65 V. The isolated output voltage is sampled from the primary-side flyback voltage, eliminating the need for an optocoupler, voltage reference, or third winding from the transformer for output voltage regulation. The high level of integration results is a simple, reliable and high-density design with only one component crossing the isolation barrier. Boundary conduction mode (BCM) switching enables a compact magnetic solution and better than ±1% load regulation and line regulation performance. An integrated 100-V power MOSFET provides output power up to 7 W with enhanced headroom for line transients.

### 2.2.2 TPS40210-Q1

The TPS40210-Q1 is a peak current-mode control low-side controller with a built in 400-mA gate driver designed to drive N-channel MOSFETs at a fixed frequency. The frequency is adjustable from 35 kHz to 1000 kHz. A small size combined with complete functionality makes the part both versatile and easy to use. The controller uses a low-value current-sensing resistor in series with the source connection of the power MOSFET to detect switching current. When the voltage drop across this resistor exceeds 150 mV, the part enters a hiccup fault mode with a time period set by the external soft-start capacitor.

### 2.2.3 LM74700-Q1

The LM74700-Q1 device is an ideal diode controller device that operates in conjunction with an external N-channel MOSFET as an ideal diode rectifier for low loss reverse polarity protection. The wide supply input range of 3 to 65 V allows control of many popular DC bus voltages. The device can withstand and protect the loads from negative supply voltages down to -65 V. With a low  $R_{\rm DS(on)}$  external N-channel MOSFET, a very low forward voltage drop can be achieved while minimizing the amount of power dissipated in the MOSFET.

### 2.2.4 TPS3700-Q1

The TPS3700-Q1 device is a wide-supply voltage window comparator which operates over a 1.8-V to 18-V range. The device has two high-accuracy comparators with an internal 400-mV reference and two opendrain outputs rated to 18 V for overvoltage and undervoltage detection. The TPS3700-Q1 device can be used as a window comparator or as two independent voltage monitors; the monitored voltage can be set with the use of external resistors.

### 2.2.5 LM46002-Q1

The LM46002 regulator is an easy to use synchronous step-down DC/DC converter that operates from 3.5-V to 60-V supply voltage. It is capable of delivering up to 2 A DC load current with exceptional efficiency and thermal performance in a very small solution size. An extended family is available in 0.5-A and 1.0-A load options in pin-to-pin compatible packages.

Optional features are included for more comprehensive system requirements, including power-good flag, precision enable, and synchronization to external clock, extendable soft-start time, and output voltage tracking. These features provide a flexible and easy to use platform for a wide range of applications. Protection features include over temperature shutdown, VCC undervoltage lockout (UVLO), cycle-by-cycle current limit, and short-circuit protection with hiccup mode.

### 2.2.6 SN6505-Q1

The SN6505-Q1 device is a monolithic push-pull transformer driver, specifically designed for small factor, isolated power supplies. It drives a low profile, center-tapped transformer from a 3.3-V or 5-V DC power supply. The SN6505x-Q1 consists of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive ground referenced N-channel power switches. The device includes two 1-A Power-MOSFET switches to ensure start-up under heavy loads. The internal protection features include a 1.7-A current limiting, under-voltage lockout, thermal shutdown, and break-before-make circuitry.

### 2.2.7 TL431-Q1

The TL431-Q1 device is a three-pin adjustable shunt regulator with specified thermal stability over applicable automotive temperature ranges. The TL431-Q1 can be used as a single voltage reference, error amplifier, voltage clamp, or comparator with integrated reference. The TL431-Q1 consists of an internal reference and amplifier that outputs a sink current based on the difference between the reference pin and the virtual internal pin. The sink current is produced by the internal Darlington pair, which allows this device to sink a maximum current of 100 mA.

### 2.2.8 ISO5852S-Q1

The ISO5852S-Q1 device is a reinforced, isolated gate driver that is capable of driving a 1200-V IGBT module with current ratings from 50 A to 200 A. The device offers:

- High isolation ratings in the industry

- 5.7-kV<sub>RMS</sub> isolation voltage

- 8000-Vpk Maximum transient isolation voltage

- 2121-Vpk Maximum transient isolation voltage

- Split outputs

- 2.5-A Peak source and 5-A peak sink currents

- 100-kV/μs Minimum common-mode transient

The device also includes the Miller clamp, soft turnoff, UVLO, DESAT detect, fault feedback, and Ready-status feedback features.

### 2.2.9 AMC1301-Q1

The AMC1301 is a fully-differential, precision, isolated amplifier. The input stage of the device consists of a fully-differential amplifier that drives a second-order, delta-sigma ( $\Delta\Sigma$ ) modulator. The modulator uses the internal voltage reference and clock generator to convert the analog input signal to a digital bit stream. The drivers transfer the output of the modulator across the isolation barrier that separates the high-side and low-side voltage domains.

### 2.2.10 AMC1311-Q1

The AMC1311-Q1 is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 7 kV peak according to VDE V 0884-11 and UL1577. Used in conjunction with isolated power supplies, this isolated amplifier separates parts of the system that operate on different common-mode voltage levels and protects lower-voltage parts from damage. The high-impedance input of the AMC1311-Q1 is optimized for connection to high-voltage resistive dividers or other voltage signal sources with high output resistance.

### 2.2.11 TPS7B8250-Q1

The TPS7B82-Q1 device is a  $40\text{-V}_{\text{IN}}$ , 300-mA low-dropout linear regulator with ultra-low quiescent current. This voltage regulator consumes only 3  $\mu\text{A}$  of quiescent current at light load, and is quite suitable for the automotive always on application. The device operates with a wide input-voltage range from 3 V to 40 V (45-V load dump protection).

# 2.3 System Design Theory

### 2.3.1 Reverse Polarity Protection

Reverse battery protection is required in every electronic subsystem of a vehicle, both by OEM standards, as well as ISO 16750-2, an international standard pertaining to supply quality. The goal is to prevent reverse-biasing components which are sensitive to polarity, like polarized capacitors and most integrated circuits.

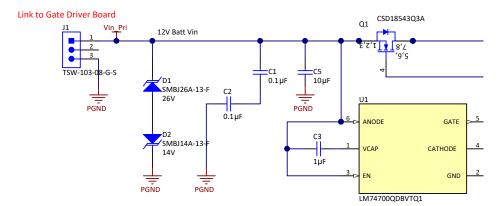

Figure 6 shows the reverse polarity protection circuit schematic. It consists of a N-channel MOSFET (Q3) which is driven by the LM74700-Q1 smart diode controller. The traditional method which implements blocking diode results in large power dissipation due to the typical 400–700 mV forward-voltage drop. The smart diode solution decreases the losses as per the R<sub>DS(on)</sub> of the MOSFET. The LM74700-Q1 controller provides a gate drive for an external N-Channel MOSFET and a fast response internal comparator to discharge the MOSFET Gate in the event of reverse polarity. A unique advantage of this scheme is that it is not referenced to ground and thus has zero I<sub>Q</sub>. The N channel MOSFET is selected according to the following criteria:

- Continuous current rating higher than 10 A which is the maximum input current at minimum input voltage in this design.

- The VGS threshold should be 2.5-V maximum

- Source-to-drain voltage V<sub>SD</sub> should be at least 0.48 V at 2 A

Figure 6. Reverse Polarity Protection Circuit Schematic

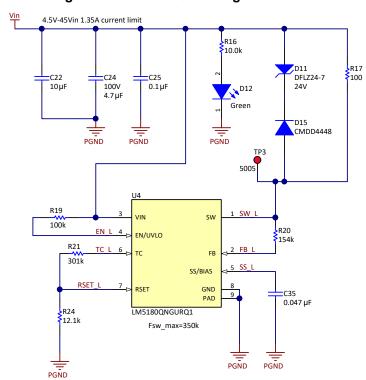

# 2.3.2 LM5180-Q1 Flyback Converter

The bias supply solution 1 is the flyback converter based on the LM5180-Q1 device which has integrated MOSFET and internal compensation. The converter provides isolated output voltages with tight regulation crossing load. The design specifications are shown in Table 2. Highlights of the converter are summarized as:

- Boundary conduction mode (BCM) control architecture provides fast line and load transient response

- Peak current-mode control

- Quasi-resonant switching for reduced power loss

- Internal loop compensation

- Integrated 100-V flyback power MOSFET

- Provides large headroom for input voltage transients

- Cycle-by-cycle overcurrent protection (OCP)

- Low transformer primary-to-secondary (inter-winding) capacitance to accommodate high dv/dt secondary-side common-mode swings.

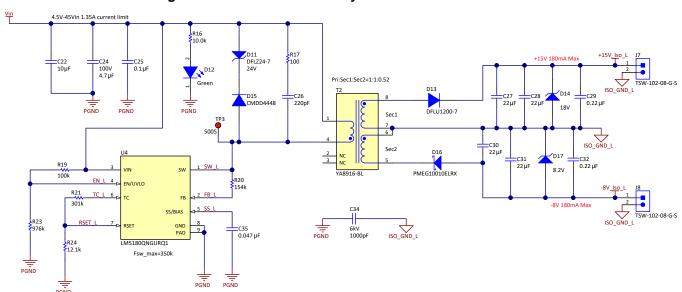

Figure 7 shows the schematic of the converter.

Table 2. LM5180-Q1 Based Flyback Converter Specifications

| PARAMETER                                      | SPECIFICATION                                                                      |

|------------------------------------------------|------------------------------------------------------------------------------------|

| Input voltage (V <sub>in</sub> )               | 4.5 V-65 V DC (For flyback converter only, TVS limits the system input to 26 V DC) |

| Output voltage (V <sub>OUT</sub> )             | +15 V, –9 V                                                                        |

| Output ripple                                  | ±3%                                                                                |

| Maximum output current (I <sub>out_max</sub> ) | 180 mA                                                                             |

| Switching frequency                            | < 350 kHz                                                                          |

| Output power (P <sub>out_max</sub> )           | 4.14 W                                                                             |

| Efficiency                                     | > 90% peak, 88% at full load                                                       |

Figure 7. LM5180-Q1 Based Flyback Converter Schematic

### 2.3.2.1 Modes of Operation and Switching Frequency

The LM5180-Q1 device uses a variable-frequency, peak current-mode (VFPCM) control architecture with three possible modes of operation as Figure 8 illustrates.

Figure 8. Operation Mode of the LM5180-Q1 Flyback Converter

At high loads, the LM5180-Q1 device operates in Quasi-Resonant Boundary Conduction Mode. The power MOSFET turns on when the current in the secondary winding reaches zero. The MOSFET turns off when the peak primary current reaches the level dictated by the output of the internal error amplifier. As the load is decreased, the peak current decreases and the frequency increases to maintain BCM operation.

# 2.3.2.2 Transformer Design

Key parameters to design the transformer include turns ratio, primary side inductance, switching frequency, saturation current, and so forth.

If ignoring the drop voltage across the switching MOSFET the winding turns ratio is calculated as:

$$V_{IN\_Min} \times T_{on} = (V_{OUT} + V_{D}) \times T_{off} \times N_{PS}$$

#### where

- V<sub>IN- Min</sub> is the minimum input voltage

- T<sub>op</sub> is the switch-on time of the switching MOSFET

- T<sub>off</sub> is the off time of the switching MOSFET

- N<sub>PS</sub> is the turns ratio of the transformer

- V<sub>D</sub> is the output rectification diode

### Considering

$$D = \frac{T_{on}}{T_{on} + T_{off}}$$

is the duty cycle, and choosing the maximum duty cycle 75% at minimum input voltage, the turns ratio of the transformer primary winding to the secondary winding is calculated as:

$$N_{PS} = \frac{V_{IN\_MIn}}{V_{OUT} + V_D} \times \frac{D}{1 - D} = 0.65$$

(2)

Select a magnetizing inductance based on the minimum off-time constraint according to:

$$L_{MAG} \!\! \geq \!\! \tfrac{(V_{OUT} + V_D) \times N_{PS} \times t_{OFF\_MIN}}{I_{PRI\_PK}} \!\! = 26.5~\mu H$$

### where

- V<sub>D</sub> is the forward drop voltage of the output rectification diode

- I<sub>PRL\_PK</sub> is the primary winding current when converter operates in frequency fold back mode (1.5 A according to the data sheet)

The built-in MOSFET of the LM5180-Q1 device is rated at 100 V. In the off cycle, when the secondary (flyback) diode is on, the voltage on the drain ( $V_{DS}$ ) is calculated as:

$$V_{DS} = V_{IN(MAX)} + V_{RFF} + V_{RING} = 82 \text{ V}$$

### where

- V<sub>IN(MAX)</sub> is the maximum input voltage

- V<sub>REF</sub> is the voltage reflected from the secondary side

- V<sub>RING</sub> is the excited spike due to resonance

The voltage across the secondary side diode is calculated as:

$$V_{Diode} = V_{OUT} + \frac{V_{IN(MAX)}}{N_{PS}} + V_{SPIKE} = 112 V$$

### where

- V<sub>OUT</sub> is the maximum output voltage

- V<sub>SPIKE</sub> is the excited spike due to resonance

The inductance of the transformer primarily determines the modes of operation in the LM5180-Q1 as the load is varied from the minimum load to full load. An increase in the magnetic inductance generally leads to an increase in the leakage inductance of the transformer. The LM5180-Q1 device has a minimum off-time  $(T_{OFF(MIN)})$  of 500 ns: the magnetizing current should not decrease to zero in less than 500 ns. Therefore the minimum primary side inductance is calculated as:

$$L_{PRI} \geq \frac{\left(V_{out} + V_{FWD}\right) \times T_{OFF\left(MIN\right)} \times N_{PS}^2}{I_{PRI\_MIN} \times N_{PS}} = 30 \quad \mu H$$

### where

- V<sub>OUT</sub> is the nominal output voltage which is 24 V

- T<sub>OFF(MIN)</sub> is the minimum off time of LM5180-Q1

- I<sub>PRI MIN</sub> is the minimum peak current flowing at primary side for the LM5180-Q1 device which is 0.27 A

- N<sub>PS</sub> is the primary to secondary turns ratio

(6)

Thus, the designed transformer should have the minimum primary inductance of 30 µH. Table 3 lists the specifications of the designed flyback transformer.

(5)

| PARAMETER     |                         | SPECIFICATION                            |

|---------------|-------------------------|------------------------------------------|

| Power rating  |                         | 4.2 W                                    |

| Input v       | /oltage                 | 4.5 V-65 V                               |

|               | utput current<br>_max)  | 180 mA                                   |

| Switching     | frequency               | < 300 kHz                                |

| Maximum       | duty cycle              | 75%                                      |

| Primary side  | e inductance            | 30 μH ±10% at 300 kHz                    |

| Leakage i     | nductance               | < 1% of primary inductance               |

|               | apacitance<br>secondary | < 20 pF                                  |

| Output voltag | e and current           | +15 V and -9 V at 180-mA average current |

| Turns         | s ratio                 | 1:1:0.52                                 |

| Peak current  | Primary                 | 1.45 A                                   |

|               | Secondary               | 1 A                                      |

| RMS current   | Primary                 | 1.1 A                                    |

|               | Secondary               | 380 mA                                   |

TI recommends the flyback transformer UA8916-BL from CoilCraft® for the LM5180-Q1-based flyback converter. The transformer features parasitic capacitance of 17 pF from the primary to secondary side.

#### 2.3.2.3 Input Capacitors

The input capacitor must supply the input current during the input voltage dip from the 12-V battery. Input capacitors are essential in limiting the ripple voltage while supplying most of the switch current during the MOSFET switch on-time.

The input capacitance is calculated as:

$$C_{in} = \frac{I_{pri\_pk} \times D_{on}}{F_{SW} \times \Delta V_{ripple}} = \frac{1.45 \text{ A} \times 0.75}{300 \text{ k} \times 4.5 \text{ V} \times 3\%} = 26.8 \text{ } \mu\text{F} \tag{7}$$

#### 2.3.2.4 **Output Capacitors**

The output capacitance ensures the converter has a small transient deviation to a step change of the load transient. The minimum needed capacitance is calculated as to maintain the output voltage drop less than 3% of the nominal voltage when the output current changes abruptly from the maximum to half (I<sub>step</sub>):

$$I_{\text{step}} = \frac{I_{\text{out}}}{2} = \frac{180 \text{ mA}}{2} = 90 \text{ mA}$$

(8)

$$V_{drop} = V_{out} \times 3\% = 24 \quad V \times 1\% = 0.24 \quad V$$

(9)

As any forward converters, the Right-Half-Plan-Zero (RHPZ) limits the bandwidth of the flyback. The frequency of the RHPZ is calculated as:

$$f_{RHPZ} = rac{R_{OUT} imes (V_{in} / V_{out})^2}{L_{PRI} imes 2\pi} = 24$$

.8 kHz

where

- R<sub>OUT</sub> is the load impedance

- L<sub>PRI</sub> is the primary inductance of the transformer

The bandwidth of the system is estimated as 1/5 of the RHPZ:

$$f_{bandwidth} = \frac{1}{5} \times f_{RHPZ} = \frac{1}{5} \times 24.8 \text{ kHz} = 4.96 \text{ kHz}$$

(11)

As the result, the output capacitance at bandwidth frequency is calculated as:

$$C_{out\_min} = \frac{1}{2 \times \pi \times f_{bandwidth}} \times \frac{1}{\Delta V_{out} / \Delta I_{loadstep} - ESR_{out}} = 12 \quad \mu F$$

(12)

Therefore a minimum of 12-µF capacitance is required for this design.

(10)

# 2.3.2.5 RC Snubber Design

When the MOSFET turns off, a high-voltage spike occurs at the drain (switch node) because of the resonances between the leakage inductor of the main transformer and the parasitic capacitance in the circuit. This causes excessive voltage on the drain of the MOSFET which can lead to breakdown and eventually failure of the device. The parasitic capacitance is composed of 3 components: (1) output capacitance of the MOSFET, (2) junction capacitance of the output diode which reflects to the primary side, (3) parasitic capacitance of the transformer winding.

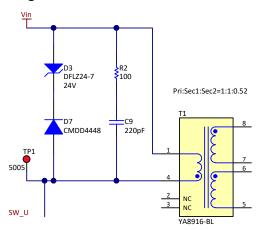

The transformer used in this design has relatively less leakage inductance. A Zener clamp is used in this reference design as Figure 9 shows, due to ease-of-design and higher light load efficiency than the RCD snubber.

Figure 9. Snubber Circuit Schematic

The power dissipated in the snubber can be calculated as:

$$\mathsf{P}_{\mathsf{sub}} \! = rac{1/2\! imes\!\mathsf{L}_{\mathsf{LK}}\! imes\!\mathsf{I}_{\mathsf{PK}}^2\! imes\!\mathsf{F}_{\mathsf{SW}}}{1\!-\!\mathsf{V}_{\mathsf{FBK}}/\mathsf{V}_{\mathsf{Ze}}}$$

where

- L<sub>Ik</sub> is the leakage inductance of the transformer

- I<sub>PK</sub> is the primary peak current

- F<sub>sw</sub> is the switching frequency

- The Zener diode is selected as 24 V

### 2.3.2.6 Verification on Input Voltage Range

The LM5180-Q1 device integrates a 100-V power MOSFET with maximum current of 1.5 A. The maximum drain-to-source voltage ( $V_{ds\_max}$ ) is calculated as:

$$V_{ds\_max} = n \times \frac{N_p}{N_L} \times (V_{out} + V_f) + V_{in\_max} = 102.5 \text{ V}$$

where

- n is the safe margin which is normally 1.5 or 2 times of the nominal value.

- $N_r/N_s$  is the turn ratio of the transformer primary winding to the secondary winding.

- V<sub>OUT</sub> is the output voltage

- V<sub>f</sub> is the forward voltage of the output diode

Therefore, the selected MOSFET breaking voltage must be larger than 102.5 V.

(13)

### 2.3.2.7 LM5180-Q1 Settings

Figure 10 shows the schematic with components surrounding the LM5180-Q1 device. The UVLO is connected to  $V_{IN}$  directly for the lowest undervoltage lockout. With the designed turns ratio of the transformer and forward voltage of the secondary diode, the ratio between R20 ( $R_{FB}$ ) and R24 ( $R_{RST}$ ) determines the output voltage. R24 ( $R_{RST}$ ) is selected as 12.1 k $\Omega$  according to the data sheet. The output voltage is 24 V, the forward voltage drop of the secondary diode is 0.7 V.  $R_{FB}$  is calculated as:

$$R_{FB} = \frac{(V_{OUT} + V_{FD}) \times N_{PS}}{0.1 \text{ mA}} = 154 \text{ k}\Omega$$

(15)

The LM5180-Q1 device employs a thermal-compensation circuit that adjusts the feedback reference based on the forward voltage thermal coefficient of the flyback diode. The thermal compensation resistor value is determined by R21 ( $R_{TC}$ ) which is calculated as:

$$R_{TC}\!=\frac{R_{FB}}{N_{PS}}$$

×  $\frac{3~mV/\,^{\circ}C}{TC_{Diode}}\!=301~k\Omega$

where

TC<sub>Diode</sub> is the absolute value of the temperature coefficient of the flyback diode

Figure 10. LM5180-Q1 Settings Schematic

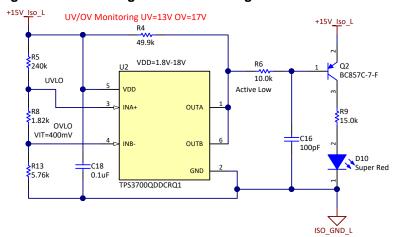

### 2.3.3 Overvoltage and Undervoltage Detection

The IGBT gate is driven from the 15-V rail to turn on the IGBT. The 15-V rail should not drop below the minimum gate voltage to properly turn on the IGBT. Driving the IGBT with lower gate voltage causes excessive power dissipation. Conversely, excessive higher gate voltage will destroy the IGBT.

The overvoltage and undervoltage detection is designed with the window comparator TPS3700-Q1. It has two high-accuracy comparators with an internal 400-mV reference and two open-drain outputs. Figure 11 shows the schematic of the detection circuit. The INA+ / INB- implements open-drain output. OUTA is driven low when the voltage at INA+ is below ( $V_{\text{ITP}} - V_{\text{HYS}}$ ) (according to the TPS3700-Q1 data sheet). The output goes high when the sense voltage returns above the respective threshold. OUTB is driven low when the voltage at this comparator exceeds  $V_{\text{ITP}}$ . The output goes high when the sense voltage returns

below the respective threshold. The undervoltage threshold is set as 13 V, and the overvoltage threshold is set as 17 V for this design. The OR logic is implemented by connecting the two open-drain outputs of the TPS3700-Q1 device. OUTA and OUTB can merge into one logic signal that goes low if either output is asserted. The 49.9-k $\Omega$  pullup resistor is used to hold these lines high when the output goes to high impedance.

Figure 11. Overvoltage and Undervoltage Detection Schematic

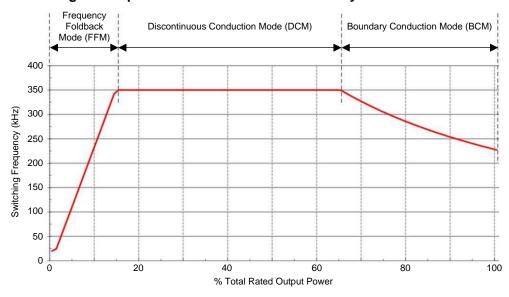

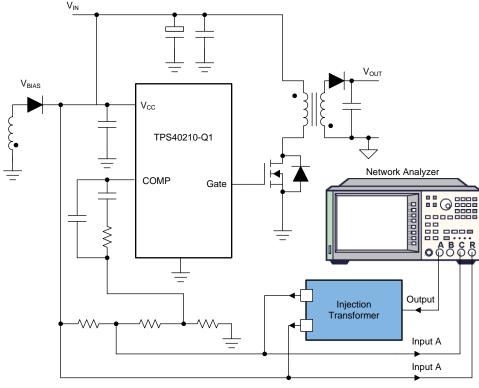

### 2.3.4 TPS40210-Q1 Flyback Converter

The bias supply solution 2 is the flyback converter based on the TPS40210-Q1 device which implements external MOSFET and primary side regulation. The procedure and calculations for designing the flyback converter are discussed in this section. Table 4 lists the design specification.

| PARAMETER                                      | SPECIFICATION                |

|------------------------------------------------|------------------------------|

| Input voltage (V <sub>IN</sub> )               | 5 V-42 V DC (52-V transient) |

| Output voltage (V <sub>OUT</sub> )             | +15 V, –9 V                  |

| Output ripple                                  | ±3%                          |

| Maximum output current (I <sub>out_max</sub> ) | 180 mA                       |

| Switching frequency                            | 100 kHz                      |

| Output power (P <sub>out_max</sub> )           | 4.14 W                       |

| Efficiency                                     | > 81% peak, 80% at full load |

Table 4. TPS40210-Q1 Based Flyback Converter Specifications

Figure 12. TPS40210-Q1 Flyback Converter Schematic

## 2.3.4.1 Switching Frequency

The oscillator frequency is determined by a resistor and capacitor connected to the RC pin of TPS40210-Q1 device. A switching frequency of 100 kHz is selected as a compromise between component size, EMI, and efficiency. The required resistor for a given oscillator frequency is calculated from:

$$R_T \!\!=\! \frac{1}{5.8 \times 10^{-8} \times F_{SW} \times C_T + 8 \times 10^{-10} \times F_{SW}^2 + 1.4 \times 10^{-7} \times F_{SW} - 1.5 \times 10^{-4} + 1.7 \times 10^{-6} \times C_T - 4 \times 10^{-9} \times C_T^2}$$

where

- $R_T$  is the timing resistance in  $k\Omega$

- F<sub>sw</sub> is the switching frequency in kHz

- $C_T$  is the timing capacitance in pF

$C_T$  and  $R_T$  are selected as 470 pF and 402 k $\Omega$ , respectively for the 100-kHz switching frequency.

# 2.3.4.2 Transformer Design

A transformer is one of the most important elements to ensure the flyback converter operates reliably and efficiently. A flyback transformer is used as an energy storage device. The energy is stored in the air-gap of the core. The flyback converter is designed for continuous-conduction mode. In comparison with the discontinuous mode, the advantages are lower peak currents, lower output voltage spikes, and lower core losses.

If ignoring the drop voltage across the switching MOSFET, and output rectification diode, the winding turns ratio is calculated as:

$$V_{IN\_Min} \times T_{on} = V_{OUT} \times T_{off} \times N_{PS}$$

where

- V<sub>IN Min</sub> is the minimum input voltage

- T<sub>on</sub> is the switch-on time of the switching MOSFET

- T<sub>off</sub> is the off time of the switching MOSFET

- N<sub>PS</sub> is the turn ratio between the primary turns and secondary turns of the transformer. (18)

Considering:

$$D = \frac{T_{on}}{T_{on} + T_{off}}$$

(17)

is the duty cycle, and choosing the maximum duty cycle as 70%. Therefore, the turn ratio of the transformer primary winding to the secondary winding is calculated as:

$$N_{PS} = \frac{V_{IN.Min}}{V_{OUT}} \times \frac{D}{1-D} = 0.49$$

(19)

Hence,  $N_{PS}$  is selected as 1:2. The actual duty cycle ( $D_{ON\ act}$ ) is calculated as:

$$D_{ON\_act} \!\!=\! \tfrac{(V_{out} \!+\! V_f) \times N_{PS}}{V_{IN\_min} \!+\! (V_{out} \!+\! V_f) \times N_{PS}} \!\!=\! 0.71$$

where

•  $V_t$  is the forward drop voltage of the output rectification diode (20)

The turn-off time duty cycle of the MOSFET is calculated as:

$$D_{OFF\_act} = 1 - D_{ON\_act} = 0.29$$

(21)

The average peak current ( $I_{\text{sec\_avgpk}}$ ) at the transformer secondary side is:

$$I_{\text{sec\_avgpk}} = I_{\text{sec\_avg}} / D_{\text{OFF\_act}} = 180 \text{ mA} / 0.29 = 620 \text{ mA}$$

(22)

The peak current at the transformer secondary side (I<sub>sec pk</sub>) is calculated as:

$$I_{\text{sec\_pk}} = \frac{2 \times I_{\text{sec\_avgpk}}}{2 - D_{\text{OFF\_act}}} = 0.73 \text{ A}$$

(23)

The average current flowing into the transformer secondary side is 180 mA. Therefore, the RMS current at the transformer secondary side ( $I_{\text{sec }rms}$ ) is calculated as:

$$I_{\text{sec\_rms}} = I_{\text{sec\_avgpk}} \times \sqrt{D_{\text{OFF\_act}}} = 0.39 \text{ A}$$

(24)

The average peak current (I<sub>pri\_avgpk</sub>) at the transformer primary side is calculated as:

$$I_{\text{pri}\_avgpk} = \frac{I_{\text{sec\_avgpk}}}{N_{\text{PS}}} = \frac{0.73 \text{ A}}{0.5} = 1.46 \text{ A}$$

(25)

The peak current at the transformer primary side (I<sub>pri pk</sub>) is calculated as:

$$I_{pri\_pk} = \frac{2^{x}I_{pri\_avgpk}}{2-D_{on\_act}} = \frac{2^{x}1.46 \text{ A}}{2-0.3} = 1.72 \text{ A}$$

(26)

The RMS current at the transformer primary side (I<sub>pri ms</sub>) is calculated as:

$$I_{pri\_rms} = I_{pri\_avgpk} \times \sqrt{D_{On\_act}} = 1.46 \times \sqrt{0.71} = 1.23 \text{ A}$$

(27)

The RMS current of the bias winding is selected as 50 mA according to the current limit of the internal regulator. The turn ratio of the transformer bias winding to the secondary winding is selected as 1:1 for better regulation. As the result, output voltage of the bias winding is Vbias =  $V_{OUT}$  = 24 V.

Table 7 details the specifications of the designed flyback transformer.

**Table 5. Flyback Transformer Specifications**

| PARAMETER                                      | SPECIFICATION                  |

|------------------------------------------------|--------------------------------|

| Qualification                                  | AEC-Q200 Grade 1 qualified     |

| Safety insulation                              | Reinforced                     |

| Power rating                                   | 4.2 W                          |

| Input voltage                                  | 4.5 V–42 V                     |

| Switching frequency                            | 100 kHz                        |

| Maximum output current (I <sub>out_max</sub> ) | 180 mA                         |

| Maximum duty cycle                             | 71%                            |

| Primary-side inductance                        | 35 μH ±10% at 100 kHz          |

| Leakage inductance                             | < 2% of primary inductance     |

| Parasitic capacitance primary to secondary     | < 20 pF                        |

| Output voltage and current                     | 24 V at 180 mA average current |

| Auxiliary winding output                       | 24 V at 50 mA                  |

| Turns ratio (Pri:Sec:Aux)                      | 1:2:2                          |

| PARAM        | METER     | SPECIFICATION |

|--------------|-----------|---------------|

| Peak current | Primary   | 1.72 A        |

|              | Secondary | 0.8 A         |

| RMS current  | Primary   | 1.2 A         |

|              | Secondary | 350 mA        |

Table 5. Flyback Transformer Specifications (continued)

TI recommends the automotive grade AEC-Q200 qualified flyback transformer YA9051-AL from CoilCraft for the TPS40210-Q1-based design. The transformer features parasitic capacitance of 20 pF from primary to secondary side.

# 2.3.4.3 Input Capacitors

The input capacitor must supply the input current during the input voltage dip from the 12-V battery. Input capacitors are essential in limiting the ripple voltage while supplying most of the switch current during the MOSFET switch on-time.

The input capacitance is calculated from 6-V minimum input voltage with 10% ripple:

$$C_{in} = \frac{I_{pri\_pk} \times D_{on}}{F_{SW} \times \Delta V_{ripple}} = \frac{1.72 \text{ A} \times 0.75}{100 \text{ k} \times 6 \text{ V} \times 10\%} = 20 \text{ } \mu\text{F}$$

(28)

### 2.3.4.4 Output Capacitors

The output capacitance ensures the converter have a small transient deviation to a step change of the load transient. The minimum needed capacitance is calculated as to maintain the output voltage drop less than 3% of the nominal voltage when the output current changes abruptly from the maximum to half (I<sub>step</sub>):

$$I_{\text{step}} = \frac{I_{\text{out}}}{2} = \frac{180 \text{ mA}}{2} = 90 \text{ mA}$$

(29)

$$V_{drop} = V_{out} \times 3\% = 24 \text{ V} \times 1\% = 0.24 \text{ V}$$

(30)

As any forward converters, the RHPZ limits the bandwidth of the flyback. The frequency of the RHPZ is calculated as:

$$f_{RHPZ} = \frac{R_{OUT} \times (V_{in} / V_{out})^2}{L_{PRI} \times 2\pi} = 24.8 \text{ kHz}$$

where

- R<sub>OUT</sub> is the load impedance

- L<sub>PRI</sub> is the primary inductance of the transformer

(31)

The bandwidth of the system is estimated as 1/5 of the RHPZ:

$$f_{\text{bandwidth}} = \frac{1}{5} \times f_{\text{RHPZ}} = \frac{1}{5} \times 24.8 \text{ kHz} = 4.96 \text{ kHz}$$

(32)

As the result, the output capacitance at bandwidth frequency is calculated as:

$$C_{out\_min} = \frac{1}{2 \times \pi \times f_{bandwidth}} \times \frac{1}{\Delta V_{out} / \Delta I_{loadstep} - ESR_{out}} = 12 \ \mu F$$

(33)

Therefore, a minimum of 12-µF capacitance is required for this design.

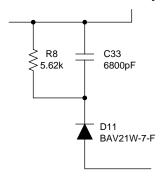

# 2.3.4.5 RC Snubber Design

When the MOSFET turns off, a high-voltage spike occurs at the drain (switch node) because of the leakage inductor of the main transformer and the parasitic capacitance in the circuit. The parasitic capacitance is composed of 3 components: (1) output capacitance of the MOSFET, (2) junction capacitance of the output diode which reflects to the primary side, (3) parasitic capacitance of the transformer winding.

As the result, implementation of an RC snubber circuit is very important to avoid MOSFET from avalanche breakdown and damage. Figure 13 shows the schematic of the RC snubber circuit.

Figure 13. RC Snubber of the TPS40210-Q1 Flyback DC/DC Converter

Voltage rating of the damping capacitance is calculated as:

$$V_{SN} = 3 \times n \times V_{out} = 3 \times 0.5 \times 24 \ V = 36 \ V$$

(34)

The damping resistance ( $R_{\text{SN}}$ ) is calculated as:

$$R_{SN} = \frac{{v_{sN}}^2}{\frac{1}{2} \times L_{lk1} \times i_{pri-pk}^2 \times \frac{v_{SN}}{v_{SN}-n} \times v_{out}} \times F_{SW}} = 8.3 \text{ k}\Omega$$

where

- L<sub>lk1</sub> is the leakage inductance of the primary side

- $I_{pri\ pk}$  is the peak current flowing into the transformer primary side

- V<sub>SN</sub> is the voltage across the snubber capacitor. It is determined at the minimum input load and full-load

- F<sub>SW</sub> is the switching frequency of the converter

- n is the turns ratio of the transformer primary to the secondary

A 5.6-k $\Omega$  resistor is selected for higher power dissipation. The power rating of the damping resistor is calculated as:

where

V<sub>SN</sub> is the voltage across the snubber capacitor. It is determined at the minimum input load and full-load condition.

The damping capacitance is calculated as:

$$C_{SN} = \frac{V_{SN}}{DV_{SN} \times R_{SN} \times F_{SW}} = \frac{36 \text{ V}}{36 \text{ V} \times 15\% \times 5.6 \text{ k}\Omega \times 100 \text{ kHz}} = 11 \text{ nF}$$

(37)

The higher the damping capacitance is, the lower the voltage spike is, and the longer the voltage spike duration will be.

Current flow through the freewheeling diode (D2) is calculated as:

$$i_{D} = C_{SN} \times \frac{dv}{dt} = 6.8 \text{ nF} \times \frac{42 \text{ V} + 0.5 \times 24 \text{ V}}{0.3 \times \frac{1}{100 \text{ Hz}}} = 0.12 \text{ A} \tag{38}$$

A Schottky diode with 200-V reverse blocking voltage, 0.2-A average current, and 2.5-A repetitive current flow is chosen in this design.

#### 2.3.4.6 Selection of MOSFETs

Selection of the MOSFET is very important for a high efficient, size optimized, and thermally enhanced power supply design. The MOSFET drain-to-source breakdown voltage must be higher than the voltage imposed on the switch node. The maximum drain-to-source voltage (V<sub>ds max</sub>) is calculated as:

$$V_{ds\_max} = n \times \frac{N_p}{N_s} \times (V_{out} + V_f) + V_{in\_max} = 66.7 \text{ V}$$

where

- n is the safe margin which is normally 1.5 or 2 times of the nominal value

- N<sub>o</sub>/N<sub>s</sub> is the turn ratio of the transformer primary winding to the secondary winding

- V<sub>OUT</sub> is the output voltage

- V<sub>f</sub> is the forward voltage of the output diode

- $V_{IN\_max}$  is the maximum input voltage

(39)

Therefore, a MOSFET with maximum drain-to-source voltage rating larger than 66.7 V must be chosen. Calculations on losses are done at the 12-V nominal input because this is the condition under which the MOSFET mostly works. Four components must be taken into account when selecting the MOSFET:

- On-state conduction losses

- Gate driver losses

- · Switching losses

- Output capacitance losses

The CSD19538Q3A, 100-V, 15-A MOSFET is selected for this reference design. The conduction losses of the MOSFET ( $P_{on}$ ) are calculated as:

$$P_{on} = I_D^2 \times R_{DS(on)} \times D_{on} = (0.63 \text{ A})^2 \times 59 \text{ m}\Omega \times 46.5\% = 0.01 \text{ W}$$

where

- I<sub>D</sub> is the conducting current during the turn-on of the switch

- R<sub>DS(on)</sub> is the channel resistance when the switch is turned on

The gate driver losses (P<sub>drive</sub>) are calculated as:

$$P_{drive} = Q_{d} \times V_{driver} \times F_{SW} = 4.3 \text{ nC} \times 8 \text{ V} \times 100 \text{ kHz} = 0.003 \text{ W}$$

where

- Q<sub>a</sub> is the gate charge

- V<sub>driver</sub> is the gate driver voltage

Switching losses of the MOSFET (PSW) are calculated as:

$$P_{SW} = \frac{1}{2} \times F_{SW} \times (V_{DSr} \times t_r \times l_{on} + V_{DSf} \times t_{off} \times l_{off}) = 0.02 \text{ W}$$

where

- V<sub>DSr</sub> is the drain-to-source voltage when MOSFET is switching at rising edge

- V<sub>DSf</sub> is the drain-to-source voltage when MOSFET is switching at falling edge

- F<sub>sw</sub> is the switching frequency

- t, is the switching rise time

- I<sub>on</sub> is the current built up level during turn on

- t<sub>off</sub> is the switching fall time

The output capacitance losses (P<sub>coss</sub>) are calculated as:

$$P_{coss} = \frac{1}{2} \times C_{oss} \times V_{DS}^2 \times F_{SW} = 0.003$$

W

where

- Coss is the output capacitance of the MOSFET

- ullet  $V_{DS}$  is the Drain-to-Source voltage when MOSFET is switching

- F<sub>sw</sub> is the switching frequency (43)

Therefore, the total losses in the MOSFET are calculated as:

$$P_{\text{total}} = P_{\text{on}} + P_{\text{SW}} + P_{\text{coss}} = 0.01 \text{ W} + 0.02 \text{ W} + 0.003 \text{ W} = 0.023 \text{ W}$$

(44)

### 2.3.5 Buck Converter

The bias supply solution 3 implements a buck converter as the front stage and a push-pull transformer driver supply as the following stage. The synchronous step-down DC/DC converter LM46002-Q1 with integrated switch is selected as the front stage. It is capable of driving up to 2 A of load current from an input voltage ranging from 3.5 V to 60 V.

# 2.3.5.1 Switching Frequency

The switching frequency can be programmed by the impedance  $R_T$  from the RT pin to ground. The frequency is inversely proportional to the  $R_T$  resistance. The LM46002-Q1 device is operated at 480-kHz switching frequency in this design.  $R_T$  is calculated as:

$$R_{T} = \frac{40200}{F_{SW}} - 0.6 = 83.2 \text{ k}\Omega \tag{45}$$

# 2.3.5.2 Output Inductor

The buck converter inductance is calculated according to the switching frequency. The selected value compromises between the size of the inductor and the peak-to-peak output ripple current. A higher inductance gives lower ripple current, which then gives a lower output voltage ripple with the same output capacitors. An inductance that gives a ripple current of 20% to 40% at the maximum current is a good starting point. The minimum inductor value is calculated based on input voltage range, output voltage, maximum output current, and the switching frequency:

$$\frac{(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{D}}{0.4 \times \mathsf{F}_{\mathsf{SW}} \times \mathsf{I}_{\mathsf{OUT}}} \leq \mathsf{L}_{\mathsf{min}} \leq \frac{(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{D}}{0.2 \times \mathsf{F}_{\mathsf{SW}} \times \mathsf{I}_{\mathsf{OUT}}}$$

### where

- V<sub>IN</sub> is the maximum input voltage in 12-V battery nominal condition

- V<sub>OUT</sub> is the output voltage

- F<sub>sw</sub> is the switching frequency

- I<sub>OUT</sub> is the output current

- D is the duty cycle at 16-V input (46)

Hence, the calculated inductance is between 10μH and 20μH. For this design, 18-μH inductance is chosen. Besides the inductor size, the rated saturation current needs to be specified as:

$$I_{\text{Ripple}} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times D}{L \times F_{\text{SW}}}$$

(47)

$$I_{L-peak} = I_{OUT} + \frac{I_{Ripple}}{2}$$

(48)

Hence, the inductor peak current is calculated as 3.6 A. The MSS1260-183MLB from Coilcraft with 5.22-A saturation current rating is selected for this design. A good practice is to use an inductor with the saturation current around 1.5 to 2 times higher than calculated.

In general, it is preferable to choose lower inductance in switching power supplies, because it usually corresponds to faster transient response, smaller DCR, and reduced size. However, inductance that is too low leads to high-output voltage ripple with the same output capacitance. It also generates more conduction loss because the RMS current is slightly higher relative that with a lower current ripple at the same DC current. As the LM46002-Q1 device implements peak current mode control, it is not recommended to have too small of an inductor current ripple. Enough of an inductor current ripple improves the signal-to-noise ratio on the current comparator and makes the control loop more immune to noise.

### 2.3.5.3 Output Capacitors

The value of output capacitors are calculated based on the maximum desired output voltage ripple, and the transient response:

$$C_{\text{OUT}} \geq \frac{1}{F_{\text{SW}} \times \frac{\Delta I_{\text{L}}}{I_{\text{OUT}}} \times \frac{\Delta V_{\text{OUT}}}{\Delta I_{\text{OUT}}}} \times \left[ \frac{\Delta I_{\text{L}}}{I_{\text{OUT}} \times 12} \times (1 + (1 - D)) + (1 - D) \times (1 + \frac{\Delta I_{\text{L}}}{I_{\text{OUT}}}) \right]$$

where

ΔI<sub>OUT</sub> is the load step change

- ΔV<sub>OUT</sub> is the target output voltage undershoot

- $\Delta$ IL is the inductor ripple current

As a result, the output capacitance should be larger than 20  $\mu$ F. Two 22- $\mu$ F ceramic capacitors are connected in parallel to meet the requirement. The second requirement is the maximum ESR of the capacitor, which is calculated from:

$$ESR \le \frac{1-D}{F_{sw} \times C_{out}} \times \left(\frac{I_{out}}{\Delta I_{L}} + 0.5\right)$$

(50)

The maximum ESR is calculated to meet the required maximum output ripple. The equivalent ESR of the output capacitors should be lower than  $0.288~\Omega$ .

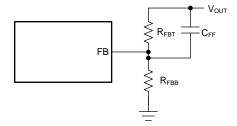

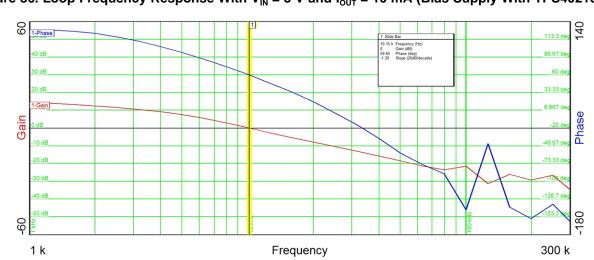

# 2.3.5.4 Loop Compensation

The LM46002-Q1 device is internally compensated with RC = 400 k $\Omega$  and CC = 50 pF. The internal compensation is designed such that the loop response is stable over the entire operating frequency and output voltage range. Depending on the output voltage, the compensation loop phase margin can be low with all ceramic capacitors. An external feed-forward cap  $C_{\text{FF}}$  is recommended to be placed in parallel with the top resistor divider RFBT for optimum transient performance.

Figure 14. Feed-Forward Capacitor for Loop Compensation

$C_{\text{FF}}$  is chosen such that the phase margin is boosted at the crossover frequency. The crossover frequency without  $C_{\text{FF}}$  can be calculated as:

$$F_{X} = \frac{\Delta I_{OUT}}{2 \times \pi \times \Delta V_{OUT} \times C_{OUT}}$$

(51)

The  $C_{FF}$  should be selected such that the bandwidth of the control loop without the CFF is centered between the zero and pole frequencies caused by the feedforward capacitor. Therefore:

$$C_{FF} = \frac{1}{2 \times \pi \times F_{\chi}} \times \frac{1}{\sqrt{R_{FBT} \times (R_{FBT} \parallel R_{FBB})}}$$

(52)

A 100-pF feedforward capacitor is selected for this design.

The LM46002 device needs a bootstrap capacitor between CBOOT and the SW pin. The recommended bootstrap capacitor is 0.47  $\mu$ F and rated at 50 V. The bootstrap capacitor must be a high-quality ceramic type with X7R or X5R grade dielectric for temperature stability.

The VCC pin is the output of an internal LDO for the LM46002 device. The input for this LDO comes from either  $V_{IN}$  or bias. To ensure stability of the part, a minimum of a 2.2- $\mu$ F, 10-V capacitor is connected from VCC to ground.

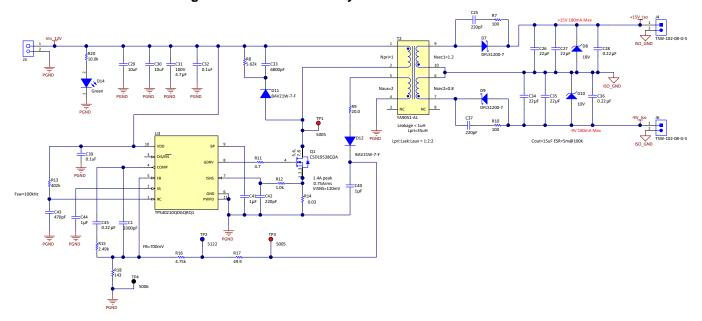

# 2.3.6 SN6505-Q1 Push-Pull Transformer Driver

The second stage implements a push-pull transformer driver to transfer power from the primary side to the secondary side. Figure 15 shows the converter operation theory.

CR1 V<sub>OUT</sub>

CR1 V<sub>OUT</sub>

CR1 V<sub>OUT</sub>

CR1 V<sub>OUT</sub>

CR1 V<sub>OUT</sub>

CR1 V<sub>OUT</sub>

CR2 Q2 Q1 Q1 Q1 Q1

Figure 15. Push-Pull Converter Theory of Operation

When Q1 conducts, current is sourced from VIN into the ground through the lower half of the transformer primary, this creates a potential at the lower half of the primary winding with the primary center tap as the positive. This voltage transfers to the transformer secondary according to the transformer polarity and turns ratio. CR1 is now forward-biased and CR2 is reverse-biased, causing a current to flow through the upper half of the secondary winding. Similarly, when Q2 conducts, the transformer primary and secondary polarities reverse. CR1 is reverse-biased and CR2 is forward-biased, which causes a current to flow from the bottom half of the secondary through CR2 into the load. Q1 and Q2 switch alternatively, with approximately 50% duty cycle to transfer power from the primary to the secondary of the transformer.

Before either switch is turned ON, there must be a short period during which both transistors are high impedance. This short period, known as break-before-make time, is required to avoid shorting out both ends of the primary.

The SN6505-Q1 push-pull transformer driver has integrated MOSFET switches. The positive temperature co-efficient of these switches has a self-correcting effect on the V-t imbalance. During a slightly longer ontime, the prolonged current flow through a FET gradually heats the MOSFET, which leads to an increase in  $R_{DS(on)}$ . The higher resistance then causes the drain-source voltage, VDS, to increase. Because the voltage at the primary is the difference between the constant input voltage, VIN, and the voltage drop across the MOSFET is gradually reduced and V-t balance is restored.

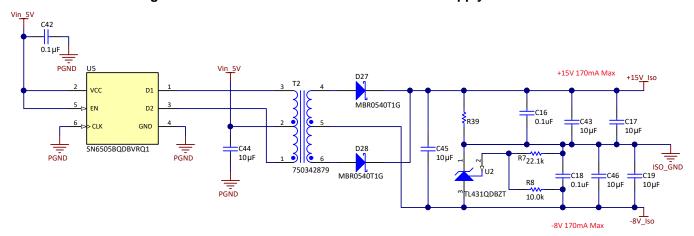

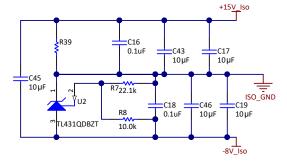

### 2.3.6.1 Power Supply Specification

Specifications of the designed push-pull power supply are summarized in Table 6. Figure 16 shows the designed schematic. The required external discrete components are: center-tapped transformer, rectifier diodes, and input and output bulk capacitors.

PARAMETER

SPECIFICATION

Input voltage

5 V ±5%

Output voltage

+15 V, -8 V

Output current

180 mA

Output voltage ripple

< 200 mV peak to peak at full load</td>

Output power

4.14 W

Table 6. Push-Pull Transformer Driver Power Supply Specifications

Figure 16. Push-Pull Transformer Driver Power Supply Schematic

### 2.3.6.2 Transformer Design

The input peak current was calculated from Equation 53. The factor 0.97 accounts for typical transformer power transfer efficiency.

$$I_{\text{in\_peak}} = \frac{P_{\text{out\_max}}/\eta}{V_{\text{in\_min}}} = \frac{4.32 \text{ W/0.97}}{4.75 \text{ V}} = 882 \text{ mA}$$

where

- P<sub>out max</sub> is the maximum output power

- V<sub>IN min</sub> is the minimum input voltage

The SN6505-Q1 device switches the internal dual MOSFETs with approximately 50% duty cycle each. Therefore, the AC current flowing through transformer primary ( $I_{pri}$ ) can be calculated from:

$$I_{pri} = \frac{I_{\text{in\_peak}}}{2} = \frac{882 \text{ mA}}{2} = 441 \text{ mA}$$

(54)

The transformer turns ratio (N<sub>ps</sub>) is calculated from:

$$N_{ps} = \frac{V_{pri}}{V_{sec} + V_f} = \frac{5 \text{ V}}{23 \text{ V} + 0.35 \text{ V}} = 1:4.67$$

where

- V<sub>sec</sub> is the voltage across the secondary winding

- V<sub>f</sub> is the forward voltage of the diode

- V<sub>ori</sub> is the voltage across the primary winding (55)

The V-t product of the transformer must be greater than Vt<sub>min</sub>. Failure to meet these criteria will lead to transformer core saturation:

$$Vt_{min} = V_{IN\_max} imes rac{T_{max}}{2} = rac{V_{IN\_max}}{2 imes F_{min}} = rac{5 \ V imes 1.05}{2 imes 300 \ kHz} = 8.75 \ V \ \mu s$$

where

- V<sub>IN max</sub> is the maximum input voltage

- F<sub>min</sub> is the minimum switching frequency

The 750342879 transformer from Wurth Electronics is selected for this design. Table 7 summarizes the specifications.

PARAMETERSPECIFICATIONTurns ratio (6-4):(1-3) $3.5:1,\pm 2\%$ DC resistance (1-3) $0.33 \Omega$  maximum at 20°CDC Resistance (6-4) $0.75 \Omega$  maximum at 20°CInductance (1-2) $50-\mu$ H minimum at 100 kHz, 10 mVac

**Table 7. Push-Pull Transformer Specifications**

(53)

(56)

| PARAMETER                   | SPECIFICATION                    |

|-----------------------------|----------------------------------|

| Dielectric (1 – 6)          | 5000 V <sub>RMS</sub> , 1 minute |

| Operating temperature range | -40°C to 125°C                   |

| Clearance distance          | 8 mm                             |

### 2.3.6.3 Rectifier Diode

To increase the efficiency of the push-pull forward converter, the forward voltage drop of the secondary side rectifier diodes must be minimized. This design implements the SN6505B version which has the high-switching frequency and the diodes are subject to excessive reverse recoveries. Schottky diodes are selected as they meet the requirements of low forward-voltage drop and fast recovery time. The diode should withstand a reverse voltage of twice the output voltage.

The forward current flowing through the diode is the rated output current which is 180 mA. The reverse blocking voltage of the diode is calculated as:

$$V_b = V_{out} + V_{in} \times \frac{N_{sec}}{N_{pri}} = 36 \quad V$$

(57)

Two 40-V, 500-mA Schottky diodes are chosen for this design.

### 2.3.6.4 Capacitor Selection

Considering two 22-µF ceramic capacitors being placed at output of the buck converter, one ceramic bypass capacitor of 100 nF is placed as close as possible to the V<sub>CC</sub> pin for high frequency noise filtering.

The output capacitor is required to filter the output ripple. The output ripple specification is calculated as:

$$\Delta V = V_{out} \times 10\% = 23 \quad V \times 1\% = 0.23 \quad V$$

(58)

The required peak current which is delivered to the gate driver is 20 A, according to the isolated gate driver board. The required capacitance is calculated as:

$$C \ge \frac{I_{peak} \times dt}{\Delta V} = 13 \ \mu F$$

(59)

Considering it could also be used to drive SiC MOSFETs with higher total gate charge, a total of two 10µF ceramic capacitors are connected in parallel at the positive and negative supply outputs.

# 2.3.6.5 Generation of the Negative Supply

The power supply output is separated into the positive rail of +15 V and the negative rail of -8 V through the TL431-Q1 device which reacts as a shunt regulator. Figure 17 shows the schematic.

Figure 17. Generation of Negative Voltage Rail Through TL431-Q1 Shunt Reference

To program the cathode voltage to a regulated voltage, a resistive bridge is shunted between the cathode and anode pins with the mid-point tied to the reference pin. The cathode voltage is calculated as:

$$V_{\text{neg}} = (1 + \frac{R_7}{R_8}) \times V_{\text{ref}} = (1 + \frac{22.1 \text{ k}\Omega}{10 \text{ k}\Omega}) \times 2.5 \text{ V} = 8 \text{ V}$$

(60)

For this equation to be valid, the TL431-Q1 device must be fully biased so that it has enough open loop gain to mitigate any gain error. The cathode current is set to:

$$I_{cat} = \frac{V_{out} - V_{neg}}{R_{39}} = \frac{23 \ V - 8 \ V}{15.4 \ k\Omega} = 0.97 \ mA \tag{61}$$

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Required Hardware

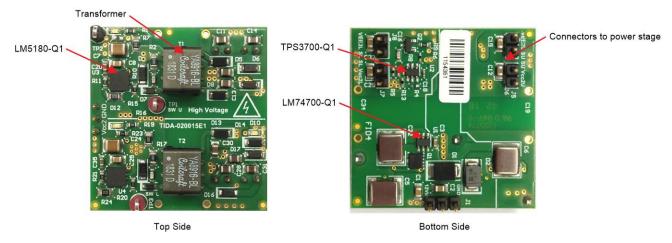

Figure 18 shows the inverter power stage board and connectors pin description. The placement of components and corresponding circuits are also described. Figure 19 shows the PCB board image of LM5180-Q1 based flyback converter from top side and bottom side, respectively. The input and output connectors are indicated.

High Side Gate Driver

DC Bus Voltage Sense

NTC Temp Sense

NTC Temp Sense

VCC1 TRO\_P BUS\_N FU FL F

GND1 TRO\_N BUS\_P RST INU+ INL+

Figure 18. Power Stage and Connectors Pin Description

Figure 19. LM5180-Q1 Based Flyback PCB Board

Figure 20 shows the LM5180-Q1 based flyback PCB board connected to the power stage.

Figure 20. LM5180-Q1 Based Bias Supply Connected to the Power Stage

Figure 21 shows the PCB board image of TPS40210-Q1 based flyback converter from top side and bottom side, respectively.

TPS40210-Q1 Transformer Connectors to power stage

Top side Bottom side

Figure 21. TPS40210-Q1 Based Flyback PCB Board Image

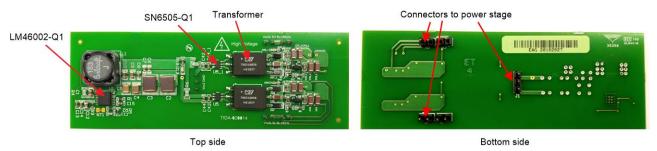

Figure 22 shows the PCB board image of buck with push-pull power supply from top side and bottom side, respectively.

Figure 22. Buck With Push-Pull Power Supply PCB Board

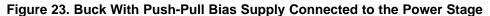

Figure 23 shows the buck with push-pull converter board implemented on top of the power stage and connected with the IGBT module.

# 3.2 Testing and Results

# 3.2.1 Low-Voltage Tests on the LM5180-Q1 Flyback Converter

This section presents the experimental results of the bias supply solution 1 which is the flyback converter based on the LM5180-Q1 device.

### 3.2.1.1 Startup

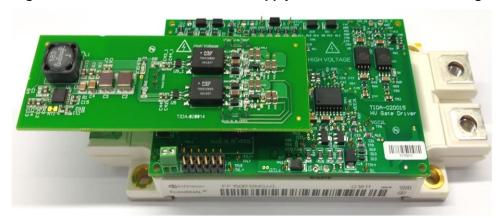

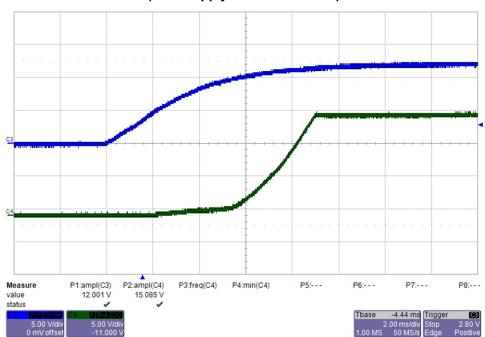

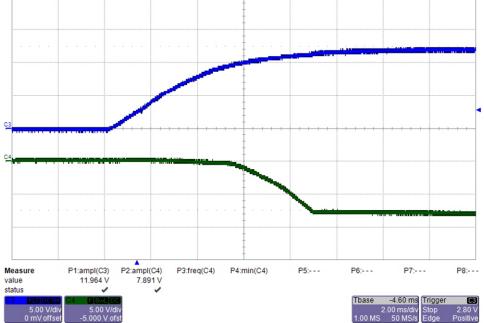

The start-up waveforms of the flyback converter designed with the LM5180-Q1 device are measured under 5- and 12-V inputs, respectively. The 15-V and –9-V rails are measured separately.

Measure P1:ampl(C3) P2:ampl(C4) P3:freq(C4) P4:min(C4) P5:-- P6:-- P7:-- P8:--- P8:---

Figure 24. Start-up Waveform of the 15-V Rail With V<sub>IN</sub> = 5 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 5 ms/div

Measure value 5.035 V 7.689 V status

2.00 V/div 0 mV offset

2.00 V/div -5.000 V ofst

Figure 25. Start-up Waveform of the -9-V Rail With  $V_{\rm IN}$  = 5 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 2 V/div, CH4: output voltage 5 V/div, 5 ms/div

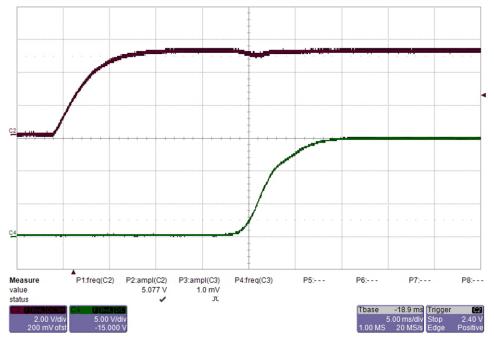

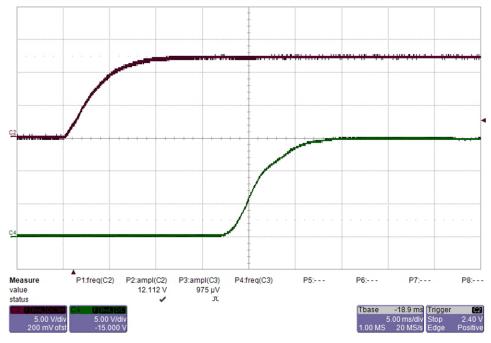

Figure 26. Start-up Waveform of the 15-V Rail With V<sub>IN</sub> = 12 V and 180-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

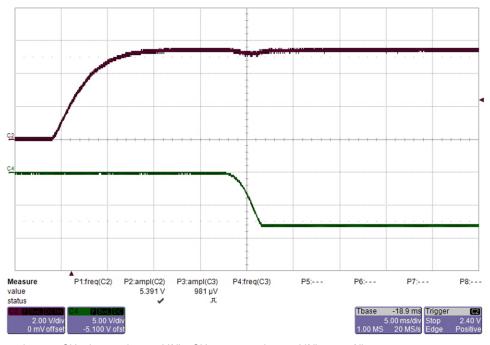

Figure 27. Start-up Waveform of the −9-V Rail With V<sub>IN</sub> = 12 V and 180-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 2 ms/div

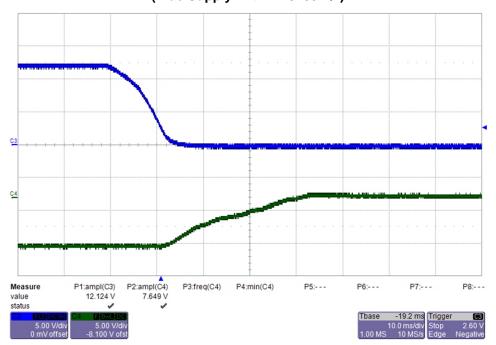

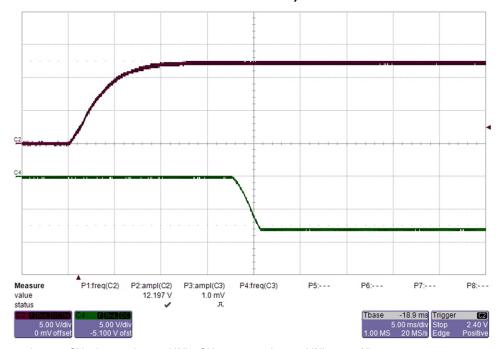

### 3.2.1.2 **Power Down**

The power-down waveforms of the flyback converter designed with the LM5180-Q1 device are measured under 5- and 12-V inputs, respectively. The 15-V and –9-V rails are measured separately.

Measure value 12.110 V 14.655 V status

5.00 V/div 5.00

Figure 28. Power-Down Waveform of the 15-V Rail With V<sub>IN</sub> = 12 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 10 ms/div

Figure 29. Power-Down Waveform of the –9-V Rail With  $\rm V_{IN}$  = 12 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 10 ms/div

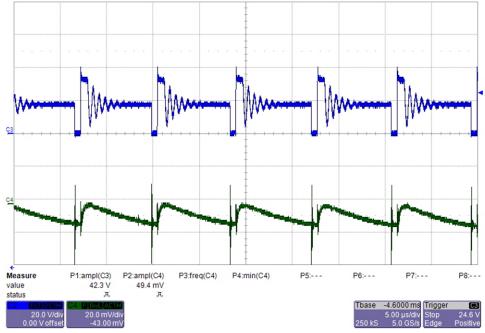

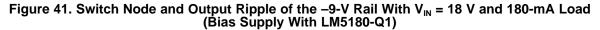

# 3.2.1.3 Switch Node and Output Voltage Ripple

The switch node and output voltage ripple of the flyback converter designed with the LM5180-Q1 device are measured under 5-, 12-, and 18-V inputs, respectively. The +15-V and –9-V rails are measured separately.

Figure 30. Switch Node and Output Ripple of the 15-V Rail With  $V_{IN}$  = 5 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 10 mV/div, 5 µs/div

Figure 31. Switch Node and Output Ripple of the 15-V Rail With V<sub>IN</sub> = 5 V and 85-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 100 mV/div, 10 µs/div

Figure 32. Switch Node and Output Ripple of the -9-V Rail With  $V_{\rm IN}$  = 5 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 20 mV/div, 5 µs/div

Figure 33. Switch Node and Output Ripple of the -9-V Rail With V $_{\rm IN}$  = 5 V and 85-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 100 mV/div, 10 µs/div

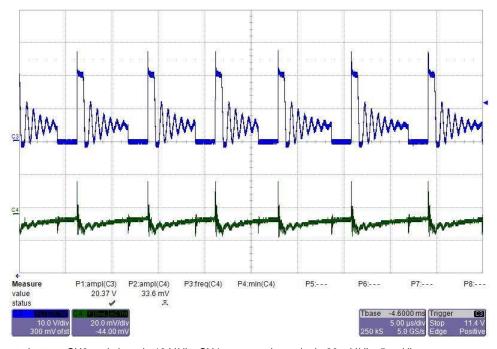

P2:ampl(C4) P3:freq(C4) value 36.0 V 49.5 mV status -4.6000 ms Trigger

Figure 34. Switch Node and Output Ripple of the 15-V Rail With  $V_{IN}$  = 12 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 20 mV/div, 10 µs/div

Figure 35. Switch Node and Output Ripple of the 15-V Rail With  $V_{\rm IN}$  = 12 V and 180-mA Load (Bias Supply With LM5180-Q1)

Measure P3:freq(C4) P5:---P7:---P8:---P1:ampl(C3) P2:ampl(C4) P4:min(C4) P6:---

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5 µs/div

26.55 V

value

183 mV

Figure 36. Switch Node and Output Ripple of the -9-V Rail With  $V_{IN}$  = 12 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 10 V/div, CH4: output voltage ripple 10 mV/div, 5 µs/div

Figure 37. Switch Node and Output Ripple of the -9-V Rail With  $V_{IN}$  = 12 V and 180-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5  $\mu$ s/div

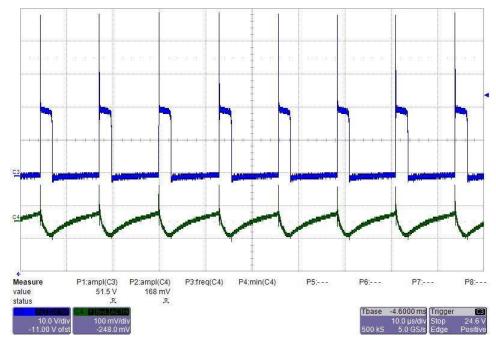

Figure 38. Switch Node and Output Ripple of the 15-V Rail With V<sub>IN</sub> = 18 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 20 mV/div, 5  $\mu$ s/div

Figure 39. Switch Node and Output Ripple of the 15-V Rail With  $V_{\rm IN}$  = 18 V and 180-mA Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 100 mV/div, 5 µs/div

-4.6000 ms Trigger

(Blas Supply With Livis 180-Q1)

Figure 40. Switch Node and Output Ripple of the -9-V Rail With  $V_{IN}$  = 18 V and no Load (Bias Supply With LM5180-Q1)

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 20 mV/div, 5  $\mu$ s/div

P3:freq(C4)

P2:ampl(C4)

65.0 mV

43.4 V

Measure value

status

P4:min(C4)

From top to bottom: CH3: switch node 20 V/div, CH4: output voltage ripple 50 mV/div, 2  $\mu$ s/div

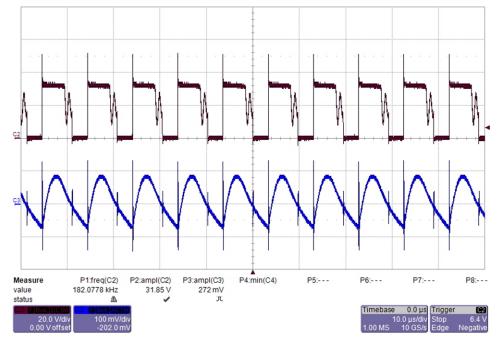

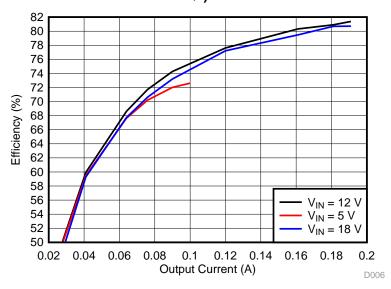

#### 3.2.1.4 **Efficiency**

Figure 42 shows the measured efficiency of the flyback converter designed with the LM5180-Q1 device over the full-load range. As can be seen, around 86% peak efficiency is achieved with the input voltages of 5 V, 12 V, and 18 V, respectively.

87.5 85 82.5 80 77.5 Efficiency (%) 75 72.5 70 67.5 65 62.5  $V_{IN} = 12 \text{ V}$ 60  $V_{IN} = 5 V$ 57.5  $V_{IN} = 18 V$ 55 0.005 0.025 0.045 0.065 0.085 0.105 0.125 0.145 0.1650.181 Output Current (A) D004

Figure 42. Measured Efficiency Under Input Voltages of 5 V, 12 V, and 18 V (Bias Supply With LM5180-Q1)

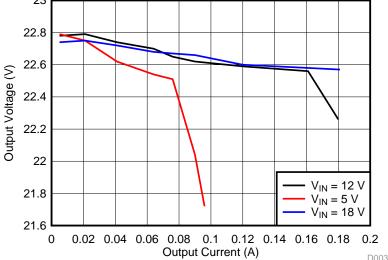

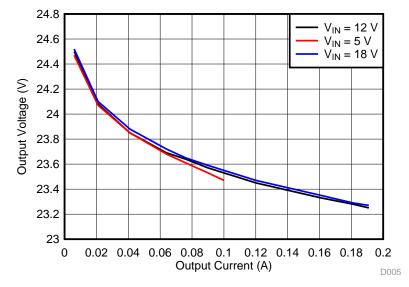

#### 3.2.1.5 Load Regulation

Load regulation measurements show the % deviation from nominal output voltage as a function of output current. The measured result of the flyback converter designed with LM5180-Q1 is shown in Figure 43. The load regulation is measured with the input voltages of 5 V, 12 V, and 18 V, respectively.

Figure 43. Load Regulation Under Input Voltages of 5 V, 12 V, and 18 V (Bias Supply With LM5180-Q1)

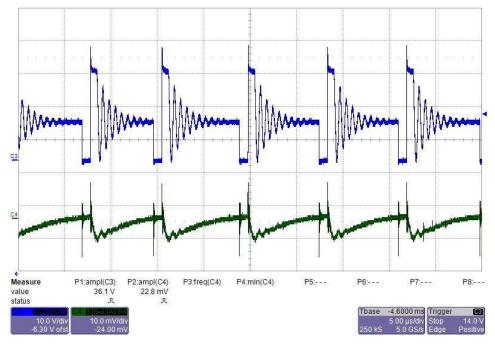

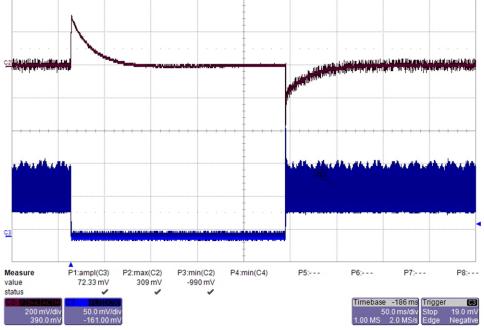

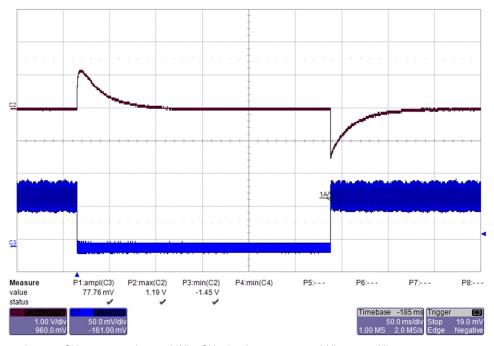

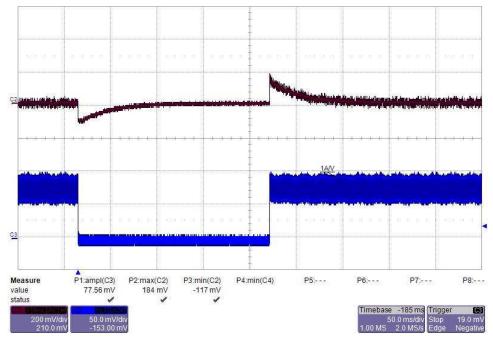

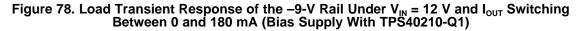

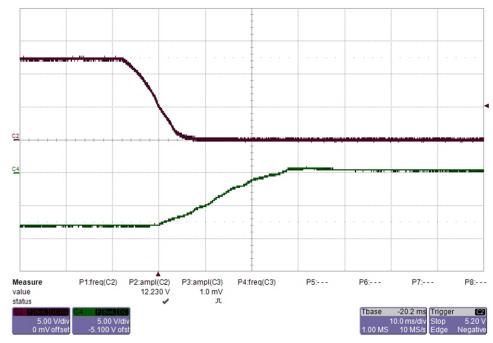

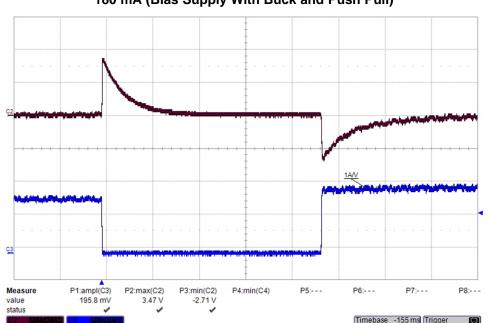

#### 3.2.1.6 Load Transients

This section shows the load transient measurements of the flyback converter designed with the LM5180-Q1 device. The load transient response presents how well a power supply copes with the changes in the load-current demand. During the test, the load is switching from 0 to full under input voltages of 5 V, 12 V, and 18 V, respectively.

Figure 44. Load Transient Response of the 15-V Rail Under V<sub>IN</sub> = 5 V and I<sub>OUT</sub> Switching Between 0 and 80 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 200 mV/div, CH3: load current 500 mA/div, 50 ms/div

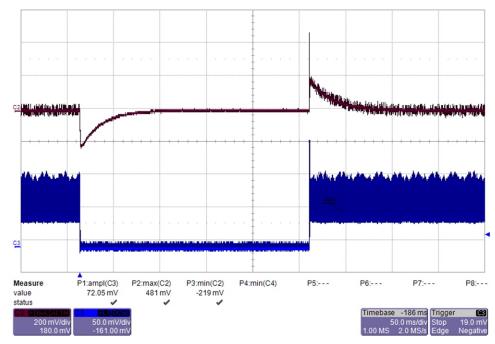

Figure 45. Load Transient Response of the -9-V Rail Under  $V_{IN} = 5$  V and  $I_{OUT}$  Switching Between 0 and 80 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 200 mV/div, CH3: load current 500 mA/div, 50 ms/div

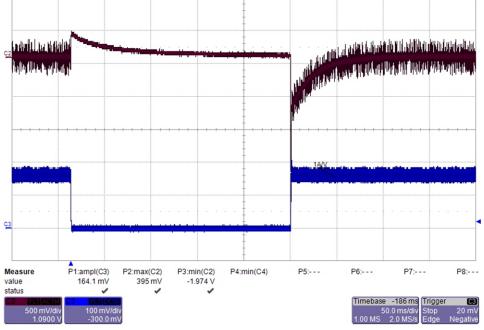

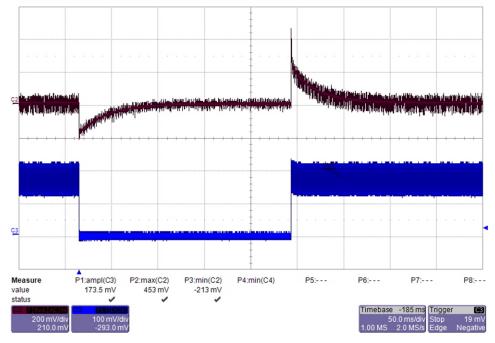

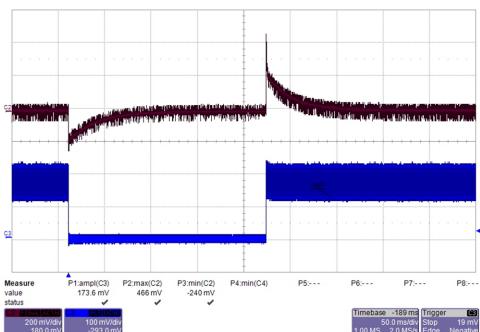

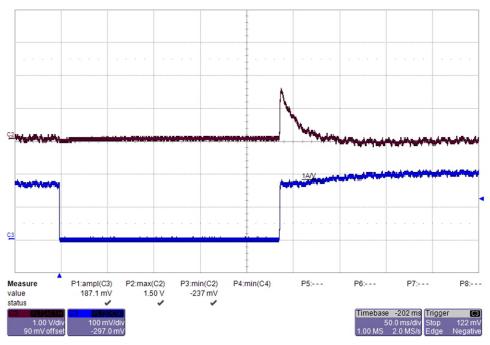

Figure 46. Load Transient Response of the 15-V Rail Under V<sub>IN</sub> = 12 V and I<sub>OUT</sub> Switching Between 0 and 180 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

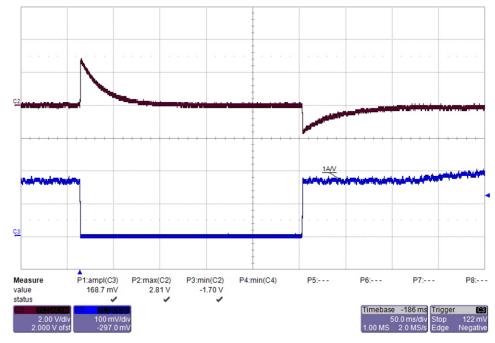

Figure 47. Load Transient Response of the -9-V Rail Under  $V_{IN} = 12 \text{ V}$  and  $I_{OUT}$  Switching Between 0 and 180 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

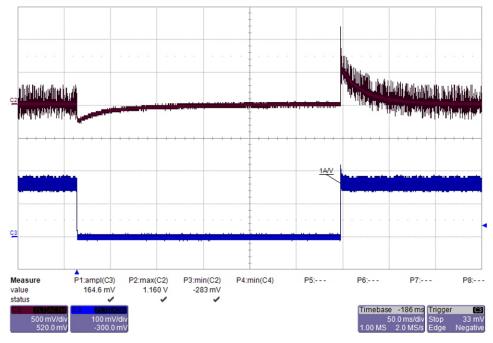

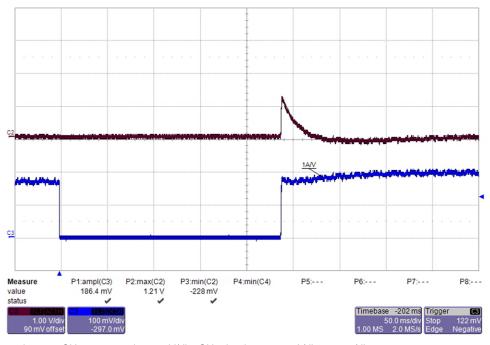

Figure 48. Load Transient Response of the 15-V Rail Under  $V_{IN}$  = 18 V and  $I_{OUT}$  Switching Between 0 and 180 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 1 V/div, CH3: load current 1 A/div, 50 ms/div

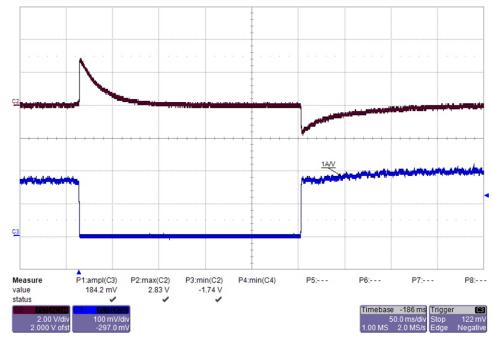

Figure 49. Load Transient Response of the -9-V Rail Under  $V_{IN} = 18$  V and  $I_{OUT}$  Switching Between 0 and 180 mA (Bias Supply With LM5180-Q1)

From top to bottom: CH2: output voltage 500 mV/div, CH3: load current 1 A/div, 50 ms/div

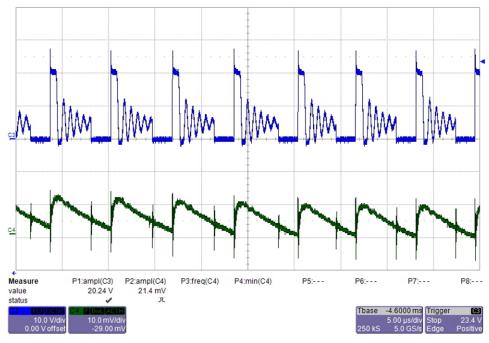

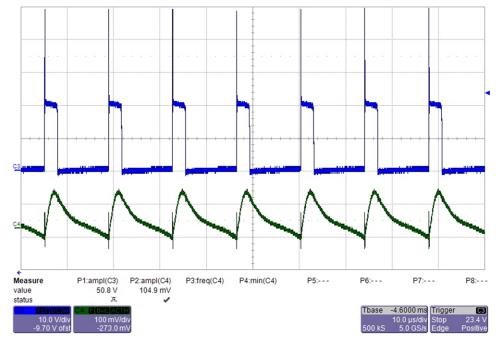

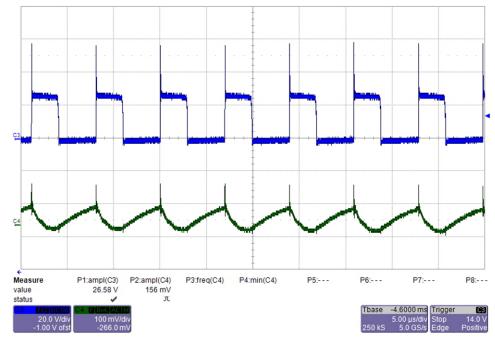

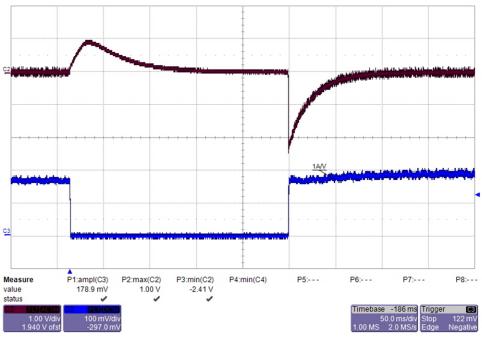

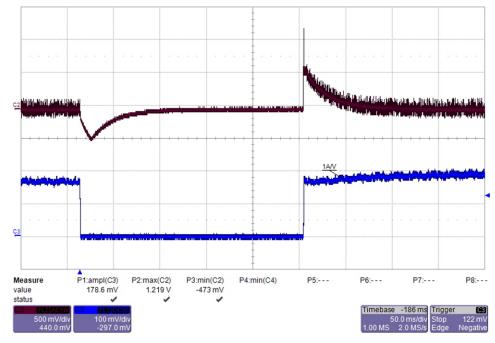

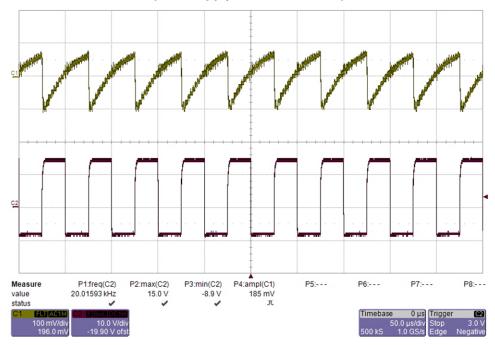

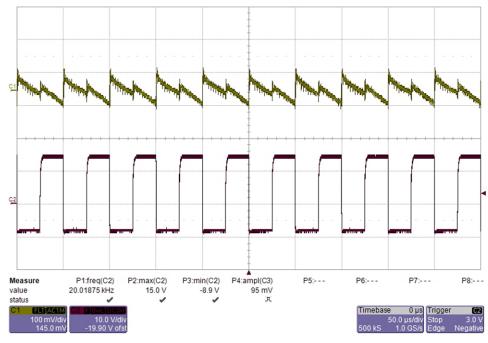

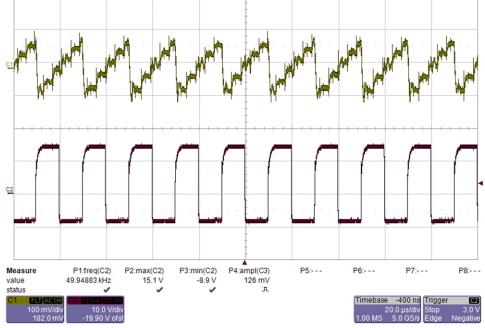

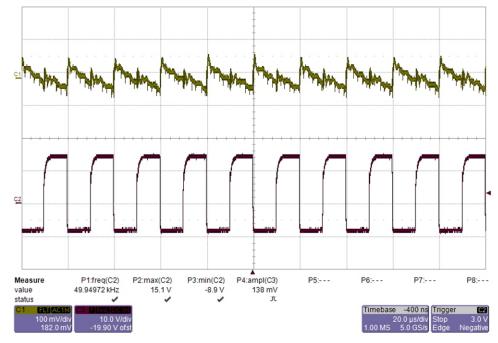

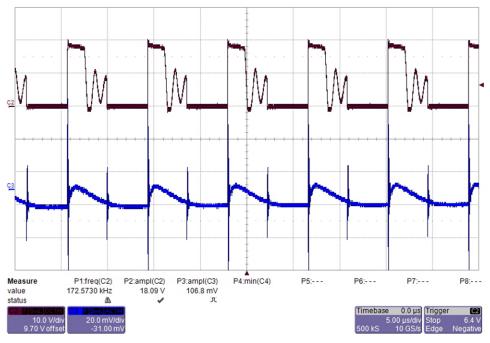

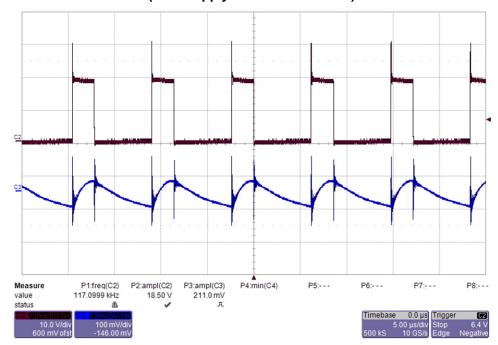

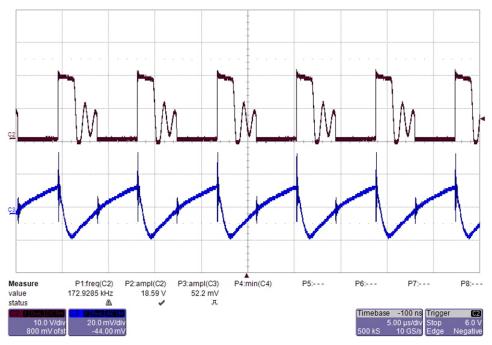

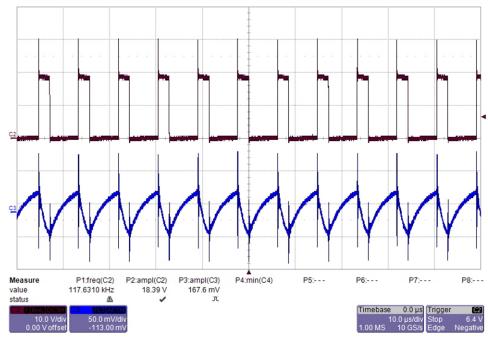

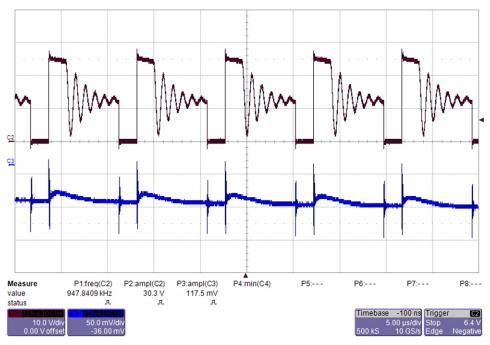

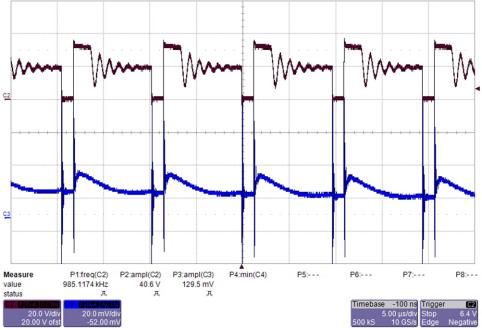

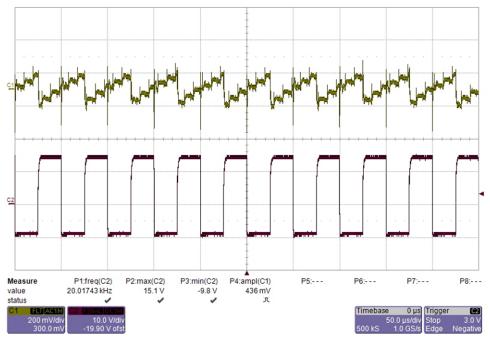

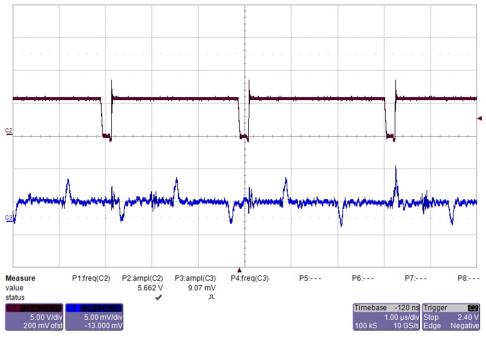

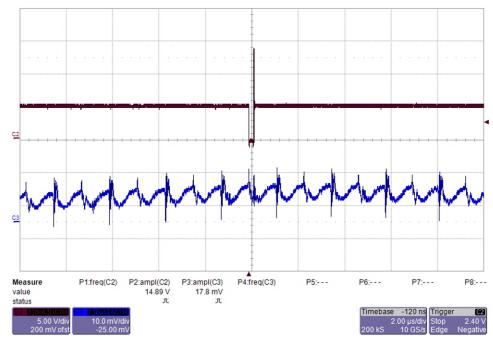

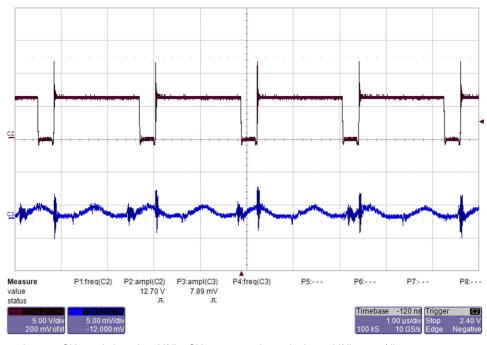

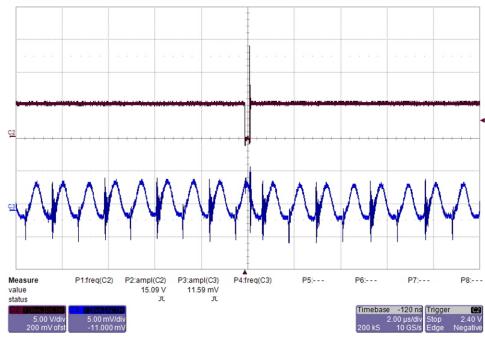

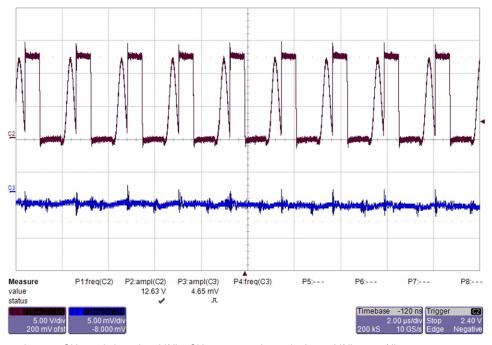

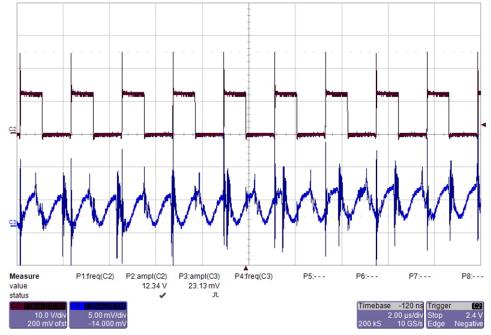

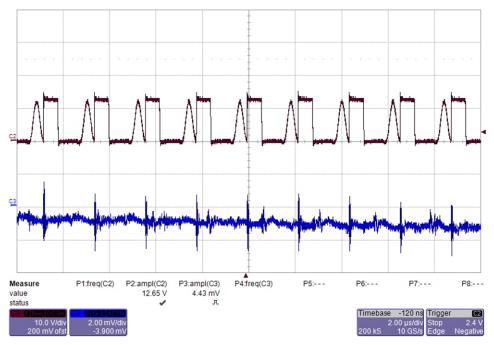

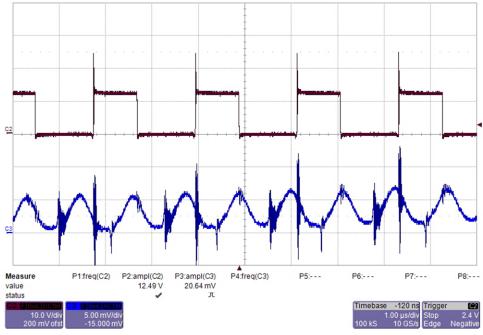

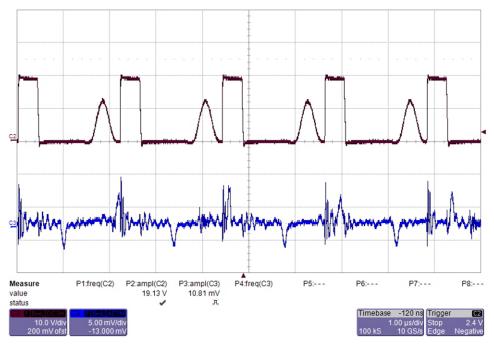

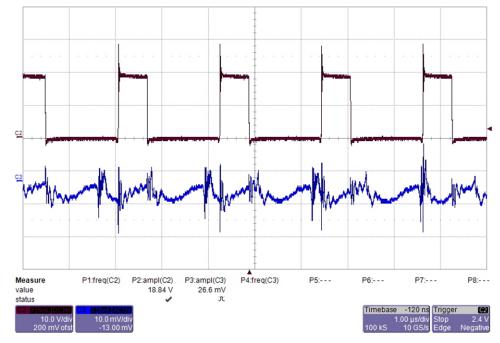

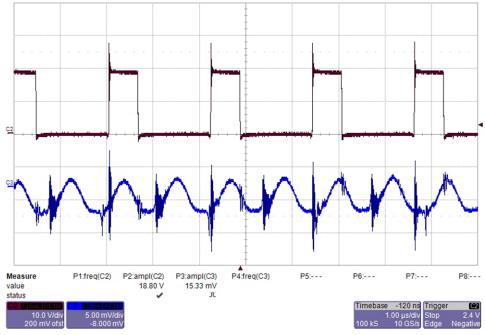

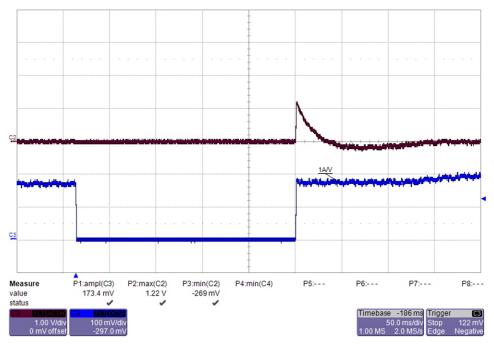

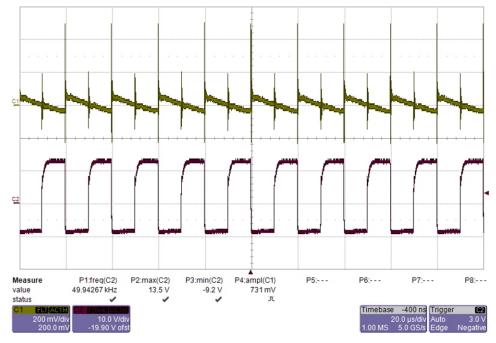

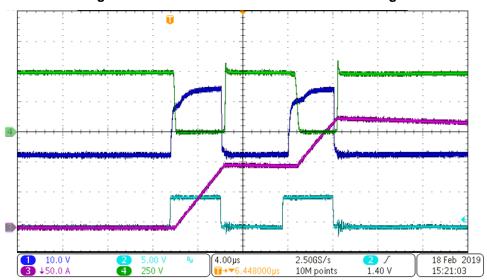

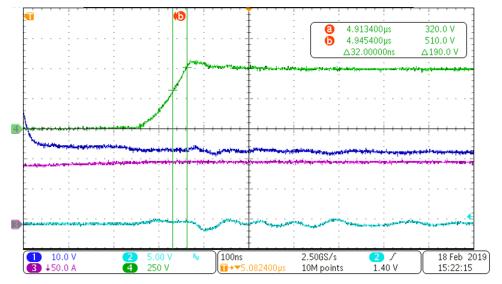

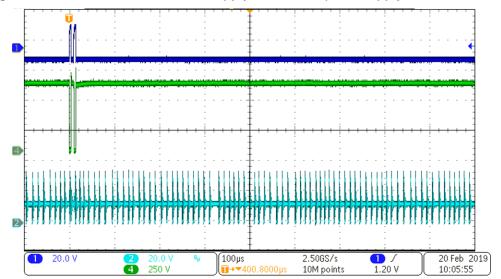

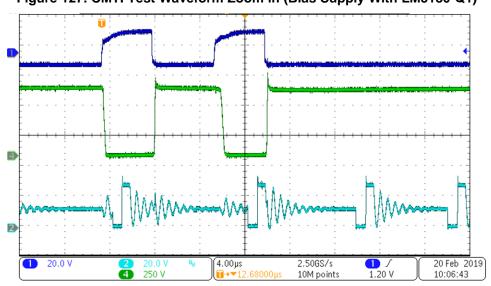

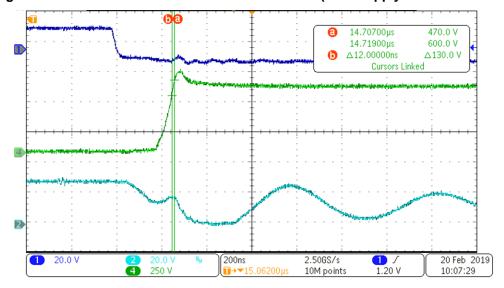

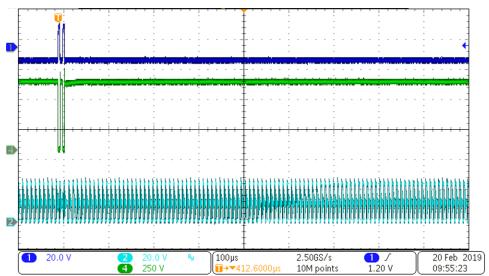

## 3.2.1.7 Voltage Ripple While Switching IGBT

The flyback converter designed with the LM5180-Q1 device is connected to the isolated gate drivers (ISO5852S-Q1) and the 1200-V IGBT module (FF150R12MS4G) for checking the voltage ripple during the switching transients. The IGBTs are switched at 20- and 50-kHz frequencies, respectively.

Figure 50. Voltage Ripple of the 15-V Rail While Switching the IGBT Module at 20 kHz (Bias Supply With LM5180-Q1)

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 50 µs/div

Figure 51. Voltage Ripple of the -9-V Rail While Switching the IGBT Module at 20 kHz (Bias Supply With LM5180-Q1)

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 50 µs/div

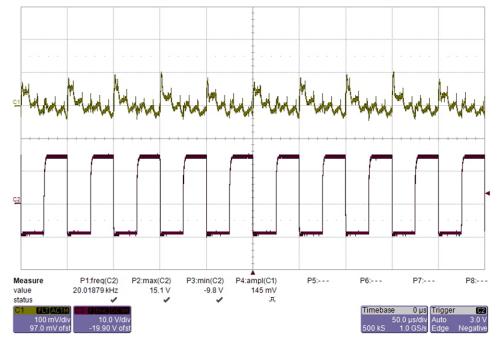

Figure 52. Voltage Ripple of the 15-V Rail While Switching the IGBT Module at 50 kHz (Bias Supply With LM5180-Q1)

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 20  $\mu$ s/div

Figure 53. Voltage Ripple of the -9-V Rail While Switching the IGBT Module at 50 kHz (Bias Supply With LM5180-Q1)

From top to bottom: CH1: output voltage 100 mV/div, CH2: gate PWM signal 10 V/div, 20 µs/div

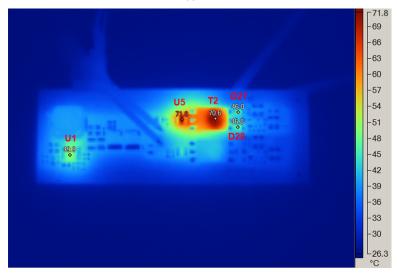

# 3.2.1.8 Thermal Image

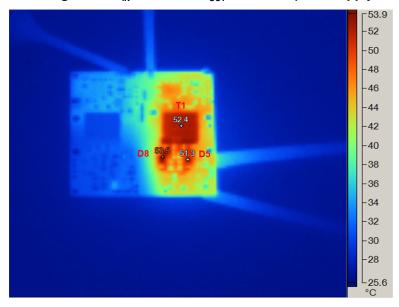

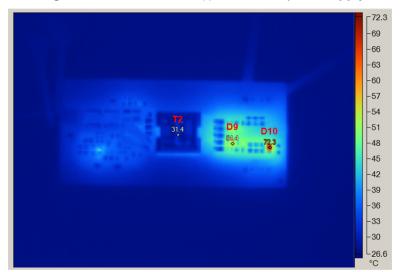

The thermal of the flyback converter designed with the LM5180-Q1 device is measured under the full-load conditions. The circuit runs at the room temperature for 30 minutes. A 12-V nominal voltage is applied. The converter is loaded with 180 mA. Figure 54 shows the thermal image of the board.

Figure 54. Thermal Image With  $V_{IN}$  = 12 V and  $I_{OUT}$  = 180 mA (Bias Supply With LM5180-Q1)

T1: Flyback transformer, D8 and D5: secondary rectification diode

# 3.2.2 Low-Voltage Tests on the TPS40210-Q1 Flyback Converter

This section presents the experimental results of the bias supply solution 2 which is the flyback converter based on the TPS40210-Q1 device.

#### 3.2.2.1 Startup

The startup waveforms of the flyback converter designed with the TPS40210-Q1 device are measured under 5- and 12-V inputs, respectively. The +15-V and -9-V rails are measured separately.

Measure P1:ampl(C4) P2:ampl(C2) P3:min(C2) P4:min(C4) P5:-- P6:-- P7:-- P8:--- Value 16:13 V 5.156 V status status

2.00 V/dav 0 mVorfset 2.00 V/dav 10.00 V/dav 1

Figure 55. Start-up Waveform of the 15-V Rail With V<sub>IN</sub> = 5 V and no Load (Bias Supply With TPS40210-Q1)

From top to bottom: CH2: input voltage 2 V/div, CH4: output voltage 10 V/div, 50 ms/div

| Measure | P1:ampl(C4) | P2:ampl(C2) | P3:min(C2) | P4:min(C4) | P5:--- | P6:--- | P7:--- | P8:--- |

Figure 56. Start-up Waveform of the -9-V Rail With  $V_{\rm IN}$  = 5 V and no Load (Bias Supply With TPS40210-Q1)

From top to bottom: CH2: input voltage 2 V/div, CH4: output voltage 5 V/div, 50 ms/div

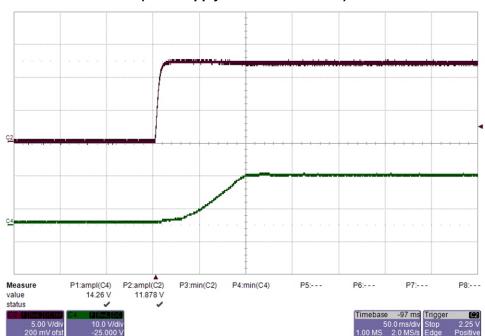

Figure 57. Start-up Waveform of the 15-V Rail With  $V_{\rm IN}$  = 12 V and 180-mA Load (Bias Supply With TPS40210-Q1)

From top to bottom: CH2: input voltage 5 V/div, CH4: output voltage 10 V/div, 50 ms/div

Figure 58. Start-up Waveform of the -9-V Rail With  $V_{\rm IN}$  = 12 V and 180-mA Load (Bias Supply With TPS40210-Q1)

From top to bottom: CH2: input voltage 5 V/div, CH4: output voltage 5 V/div, 50 ms/div

Measure

value

status

P1:ampl(C4)

14.91 V

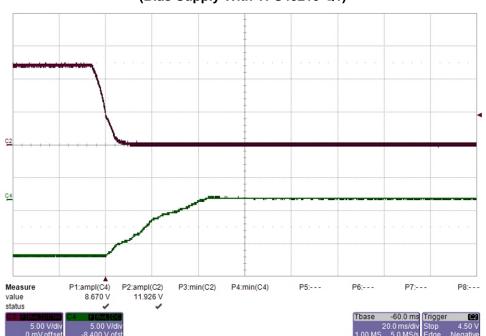

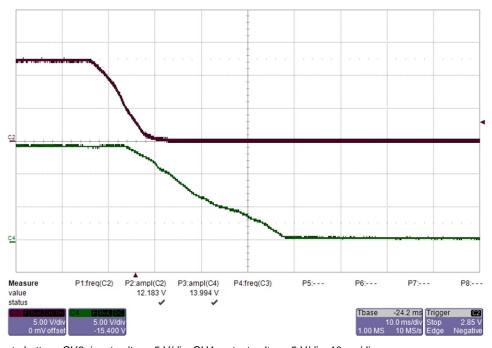

#### 3.2.2.2 Power Down

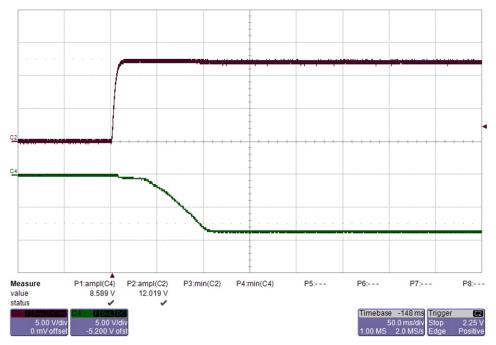

The power down waveforms of the flyback converter designed with the TPS40210-Q1 device are measured under 5- and 12-V inputs, respectively. The +15-V and –9-V rails are measured separately.

C2

Figure 59. Power-Down Waveform of the 15-V Rail With  $V_{IN}$  = 12 V and no Loa (Bias Supply With TPS40210-Q1)

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 10 V/div, 20 ms/div

P3:min(C2)

P2:ampl(C2)

11.922 V

Figure 60. Power-Down Waveform of the -9-V Rail With  $V_{IN}$  = 12 V and no Load (Bias Supply With TPS40210-Q1)

P4:min(C4)

P5:---

P6:---

P8:---

-60.0 ms Trigger

From top to bottom: CH3: input voltage 5 V/div, CH4: output voltage 5 V/div, 20 ms/div

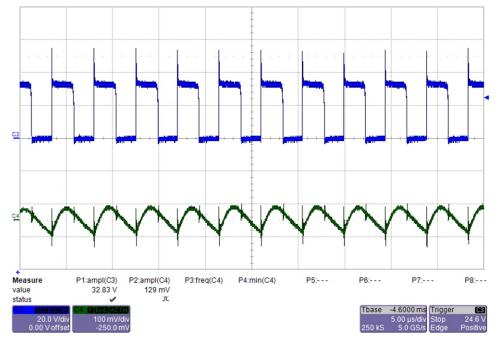

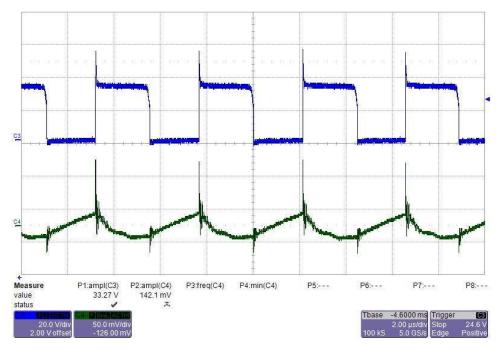

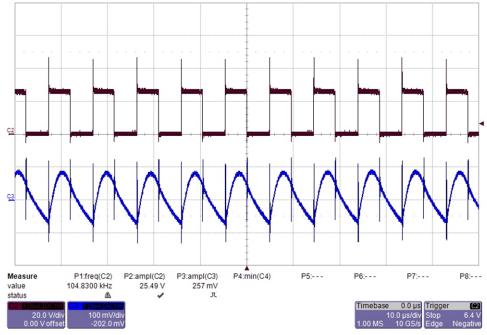

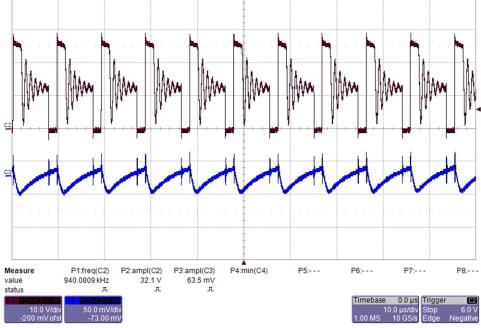

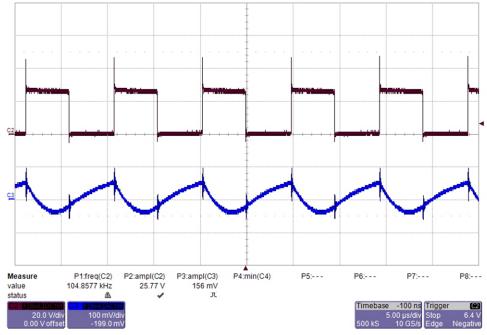

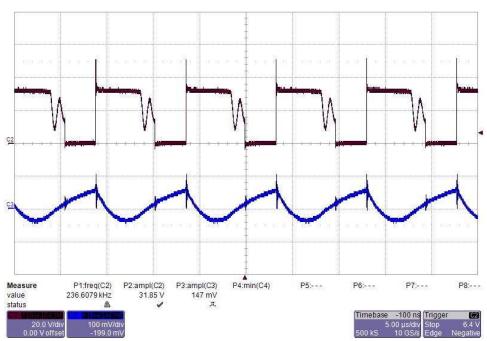

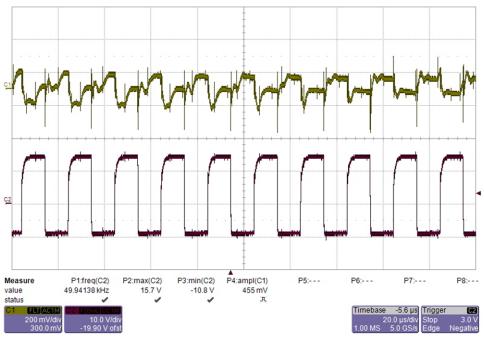

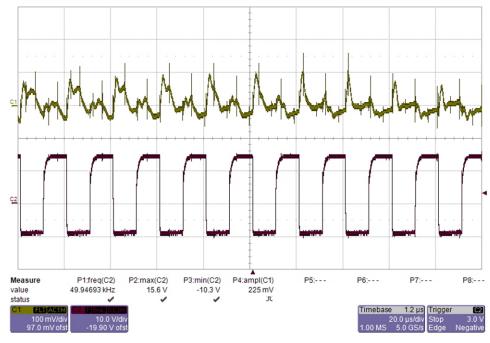

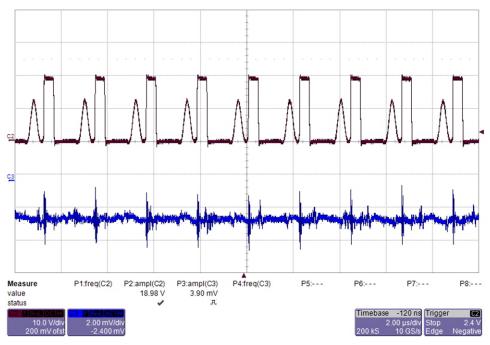

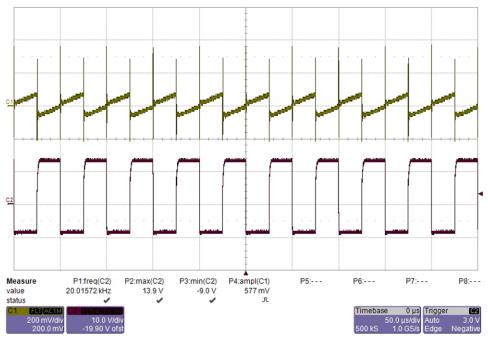

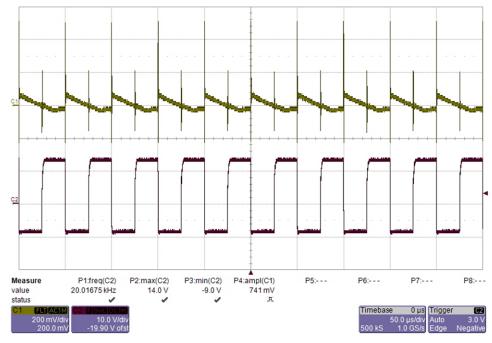

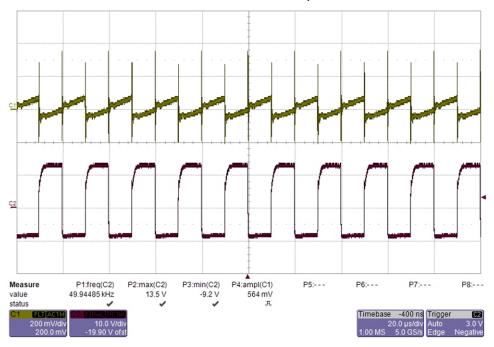

## 3.2.2.3 Switch Node and Output Voltage Ripple

The switch node and output voltage ripple of the flyback converter designed with the TPS40210-Q1 device are measured under 5-, 12-, and 18-V inputs, respectively. The 15-V and –9-V rails are measured separately.

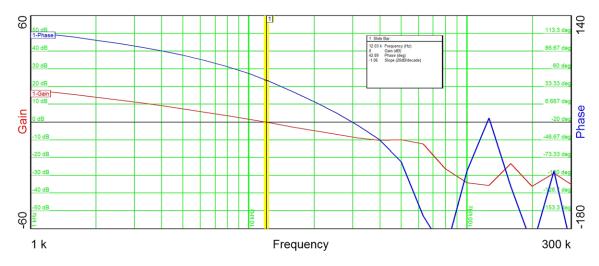

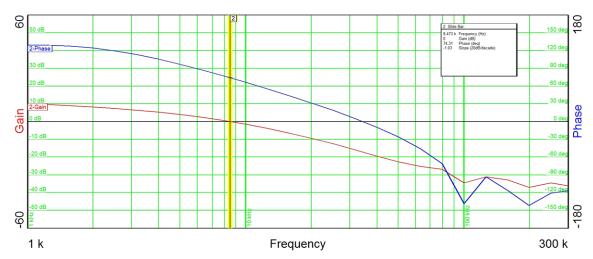

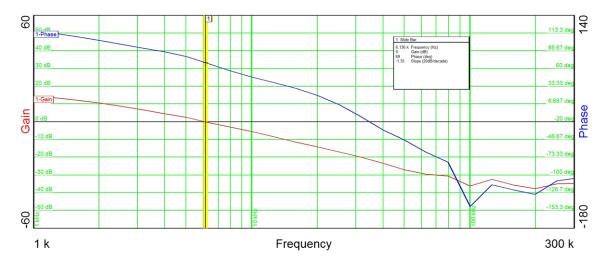

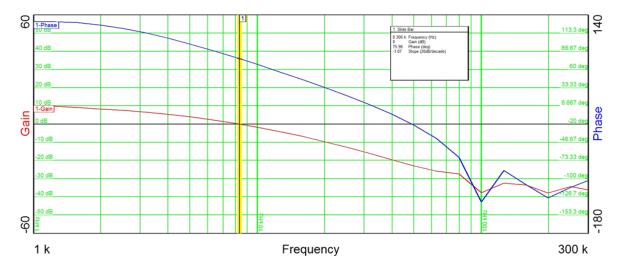

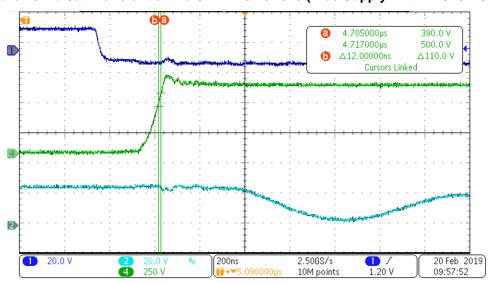

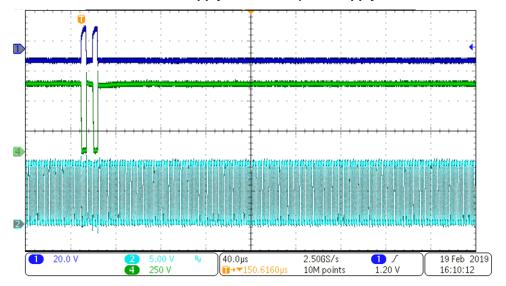

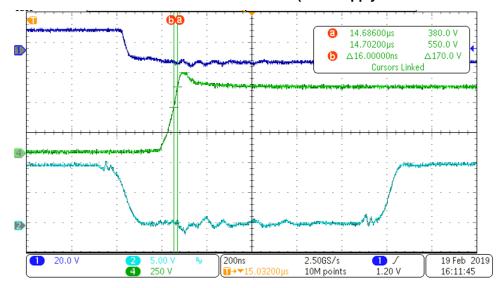

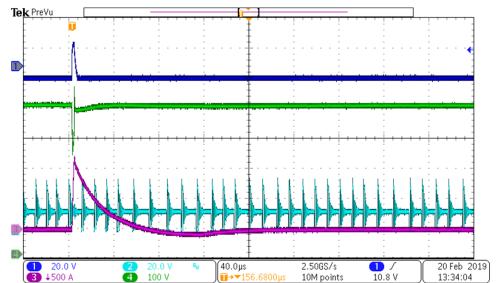

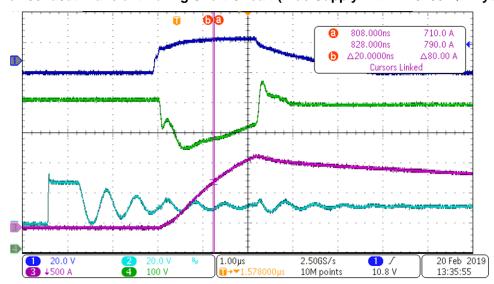

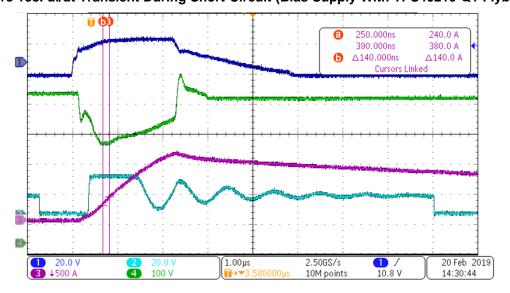

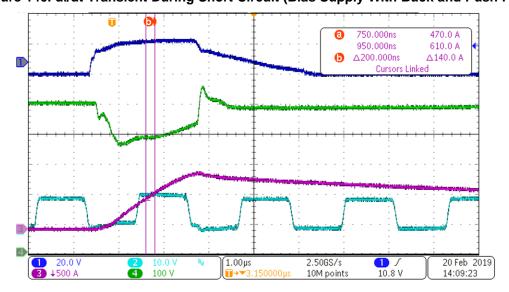

Figure 61. Switch Node and Output Ripple of the 15-V Rail With V<sub>IN</sub> = 5 V and no Load (Bias Supply With TPS40210-Q1)