Application Report SCAA100-February 2009

# Ethernet Clock Generation Using the CDCM6100x

Firoj Kabir and Johnny Lau

ICP - Clock Distribution Circuits

#### ABSTRACT

This application report is a guide for using Texas Instruments CDCM6100x in an Ethernet LAN and WAN application as a clock distributor and clock synthesizer along with measured jitter performance results.

#### Background

Today's networking boxes require clock generation and buffering. Traditional methods involved a clock oscillator and a clock buffer. For LAN applications, a typical 156.25-MHz clock is needed, and for WAN applications a 155.52-MHz clock is used. Due to the low jitter and accuracy needed for these clock oscillators, their cost are high. So how does a designer lower cost but maintain low jitter, high accuracy, and clock buffering in a single solution? The CDCM6100x answers this question.

#### **Functional Description**

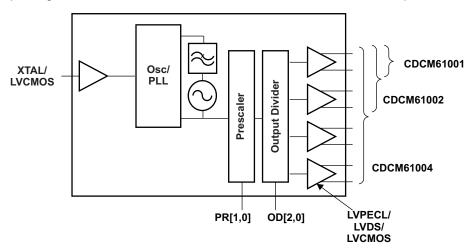

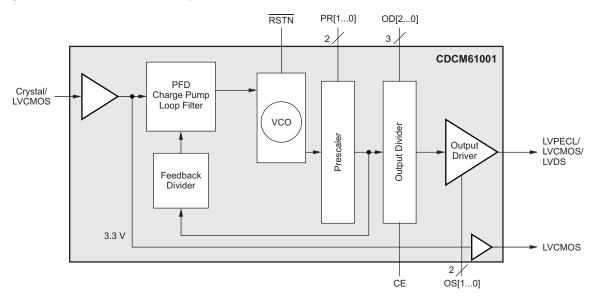

The CDCM6100x is a highly versatile, low-jitter frequency synthesizer which can generate low-jitter clock outputs, selectable among LVPECL, LVDS, or LVCMOS, from a low- frequency crystal or LVCMOS input for a variety of wireline and data communication applications. The CDCM6100x features an on-chip PLL that can be easily configured solely through control pins. The overall output jitter performance is less than 1 ps, rms or 35 ps, pk-pk, thus making the device a perfect choice for use in demanding applications like SONET, Ethernet, Fibre Channel, and SAN. The CDCM6100x is packaged in a small 32-pin, 5-mm  $\times$  5-mm QFN package. The CDCM6100x is available in one-, two-, and four- output versions.

Figure 1. CDCM6100x Functional Block Diagram

1

#### Application

Today's networking LAN and WAN clocking require low jitter (typ < 1ps rms or lower). Typical clock speeds for LAN applications are 625 MHz, 312.5 MHz, 156.25 MHz, and 125 MHz. For WAN applications, 622.08 MHz, 311.04 MHz, 155.52 MHz, and 77.76 MHz are commonly used. For both LAN and WAN systems, the output signal type needed can be differential (LVPECL or LVDS) or single-ended 3.3-V LVCMOS. This application report demonstrates solutions that can meet these needs while also offering a lower cost solution to today's high priced oscillators and clock buffers.

#### **Test Equipment and Setup**

All the measurements discussed in this application report were taken under normal operating conditions using a 3.3-V power supply and at room temperature.

Equipment used:

- Agilent E5052A Signal Source Analyzer

- Power supply

- CDCM6100x EVM

### **Block Diagram and Jitter Test Results of LAN Solutions**

The following four solutions show how to generate networking LAN clocks from the CDCM6100x devices and a low-cost, standard 25-MHz crystal. The 25 MHz is fed into the CDCM6100x VCO core to generate a 625-MHz, 312.5-MHz, 156.25-MHz, or a 125-MHz frequency available to the output buffer. The output signal type can be native LVPECL, LVDS, or LVCMOS. These examples select LVPECL for the output buffers, but also included are some LVDS and LVCMOS measurements at the end of this applications report.

### LAN Solution 1 Block Diagram:

This solution uses the one-output version CDCM61001 to generate 625 MHz. If more outputs are needed, the CDCM61002 and CDCM61004 can supply two or four outputs, respectively.

Figure 2. LAN Block Diagram 1

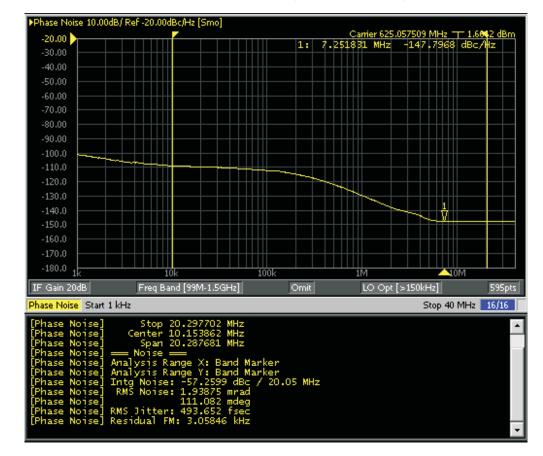

## LAN Solution 1 Jitter Test Results:

## OUT\_0 = 625-MHz LVPEL – RMS Jitter is 494 *f* sec (10 kHz–20 MHz)

## LAN Solution 2 Block Diagram

This solution uses the one output version CDCM61001 to generate 312.5 MHz. If more outputs are needed, the CDCM61002 and CDCM61004 can supply two or four outputs, respectively

Figure 3. LAN Block Diagram 2

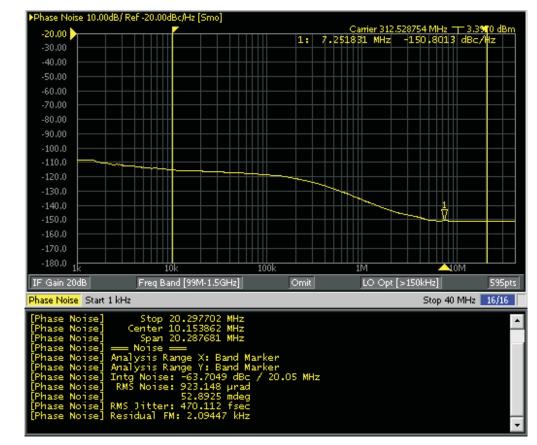

## LAN Solution 2 Jitter Test Results:

## OUT\_0 = 312.5-MHz LVPEL - RMS Jitter is 470 fsec (10 kHz-20 MHz)

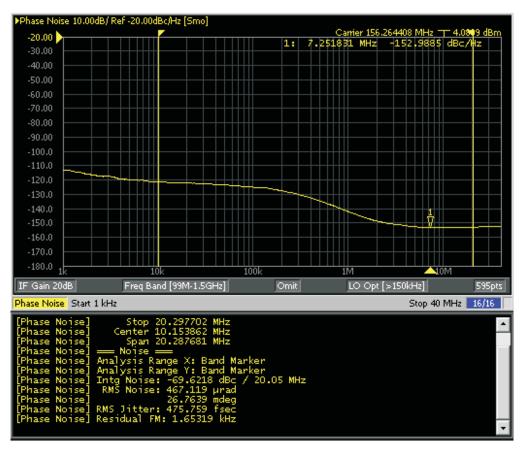

## LAN Solution 3 Block Diagram:

This solution uses the two-output version CDCM61002 to generate two copies of 156.25 MHz. If more or less outputs are needed, the CDCM61001 and CDCM61004 can supply one or four outputs, respectively.

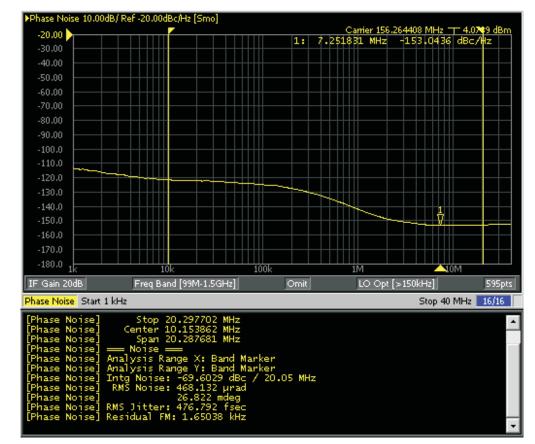

## LAN Solution 3 Jitter Test Results:

## OUT\_0 = 156.25-MHz LVPEL - RMS Jitter is 477 fsec (10 kHz-20 MHz)

## OUT\_1 = 156.25-MHz LVPEL – RMS Jitter is 476 fsec (10 kHz–20 MHz)

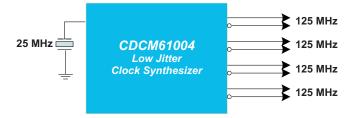

#### LAN Solution 4 Block Diagram:

This solution uses the four-output version CDCM61004 to generate four copies of 125 MHz. If less outputs are needed, the CDCM61001 and CDCM61002 can supply one or two outputs, respectively.

Figure 5. LAN Block Diagram 4

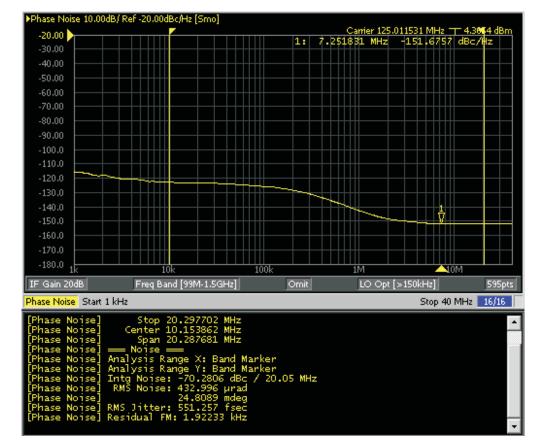

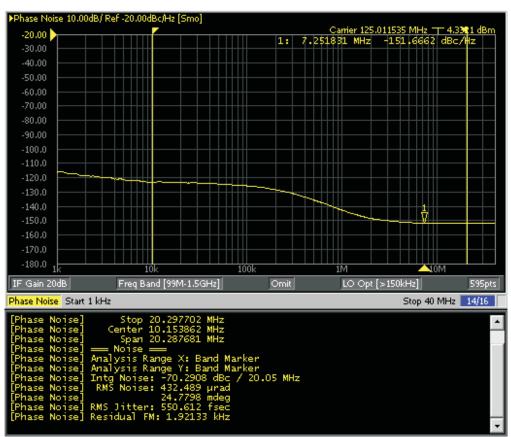

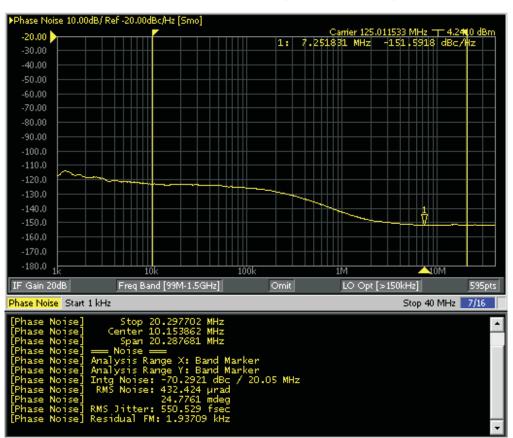

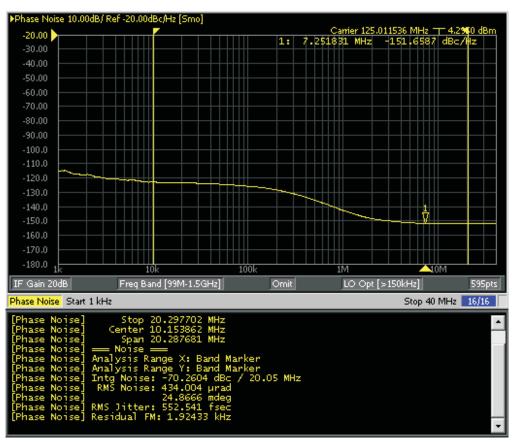

## LAN Solution 4 Jitter Test Results:

## OUT\_0 = 125-MHz LVPECL – RMS Jitter is 551 fsec (10 kHz–20 MHz)

## OUT\_1 = 125-MHz LVPECL - RMS Jitter is 551 *f* sec (10 kHz-20MHz)

## OUT\_2 = 125-MHz LVPECL – RMS Jitter is 551 fsec (10 kHz–20 MHz)

## OUT\_3 = 125-MHz LVPECL – RMS Jitter is 553 fsec (10 kHz–20 MHz)

#### **Block Diagram and Jitter Test Results of WAN Solutions**

The following four solutions show how to generate networking WAN clocks from the CDCM6100x devices and a low-cost, standard 24.8832-MHz crystal. The 24.8832 MHz is fed into the CDCM6100x VCO core to generate a 622.08-MHz, 311-04 MHz, 155-52 MHz, or 77.76-MHz frequency available to the output buffer. The output signal type can be native LVPECL, LVDS, or LVCMOS. These examples select LVPECL for the output buffers.

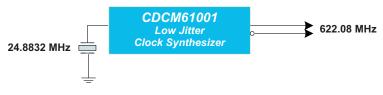

#### WAN Solution 1 Block Diagram:

This solution uses the one output version CDCM61001 to generate 622.08 MHz. If more outputs are needed, the CDCM61002 and CDCM61004 can supply two or four outputs, respectively.

Figure 6. WAN Block Diagram 1

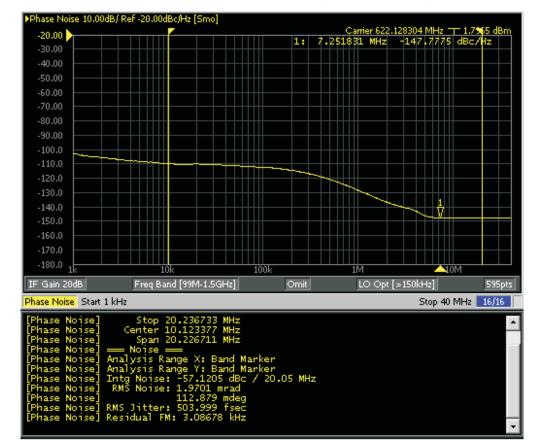

### WAN Solution 1 Jitter Test Results:

## OUT\_0 = 622.08-MHz LVPECL - RMS Jitter is 504 fsec (10 kHz-20 MHz)

#### WAN Solution 2 Block Diagram:

This solution uses the one-output version CDCM61001 to generate 311.04 MHz. If more outputs are needed, the CDCM61002 and CDCM61004 can supply two or four outputs, respectively.

## WAN Solution 2 Jitter Test Results:

## OUT\_0 = 311.04-MHz LVPECL - RMS Jitter is 486 fsec (10 kHz-20 MHz)

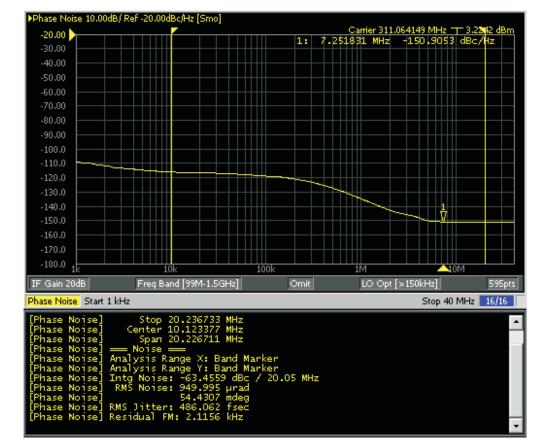

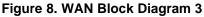

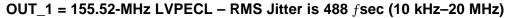

## WAN Solution 3 Block Diagram:

This solution uses the two-output version CDCM61002 to generate two copies of 155.22 MHz. If more or less outputs are needed, the CDCM61001 and CDCM61004 can supply one or four outputs, respectively.

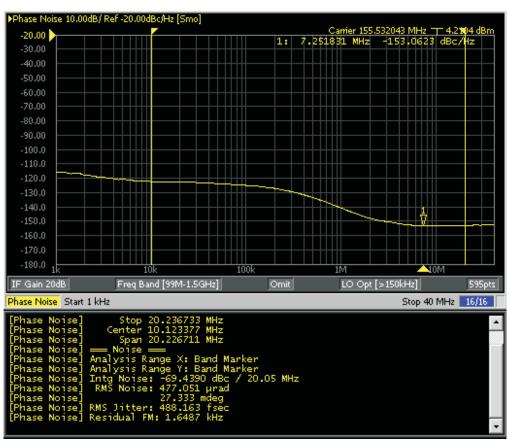

## WAN Solution 3 Jitter Test Results:

## OUT\_0 = 155.52-MHz LVPECL - RMS Jitter is 489 fsec (10 kHz-20 MHz)

#### WAN Solution 4 Block Diagram:

This solution uses the four-output version CDCM61004 to generate four copies of 77.76 MHz. If less outputs are needed, the CDCM61001 and CDCM61002 can supply one or two outputs, respectively.

Figure 9. WAN Block Diagram 4

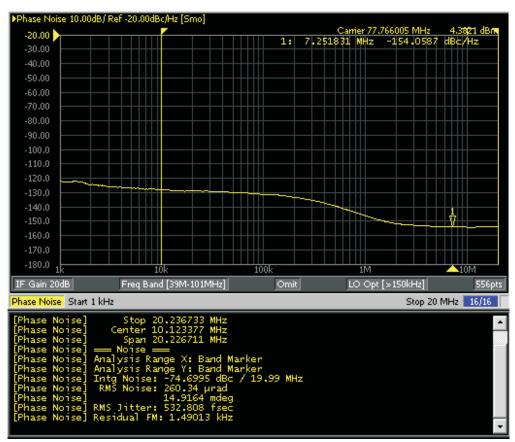

## WAN Solution 4 Jitter Test Results:

## OUT\_0 = 77.76-MHz LVPECL – RMS Jitter is 535 fsec (10 kHz–20 MHz)

Phase Noise 10.00dB/ Ref -20.00dBc/Hz [Smo] Carrier 77.766013 MHz 4.3747 7.251831 MHz -153.9317 dBc/Hz -20.00 17 dBi 1: -40.00 -50.00 -70.00 -80.00 -90.00 -130.0 -140.0 -160.0 -170.0 -180.0 100k 1M 10M IF Gain 20dB Freq Band [39M-101MHz] Omit LO Opt [>150kHz] 556pts Phase Noise Start 1 kHz Stop 20 MHz 16/16 Phase Noise lase MHZ lase Marker Marker lase ø 19.99 MHz dBc ase lase unac ise: 20 RMS Jitte Residual FM : kHz 1

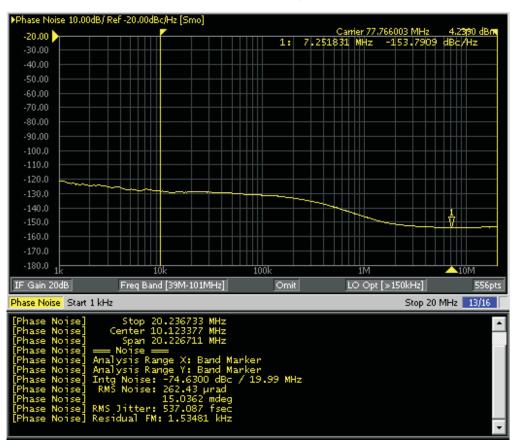

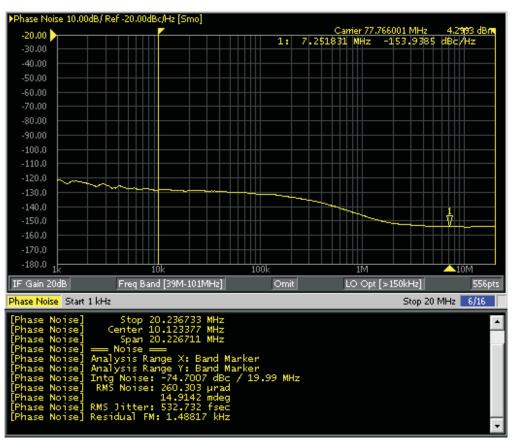

## OUT\_1 = 77.76-MHz LVPECL - RMS Jitter is 533 fsec (10 kHz-20 MHz)

## OUT\_2 = 77.76-MHz LVPECL – RMS Jitter is 537 fsec (10 kHz–20 MHz)

## OUT\_3 = 77.76-MHz LVPECL – RMS Jitter is 533 fsec (10 kHz–20 MHz)

## **Performance Summary**

#### **LAN Configurations**

Performance results of this LAN configuration are:

- CDCM61001 = 625 MHz

OUT\_0 = 625-MHz LVPEL - RMS Jitter is 494 f sec (10 kHz–0 MHz)

- CDCM61001 = 312.5 MHz

OUT\_0 = 312.5-MHz LVPEL RMS Jitter is 470 f sec (10 kHz-20 MHz)

- 3. CDCM61002 = 2 × 156.25 MHz

- OUT\_0 = 156.25-MHz LVPEL **RMS Jitter is 477** f sec (10 kHz-20 MHz)

- OUT\_1 = 156.25-MHz LVPEL *RMS Jitter is 476* f sec (10 kHz-20 MHz)

```

4. CDCM61004 = 4 \times 125 MHz

```

OUT\_0 = 125-MHz LVPECL - **RMS** Jitter is 551 f sec (10 kHz-20 MHz) OUT\_1 = 125-MHz LVPECL - **RMS** Jitter is 551f sec (10 kHz-20MHz) OUT\_2 = 125-MHz LVPECL - **RMS** Jitter is 551 f sec (10 kHz-20 MHz) OUT\_3 = 125-MHz LVPECL - **RMS** Jitter is 553 f sec (10 kHz-20 MHz)

## **WAN Configurations**

Performance results of this WAN configuration are:

1. CDCM61001 = 622.08 MHz

OUT\_0 = 622.08-MHz LVPECL - *RMS Jitter is 504* f sec (10 kHz-20 MHz)

- CDCM61001 = 311.04 MHz OUT\_0 = 311.04-MHz LVPECL - *RMS Jitter is 486 f sec* (10 kHz-20 MHz)

ODOMC1002 - 0.1455 50 MUT

- 3. CDCM61002 = 2 × 155.52 MHz

```

OUT_0 = 155.52-MHz LVPECL - RMS Jitter is 489 f sec (10 kHz-20 MHz)

OUT_1 = 155.52-MHz LVPECL - RMS Jitter is 488 f sec (10 kHz-20 MHz)

4. CDCM61004 = 4 × 77.76 MHz

OUT_0 = 77.76-MHz LVPECL - RMS Jitter is 535 f sec (10 kHz-20 MHz)

OUT_1 = 77.76-MHz LVPECL - RMS Jitter is 533 f sec (10 kHz-20 MHz)

OUT_2 = 77.76-MHz LVPECL - RMS Jitter is 537 f sec (10 kHz-20 MHz)

```

OUT 3 = 77.76-MHz LVPECL – **RMS Jitter is 533** f sec (10 kHz–20 MHz)

#### **Additional Data**

As previously mentioned, the CDCM6100x output type can be configured to LVPECL, LVDS, or LVCMOS. The following are some additional jitter measurements with LVDS and LVCMOS outputs.

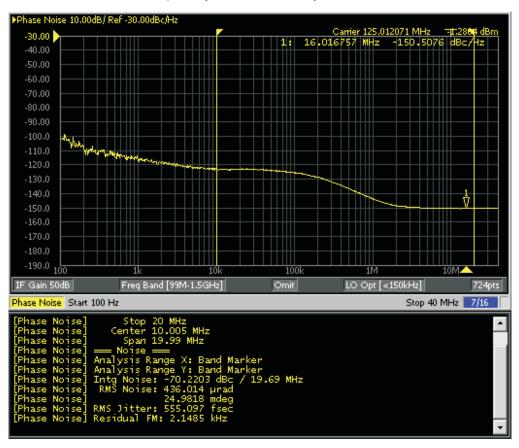

### 125-MHz LVDS – RMS Jitter is 555 fsec (10 kHz–20 MHz)

#### Phase Noise 10.00dB/ Ref -30.00dBc/Hz Carrier 125.012077 MHz -30.00 16,016757 MHz 1: -151.4924 dBc/ -40.00 -50.00 -60.00 -70.00 -80,00 -90.00 -100.0 -120.0 -130.0 -140.0 -150.0 -170.0 -180.0 -190.0 100 1N10M 1 LO Opt [<150kHz] Freq Band [99M-1.5GHz] IF Gain 50dB Omit 724pts Stop 40 MHz 10/16 Phase Noise Start 100 Hz lase MHz 19 Marker Marke 19.69 MHz lase lase unad lase RMS Jitter: Residual EM : 1,91899 kH7 lase

## 125-MHz LVCMOS – RMS Jitter is 539 fsec (10 kHz–20 MHz)

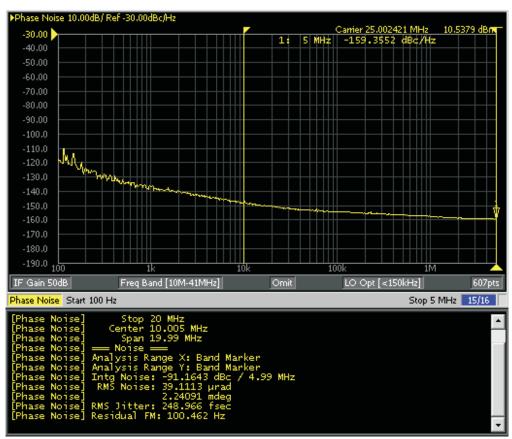

## **Crystal Bypassed Output**

The CDCM6100x also has a unique feature that is worth noting. The device includes a bypassed output of the crystal frequency that is LVCMOS. OSC\_OUT is an LVCMOS output that can be used in test mode to monitor proper loading of the input crystal to achieve the necessary crystal frequency with least error. This bypassed output is only available when the main outputs are selected on the LVPECL level. The output buffer is disabled during VCO calibration and is enabled only after calibration is complete. A 25-MHz input crystal was used in these examples.

## 25-MHz LVCMOS – RMS Jitter is 249 fsec (10 kHz–5 MHz)

## Conclusion

The CDCM6100x performance meets today's networking frequencies and low-jitter requirements <1 ps rms. It is a simple hardware configurable device that requires no preprogramming. The CDCM6100x is offered in a 32-pin, 5-mm  $\times$  5-mm QFN package. This single, 3.3-V device can replace the functionality of expensive oscillators and buffers. The CDCM6100x also offers an additional LVCMOS output at crystal frequency.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated