# Designing With the TLC320AC01 Analog Interface for DSPs

*SLAA006 May* 1995

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

# Contents

# Title

| 1.1 Overview of Device       1         2 ANALOG INPUT       3         2.1 Signal-to-Noise and Signal-to-Distortion Measurements       3         2.2.1 Noise Considerations       3         2.2.1 Noise Considerations       3         2.2.2 V <sub>MID</sub> Referenced Input Circuit Configuration       4         2.2.3 O-V Referenced Input Circuit Configuration       4         2.2.4 Gain Control       5         2.3 Layout and Grounding       6         2.4 Power Supply       6         2.5 Sampling Rate and Filters       6         2.5.1 High-Pass Filter       7         3 ANALOG OUTPUT       8         3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.3 Register 1 (A Register)       14                                                          | 1 | INTRODUCTION                    | ••• | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------|-----|----|

| 2.1 Signal-to-Noise and Signal-to-Distortion Measurements32.2 Input Preamp Design32.2.1 Noise Considerations32.2.2 V <sub>MID</sub> Referenced Input Circuit Configuration42.2.3 O-V Referenced Input Circuit Configuration42.2.4 Gain Control52.3 Layout and Grounding62.4 Power Supply62.5 Rampling Rate and Filters62.5 Unitage Swipply63 ANALOG OUTPUT83.1 Signal-to-Noise and Signal-to-Distortion Ratio83.2 Voltage Swing and PSRR83.3 (Sin x)/x Correction94 DIGITAL DESIGN CONSIDERATIONS104.1.1 Maximum Clock Rate104.1.3 Edge Timing104.1.3 Edge Timing114.3.3 Calculation of Interface Component Values134.4 Programming144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifter Gain Select Register)154.5.6 Register 1 (A Register)154.5.7 Register 6 (Digital Configuration Register)154.5.7 Register 7 (Frame-Sync Delay Register)154.5.7 Register 7 (Change Sync Number Register)154.5.7 Register 7 (Change Sync Number Register)15 <tr< td=""><td></td><td>1.1 Overview of Device</td><td>•••</td><td>1</td></tr<> |   | 1.1 Overview of Device          | ••• | 1  |

| 2.1 Signal-to-Noise and Signal-to-Distortion Measurements32.2 Input Preamp Design32.2.1 Noise Considerations32.2.2 V <sub>MID</sub> Referenced Input Circuit Configuration42.2.3 O-V Referenced Input Circuit Configuration42.2.4 Gain Control52.3 Layout and Grounding62.4 Power Supply62.5 Rampling Rate and Filters62.5 Unitage Swipply63 ANALOG OUTPUT83.1 Signal-to-Noise and Signal-to-Distortion Ratio83.2 Voltage Swing and PSRR83.3 (Sin x)/x Correction94 DIGITAL DESIGN CONSIDERATIONS104.1.1 Maximum Clock Rate104.1.3 Edge Timing104.1.3 Edge Timing114.3.3 Calculation of Interface Component Values134.4 Programming144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifter Gain Select Register)154.5.6 Register 1 (A Register)154.5.7 Register 6 (Digital Configuration Register)154.5.7 Register 7 (Frame-Sync Delay Register)154.5.7 Register 7 (Change Sync Number Register)154.5.7 Register 7 (Change Sync Number Register)15 <tr< td=""><td>2</td><td>ANALOG INPUT</td><td></td><td>3</td></tr<>             | 2 | ANALOG INPUT                    |     | 3  |

| 2.2       Input Preamp Design       3         2.2.1       Niose Considerations       3         2.2.2       Ving Referenced Input Circuit Configuration       4         2.2.3       0-V Referenced Input Circuit Configuration       4         2.2.4       Gain Control       5         2.3       Layout and Grounding       6         2.4       Power Supply       6         2.5       Sampling Rate and Filters       6         2.5.1       High-Pass Filter       7         3       ANALOG OUTPUT       8         3.1       Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2       Voltage Swing and PSRR       8         3.3       (Sin x)/x Correction       9         4       DESIGN CONSIDERATIONS       10         4.1.1       Maximum Clock Rate       10         4.1.2       Synchronization of Negative Rail Generator       10         4.1.3       Reset Considerations       11         4.3.1       Reset Considerations       11         4.3.2       Interface Considerations       11         4.3.3       Reset Considerations       14         4.4       Programming       10         4.5.2                                                                                                                                                      | - |                                 |     |    |

| 2.2.1 Noise Considerations32.2.2 V <sub>MID</sub> Referenced Input Circuit Configuration42.2.3 0-V Referenced Input Circuit Configuration42.2.4 Gain Control52.3 Layout and Grounding62.4 Power Supply62.5 Sampling Rate and Filters62.5.1 High-Pass Filter73 ANALOG OUTPUT83.1 Signal-to-Noise and Signal-to-Distortion Ratio83.2 Voltage Swing and PSRR83.3 (Sin x)/x Correction94 DIGITAL DESIGN CONSIDERATIONS104.1 DSP Serial Interface104.1.2 Synchronization of Negative Rail Generator104.1.3 Edge Timing104.2.4 Hardware Design of TMS320C50 Based DSP System114.3.3 Calculation of Interface Component Values134.4.4 Initialization144.5.7 Register 1 (A Register)144.5.8 Register 2 (B Register)144.5.5 Register 1 (A Register)144.5.6 Register 3 (A' Register)154.5.7 Register 4 (Amplifier Gain Select Register)154.5.7 Register 7 (Grame-Sync Number Register)154.5.7 Register 7 (Grame-Sync Number Register)154.5.7 Register 8 (Grame-Sync Number Register)154.5.7 Register 8 (Frame-Sync Number Register)154.5.7 Register 8 (Frame-Sync Dolay Register)154.5.7 Missi20CS0 Assembler Listing16                                                                                                                                                                     |   |                                 |     |    |

| 2.2.2 V <sub>MID</sub> Referenced Input Circuit Configuration       4         2.2.3 Gain Control       5         2.3 Layout and Grounding       6         2.4 Power Supply       6         2.5 Sampling Rate and Filters       6         2.5.1 High-Pass Filter       7         3 ANALOG OUTPUT       8         3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4.1 Initialization       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 1 (A Register)       15         4.5.7 Register 1 (A Register)       15         4.5.7 Register 5 (Aralog Configuration Register)                                                       |   |                                 |     |    |

| 2.2.3       0-V Referenced Input Circuit Configuration       4         2.2.4       Gain Control       5         2.3       Layout and Grounding       6         2.4       Power Supply       6         2.5       Sampling Rate and Filters       6         2.5.1       High-Pass Filter       7         3       ANALOG OUTPUT       8         3.1       Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2       Voltage Swing and PSRR       8         3.3       (Sin x)/x Correction       9         4       DIGITAL DESIGN CONSIDERATIONS       10         4.1       Atximum Clock Rate       10         4.1.1       Maximum Clock Rate       10         4.1.2       Synchronization of Negative Rail Generator       10         4.1.3       Edge Timing       10         4.1.4       Edge Timing       11         4.3       Battery Operation       11         4.3.1       Interface Interface Component Values       13         4.4       Programming       14         4.3.2       Interface Component Values       13         4.4       Acculation of Interface Component Values       13         4.4.4                                                                                                                                                      |   |                                 |     |    |

| 2.2.4 Gain Control52.3 Layout and Grounding62.4 Power Supply62.5 Sampling Rate and Filters62.5.1 High-Pass Filter73 ANALOG OUTPUT83.1 Signal-to-Noise and Signal-to-Distortion Ratio83.2 Voltage Swing and PSRR83.3 (Sin x)/x Correction94 DIGITAL DESIGN CONSIDERATIONS104.1 DSP Serial Interface104.1.2 Synchronization of Negative Rail Generator104.1.3 Lager Timing104.2.4 Hardware Design of TMS320C50 Based DSP System114.3.3 Calculation of Interface Component Values134.4 Programming144.5.1 Reset Considerations114.5.2 Register Descriptions144.5.3 Register 1 (A Register)144.5.4 Register 1 (A Register)144.5.5 Register 1 (A Register)144.5.6 Register 2 (B Register)144.5.7 Register 1 (A Register)144.5.8 Register 1 (A Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 4 (Amplifier Gain Select Register)154.5.7 Register 5 (Chalog Configuration Register)154.5.7 Register 7 (Frame-Sync Delay Register)154.5.7 Register 7 (Frame-Sync Delay Register)154.5.7 Register 8 (Frame-Sync Delay Register)154.5.7 Register 8 (Chalog Configuration Register)154.5.7 Register 8 (Chalog Configuration Register)154.5.7 Register 7 (Frame-Sync Delay Register) <td< td=""><td></td><td></td><td></td><td></td></td<>                       |   |                                 |     |    |

| 2.3 Layout and Grounding       6         2.4 Power Supply       6         2.5 Sampling Rate and Filters       6         2.5.1 High-Pass Filter       7         3 ANALOG OUTPUT       8         3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.2.4 Hardware Design of TMS320C50 Based DSP System       11         4.3.3 Calculation of Interface Component Values       13         4.4.1 Initialization       14         4.5.2 Register Descriptions       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 7 (Frame-Sync Delay Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15                                           |   |                                 |     |    |

| 2.4 Power Supply       6         2.5 Sampling Rate and Filters       6         2.5.1 High-Pass Filter       7         3 ANALOG OUTPUT       8         3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.3 Battery Operation       11         4.3.3 Claculation of Interface Component Values       13         4.4.4 Initialization       11         4.3.2 Scaludation of Interface Component Values       13         4.4.4 Programming       14         4.5.1 Register 1 (A Register)       14         4.5.2 Register 1 (R Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Analog Configuration Register)       15                                                           |   |                                 |     |    |

| 2.5 Sampling Rate and Filters       6         2.5.1 High-Pass Filter       7         3 ANALOG OUTPUT       7         3 ANALOG outPut       8         3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.2 Hardware Design of TMS320C50 Based DSP System       11         4.3 I Reset Considerations       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Reset Considerations       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       15         4.5.6 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15 <t< td=""><td></td><td></td><td></td><td></td></t<>   |   |                                 |     |    |

| 3 ANALOG OUTPUT83.1 Signal-to-Noise and Signal-to-Distortion Ratio83.2 Voltage Swing and PSRR83.3 (Sin x)/x Correction94 DIGITAL DESIGN CONSIDERATIONS104.1 DSP Serial Interface104.1.1 Maximum Clock Rate104.1.2 Synchronization of Negative Rail Generator104.1.3 Edge Timing104.2 Hardware Design of TMS320C50 Based DSP System114.3 Interfacing to a 3-V DSP Processor114.3.2 Interfacing to a 3-V DSP Processor134.4 Programming144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)154.5.6 Register 3 (A' Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.5.1 Rogister 7 (Frame-Sync Delay Register)154.5.7 Register 8 (Frame-Sync Delay Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.7 Rogister 8 (Frame-Sync Number Register)154.5 Register 8 (Frame-Sync Number Register)154.5 Rugister 8 (Frame-Sync Number Register)154.5 Register 7 (Frame-Sync Delay Register)154.5 Register 8 (Frame-Sync Number Register)154.5 Register 7 (Frame-Sync Delay Register)154.5 Rugister 8 (Frame-Sync Number Register)154.5 Rugister                                           |   |                                 |     |    |

| 3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.1 Pseudo Configuration Register)       15         4.5.6 Register 7 (Fr                        |   | 2.5.1 High-Pass Filter          | ′   | 7  |

| 3.1 Signal-to-Noise and Signal-to-Distortion Ratio       8         3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.1 Pseudo Configuration Register)       15         4.5.6 Register 7 (Fr                        | 2 |                                 |     | Q  |

| 3.2 Voltage Swing and PSRR       8         3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.3.3 Reset Considerations       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.9 Register 8 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Delay Register)       15<                                 | 3 |                                 |     |    |

| 3.3 (Sin x)/x Correction       9         4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.9 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15 <td></td> <td></td> <td></td> <td></td>       |   |                                 |     |    |

| 4 DIGITAL DESIGN CONSIDERATIONS       10         4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.3 Edge Timing       10         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.9 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15                                                         |   |                                 |     |    |

| 4.1 DSP Serial Interface       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.4 Battery Operation       10         4.1.5 Edge Timing       10         4.1.6 Edge Timing       10         4.1.7 Edge Timing       10         4.1.8 Edge Timing       10         4.1.9 Edge Timing       10         4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.4 Edge Timing       10         4.1.7 Battery Operation       11         4.3 Reset Considerations       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       13         4.4 Programming       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 3 (A' Re                                                                                              |   |                                 |     |    |

| 4.1.1 Maximum Clock Rate       10         4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.2 Hardware Design of TMS320C50 Based DSP System       11         4.3 Battery Operation       11         4.3 Battery Operation       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Initialization       14         4.5.2 Register Descriptions       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.1 Programming       15         4.5.2 Register 7 (Frame-Sync Number Register)       15         4.5.3 Register 7 (Frame-Sync Number Register)       15         4.5.4 Register 7 (Frame                        | 4 |                                 |     |    |

| 4.1.2 Synchronization of Negative Rail Generator       10         4.1.3 Edge Timing       10         4.1.3 Edge Timing       10         4.2 Hardware Design of TMS320C50 Based DSP System       11         4.3 Battery Operation       11         4.3 Battery Operation       11         4.3 Lastery Operation       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.5.1 Register Descriptions       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.8 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.5.9 Register 7 (Frame-Sync Number Register)       15         4.5                        |   |                                 |     |    |

| 4.1.3 Edge Timing       10         4.2 Hardware Design of TMS320C50 Based DSP System       11         4.3 Battery Operation       11         4.3 Battery Operation       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.4.1 Initialization       14         4.5 Register Descriptions       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.9 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.6 TLC320AC01/TMS320C50 Demonstration Program       15         4.7 TMS320C50 Assembler Listing       16                                                                                                                                                         |   |                                 |     |    |

| 4.2 Hardware Design of TMS320C50 Based DSP System       11         4.3 Battery Operation       11         4.3 Reset Considerations       11         4.3.1 Reset Considerations       11         4.3.2 Interfacing to a 3-V DSP Processor       11         4.3.3 Calculation of Interface Component Values       13         4.4 Programming       14         4.4.1 Initialization       14         4.5 Register Descriptions       14         4.5.1 Pseudo Register 0 (no-op)       14         4.5.2 Register 1 (A Register)       14         4.5.3 Register 2 (B Register)       14         4.5.4 Register 3 (A' Register)       14         4.5.5 Register 4 (Amplifier Gain Select Register)       15         4.5.6 Register 5 (Analog Configuration Register)       15         4.5.7 Register 6 (Digital Configuration Register)       15         4.5.9 Register 7 (Frame-Sync Delay Register)       15         4.5.9 Register 8 (Frame-Sync Number Register)       15         4.6 TLC320AC01/TMS320C50 Demonstration Program       15         4.7 TMS320C50 Assembler Listing       16                                                                                                                                                                                         |   |                                 |     |    |

| 4.3 Battery Operation114.3.1 Reset Considerations114.3.2 Interfacing to a 3-V DSP Processor114.3.3 Calculation of Interface Component Values134.4 Programming144.4.1 Initialization144.5.1 Register Descriptions144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.6 TLC320AC01/TMS320C50 Demonstration Program16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                 |     |    |

| 4.3.1 Reset Considerations114.3.2 Interfacing to a 3-V DSP Processor114.3.3 Calculation of Interface Component Values134.4 Programming144.4.1 Initialization144.5.1 Register Descriptions144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                 |     |    |

| 4.3.2 Interfacing to a 3-V DSP Processor114.3.3 Calculation of Interface Component Values134.4 Programming144.4.1 Initialization144.5 Register Descriptions144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                 |     |    |

| 4.3.3 Calculation of Interface Component Values134.4 Programming144.4.1 Initialization144.5 Register Descriptions144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                 |     |    |

| 4.4 Programming144.4.1 Initialization144.5 Register Descriptions144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)144.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                 |     |    |

| 4.4.1 Initialization144.5 Register Descriptions144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)144.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                 |     |    |

| 4.5 Register Descriptions144.5.1 Pseudo Register 0 (no-op)144.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 3 (A' Register)144.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                 |     |    |

| 4.5.1Pseudo Register 0 (no-op)144.5.2Register 1 (A Register)144.5.3Register 2 (B Register)144.5.4Register 3 (A' Register)144.5.5Register 3 (A' Register)144.5.6Register 5 (Analog Configuration Register)154.5.7Register 6 (Digital Configuration Register)154.5.8Register 7 (Frame-Sync Delay Register)154.5.9Register 8 (Frame-Sync Number Register)154.6TLC320AC01/TMS320C50 Demonstration Program154.7TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                 |     |    |

| 4.5.2 Register 1 (A Register)144.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 3 (A' Register)144.5.6 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                 |     |    |

| 4.5.3 Register 2 (B Register)144.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 0                               |     |    |

| 4.5.4 Register 3 (A' Register)144.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                 |     |    |

| 4.5.5 Register 4 (Amplifier Gain Select Register)154.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                 |     |    |

| 4.5.6 Register 5 (Analog Configuration Register)154.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                 |     |    |

| 4.5.7 Register 6 (Digital Configuration Register)154.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                 |     |    |

| 4.5.8 Register 7 (Frame-Sync Delay Register)154.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                 |     |    |

| 4.5.9 Register 8 (Frame-Sync Number Register)154.6 TLC320AC01/TMS320C50 Demonstration Program154.7 TMS320C50 Assembler Listing16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                                 |     |    |

| 4.6 TLC320AC01/TMS320C50 Demonstration Program       15         4.7 TMS320C50 Assembler Listing       16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                 |     |    |

| 4.7 TMS320C50 Assembler Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                 |     |    |

| 4.8 Linker Command File: AC01DEMO CMD Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                 |     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.7 TMS520C50 Assembler Listing | ••• | 19 |

| 4.9 Measuring the DAC Filter Response with a White Noise Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                 |     |    |

| 4.10 Example Noise Generator Code Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                 |     |    |

| Title                                     | Page |

|-------------------------------------------|------|

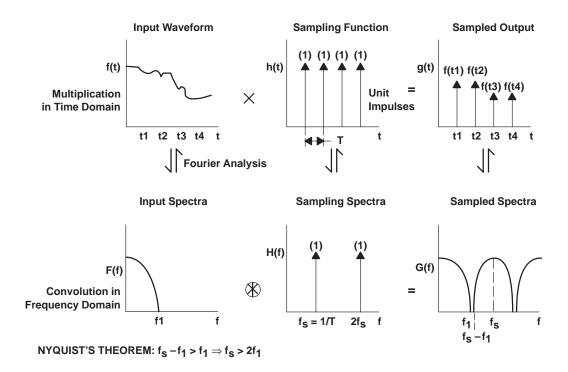

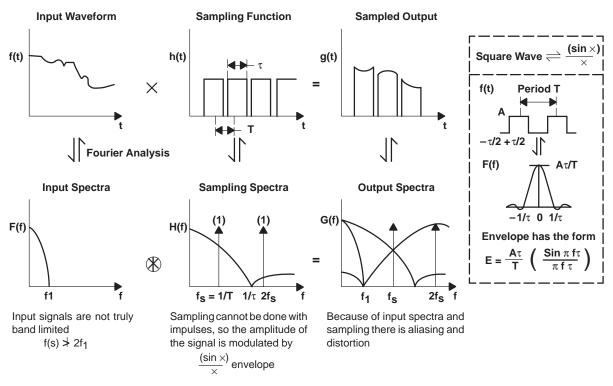

| 5 SAMPLING AND QUANTIZATION – TUTORIAL    | 21   |

| 5.1 Sampling                              |      |

| 5.1.1 Ideal Sampling                      |      |

| 5.1.2 Real Sampling                       |      |

| 5.1.3 Aliasing Effects and Considerations |      |

| 5.2 Theoretical SNR for a 14-Bit Device   |      |

| 5.3 References                            |      |

Contents

# List of Illustrations

| Figure | Title                                            | Page |

|--------|--------------------------------------------------|------|

| 1.     | TLC320AC01 Analog Interface for DSP              | 2    |

| 2.     | ADC Noise and Distortion Measurement             | 3    |

| 3.     | V <sub>MID</sub> Referenced Input Circuit        | 4    |

| 4.     | 0-V Referenced Input Circuit                     | 5    |

| 5.     | Input Circuit for 6 S/W Selectable Gain Settings | 6    |

| 6.     | DAC Noise and Distortion Measurements            | 8    |

| 7.     | Differential to Single Ended Output Circuit      | 9    |

| 8.     | (Sin x)/x Error                                  | 9    |

| 9.     | TLC320AC01 to TMS320C50 Hardware Schematic       |      |

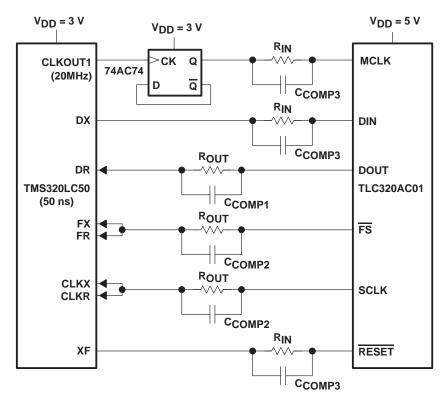

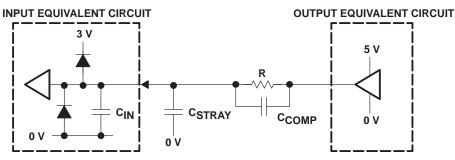

| 10.    | Interfacing to 3-V DSP                           | 13   |

| 11.    | Interfacing to 3-V DSP – Component Values        |      |

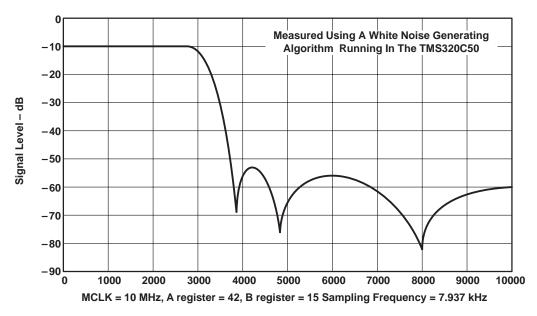

| 12.    | DAC Channel Frequency Response                   | 20   |

| 13.    | Ideal Sampling                                   |      |

| 14.    | Real Sampling                                    |      |

iv

# **1 INTRODUCTION**

This application report was prepared by John Walliker and Julian Daley of University College London. It is based on their experience of using the device as part of a specialized signal processing hearing aid. However the techniques described, for both the analog and digital interfaces, are appropriate for a wide variety of applications.

Measurements of performance quoted in this application note are those achieved with the particular samples and test set-up. For the full device specification see the TLC320AC01 data manual, reference SLAS057A.

Some features of the TLC320AC01 were not used in this design and therefore have not been covered here. They are phase adjustment and the use of multiple devices.

## 1.1 Overview of Device

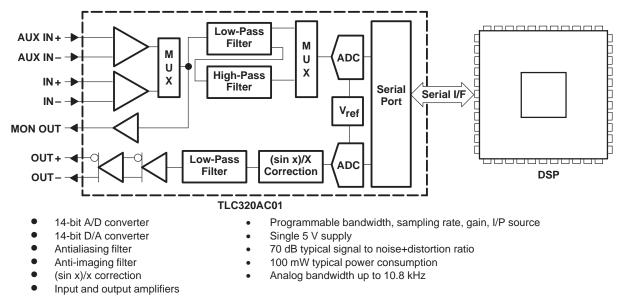

The TLC320AC01 is a 14-bit resolution, audio frequency (approximately 12-kHz bandwidth) analog interface for DSP with integral anti-aliasing and reconstruction filters. It has a synchronous, serial, digital interface designed for ease of connection to many DSP chips.

The internal circuit configuration and the performance parameters, such as input source, sampling rate, filter bandwidths and gain, are determined by writing in control information to eight data registers. These registers are used to set-up the device for a given mode of operation and given application. The ADC channel and the DAC channel operate synchronously and data is transferred in 2's complement format.

The anti-aliasing filter is a switched-capacitor low-pass filter with a sixth-order elliptic characteristic. The high-pass is a single-pole filter, which can be switched out if required. There is a 3-pole continuous-time filter that precedes the switched-capacitor filter to eliminate aliasing caused by sampling in the switched-capacitor filter.

The output-reconstruction filter is also a switched-capacitor low-pass filter with a sixth-order elliptic characteristic and it is followed by a second-order  $(\sin x)/x$  correction filter. This is followed by a three-pole continuous-time filter to eliminate images caused by sampling in the switched-capacitor filter.

There are three basic modes of operation available:

- Stand-alone analog-interface mode, where the TLC320AC01 generates the shift clock and the frame sync for the data transfers and is the only AIC used.

- Master-slave mode, where the master TLC320AC01 generates the shift clock and the frame sync and the rest are slaves to these signals.

- Linear-codec mode, where the shift clock and the frame sync are generated externally and the timing can be any of the standard codec timing patterns.

The TLC320AC01 is available in a standard 28-pin plastic J-lead chip carrier (FN suffix) and a 64-pin plastic-quad-flat-pack (PM suffix) which is only 1,5 mm thick, making it suitable for use in portable systems.

The device has a maximum power dissipation of 110 mW in the active mode and 10 mW in the power down mode. It runs from a single 5-V supply, both for digital and analog circuitry. This is particularly useful for portable equipment, but does require extra care in the design of the analog input and output stages.

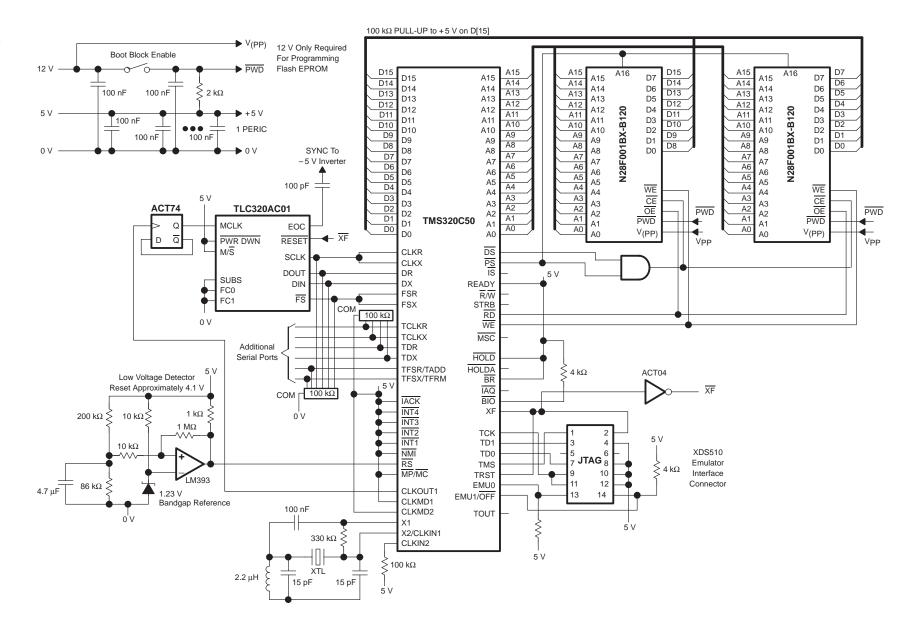

Figure 1. TLC320AC01 Analog Interface for DSP

# 2 ANALOG INPUT

#### 2.1 Signal-to-Noise and Signal-to-Distortion Measurements

With the internal gain of the TLC320AC01 set to 0 dB, a full scale signal corresponds to 6 V peak-peak at the analog input (equivalent to  $6/(2\sqrt{2}) = 2.12$  V RMS).

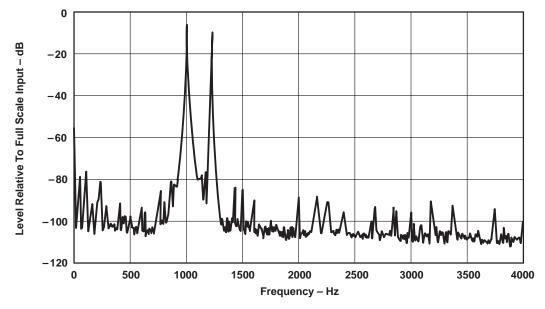

The input signal-to-noise ratio of the TLC320AC01 can be expressed in terms of the number of least significant bits (LSB) of noise present in the digital signal, when both its inputs are connected to  $V_{MID}$ . The RMS value of the noise was measured on the test boards at 0.5 LSB. This corresponds to a noise voltage of approximately 180  $\mu$ V RMS at the input (i.e., a signal-to-noise ratio of 81 dB). The intermodulation measurements are shown in Figure 2. The stimulus was the sum of a 1 kHz signal at -6 dB referred to full scale plus a 1.2 kHz signal at -12 dB referred to full scale. Distortion products are approximately 80 dB down throughout the pass band. The low frequency peaks that can be seen are multiples of 50 Hz interference.

Figure 2. ADC Noise and Distortion Measurement

In the test circuit, the dc accuracy on the samples measured was 14 LSB, equivalent to 5 mV of dc offset.

## 2.2 Input Preamp Design

#### 2.2.1 Noise Considerations

In order that the input preamp does not significantly affect the noise performance of the system, it should produce a noise level at least 6 dB below the TLC320AC01, (i.e., less than 90  $\mu$ V RMS) at the TLC320AC01 input.

Consider the case of a microphone producing 20 mV peak-to-peak at the maximum sound level, a preamp is needed with a gain of 6 V.20 mV = 300 to get a full scale input at the ADC. So the input noise produced by the preamp must be less than 90  $\mu$ V/300 = 300 nV RMS.

For a preamp with a bandwidth of 10 kHz the input noise voltage should be less than

$$\frac{300 \text{ nV}}{\sqrt{10 \text{ kHz}}} = 3 \text{ nV}/\sqrt{\text{Hz}}$$

This noise is made up of the operational amplifier's noise voltage combined with the thermal noise of the equivalent series resistance of the input source. Resistor values need to be carefully chosen, since a 10 k $\Omega$  resistor produces thermal noise of 14 nV/ $\sqrt{\text{Hz}}$  at room temperature. (spectral noise voltage density for a resistor is given by  $\sqrt{4\text{KTR}}$ , where K is Boltzman's constant, T is the absolute temperature and R the resistance). In this case, a 100- $\Omega$  resistor was chosen

(producing a thermal noise of  $1.4 \text{ nV}/\sqrt{\text{Hz}}$  at room temperature). A MAX410 operational amplifier was chosen for the first gain stage as this has a noise voltage of  $2.4 \text{ nV}/\sqrt{\text{Hz}}$ . Noise voltages combine as the root of the sum of the squares, so the total noise is given by:

$$\sqrt{\left(2.4 \text{ nV}^2 + 1.4 \text{ nV}^2\right)} = 2.8 \text{ nV}/\sqrt{\text{Hz}}$$

The gain is split between two operational amplifiers. The first, low noise, operational amplifier configured as a noninverting amplifier with a gain of 100, followed by a second noninverting stage with a gain of three. This second operational amplifier does not need such a low noise voltage specification since its input noise is only being amplified by three. The TLC2272 dual operational amplifier, which has a noise voltage of  $9 \text{ nV}/\sqrt{\text{Hz}}$ , is chosen for its low power consumption, low input offset and well behaved performance under overload. (These operational amplifiers do not exhibit the behavior of BiFETs which can produce phase reversal of the output when the inputs go out of negative common mode range).

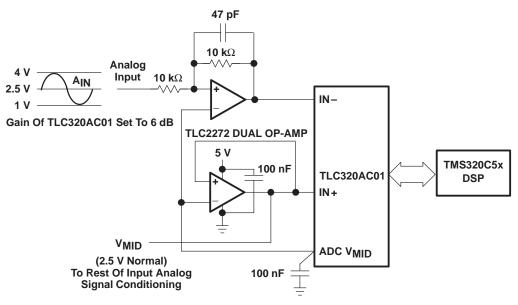

Figure 3. V<sub>MID</sub> Referenced Input Circuit

#### 2.2.2 V<sub>MID</sub> Referenced Input Circuit Configuration

The configuration of the input circuitry requires extra care since all internal signals are referenced to  $V_{MID}$  rather than ground, to allow single supply operation. The PSRR at the internally generated  $V_{MID}$  point is low, so it is important that both the differential inputs are referenced to  $V_{MID}$  with any noise on  $V_{MID}$  appearing equally on both inputs. There are two ways of fulfilling this criterion. The first is to reference the whole input circuit to  $V_{MID}$  (using this as a virtual ground) as shown in Figure 3.

This configuration has the advantage of simplicity although there are some drawbacks. The buffered  $V_{MID}$  point has to be capable of driving the virtual ground and since many operational amplifiers are unhappy driving large capacitive loads this problem must not be overlooked. The TLC2272 is a good choice for this application. The input needs to be referenced to  $V_{MID}$ , which may cause a problem if interfacing to an externally powered, ground referenced signal. In this case the input needs to be ac coupled.

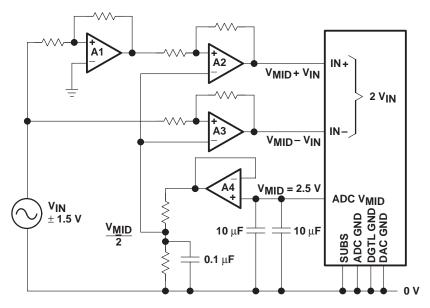

#### 2.2.3 0-V Referenced Input Circuit Configuration

The second method is to level shift the signal just before the ADC inputs as shown in Figure 4. In this circuit, the preamp input is referenced to 0 V. This circuit allows a full range input swing ( $V_{MID} \pm 1.5$  V on each input) for an input signal of  $\pm 1.5$  V. Any noise on  $V_{MID}$  appears equally on both differential inputs and is therefore cancelled. The common mode range of the inputs does not exceed the supply rails, so  $V_{MID}$  noise must not take the input signal outside the supply rails. The eight resistors can conveniently be in one thin film resistor package, giving good matching of resistor values and hence good power supply rejection ratio (PSRR) and dc accuracy. Amplifier A1 must have  $\pm 5$  V or greater power rails but A2 to A4 only need a single 5-V rail.

Figure 4. 0-V Referenced Input Circuit

#### 2.2.4 Gain Control

The internal preamp of the TLC320AC01 has software selectable internal gain of 0 dB, 6 dB or 12 dB plus a squelch mode (-60 dB). With 0 dB gain, plus or minus full scale result is given for a differential input of  $\pm 3$  V. With a single ended input configuration (one input tied to V<sub>MID</sub>), this would not allow plus or minus full scale before the operational amplifiers run out of headroom, so the gain must be set to 6 dB or 12 dB which would give plus or minus full scale with  $\pm 1.5$  V and  $\pm 0.75$  V, respectively, at the TLC320AC01 input.

Most of the input noise is associated with the converter itself, rather than the input amplifiers or multiplexers. Therefore, the signal-to-noise ratio is hardly affected by the chosen input gain. However, it is easier to ensure good rejection of power supply noise coupled through  $V_{\rm MID}$  at low gains.

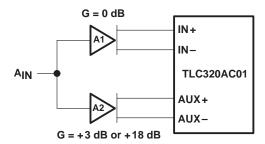

The TLC320AC01 has two sets of differential inputs, IN and AUX IN which can be individually selected (or both selected simultaneously for mixing).

If more gain settings are required, a combination of software switching of input source and input gain coupled with an extra hardware gain stage (see Figure 5) allows six software selectable gain steps as shown in the following table.

| EXTERNAL GAIN 3 dB |                       |                    | EXTERNAL GAIN 18 dB |                       |                    |

|--------------------|-----------------------|--------------------|---------------------|-----------------------|--------------------|

| NORM/AUX<br>INPUT  | INTERNAL GAIN<br>(dB) | TOTAL GAIN<br>(dB) | NORM/AUX<br>INPUT   | INTERNAL GAIN<br>(dB) | TOTAL GAIN<br>(dB) |

| NORM               | 0                     | 0                  | NORM                | 0                     | 0                  |

| AUX                | 0                     | 3                  | NORM                | 6                     | 6                  |

| NORM               | 6                     | 6                  | NORM                | 12                    | 12                 |

| AUX                | 6                     | 9                  | AUX                 | 0                     | 18                 |

| NORM               | 12                    | 12                 | AUX                 | 6                     | 24                 |

| AUX                | 12                    | 15                 | AUX                 | 12                    | 30                 |

Internal Gain Settings 0 dB, 6 dB, 12 dB

#### Figure 5. Input Circuit for 6 S/W Selectable Gain Settings

#### 2.3 Layout and Grounding

Although earthing and PCB layout do not seem to be too critical for this device, it is good practice to ensure that the ground current from sensitive devices such as the ADC does not flow in the same copper as currents from other devices. This means having a central ground point near the device or using power planes with splits where necessary to isolate return current from other devices.

The substrate (SUBS) should be connected to ADC ground. Failure to do so can result in noisy and unstable operation. The circuit should be well decoupled for low and high frequencies to minimize noise injection from the supplies.

# 2.4 Power Supply

With a master clock frequency of 10 MHz, the TLC320AC01 samples typically drew 10 mA at 5 V with default register values. The supply current depends principally on the filter clock frequency. If a negative supply is needed for operational amplifiers, etc., it may be convenient to generate it using a negative voltage converter. Since the negative supply generally draws little current this is a feasible solution and avoids the need for a second battery in portable systems. The ICL7660 needs no external inductors and is available in an 8-pin small outline package. As the internal oscillator of the ICL7660 free runs at about 10 kHz, noise generated from this oscillator can find its way into the ADC input, often beating with the sampling clock creating a whirring type noise. It is however possible to lock this oscillator to the ADC clock by linking the conversion complete signal to the oscillator input on the ICL7660. Coupling via a 100-pF capacitor allows the converter to free-run if the ADC is not operative (e.g., during start-up). Any noise that now gets coupled into the ADC will be the same for each sample, creating a dc result that is much easier to deal with. Alternatively the TLE2682 provides a negative rail generator supplying up to 100 mA (which can be phase locked) plus a dual operational amplifier in one 16-pin wide body SO package).

# 2.5 Sampling Rate and Filters

Within limits, the sampling rate of the device (both ADC and DAC are inherently synchronous) can be set under software control. If the DAC is not used then the ADC can run at up to 43.2k samples/sec. However, if the DAC is to be used the sampling rate must be limited to 25k samples/sec.

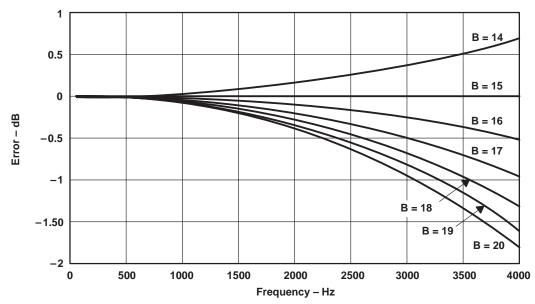

The anti-aliasing filters (switched capacitor type) track the sampling rate by setting the corner frequency of the filter to some fraction of the sampling rate. This allows for the possibility of sub-Nyquist sampling, which should be avoided in most cases. The ratio of sampling rate to anti-aliasing filter corner frequency is set by the B register value (REG<sub>B</sub>). The anti-aliasing corner frequency is set by the A register value (REG<sub>A</sub>) within the TLC320AC01.

Conversion rate is given by:

$$f_{sample} = \frac{f_{MCLK}}{\left(2 \times \text{Reg}_{A} \times \text{Reg}_{B}\right)}$$

The anti-aliasing corner frequency is given by:

$$f_{lp} = \frac{{}^{t}MCLK}{80 \times Reg_{A}}$$

$$\frac{f_{sample}}{f_{lp}} = \frac{40}{Reg_{B}}$$

To satisfy Nyquist's sampling theorem:

$$\frac{f_{sample}}{f_{lp}} \ge 2$$

$$\therefore Reg_B \le 20$$

The default of 18 for the B register gives  $f_{sample}/f_{lp} = 2.2$ . This ensures that energy above the Nyquist frequency is well into the filter's stop band.

The product of the A and B registers must be greater than 65 to allow for 17 serial clock cycles between conversions (16 data bits plus one extra cycle for frame sync in master or standalone mode). The B register must not be less than 10, since the ADC conversion takes 10 B register counts to complete. The A and B registers have a maximum value of 255.

#### 2.5.1 High-Pass Filter

The TLC320AC01 also has a high-pass filter which can be used to attenuate subsonic noise and remove dc offsets. The importance of subsonic noise filtering should not be underestimated. For example: air conditioning systems are a notorious source of low frequency noise and a slamming door can produce extremely high levels of subsonic energy. The filter in the TLC320AC01 has a corner frequency of  $f_S/200$  and a slope of 6 dB per octave. The corner frequency cannot be changed independently of the sampling frequency.

#### **3 ANALOG OUTPUT**

As previously mentioned, the maximum sample rate for the DAC, at 25 kHz, is lower than for the ADC. This limits the bandwidth of the output signal to less than 12.5 kHz.

#### 3.1 Signal-to-Noise and Signal-to-Distortion Ratio

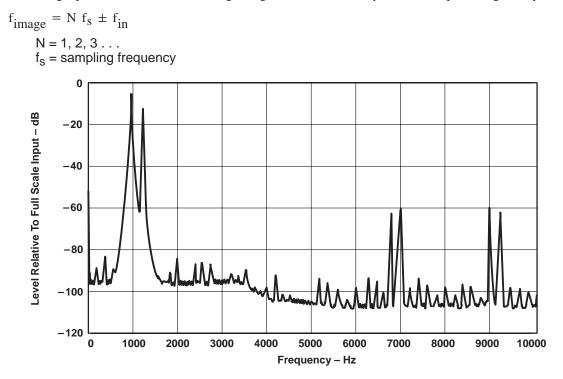

Figure 6 shows the result of intermodulation distortion measurements for the DAC made on the test boards. The noise floor can be seen at approximately -90 dB in the pass band, falling to approximately -108 dB at frequencies above  $f_s/2$ . There are some distortion products in the pass band at approximately -85 dB. The double peaks at approximately 7 kHz and 9 kHz are images of the signal that have been only partially attenuated by the reconstruction filter. Images are the digital to analog equivalents of aliases in analog to digital conversion. They occur at frequencies given by:

Figure 6. DAC Noise and Distortion Measurements

If the images are to large for a given application they can be removed by continuous-time low-pass filtering at the output of the DAC. The size of the images reflects the 45 dB stop-band attenuation of the reconstruction filter.

#### 3.2 Voltage Swing and PSRR

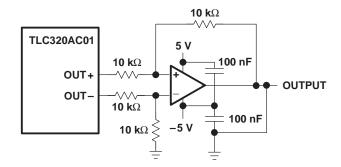

The voltage swing at the differential output is  $\pm 6$  V for a full scale output. There are software selectable attenuators giving outputs of 0 dB, -12 dB and a squelch mode of -60 dB. Although there is not a large improvement in SNR ratio by using a differential output stage, it has the added advantage of increasing the PSRR and allowing level shifting to a ground referenced output without having to ac couple the signal. Using a thin film resistor pack for the differential amplifier gives the well matched resistors needed for good common mode rejection and accurate gain. Using a differential amplifier in this way the PSRR was improved from 49 dB to 53 dB (see Figure 7).

Figure 7. Differential to Single Ended Output Circuit

# 3.3 (Sin x)/x Correction