# TSB41BA3DI / TSB41BA3D Errata

This document is provided to explain an erratum involving 1394 PHY Self-ID reporting on the PHY/LINK interface for the TSB41BA3DI / TSB41BA3DI PHY device.

#### Contents

| 1 | Detailed Description | 2 |

|---|----------------------|---|

| 2 | Overall Impact       | 5 |

| 3 | Workaround           | _ |

Detailed Description www.ti.com

### 1 Detailed Description

When a bus reset occurs, the TSB41BA3DI / TSB41BA3D PHY Self-ID packet is not received by the OHCI link resulting in incorrect values in the OHCI Self-ID register (0 x 68) and missing Self-ID packet data in host memory.

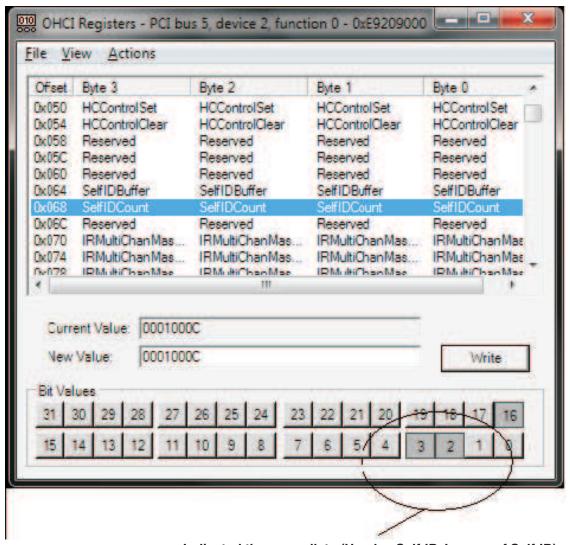

Indicated three quadlets (Header, Self-ID, Inverse of Self-ID) of Self-ID data present in host memory.

Figure 1. TSB82AA2 Self-ID Register With TSB41BA3AI PHY

www.ti.com Detailed Description

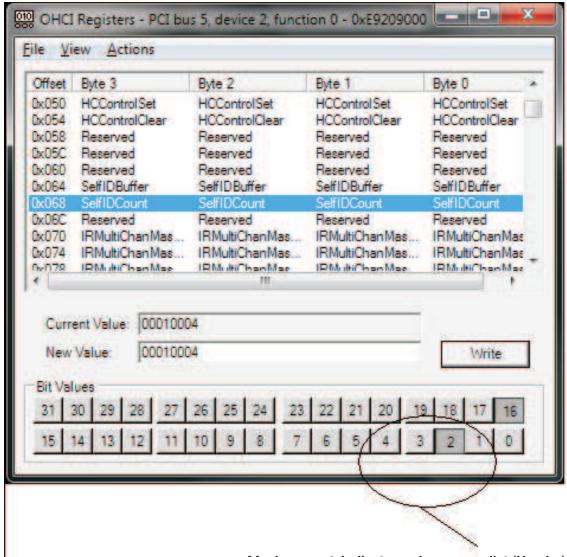

Afer bus reset, indicates only one quadlet (Header) of Self-ID information in host memory.

Figure 2. TSB82AA2 Self-ID Register With TSB41BA3DI / TSB41BA3D PHY

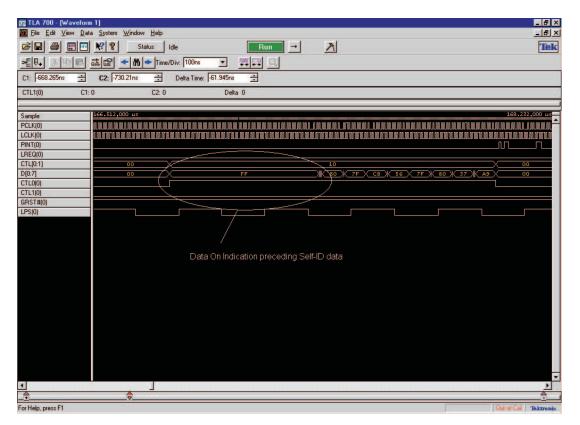

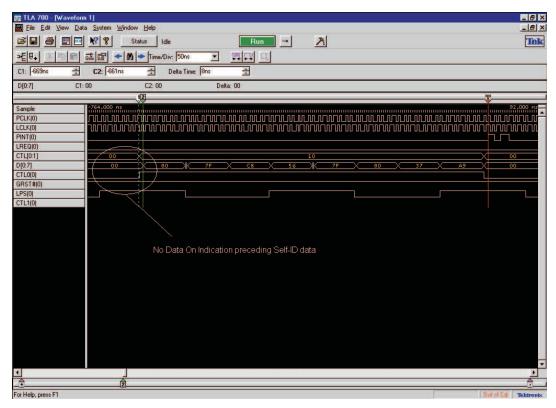

Capturing data on the PHY/LINK interface after a bus reset reveals that both the TSB41BA3AI and TSB41BA3DI / TSB41BA3D do send their respective Self-IDs to the OHCI link. The TSB41BA3AI however sends a Data On indication preceding the Self-ID data, the TSB41BA3DI / TSB41BA3D does not. The sending of the Data On indication is not required per the 1394 specification (Not needed per 1394-1995 specification), but the OHCI link expects the Data On indication to precede the Self-ID, otherwise the data is ignored. The review of the design verified that the OHCI Link does expect to see the Data On indication before the Self-ID.

Detailed Description www.ti.com

Figure 3. PHY/LINK Interface After Bus Reset With TSB41BA3AI

Figure 4. PHY/LINK Interface After Bus Reset With TSB41BA3DI / TSB41BA3D

www.ti.com Overall Impact

## 2 Overall Impact

If the host utilizes memory to build the bus topology, the TSB41BA3DI / TSB41BA3D (host PHY) Self-ID will be missing in the topology. The bus topology map will be incomplete.

#### 3 Workaround

The missing Self-ID from the host PHY (TSB41BA3DI / TSB41BA3D) can be created by reading registers directly from the PHY, then the topology map can be built using the data from the PHY and Link registers.

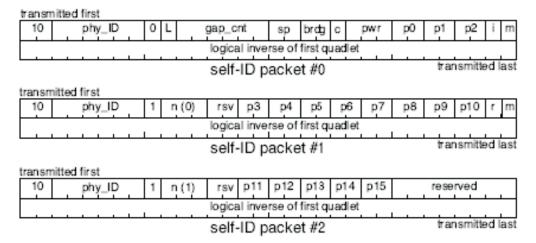

The Self ID contains the following information which can be read from the PHY registers (taken from 1394-1995):

Workaround www.ti.com

## Table 1. Self ID

| Field   | Derived From                          | Comment                                                                                                                                                                                                |

|---------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      |                                       | Self-ID packet identifier.                                                                                                                                                                             |

| phy_ID  | physical_ID                           | physical node identifier of the sender of this packet.                                                                                                                                                 |

| L       | link_active                           | If set, this node has an active Link and Transaction Layer.                                                                                                                                            |

| gap_cnt | gap_count                             | Current value for the PHY_CONFIGURATION.gap_count field of this node.                                                                                                                                  |

|         |                                       | Speed capabilities:                                                                                                                                                                                    |

|         |                                       | 00 98.304 Mbit/s                                                                                                                                                                                       |

| sp      | PHY_SPEED                             | 01 98.304 Mbit/s, 196.608 Mbit/s                                                                                                                                                                       |

|         |                                       | 10 98.304 Mbit/s, 196.608 Mbit/s, and 393.216 Mbit/s                                                                                                                                                   |

|         |                                       | 11 Reserved for future definition                                                                                                                                                                      |

|         |                                       | Worst-case repeater data delay.                                                                                                                                                                        |

|         |                                       | 00 ≤ 144 μs (≈14/BASE_RATE)                                                                                                                                                                            |

| del     | PHY_Delay                             | 01 Reserved                                                                                                                                                                                            |

|         |                                       | 10 Reserved                                                                                                                                                                                            |

|         |                                       | 11 Reserved                                                                                                                                                                                            |

| •       | CONTENDER                             | If set and the link_active flag is set, this nodde is a contender for the bus o:                                                                                                                       |

| С       | CONTENDER                             | isochronous resource manager as described in 8.4.1                                                                                                                                                     |

|         |                                       | Power consumption and source characteristics:                                                                                                                                                          |

|         |                                       | Node does not need power and does not repeat power.                                                                                                                                                    |

|         |                                       | Node is self-powered and provides a minimum of 15 W to the bus.                                                                                                                                        |

|         |                                       | Node is self-powered and provides a minimum of 30 W to the bus.                                                                                                                                        |

|         |                                       | Node is self-powered and provides a minimum of 45 W to the bus.                                                                                                                                        |

| pwr     | POWER_CLASS                           | Node may be powered from the bus and is using up to 1 W.                                                                                                                                               |

|         |                                       | Node is powered from the bus and is using up to 1 W. An additional 2 W is needed to enable the link and higher layers.                                                                                 |

|         |                                       | Node is powered from the bus and is using up to 5 W. An additional 2 W is needed to enable the link and higher layers.                                                                                 |

|         |                                       | Node is powered from the bus and is using up to 9 W. An additional 2 W is needed to enable the link and higher layers.                                                                                 |

|         |                                       | Port status                                                                                                                                                                                            |

|         | NPORT                                 | 11 Connected to child node                                                                                                                                                                             |

| p0p26   | child [NPORT]<br>Connected<br>[NPORT] | 10 Connected to parent node                                                                                                                                                                            |

|         |                                       | 01 Not connected to any other PHY                                                                                                                                                                      |

|         |                                       | 00 Not present on this PHY                                                                                                                                                                             |

| i       | initiated_reste                       | if set, this node initiated the current bus reset (i.e., it started sending a bus_reset signal before it receives one) (optional. If not implemented, this bit shall be returned as a zero)            |

| m       | more_packets                          | If set, another self-ID packet for this node will immediately follow (i.e., is this bit is set an the next self-id packet received has a different phy_ID, then a self-id packet was lost)             |

| n       |                                       | Extended self-ID packet sequence number (0 through 2, corresponding to self-ID packets #1 through #3). If n has a value of 3 through 7, then the rsv.pa_ph.r and m fields in figure 4.18 are reserved. |

| r.rsv   |                                       | Reserved for future definition. set to zeros.                                                                                                                                                          |

Sample code is provided in the specification regarding the generation of Self-ID.

www.ti.com Revision History

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | Changes from Original (December 2009) to A Revision                   |  |  |  |

|----|-----------------------------------------------------------------------|--|--|--|

| •  | Changed TSB41BA3DI to: TSB41BA3DI / TSB41BA3D throughout the document |  |  |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated