# TPS2384 PoE Firmware Version 2.4

# User's Guide

Literature Number: SLVU195 June 2007

2

# **Contents**

| Prefa | ace  |                                                        |

|-------|------|--------------------------------------------------------|

| 1     | TPS2 | 2384 PoE Firmware Version 2.4                          |

|       | 1.1  | Overview                                               |

|       |      | 1.1.1 Firmware Features and Support                    |

|       |      | 1.1.2 Passive Component Values                         |

|       | 1.2  | Firmware Design                                        |

|       |      | 1.2.1 Reset, Idle                                      |

|       |      | 1.2.2 Discovery                                        |

|       |      | 1.2.3 Discovered, Classify                             |

|       |      | 1.2.4 RampUp                                           |

|       |      | 1.2.5 Power Up –DC Disconnect                          |

|       |      | 1.2.6 Power Up – AC Disconnect                         |

|       |      | 1.2.7 Ramp Down/Fault States                           |

|       | 1.3  | Host Interface Protocol                                |

|       |      | 1.3.1 Command Overview                                 |

|       |      | 1.3.2 Transactions: Host Controller to Power Subsystem |

|       |      | 1.3.3 Information Request                              |

|       |      | 1.3.4 Transactions: Power Subsystem to Host Controller |

|       |      | ·                                                      |

| 2     |      | ilization                                              |

|       | 2.1  | Overview                                               |

|       | 2.2  | Sequence of Events                                     |

|       | 2.3  | Detail40                                               |

| 3     | AC a | nd DC Disconnect4                                      |

|       | 3.1  | DC Disconnect                                          |

|       | 3.2  | AC Disconnect                                          |

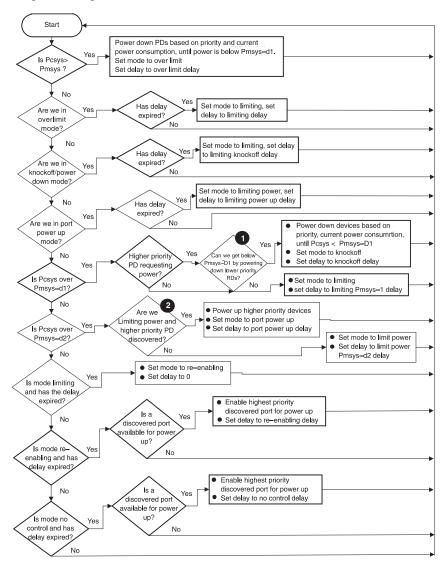

| 4     | Powe | er Management4                                         |

|       | 4.1  | Overview                                               |

|       |      | 4.1.1 Available Power - Pmsys                          |

|       |      | 4.1.2 Power Management Configuration                   |

|       |      | 4.1.3 Disabling Power Management                       |

|       | 4.2  | Definitions and Formulas                               |

|       | 4.3  | System Parameters                                      |

|       | 4.4  | State Definitions                                      |

|       | 4.5  | Design Flow                                            |

|       | 4.6  | Pseudo-Code                                            |

|       | 4.7  | Power Management and Port Mapping48                    |

| _     |      |                                                        |

| 5     | Port | Mapping                                                |

| 6     | Lega | cy Detection5                                          |

|       | 6.1  | Supported Legacy Devices5                              |

|       | 6.2  | Legacy Device Characteristics 5                        |

|       | 6.3  | Signatures and Algorithm 5                             |

|       |      | 6.3.1 Voltage Before Discovery                         |

|   |      | 6.3.2 Discovery Currents                             | 52 |

|---|------|------------------------------------------------------|----|

|   |      | 6.3.3 Voltage Before and During Constant Current     | 52 |

|   | 6.4  | Resistive and Capacitive Ranges                      | 53 |

| 7 | Soft | ware Download                                        | 55 |

|   | 7.1  | Introduction                                         | 55 |

|   | 7.2  | The Relationship Between BSL and the PoE-Application | 55 |

|   | 7.3  | Flash Programming Procedure                          | 56 |

|   |      | 7.3.1 Messages                                       | 56 |

|   |      | 7.3.2 Clear Application                              | 56 |

|   |      | 7.3.3 Clear Information                              | 56 |

|   |      | 7.3.4 Receive Data Block                             | 57 |

|   | 7.4  | Detailed Programming Sequence                        | 57 |

| 8 | Mod  | ule Configuration                                    | 59 |

|   | 8.1  | Introduction                                         | 59 |

|   | 8.2  | Module Default Configuration                         | 60 |

|   | 8.3  | Module Configuration Examples                        |    |

|   |      | 8.3.1 GUI Support                                    |    |

|   |      |                                                      |    |

# **List of Figures**

| 1-1  | PoE System Block Diagram (24-port system) | . 9 |

|------|-------------------------------------------|-----|

| 1-2  | Firmware Port State Machine Overview      | 12  |

| 1-3  | Reset, Idle States Details                | 13  |

| 1-4  | Reset, Idle States Details                | 14  |

| 1-5  | Discovered, Classify States Detail        |     |

| 1-6  | Ramp up States Detail                     |     |

| 1-7  | DC Disconnect States Detail               | 19  |

| 1-8  | AC Disconnect Waveforms                   |     |

| 1-9  | AC Disconnect States Detail               |     |

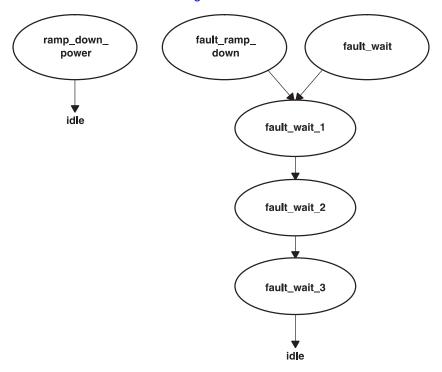

| 1-10 | Ramp Down/Fault States Detail             |     |

| 4-1  | Power Management Algorithm                | 46  |

|      | List of Tables                            |     |

|      | List of Tables                            |     |

| 1-1  | Reference Design Passive Component Values | 11  |

| 1-2  | Host Interface Protocol Commands          | 25  |

| 1-3  | Reset Message Format                      | 26  |

| 1-4  | System Write Message Format               | 28  |

| 1-5  | Port Write Message Format                 | 30  |

| 1-6  | Save/Restore Configuration Message Format | 31  |

| 1-7  | Program Controller Message Format         | 32  |

| 1-8  | Information Request Message Format        | 32  |

| 1-9  | Acknowledge Message Format                | 33  |

| 1-10 | System Read Message Format                | 34  |

| 1-11 | Power Read Message Format                 | 35  |

| 1-12 | System Info Message Format                | 35  |

| 1-13 | Port Read Message Format                  | 36  |

| 1-14 | All Ports Status Message Format           | 37  |

| 1-15 | Port Enables Message Format               | 38  |

| 4-1  | Power Management Port Configuration.      |     |

| 4-2  | Power Management Terms and Definitions    | 44  |

| 4-3  | Power Management State Definition Table   | 45  |

| 6-1  | A/D Ranges for Legacy PDs                 |     |

| 7-1  | Clear Application Message Format          | 56  |

| 7-2  | Clear Information Message Format          |     |

| 7-3  | Receive Data Block Message Format         |     |

| 7-4  | Flash Programming Sequence                |     |

| 8-1  | I2C Addressing Recommendations            |     |

# Read This First

This manual contains information that enables customers to use firmware for the MSP430 that supports the TPS2384 Power Controller device from Texas Instruments.

This guide is a functional and design description of the firmware, and describes its use on the TPS2384 reference system.

Use of this firmware and GUI is bound by the included Software License Agreement located in this folder.

#### **Related Documentation from Texas Instruments**

Documents related to Power over Ethernet firmware for the TPS2384 are:

- 1. Quad Ethernet Power Sourcing Equipment Power Manager (TPS2384 PSE data sheet ) (SLUS634)

- 2. TPS2384 User's Guide (User's Guide for the TPS2384 Reference Design) (SLVU126)

- PSE Controller Interface Control (Design guidelines for MSP430 controller for use with TPS23284 PSE) (SLUA328)

- 4. Firmware release 2.4 for the TPS2384 PSE (Release Notes)

- 5. Power Over Etherner Power Sourcing Equipment Software License Agreement

#### If You Need Assistance

For assistance with Power over Ethernet firmware and related issues, contact your local Texas Instruments sales representative.

# TPS2384 PoE Firmware Version 2.4

#### 1.1 Overview

The TPS2384 PSE is a 4-channel Power-over-Ethernet (PoE) Power Sourcing Equipment (PSE) manager. The TPS2384 manages power distribution to powered devices (PDs) over Ethernet cabling according to the IEEE 802.3af specification. The TPS2384 can be used in one of two modes: *auto mode* or *port management (manual) mode*.

In auto mode, the TPS2384 provides basic IEEE 802.3af-compliant power to PDs over a RJ-45 Ethernet physical interface. It automatically detects, classifies and powers ports, according to this standard. The TPS2384 is a standalone device in auto mode, and does not require any type of controller.

Port-management or manual mode allows more control over the PSE so that additional functionality can be provided by the PoE subsystem. In manual mode, the TPS2384 works in conjunction with a MSP430 microcontroller that provides all the instructions to the TPS2384 for the various states of device discovery and powering. Manual-mode functionality such as Power Management, Legacy Device Detection and other features are described later in this document. The remainder of this document describes the manual mode operation of the PoE system with the MSP430 controller.

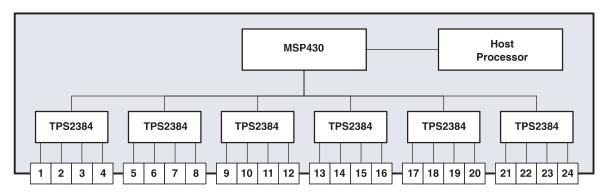

One MSP430 microcontroller can control up to 12 TPS2384s simultaneously, for a total of 48 ports in a system. The diagram below shows a simplified block diagram for a 24-port system with a MSP430 microcontroller. The MSP430 interfaces to the TPS2384 devices through a standard I<sup>2</sup>C bus, where the MSP430 is the bus master. The MSP430 interfaces to the host controller either through RS-232 or I<sup>2</sup>C.

Figure 1-1. PoE System Block Diagram (24-port system)

The MSP430 lets system designers manage many PoE controllers in one system with cost, power, and space constraints. In a switch, it offloads the low-level device specific tasks and power management responsibilities from the CPU.

For more information on Texas Instruments TPS2384 PoE controller and associated firmware, see the product pages at:

http://focus.ti.com/docs/prod/folders/print/tps2384.html

This User's Guide describes the content, design, and use of this firmware.

#### 1.1.1 Firmware Features and Support

The MSP430 firmware supports the TPS2384 PSE in port-management mode, providing a number of features in a PoE system.

The firmware supports the following system configurations and devices:

- TPS2384 PSE controller, revision G

- Firmware runs on the MSP430F148 or MSP430F169 microcontroller on the TPS2384 Reference Design

- The firmware supports modules and discreet solutions with the TPS2384 that include a port capacitor between the P and N pins with a value of 220 nF. If the module or discreet solution contains a port capacitor of a different value, the firmware will not detect devices reliably and will be non-compliant with IEEE 802.3al.

- The firmware supports any number of ports between 4 and 48 that are a multiple of 4. (1–12 TPS2384 4-channel devices)

- The firmware supports PoE modules from a number of vendors that contain the TPS2384 4-channel PSE.

- The system supports either an RS-232 or I<sup>2</sup>C inteface between the MSP430 and the host. If a RS-232 interface is used, then a MSP430F148 or MSP430F169 controller will work. If an I<sup>2</sup>C interface is used, then the MSP430F169 controller must be used.

- The reference design also comes with a **GUI** that can be used for configuration and control of the application on the reference design.

The firmware supports the following features:

- √ Fully compliant with IEEE802.3af Power-over-Ethernet specification

- √ Device Discovery and Classification

- √ AC or DC disconnect

- √ Power Management

- √ Legacy Device Detection

- √ Logical-to-Physical Port Mapping

- √ Save-to-Flash and Restore-Factory-Defaults

- √ Firmware Download Support

10

#### 1.1.2 Passive Component Values

The TPS2384 device has several passive components that can be used with it that affect the system in different ways. The software was designed to work with the specific component values shown in Table 1-1. If a system is designed using a different value for the given components, then the software may not work perfectly and may need to be modified for the specific application.

**Table 1-1. Reference Design Passive Component Values**

| Device                     | Location                                                                                     | Purpose                                                                                                                                             | Value<br>Supported by<br>Unmodified<br>Firmware |

|----------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Port Capacitor             | Between the P and N pins on each TPS2384 port                                                | Controls the power ramp-up and ramp-down rates. (According to the IEEE 802.3af specification, a wide range of port capacitance values may be used.) | 220 nF                                          |

| AC Disconnect<br>Capacitor | There is a capacitor between the AC high and AC low signals (on the other side of a switch). | Controls the characteristics of the AC Disconnect waveform (frequency, etc.)                                                                        | 68 μF/100V                                      |

See the data sheet on the TPS2384 and the PoE controller interface control document in the *Related Information* section above for more information.

#### 1.1.2.1 Port Capacitor

There is a port capacitor between the P and N pins on each port of the TPS2384. This controls the rate at which power ramp up and down happens. According to the IEEE 802.3af specification, there is a wide range of port capacitance that is allowed to be used here.

The firmware for the MSP430 that supports the TPS2384 is written to assume a value of 220 nF for this port capacitor. Other values for the port capacitor will require customization of the firmware.

#### 1.1.2.2 AC Disconnect Capacitor

There is a capacitor between the AC high and AC low signals (on the other side of a switch). This capacitor controls the characteristics of the AC Disconnect waveform (frequency, etc.) and the software relies on a value of 68 F/100V device.

#### 1.1.2.3 Serial Interface

The host serial interface uses the MSP430's on board UART. It is run at 19.2K baud set to 8 data bits, no parity and 1 stop bit.

#### 1.2 Firmware Design

This firmware runs on the MSP430 to control the TPS2384, and supports systems with up to 48 ports; up to 12 TPS2384 devices, each with 4 ports. The firmware controls the system-level parameters as well as port-level parameters for each TPS2384 device within the system.

The firmware uses a state machine approach to accomplish this. The state machine tracks the operational state of each port on any given TPS2384. The firmware iterates through the TPS devices and through the ports, servicing ports in a fixed sequence.

There are two interrupts that can occur any time; one for serial communications (either RS-232 or I<sup>2</sup>C) with the host, while the other interrupt is for a fixed system-timer tick that controls the state machine timing.

The firmware also keeps track of system and device error conditions that occur, as well as any administrative events that affect the port states, such as administratively disabling a port, or changing a port configuration to not support a particular feature.

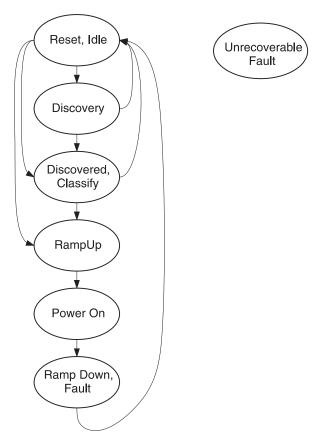

The main loop of the firmware that iterates through these states is in the *main.c* file. For DC-disconnect mode, each main loop takes approximately 75 milliseconds. For AC-disconnect mode, each main loop takes approximately 25 milliseconds. A high-level diagram of the states implemented in the firmware is shown in Figure 1-2.

Note that not every state is shown in Figure 1-2. States are lumped together in groups for clarity. Currently there are more than 30 different states.

Figure 1-2. Firmware Port State Machine Overview

Descriptions of each state are given below.

# 1.2.1 Reset, Idle

The Reset/Idle state group has only two states -idle and reset\_port.

Idle is the initial state of the system at startup. This state can be entered from a number of places, depending on system or device changes that occur as the machine is advancing through the states. If the port and discovery are enabled, idle advances to the *pre\_discovery* state in the *Discovery* group.

- If the IEEE specification test mode is selected, it must be powered up immediately. In this case, *idle* goes either to *discovered\_test* in the *Discovered, Classify* group, or to *ramp\_up\_power*. It only goes to *ramp\_up\_power* if power management has already enabled power to this port. Normally, it goes to *discovered\_test* and sets the discovered bit to tell the power management task that it needs power. Even though test is intended to power up the port regardless of port state, it is still subject to power management.

- The Reset\_port state sends a command to the TPS2384 to reset the port, then always goes to the idle state. It is provided for states where there is no time left in the time slice to send a reset command on the I<sup>2</sup>C port.

Figure 1-3. Reset, Idle States Details

# 1.2.2 Discovery

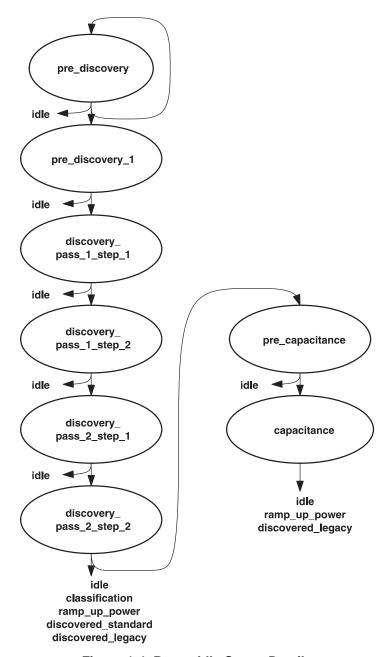

The *Discovery* states support the process of device discovery for IEEE 802.3af-compliant PDs, and for Legacy PDs. These states are always entered from the idle state.

If a valid PD is discovered, the state machine proceeds to either the discovered/classify set of states, or directly to the ramp up state. If no PD is found, the discovery states periodically cycle back to the idle state to start over again.

Figure 1-4 shows the state transitions, and the text following that describes what happens in each specific state.

Figure 1-4. Reset, Idle States Details

#### 1.2.2.1 Pre\_discovery State

The TPS2384 has leakage current when measurements are being made. The leakage current pulls up the voltage on the port when there is no device present to consume the currrent and pull the voltage down. If the voltage is above a threshold, two things are true:

- 1. There is nothing plugged into the port

- 2. It is not possible to get the voltage correct for discovery.

The *pre\_discovery* state measures the voltage on the port. If the voltage goes below a specific threshold, the state is changed to *pre\_discovery\_1*. If the voltage does not go below the threshold in a specified number of port cycles, the port is reset and sent back to the *idle* state to start over again.

# 1.2.2.2 Pre\_discovery\_1 State

The *pre\_discovery\_1* state reads the voltage on the port a second time to verify that it is still below the threshold required for discovery. If it is, it starts the 4.4 volt measurement of current and advances the state to *discovery\_pass\_1\_step\_1*. If it is not, it resets the port and sends the state back to *idle*.

#### 1.2.2.3 Discovery states

The Standard Discovery process on the TPS2384 firmware uses a 4-meaurement-point discovery. Instead of simply applying 4.4 and 8.8 volts to the port and measuring the currents, it goes through the sequence twice. This enables it to filter out capacitive loads that might look like resistive loads with only 2 meaurement points. It also enables it to identify certain types of legacy PDs that have some capacitance in their signatures.

All of the discovery states first check to ensure that the port is still enabled. If it is not, they reset the port and set it back to the *idle* state. If it is, they finish a measurement, generally start a measurement, and go on to the next state in the sequence.

| Discovery_pass_1_step_1 State | Reads and stores the current for the 4.4 volt test started by pre_discovery_1. It starts an 8.8 volt current measurement.                                           |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Discovery_pass_1_step_2 State | Reads and stores the current for the 8.8 volt test started by Discovery_pass_1_step_1. It starts a second 4.4 volt current measurement.                             |

| Discovery_pass_2_step_1 State | Reads and stores the current for the 4.4 volt test started by Discovery_pass_1_step_2. It starts a second 8.8 volt current measurement.                             |

| Discovery_pass_2_step_2 State | Reads and stores the current for the 8.8 volt test started by<br><i>Discovery_pass_2_step_1</i> . It then does up to three discovery processes if they are enabled. |

If standard discovery is enabled, it uses 4 current differences, one for each pair of 4.4 and 8.8 volt currents. If all 4 are within an acceptable range, the PD is marked as discovered. If powerup is enabled and no other port on the TPS2384 is operating the output FET in the linear region, classification is enabled and the state is set to *classification*. Otherwise, the state is set to *discovered\_standard*.

If legacy discovery is enabled, and no standard discovery occurs, the firmware compares the 4 currents to the several sets of windows for current derived from various legacy devices. Legacy devices are devices which do not meet the IEEE standard for PoE, but can nonetheless be powered up. As mentioned before, the 4 point discovery method makes it possible to identify the resistive and capacitive signatures of these devices simply by measuring the 4 currents.

If a legacy device is discovered, and powerup is enabled for this port, ramp up is started, and the state is set to  $ramp\_up\_power$ . This is done only if no other FET on the TPS2384 is in the linear mode. Ramp up and classification operate the power FET on the port in the linear mode, which increases the power dissipation of the TPS2384. For this reason, only one port at a time is allowed to do this.

If powerup is not enabled, the state is set to discovered legacy.

The third discovery mode is capacitive discovery. If no other discovery occurs, the discovery currents are tested against a final window. This window currently involves a very high current on the second measurement (8.8 volts) and a very low current on the third measurement (4.4 volts). This signature indicates a capacitor on the port that cannot be charged up to 8.8 volts, and that then is not discharged down to 4.4 volts. To characterize this device, if capacitive discovery is enabled, the TPS2384 is put in voltage measurement mode, and the state is set to *pre capacitance*.

If none of the discoveries take place, the port is flagged as not discovered, the port is reset, and the state is set to idle.

#### 1.2.2.4 Pre capacitance State

The *pre-capacitance* state reads and stores the results of the voltage measurement started by the previous state. If the voltage is low enough, and the port and capacitive discovery are still enabled, it starts a capacitance measurement. It sets the TPS2384 up in a mode which puts out a fixed current and measures voltage. It sets the state to *capacitance*.

If the voltage is not low enough or something is disabled, the port is reset and set back to *idle* mode.

#### 1.2.2.5 Capacitance State

If the port and capacitive detection are still enabled, the *capacitance* state reads in the voltage result from the constant current. This is then subtracted from the pre-capacitance voltage to get a charge rate. If this charge rate is within the window of the PD signatures, the device is considered to be discovered. If powerup is enabled, ramp up is started, and the state is set to *ramp\_up\_power*. If not, the state is set to *discovered\_legacy*.

If something is disabled, or if the voltage difference is outside the window, the device is labeled as not discovered, the port is reset, and the state is set to *idle*.

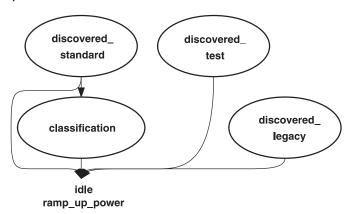

# 1.2.3 Discovered, Classify

The discovered states are provided because of the tight control that power management has over PDs in the firmware. In general, the ports are not enabled for powerup until they are discovered. It is necessary for the firmware to set the discovered bit, and for the power manager to recognize this and set the powerup enabled bit. The discovered states permit one port cycle to pass to enable this to happen. All of these states reset the port and return it to the idle state if it is disabled.

Figure 1-5. Discovered, Classify States Detail

#### 1.2.3.1 Discovered\_standard State

The *discovered\_standard* state is reached, not surprisingly, from a standard discovery. Like most states, it checks first to see if the port is enabled. If it is, and if powerup and classification are enabled, it starts the classification process on the port, and sets the state to *classification*. If classification is disabled, but powerup is enabled, it starts the ramp up on the port, and sets the state to *ramp\_up\_power*. Note that these steps are only taken if no other FET on the TPS2384 is operating in the linear region.

Even though there is a classification enable bit, the existing software does not clear it, so the discovered standard state should always advance to the classification state.

#### 1.2.3.2 Discovered test State

The *discovered\_test* state is very simple. If the port is enabled for powerup and no other FET on the device is in linear mode, the ramp up process is started, and the state is set to *ramp\_up\_power*. If not, the port is reset and the state is set to *idle*.

#### 1.2.3.3 Discovered\_legacy State

The *discovered\_legacy* state is entered either after a legacy or capacitive discovery. It is very similar to the *discovered\_test* state. The only difference is that the discovered\_test state puts the PORT\_STATUS\_TEST\_MODE value into the temporary register. The *ramp\_up\_power* state puts this value into the port status memory. For *discovered\_legacy* the value has been put in during previous states, and reflects either legacy or capacitive discovery.

#### 1.2.3.4 Classification

The *classification* state is entered after discovery if powerup and *classification* are enabled. *Classification* is deliberately put after powerup enable because it can draw a fair amount of power itself – about 100 milliamps or 4.8 watts worst case. *Classification* reads the classification current from the TPS2384 and determines the PD class. Then it starts power ramp up, sets the state to *ramp\_up\_power*, and loads the temporary register with PORT\_STATUS\_POWERED\_RESISTIVE\_DISCOVERY.

# 1.2.4 RampUp

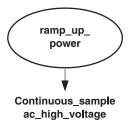

Figure 1-6. Ramp up States Detail

The *ramp\_up\_power* state is entered from a variety of states. If DC disconnect is enabled, it sets the port up for continuous sample mode and sets the port state to continuous sample.

If AC disconnect is enabled, *ramp\_up\_power* pauses 1 port cycle if necessary to sync up to the AC disconnect waveform. It then sets the port up for voltage mode and sets the state to *ac\_high\_voltage*.

In any case, *ramp\_up\_power* turns off the flag indicating that the FET is in the linear mode, puts the port status from the temporary register into the port status byte, flags that the port is powered up, and puts a nominal 48 volts into the port voltage. This is done because it takes considerable time to measure the voltage in continuous sample mode.

#### 1.2.5 Power Up -DC Disconnect

The power up group of states is discussed in two groups – DC disconnect and AC disconnect.

The TPS2384 has a mode – continuous sample – that provides significant automation for DC disconnect. Whenever the port is powered up, the TPS2384 provides undervoltage, overvoltage and overcurrent protection. When the port is also in continuous sample mode, the TPS2384 provides two other functions as well; an automatic IEEE-compatible DC disconnect function, and automated sequencing between current and voltage reads.

Because of the high level of support provided by the TPS2384, the main loop for DC disconnect is very simple. Each port is processed in a simple sequence starting with the lowest number port and ending with the highest.

This is referred to as a port cycle.

Figure 1-7. DC Disconnect States Detail

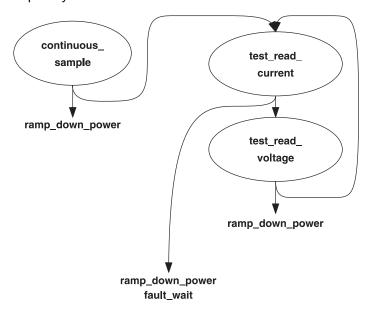

#### 1.2.5.1 Continuous Sample

The *continuous\_sample* state is the normal state for a powered-up port on the TPS2384. It always checks to verify that the port is still enabled for powerup. If not, it ramps down the port and sets it to *ramp\_down\_power*.

If the port is in test mode, the *continuous\_sample* routine starts a current read and sets the state to test\_read\_current.

Normally, the *continuous\_sample* state reads port current. Periodically, but much less frequently, it reads port voltage. Always, it calculates port power. If the power is over the port power limit, it ramps down the port and flags an overlimit fault.

Normally, the *continuous\_sample* mode is stable for a long time, as long as the PD is powered up.

The *continuous\_sample* mode also reads the port status, and sets the port state to *control\_state\_fault\_wait* in order to further distinguish fault types.

#### 1.2.5.2 Test read current

The *Test\_read\_current* state is provided to override the automatic DC disconnect feature in the TPS2384. In the IEEE mandated test mode, port power is supposed to be maintained regardless of the presence or absence of a PD on the port. The automatic DC disconnect feature in continuous sample mode on the TPS2384 would defeat this. However, it is still necessary, even in test mode, to read current and voltage and perform power management.

The *test\_read\_current* state first checks to see that the port is still enabled for powerup and is still in test mode. If these criteria are not met, it starts the ramp down process, and sets the port state to *ramp\_down\_power*.

If the criteria are met, it reads and stores the current value from the TPS2384. Next, it checks for a fault indication from the TPS2384. If it gets one, it sets the state to *fault wait*, and sets the port status to UV/OV fault.

Test\_read\_current also calculates the power consumption for the port every time through. Since it is a test mode, however, it does not perform an overlimit calculation on the port power limit.

If there is no fault, the firmware starts a voltage measurement process on the TPS2384 and set the port state to test\_read\_voltage.

#### 1.2.5.3 Test read voltage

Test\_read\_voltage is very similar to test\_read\_current, except that it reads voltage instead. It does not test for a fault. Since the TPS2384 shuts the port down automatically upon fault detection, it is not necessary to check every single port cycle.

If all is well, test\_read\_voltage sets up for a current measurement and sets the state to test\_read\_current.

#### 1.2.6 Power Up - AC Disconnect

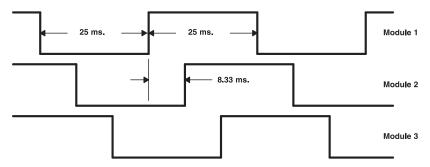

While the TPS2384 provides an interface to drive the FETs for a square wave based AC disconnect, it provides no help with timing that square wave or with detecting disconnect. All these functions must be provided by the firmware on the MSP430.

The need to provide these functions, as well as the speed limitations of the I<sup>2</sup>C interface to the TPS2384, make the main loop for AC disconnect much more complex than that for DC disconnect.

The software supports up to 6 modules, each with its own AC disconnect waveform. The frequency is 20 Hz., so each half cycle takes 25 milliseconds. The module waveforms are usually 25/n milliseconds apart, when n is the number of installed modules.

For example, in a system with 3X Modules (2X8), the waveforms are spaced 8.3333 milliseconds apart, as shown in Figure 1-8.

Figure 1-8. AC Disconnect Waveforms

The TPS2384 has an integrating A/D converter that has a maximum conversion time of 21 milliseconds. For this reason, the software is structured so that it starts as many conversions as possible in the first 4 milliseconds of the half cycle on each module. For more information on the AC disconnect timing, consult the source listings.

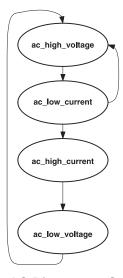

Figure 1-9 shows the AC disconnect states.

Figure 1-9. AC Disconnect States Detail

#### 1.2.6.1 AC\_high\_voltage

AC\_high\_voltage first checks to see if the port is still enabled for powerup. If not, it starts a ramp-down and goes to the ramp\_down\_power state. Next it adds the port power to the system power accumulators.

Next it checks the *ac\_high* variable to make sure that the AC disconnect signal is high. If the signal is not high, the state just waits another cycle for it to be high so that it can do a correct measurement.

Next, it reads the voltage value from the TPS2384 and stores it in the temporary register for the port. Then it starts another voltage-read cycle for the port and sets the state to ac\_low\_current.

The names of states in AC disconnect describe the operation for which they prepare parts of the system, not the operation that they complete. So the *ac\_high\_voltage* state starts the measurement of voltage with the AC signal high. The voltage it reads in is from the AC low phase.

#### 1.2.6.2 AC\_low\_current

The *ac\_low\_current* state performs the usual checks for powerup enable and AC phase. These are also performed for the rest of the AC states.

Next, it reads in the voltage from the TPS2384. This voltage is the high AC phase voltage. It averages the high and low voltages and saves the average as the port voltage. It then calculates the port power. If the port power is over the limit, it starts ramp-down, and sets the state to *fault\_ramp\_down*.

If the power is acceptable, it then calculates the difference between the high and low phase voltages. If the difference is above a threshold, the PD has probably been removed. If a difference above a threshold is found, the state is set back to *ac\_high\_voltage* and not to *ac\_high\_current*. So the AC-disconnect sequence is shortened into only two states until the next AC-disconnect sequence entry.

The software waits for a specific number (6 times) of high voltages in succession before ramping down the port and going to *fault\_ramp\_down* state. This also ensures that *Green-PDs* with modulated current consumption are not disconnected.

Ac\_low\_current starts a current measurement and sets the state to ac\_high\_current.

#### 1.2.6.3 AC\_high\_current

Ac\_high\_current is very similar to ac\_low\_current. First, it performs the usual checks for powerup-enable and AC phase. Then it reads the content of the port status register. If any fault is detected when reading the status, the state control\_state\_fault\_ramp\_down is set. Otherwise, it initiates the high current measurement and sets the state to ac\_low\_voltage.

#### 1.2.6.4 AC\_low\_voltage

AC\_low\_voltage reads the high current measurement. This value is used for the port power and port power limit check. If that within limits, it starts a voltage measurement and sets the state to ac\_high\_voltage. This completes the AC-disconnect cycle.

# 1.2.7 Ramp Down/Fault States

The Ramp-Down/Fault states are entered from the power-on states. The only way for a ramp down to occur without a fault is either for the port to be disabled, or for power management to power down the port. An AC or DC disconnect is considered to be a fault.

The Ramp Down/Fault states are shown in Figure 1-10.

Figure 1-10. Ramp Down/Fault States Detail

#### 1.2.7.1 Ramp\_down\_power

The *ramp\_down\_power* state is very simple. It occurs when either the port currently on is disabled or port powerup is disabled. It simply resets the port, clears various flags and values such as power and voltage, and sets the state to *idle*. Since it is shutting down the port, there is no need to check for enable or any other inputs.

#### 1.2.7.2 Fault\_ramp\_down

Fault\_ramp\_down occurs upon any fault from the TPS2384, or when there is an AC disconnect event, or when a PD is consuming more power than a port can support. It also has no checks for control inputs. It follows states that do not have time to start a ramp-down function. Some states spend too much time doing reads and writes, and would overflow their time slot if they tried to start a ramp down as well. Like ramp\_down\_power, it clears power, voltage, and current, and various flags. It advances to fault\_wait\_1.

#### 1.2.7.3 Fault\_wait

Fault\_wait occurs when there is any fault (including a disconnect event) from a TPS2384. This applies to both DC disconnect mode and test mode. It is designed to follow states that do not have time left to reset the port. Several states take so much time reading from and writing to the TPS2384 that they would run out of time in their time slot.

Fault\_wait resets the port, clears the powerup parameters and flags, and sets the state to fault\_wait\_1.

#### 1.2.7.4 Fault wait 1

Fault\_wait\_1 updates fault status, and sets the value in general\_count as a delay count according to the specific type of fault encountered. (Delay countdown is handled by power management.) Then it sets the next state to fault wait 2.

#### 1.2.7.5 Fault\_wait\_2

Fault\_wait\_2 starts a temperature measurement, then sets the next state to fault\_wait\_3.

#### 1.2.7.6 Fault\_wait\_3

Fault\_wait\_3 reads a temperature-measurement result, and counts down *general\_count* by one. If the delay time has not expired, it continues to start another temperature measurement without changing the state; otherwise, it sets the next state to *idle*, and resets the port in the TPS2384.

#### 1.3 Host Interface Protocol

The PoE system solution includes the MSP430 microcontroller on which the firmware runs, as well as up to 12 TPS2384 power controllers. This system interoperates with a host over an RS-232 interface. In the future, this interface can also be an I<sup>2</sup>C bus.

In order to interoperate with the host, a well-defined protocol exists between the MSP430 microcontroller and the host. This is referred to as the *Host Interface Protocol*.

The Host Interface Protocol consists of a set of commands that allow the host processor system and PoE system to interact. Each of these commands defines a data format that allows this exchange of information between the systems.

#### 1.3.1 Command Overview

The commands comprising the Host Interface Protocol are shown in Table 1-2.

**Table 1-2. Host Interface Protocol Commands**

| Command                       | Code                                                                                                                           | Description                                                                                                                                                                                          | Direction   |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Reset 0x52                    |                                                                                                                                | Resets the MSP430 firmware and system hardware into a known state. The MSP430 responds with an Acknowledge message.                                                                                  | Host to PoE |

| System Write                  | 0x05                                                                                                                           | Writes parameters that control system-level functionality. The MSP430 responds with an Acknowledge message.                                                                                          | Host to PoE |

| Save/Restore<br>Configuration | 0x06                                                                                                                           | Saves parameters to the flash memory, or restores default parameters. The MSP430 responds with an Acknowledge message.                                                                               | Host to PoE |

| Program Controller            | 0x07                                                                                                                           | Initiates software download of a new image to the MSP430. The MSP430 responds with an Acknowledge message.                                                                                           |             |

| Port Write                    | 0x80 –<br>0xAF <sup>(1)</sup>                                                                                                  | Writes parameters that control port-level functionality. The MSP430 responds with an Acknowledge message.                                                                                            | Host to PoE |

| Information Request           | 0xBA                                                                                                                           | Requests information from MSP430 such as system status, port status, etc. The MSP430 responds with a System Read, Power Read, Port Read, All Ports Status or All Ports Enabled Message.              | Host to PoE |

|                               |                                                                                                                                | Erase the PoE application program. The MSP430 responds with an Acknowledge message.                                                                                                                  | Host to PoE |

| Clear Information             | ormation 0xF1 Erase the PoE configuration information. The MSP430 responds with an Acknowledge message.                        |                                                                                                                                                                                                      | Host to PoE |

| Receive Data Block            | ve Data Block 0xF2 Send a data block for programming into the Flash memory. The MSP430 responds with an Acknowledge message.   |                                                                                                                                                                                                      | Host to PoE |

| Acknowledge 0xBA              |                                                                                                                                | Acknowledges receipt of a Reset, System Write, Save/Restore Configuration, Program Controller or Port Write message from the Host, or an Acknowledge of an error detected in any requesting message. | PoE to Host |

| System Read 0x05              |                                                                                                                                | System-level parameters sent in response to an Information Request message.                                                                                                                          | PoE to Host |

| Power Read 0x08               |                                                                                                                                | System power information sent in response to an Information Request message.                                                                                                                         | PoE to Host |

| System Info 0x09              |                                                                                                                                | Basic boot-level parameters sent in response to an Information Request message asking for system info parameters.                                                                                    | PoE to Host |

| Port Status                   | Port Status 0x10 – Status of a group of ports, sent in response to an Information Request message asking for all ports status. |                                                                                                                                                                                                      | PoE to Host |

| Port Enables                  | t Enables 0x20 Enable status of all ports, sent in response to an Information Request message.                                 |                                                                                                                                                                                                      | PoE to Host |

| Port Read                     | 0x80 –<br>0xAF                                                                                                                 | Port level parameters, sent in response to an Information Request message.                                                                                                                           | PoE to Host |

<sup>(1)</sup> The Port Write code contains both the code and the port which should be written.

The interface for the Host Interface Protocol is defined in the protocol.h header file.

#### 1.3.1.1 Protocol Format

The protocol consists of a message code (as described in Table 1-2), 0 or more data bytes specific to the message code, and a 2-byte checksum field.

The checksum is the 16-bit sum of all the previous bytes of the message. This is generated by the transmitter and validated by the receiver.

The 16-bit (two-byte) data types are stored as follows: the high byte of the data is stored in the first storage location (closer to the message code) and the low byte of the data is stored in the second storage location.

#### 1.3.1.2 Protocol Validation

The MSP430 controller monitors the incoming message data to ensure integrity within all communications messages. The PoE controller verifies the following:

- The checksum is correct

- · The length of the message is correct for the associated command

- Invalid data is not received with the specific command

- The message is received in a timely fashion

Any of these detected errors is recorded and transmitted back to the host controller via an Acknowledge message and the appropriate Response Code.

#### 1.3.2 Transactions: Host Controller to Power Subsystem

The following messages are used for communication initiated by the host controller to the power system (MSP430 and TPS2384).

#### 1.3.2.1 Reset

This message is sent from the host processor to the MSP430 to reset the PoE controller(s). The values of the first 5 bytes spell out the word *RESET*, to ensure that the MSP430 does not trigger a system reset incorrectly. The MSP430 responds immediately to this message with an *Acknowledge* message. With a full configuration, it can take up to 2 seconds to perform the reset – when it is completed, a System Info message is sent.

Table 1-3. Reset Message Format

| Byte | Fleld      | Values     |

|------|------------|------------|

| 1    | Reset code | 0x52 ('R') |

| 2    | Data       | 0x45 ('E') |

| 3    | Data       | 0x53 ('S') |

| 4    | Data       | 0x45 ('E') |

| 5    | Data       | 0x54 ('T') |

| 6-7  | Checksum   | 0x0183     |

#### 1.3.2.2 System Write

This message is sent from the host processor to the MSP430 to write system level parameters in the MSP430 that control the TPS2384 power controller(s). The MSP430 responds to this message with an *Acknowledge* message.

If the Modify bit is set for a particular parameter, the parameter data is applied to the system parameter. If the Modify bit is not set for a particular parameter, the parameter data is ignored.

The *Knockoff* bit, when set, allows Power Management to allow a higher priority device, when plugged in, to take precedence over and power down a lower priority device.

If the Start bit is set, it starts processing, and locks certain bits as described below.

The Modify Enable allows the Number of Module, Number of Ports and the 1st Port Number on Modules to be changed. The number of modules refers to the number of AC disconnects circuits in the system. For example a 24 port system might have 2 AC disconnect circuits, each servicing 12 ports. So the Number of Modules for that system would be 2. The Number of TPS2384 in the system refers to the number of TPS2384's in the system. There are 4 ports per chip so in the 24 port system there there would be 8 TPS2384's in the system.

The  $1^{st}$  Port Number on  $1^{st}$  Module is not available, as this is a fixed address (of 0) and can not be changed. The Number of Modules must reflect that there is always at least 1 module. The next unused  $1^{st}$  Port Number of X Module must reflect the next unused address, which indicates what the last address of the previous module is. For example, on a 20-port, 2-module system, you might have  $1^{st}$  Port Number on  $1^{st}$  Module = 12 and  $1^{st}$  Port Number on  $2^{nd}$  Module = 20. The port numbers are zero-based, so port 20 indicates physical port 21.

The changes to the Port and Module parameters do not take affect until a Save/Restore Configuration message is received, with at least the *System Settings* requested.

**Table 1-4. System Write Message Format**

| Byte  | Field                                                                                         | Values                               |

|-------|-----------------------------------------------------------------------------------------------|--------------------------------------|

| 1     | System Write code                                                                             | 0x05                                 |

| 2     | Knockoff , AC Disconnect, Detection Type and Start parameters:                                | Varies                               |

|       | Bit 0: Modify Knockoff                                                                        |                                      |

|       | Bit 1: Modify AC Disconnect                                                                   |                                      |

|       | Bit 2: Modify Detection Type                                                                  |                                      |

|       | Bit 3: Modify Start Control                                                                   |                                      |

|       | Knockoff:                                                                                     |                                      |

|       | Bit 4: Knockoff (0-enabled, 1- disabled)                                                      |                                      |

|       | AC Disconnect:                                                                                |                                      |

|       | Bit 5: AC Disconnect (0-DC, 1-AC)                                                             |                                      |

|       | Detection Type:                                                                               |                                      |

|       | Bit 6: Detection Type (0-resistive, 1-capacitive)                                             |                                      |

|       | Start Control:                                                                                |                                      |

|       | Bit 7: Start (0-OFF, 1-ON)                                                                    |                                      |

| 3-4   | Maximum Power available when only one supply is working (watts)                               | Varies – 0xFFFF represents no change |

| 5-6   | Maximum Power available when both supplies are active (watts)                                 | Varies – 0xFFFF represents no change |

| 7     | User-defined label for the PoE controller                                                     | Varies                               |

| 8     | Port and Module parameters:                                                                   | Varies                               |

|       | Modify Enables:                                                                               |                                      |

|       | Bit 0: Modify Number of Modules, Number of Ports, and 1 <sup>st</sup> Port Number on Module X |                                      |

|       | Number of Moduels:                                                                            |                                      |

|       | Bits 1-3: Number of Modules (1 to 6)                                                          |                                      |

|       | Number of Ports:                                                                              |                                      |

|       | Bits 4-7: Number of Ports (in multiples of 4: 1-4 ports, 2-8 ports, 12-48 ports)              |                                      |

| 9     | 1 <sup>st</sup> Port Number on 2 <sup>nd</sup> Module                                         | Varies                               |

| 10    | 1 <sup>st</sup> Port Number on 3 <sup>rd</sup> Module                                         | Varies                               |

| 11    | 1 <sup>st</sup> Port Number on 4 <sup>th</sup> Module                                         | Varies                               |

| 12    | 1 <sup>st</sup> Port Number on 5 <sup>th</sup> Module                                         | Varies                               |

| 13    | 1 <sup>st</sup> Port Number on 6 <sup>th</sup> Module                                         | Varies                               |

| 14    | Unused                                                                                        | Varies                               |

| 15-16 | Checksum                                                                                      | Varie                                |

|       | •                                                                                             |                                      |

#### 1.3.2.2.1 Start up Sequence

After a hardware or software reset command, the firmware:

- Initializes the MSP430

- Asserts reset on the TPS2384s, disabling all activity on the PoE ports

- Sends the System Read message to the host (only valid on RS-232 interface the I<sup>2</sup>C version does not automatically send this message, it must be polled for by the host)

- Handles all host interface protocol messages

After initializing the port and system configurations, the host sends a System Write command with the start bit set. This causes the firmware to:

- Lock in AC disconnect (and start bit)

- Initialize the TPS2384s (≈ 5 seconds)

- Start running the PoE ports

- Start again to handle all the interface protocol messages

The only way to change the AC disconnect is to reset the MSP430, either with a hardware reset, or with a Reset command.

#### 1.3.2.3 Port Write

This message is sent from the host processor to the MSP430 to write port-level parameters in the MSP430 that control the TPS2384 power controllers. The MSP430 responds to this message with an *Acknowledge* message.

The ability to set the Logical Port Number is not available when sending this message addressed to *All Ports*. Setting of the Logical Port Number is mutually exclusive of setting any other parameter using the Port Write message. When setting the Logical Port Number, the Port Write code always refers to the physical port number, regardless of any other previous Logical Port setting for the port number. The Logical Port Number does not take affect until a Save/Restore message is received with the Logical Port Numbering parameter set for saving. The Physical and Logical Port Numbers must be within the configured *Number of Ports* that is part of the System Write message.

When not setting the Logical Port Number, the Port Write code refers to the remapped (if previously set) logical port, or the physical port (if not previously set).

**Table 1-5. Port Write Message Format**

| Byte | Field                                                                                                                                                                                                                                                                                                                                  | Values                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1    | Port Write code                                                                                                                                                                                                                                                                                                                        | 0x80 – 0xAF is an individual port (0x80 + port number).        |

|      |                                                                                                                                                                                                                                                                                                                                        | 0xB0 represents all ports.                                     |

| 2    | Modify Enables:                                                                                                                                                                                                                                                                                                                        | Varies                                                         |

|      | <ul> <li>Bit 0: Modify 'Port Enable'</li> <li>Bit 1: Modify 'Port Priority'</li> <li>Bit 2: Modify 'Legacy Support'</li> <li>Bit 3: Modify 'Power Management'</li> <li>Bit 4: Modify 'Test Mode'</li> <li>Bit 5: Modify 'I2C Parameters'</li> <li>Bit 6: Modify 'Clear Events'</li> <li>Bit 7: Modify 'Logical Port Number'</li> </ul> |                                                                |

| 3    | Port Enable:                                                                                                                                                                                                                                                                                                                           | Varies                                                         |

|      | Bit 0: Port Enable (0- disabled, 1 enabled, disabled is default)                                                                                                                                                                                                                                                                       |                                                                |

|      | Port Priority:                                                                                                                                                                                                                                                                                                                         |                                                                |

|      | Bits 1-2: Port Priority (1-critical, 2-high, 3- low, 0 indicates no change)                                                                                                                                                                                                                                                            |                                                                |

|      | Legacy Support:                                                                                                                                                                                                                                                                                                                        |                                                                |

|      | Bit 3: Legacy Support (0-disabled, 1-enabled, disabled is default),                                                                                                                                                                                                                                                                    |                                                                |

|      | Bit 4: Capacitive Support (0-disabled, 1-enabled, disabled is default)                                                                                                                                                                                                                                                                 |                                                                |

|      | Power Management:                                                                                                                                                                                                                                                                                                                      |                                                                |

|      | <ul> <li>Bit 5: Power Limit from Classification (0-disabled, 1- enabled, disabled is<br/>default)</li> </ul>                                                                                                                                                                                                                           |                                                                |

|      | Bit 6: Power Limit for Management (0- disabled, 1-enabled, disabled is default)                                                                                                                                                                                                                                                        |                                                                |

|      | Test Mode:                                                                                                                                                                                                                                                                                                                             |                                                                |

|      | Bit 7: Test Mode (0- Auto, 1-Test, Auto is default),                                                                                                                                                                                                                                                                                   |                                                                |

| 4    | I <sup>2</sup> C Parameters:                                                                                                                                                                                                                                                                                                           | Varies                                                         |

|      | Bits 0-4: Address (1 to 31)                                                                                                                                                                                                                                                                                                            |                                                                |

|      | Bit 5-6: Bus (1 to 3, default is 1)                                                                                                                                                                                                                                                                                                    |                                                                |

|      | Clear Events:                                                                                                                                                                                                                                                                                                                          |                                                                |

|      | Bit 7: Clear Events (1-clears Overload and Underload flags)                                                                                                                                                                                                                                                                            |                                                                |

| 5    | Logical Port Number (used for all future protocol messages when per-port information is requested)                                                                                                                                                                                                                                     | Varies                                                         |

| 6-7  | Maximum Power (milliwatts)                                                                                                                                                                                                                                                                                                             | Varies – 0xFFFF represents no change, (default power is 15.4W) |

| 8-9  | Checksum                                                                                                                                                                                                                                                                                                                               | Varies                                                         |

#### 1.3.2.4 Save/Restore Configuration

This message is sent from the host processor to the MSP430 to record system and channel-level parameters to flash memory, and uses that information through subsequent resets of the device. This message is also sent from the host processor to the MSP430 to restore the initial default values for all configuration information. The MSP430 responds to this message with an Acknowledge message.

If the Modify bit is set for a particular parameter, the parameter data will be applied to the system parameter. If the Modify bit is not set for a particular parameter, the parameter data will be ignored.

The System Settings saved are:

- Number of ports, modules, first port number in each module

- Port enabled state, power priority, power limits

It may take up to 2 seconds to record this information; therefore the host processor needs to wait before resuming transactions with the MSP430. The PoE does not reset after this operation.

The Logical Port Numbering settings saved are:

Logical port numbers sent in Port Write message

All the logical port numbers assigned up to this point are recorded in the flash memory, and the PoE then resets.

The restoring of all initial default values occurs after the Acknowledge message is sent and then the MSP430 writes them to flash memory and resets.

| Byte | Field                                                                                                                                                   | Values |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1    | Save/Restore Configuration code                                                                                                                         | 0x06   |

| 2    | Modify Enables:                                                                                                                                         | Varies |

|      | <ul> <li>Bit 0: Modify 'Save Configuration'</li> <li>Bit 1: Reserved</li> <li>Bit 2: Reserved</li> <li>Bit 3: Modify 'Restore Configuration'</li> </ul> |        |

|      | Save Configuration:                                                                                                                                     |        |

|      | <ul> <li>Bit 4: System Settings (1-save)</li> <li>Bit 5: Logical Port Numbering (1- save)</li> <li>Bit 6: Reserved</li> </ul>                           |        |

|      | Restore Configuration:                                                                                                                                  |        |

|      | Bit 7: Restore Default Data (1- restore)                                                                                                                |        |

| 3-4  | ChecksumChapter 7                                                                                                                                       | Varies |

Table 1-6. Save/Restore Configuration Message Format

#### 1.3.2.5 Program Controller

This message is sent from the host processor to the MSP430 to initiate a software download of a new image to the MSP430. See the section on *Software Download* for more information on this process.

**Table 1-7. Program Controller Message Format**

| Byte | Field                   | Values |

|------|-------------------------|--------|

| 1    | Program Controller code | 0x07   |

| 2    | Check code              | 0xAA   |

| 3    | Check code              | 0x55   |

| 4-5  | Checksum                | 0x-106 |

# 1.3.3 Information Request

This message is sent from the host to the MSP430 to request information from the MSP430 such as system status, port status, etc. The MSP430 responds with an informational response. No separate Acknowledge message is sent by the MSP430.

**Table 1-8. Information Request Message Format**

| Byte | Field                    | Values                                                                                                                                                                                                                                                        |  |

|------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | Information Request code | 0xBA                                                                                                                                                                                                                                                          |  |

| 2    | Message Code             | Message Code: 0x05: System Read 0x08: Power Read 0x09: System Info 0x10: Port Status (ports 0–11) 0x11: Port Status (ports 12–23) 0x12: Port Status (ports 24–35) 0x13: Port Status (ports 36–47) 0x20: Port Enable Status (all ports) 0x80: 0xAF – Port Read |  |

| 3-4  | Checksum                 | Varies                                                                                                                                                                                                                                                        |  |

# 1.3.4 Transactions: Power Subsystem to Host Controller

The following responses are sent by the MSP430 in request to a message from the host.

#### 1.3.4.1 Acknowledge

This is a message from the MSP430 to the host that acknowledges receipt of a Reset, System Write, Port Write, Save/Restore Configuration, Program Controller, Clear Application, Clear Information, or Receive Data Block message from the Host, or an acknowledge of an error detected in the requesting message.

Table 1-9. Acknowledge Message Format

| Byte | Field            | Values                                                                                                                                                                            |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Acknowledge Code | 0xBA                                                                                                                                                                              |

| 2    | Response Code    | Response Code: 0x00: Success 0x01: Bad Checksum 0x02: Message Too Long 0x03: Message Not Recognized 0x04: Invalid Data In Message 0x05: Message Timed Out 0x06: Programming Error |

| 3-4  | Checksum         | Varies                                                                                                                                                                            |

Bad Checksum: The calculated checksum of the received message does not match that of the

received checksum.

Message Too Long: The received message count is longer than the expected count for the specific

command (based on the Command Code).

Message Not The Command Code received is not part of the accepted list of Command

Recognized: Codes.

Invalid Data In Data associated with the specific command does not meet the specification of

Message: the command.

Message Timed Out: More than 100 milliseconds has elapsed between receiving one byte of the

message and the next.

Programming Error: An error occurred while attempting to write to the FLASH during the

programming procedure, or the correct sequence was not followed.

# 1.3.4.2 System Read

This is a message containing system-level parameters sent from MSP430 to host. This message is sent in response to an Information Request message asking for system level parameters.

Table 1-10. System Read Message Format

| Byte  | Field                                                 | Values                                                                                               |

|-------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 1     | System Read Code                                      | 0x05                                                                                                 |

| 2     | Reserved                                              | Reserved                                                                                             |

|       | • Bit 0                                               | • Bit 0: Reserved                                                                                    |

|       | Factory Defaults:                                     | Factory Defaults:  • Bit 1: Kernel Status (1-using factory default values)                           |

|       | Boot Message:                                         | Boot Message:  • Bit 2: Boot Time Message(0 – normal runtime, 1-boot time)                           |

|       | Knockoff:                                             | Knockoff:  • Bit 4: Knockoff (0-enabled, 1- disabled)                                                |

|       | AC Disconnect:                                        | AC Disconnect:  • Bit 5: AC Disconnect (0-DC, 1- AC)                                                 |

|       | Detection Type:                                       | Detection Type:  • Bit 6: Detection Type (0-resistive, 1-capacitive)                                 |

|       | Start Control:                                        | Start Control: • Bit 7: Start (0-OFF, 1-ON)                                                          |

| 3-5   | Serial Number                                         | Varies                                                                                               |