## DS90C241 Serializer and DS90C124 Deserializer Evaluation Kit

# User's Manual

# **NSID: SERDES24-35USB**

Rev 1.5

National Semiconductor Corporation

Date: 2/27/2008 Page 1 of 39

### **Table of Contents**

| TABLE OF CONTENTS                                                                                                                          |   |

|--------------------------------------------------------------------------------------------------------------------------------------------|---|

| INTRODUCTION:                                                                                                                              |   |

| CONTENTS OF THE EVALUATION KIT:                                                                                                            | 4 |

| DS90C241/124 SERDES TYPICAL APPLICATION:                                                                                                   | 4 |

| HOW TO SET UP THE EVALUATION KIT:                                                                                                          | 6 |

| EVALUATION BOARD POWER CONNECTIONS:                                                                                                        | 6 |

| DS90C241 TX SERIALIZER BOARD DESCRIPTION:                                                                                                  | 7 |

| Configuration Settings for the Tx Evaluation Board<br>Tx LVCMOS and LVDS Pinout by Connector<br>BOM (Bill of Materials) Serializer PCB:    |   |

| DS90C124 RX DE-SERIALIZER BOARD DESCRIPTION:                                                                                               |   |

| CONFIGURATION SETTINGS FOR THE RX EVALUATION BOARD<br>RX LVDS PINOUT AND LVCMOS BY CONNECTOR<br>BOM (BILL OF MATERIALS) DE-SERIALIZER PCB: |   |

| TYPICAL CONNECTION AND TEST EQUIPMENT                                                                                                      |   |

| TYPICAL CONNECTION DIAGRAM TX – USER QUICK REFERENCE                                                                                       |   |

| TYPICAL CONNECTION DIAGRAM RX – USER QUICK REFERENCE                                                                                       |   |

| TROUBLESHOOTING DEMO SETUP                                                                                                                 |   |

| APPENDIX                                                                                                                                   |   |

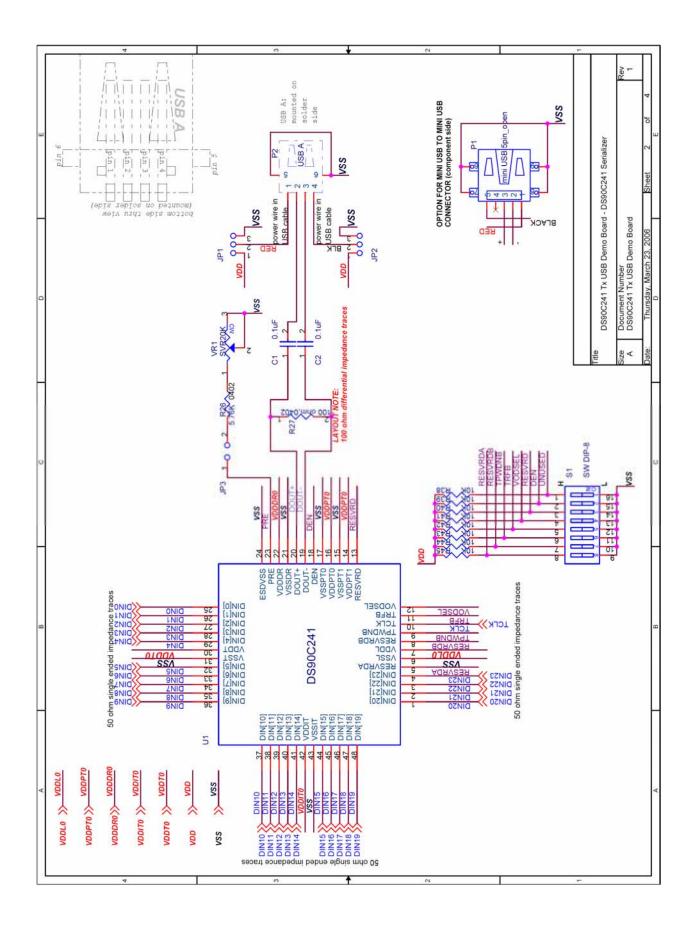

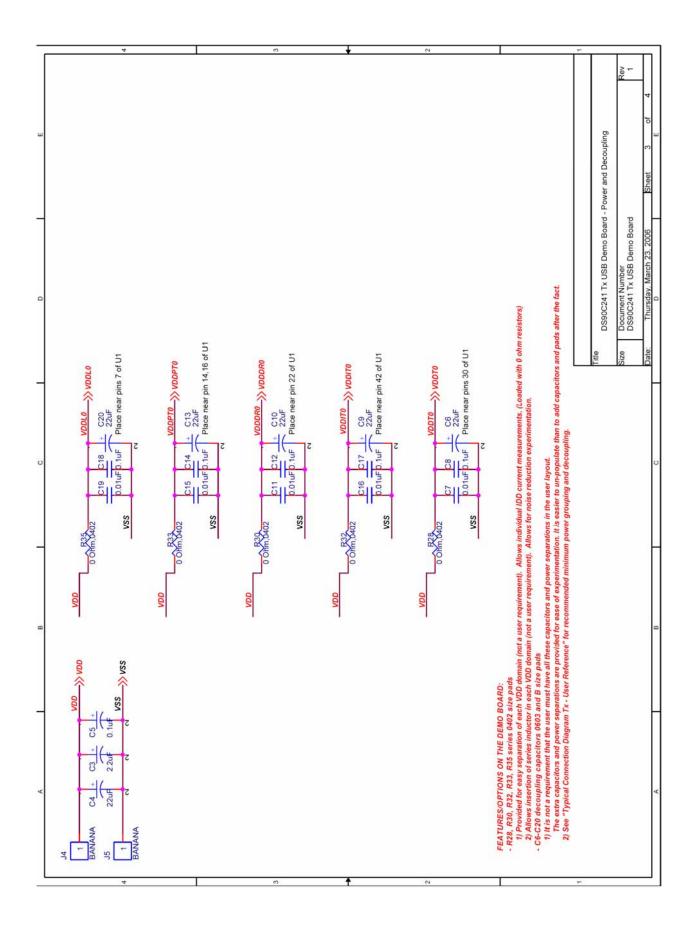

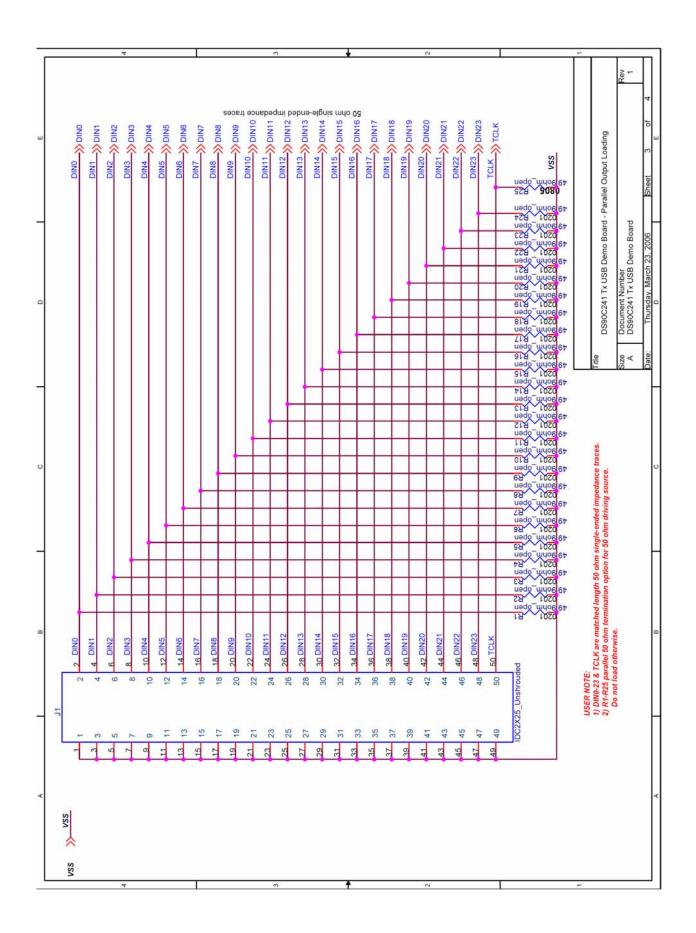

| SERIALIZER (TX) PCB SCHEMATIC:                                                                                                             |   |

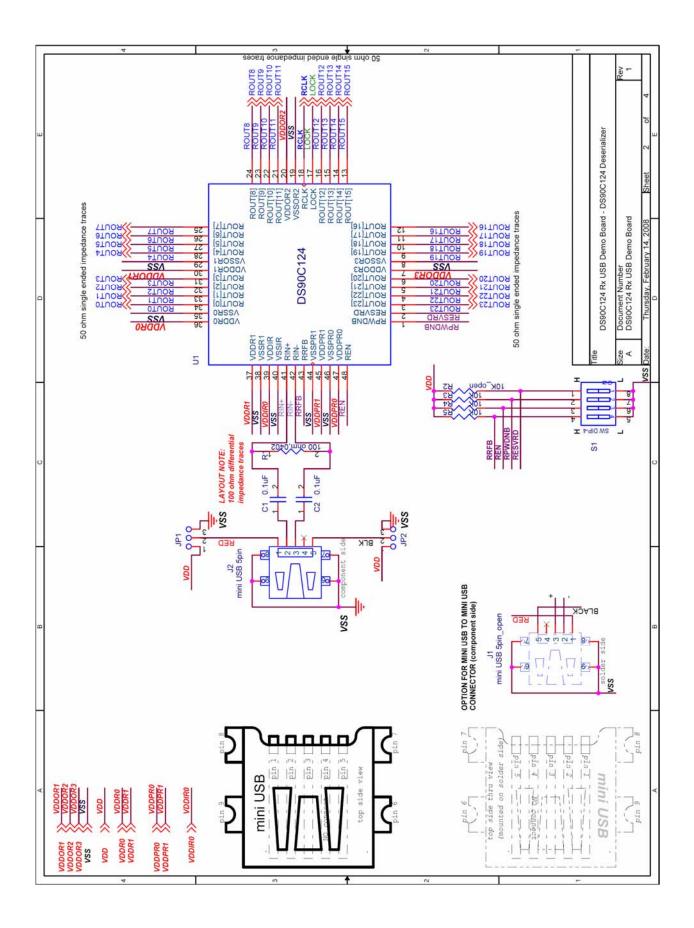

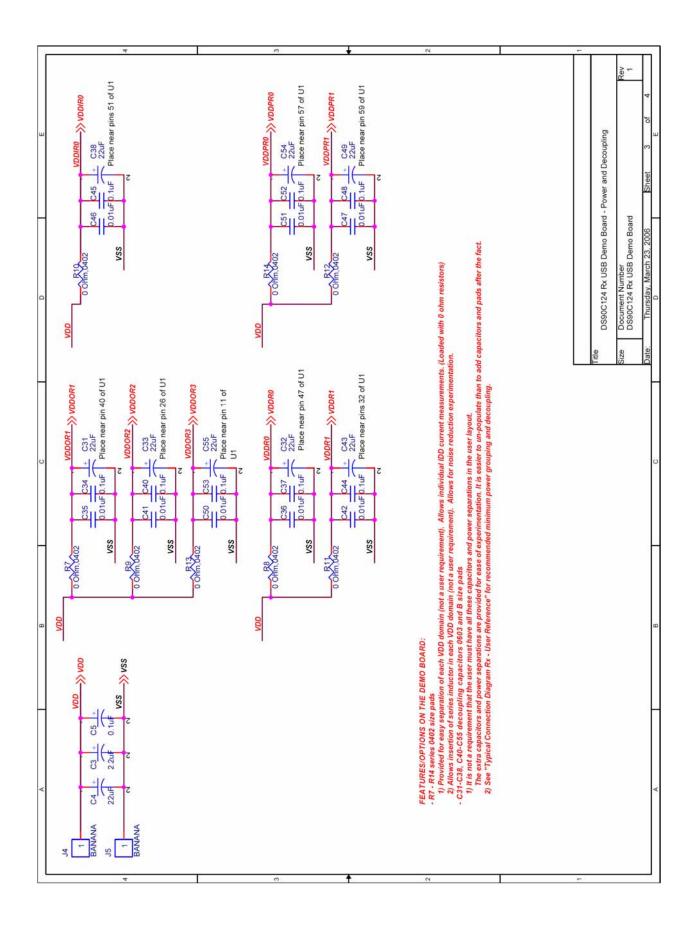

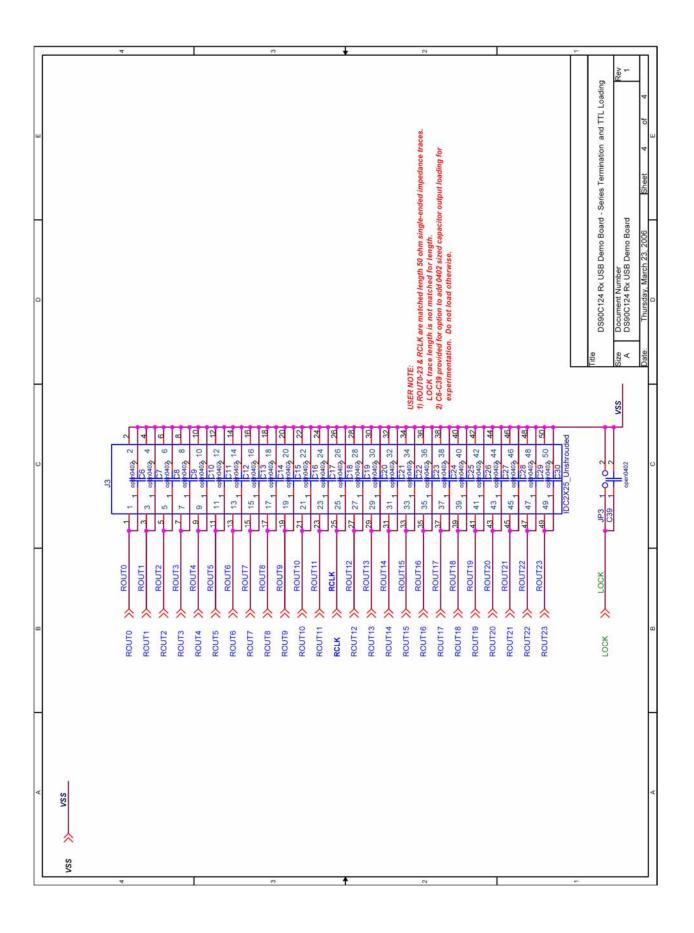

| DE-SERIALIZER (RX) PCB SCHEMATIC:                                                                                                          |   |

| SERIALIZER (TX) PCB LAYOUT:                                                                                                                |   |

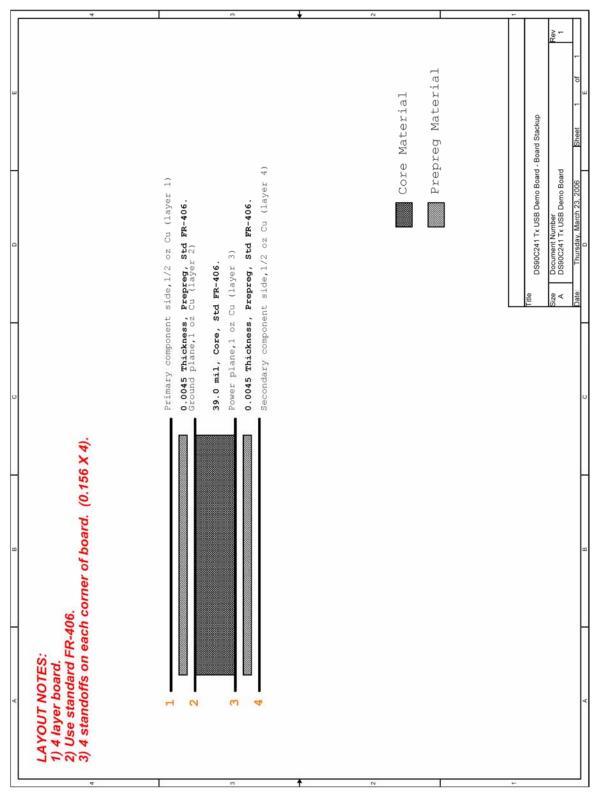

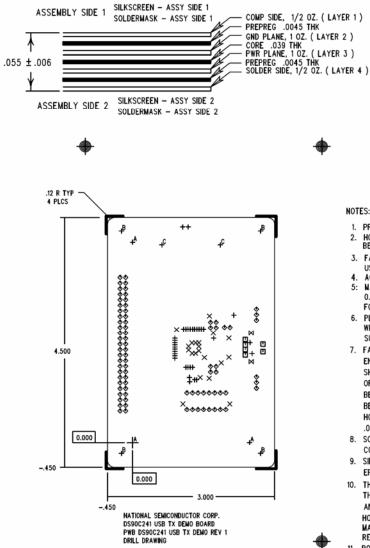

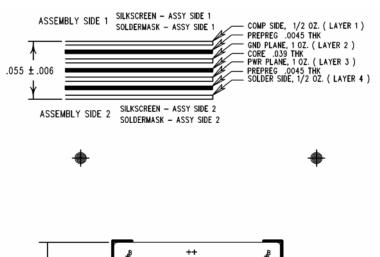

| SERIALIZER (TX) PCB STACKUP:                                                                                                               |   |

| DESERIALIZER (RX) DEMO PCB LAYOUT:                                                                                                         |   |

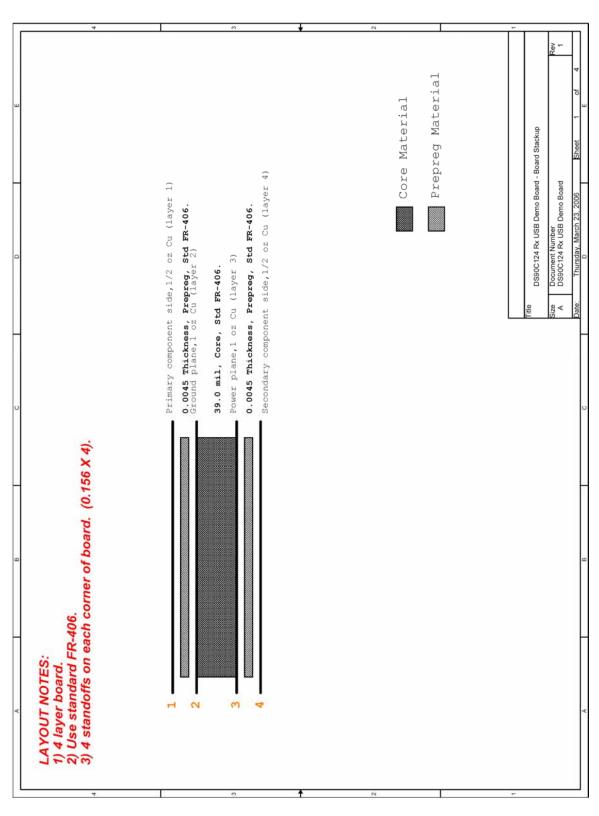

| DESERIALIZER (RX) PCB STACKUP:                                                                                                             |   |

### Introduction:

National Semiconductor's DS90C241/124 embedded clock SERDES evaluation kit contains 1 - DS90C241 Serializer (Tx) board, 1 - DS90C124 De-serializer (Rx) board, and 1 - two (2) meter high speed USB 2.0 cable.

Note: the evaluation boards are not for EMI testing. The evaluation boards were designed for easy accessibility to device pins with tap points for monitoring or applying signals, additional pads for termination, and multiple connector options.

The DS90C241/124 chipset supports a variety of display and general purpose applications. The single embedded clock LVDSe interface is well-suited for any display system interface. Typical applications include: navigation displays, automated teller machines (ATMs), POS, video cameras, global positioning systems (GPS), portable equipment/instruments, factory automation, etc.

The DS90C241 and DS90C124 can be used as a 24-bit general purpose LVDSe Serializer and De-serializer chipset designed to transmit data at clocks speeds ranging from 8 to 35 MHz.

The Serializer board accepts 3.3V\_LVCMOS input signals. The Serializer converts the 3.3V\_LVCMOS parallel inputs into a single serialized LVDSe data pair with an embedded LVDS clock. The serial data stream toggles at 28 times the base clock rate. With an input clock at 35 MHz, the transmission rate for the LVDSe line is 840Mbps.

The De-serializer board accepts the LVDSe serialized data stream with embedded clock and converts the data back into parallel 3.3V\_LVCMOS signals and clock. Note that NO external reference clock is needed to prevent harmonic.

Suggested equipment to evaluate the chipset; a 3.3V\_LVCMOS signal source such as a video generator,word generator or pulse generator and an oscilloscope with a bandwidth of at least 35 MHz will be needed.

The user needs to provide the proper 3.3V\_LVCMOS/RGB inputs and 3.3V\_LVCMOS/clock to the Serializer and also provide a proper interface from the Deserializer output to an LCD panel or test equipment. The Serializer and Deserializer boards can also be used to evaluate device parameters. A cable conversion board or harness scramble may be necessary depending on type of cable/connector interface used on the input to the DS90C241 and to the output of the DS90C124.

Example of suggested display setup:

- 1) video generator with 3.3V\_LVCMOS output

- 2) 18-bit LCD panel with a 3.3V\_LVCMOS input interface.

### **Contents of the Evaluation Kit:**

- 1) One DS90C241 Serializer board

- 2) One DS90C124 De-serializer board

- 3) One 2-meter high speed USB 2.0 cable (4-pin USB A to 5-pin mini USB)

- 4) Evaluation Kit Documentation (this manual)

- 5) DS90C241/124 Datasheet

### DS90C241/124 SERDES Typical Application:

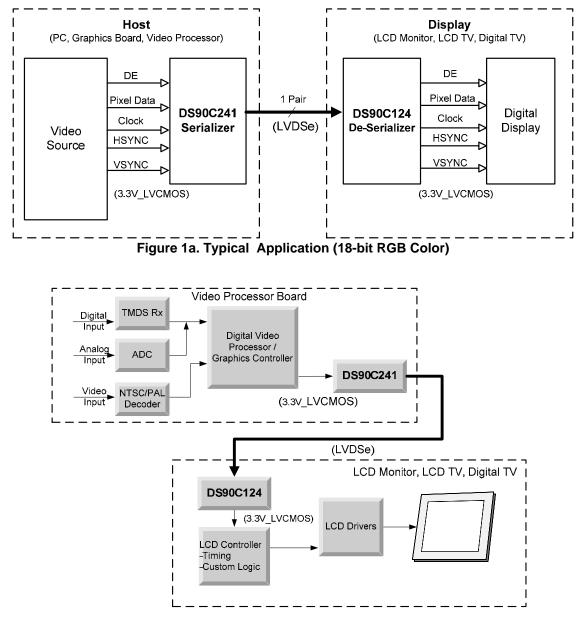

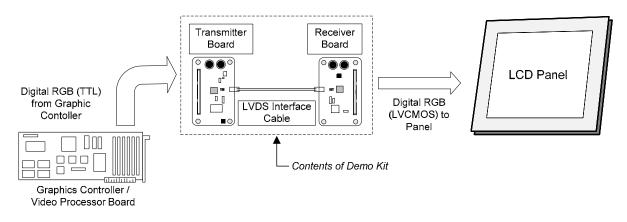

Figure 1b. Typical DS90C241/124 SERDES System Diagram

Figures 1a and 1b illustrate the use of the Chipset (Tx/Rx) in a Host to Flat Panel Interface.

The chipsets support up to 18-bit color depth TFT LCD Panels.

Refer to the proper datasheet information on Chipsets (Tx/Rx) provided on each board for more detailed information.

### How to set up the Evaluation Kit:

The PCB routing for the Tx input pins (DIN) have been laid out to accept incoming 3.3V\_LVCMOS signals from 2x25-pin IDC connector. The TxOUT/RxIN (DOUT/RIN) interface uses a single twisted pair cable (provided). The PCB routing for the Rx output pins (ROUT) are accessed through a 2x25-pin IDC connector. Please follow these steps to set up the evaluation kit for bench testing and performance measurements:

- 1) A two (2) meter high speed USB 2.0 cable has been included in the kit. Connect the

- 4-pin USB A side of cable harness to the serializer board and the otherside 5-pin mini USB jack 4-pin USB A side of cable harness to the serializer board and the otherside 5-pin mini USB jack 5

- 2) Jumpers and switches have been configured at the factory; they should not require any changes for immediate operation of the chipset. See text on Configuration settings for more details.

- 3) From the Video source, connect a flat cable (not supplied) to the Serializer board and connect another flat cable (not supplied) from the De-serializer board to the panel. Note: For non 50 ohm signal sources, provide 3.3V\_LVCMOS input signal levels into DIN[23:0] and TCLK and remove the 49.9 ohm parallel termination resistors R1-R25 on the DS90C241 Serializer board.

- Power for the Tx and Rx boards must be supplied externally through Power Jack (VDD). Grounds for both boards are connected through Power Jack (VSS) (see section below).

#### **Evaluation Board Power Connections:**

The Serializer and De-serializer boards must be powered by supplying power externally through J4 (VDD) and J5 (VSS) on Serializer Board and J4 (VDD) and J5 (VSS) on Deserializer board. Note +4V is the MAXIMUM voltage that should ever be applied to the Serializer (DS90C241) or De-serializer (DS90C124) VDD terminal. Damage to the device(s) can result if the voltage maximum is exceeded.

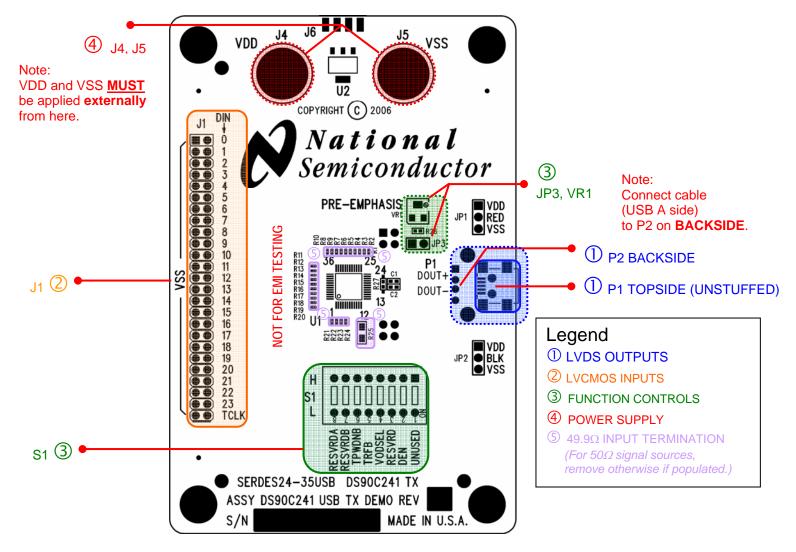

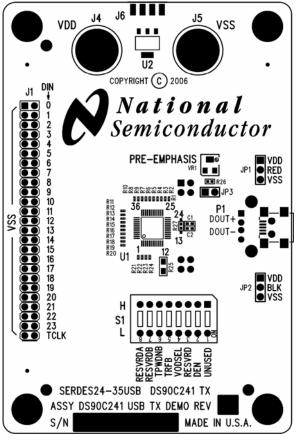

### **DS90C241 Tx Serializer Board Description:**

The 2x25-pin IDC connector J1 accepts 24 bits of 3.3V\_LVCMOS RGB data along with the clock input.

The Serializer board is powered externally from the J4 (VDD) and J5 (VSS) connectors shown below. For the Serializer to be operational, the Power Down (S1-TPWDNB) and Data Enable (S1-DEN) switches on S1 must be set HIGH. S1- RESVRDA, RESVRDB, and VODSEL must be set LOW. Rising or falling edge reference clock is user selected on S1-TRFB: HIGH (for rising edge strobing) or LOW (for falling edge strobing).

The USB connector P2 (USB-A side) on the bottom side of the board provides the interface connection to the LVDS signals to the De-serializer board. Note: P1 (mini USB) on the top side is un-stuffed and not to be used with the cable provided in the kit.

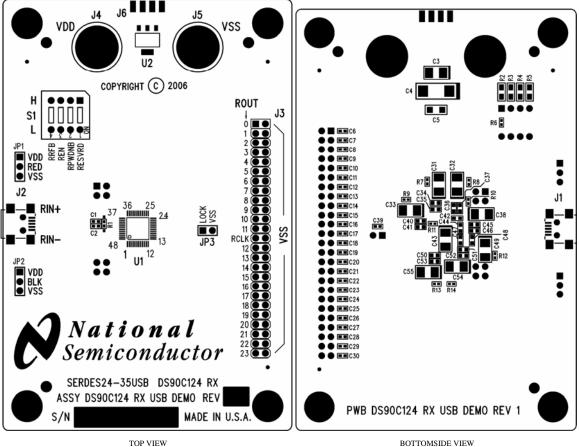

Figure 2. DS90C241 Tx Evaluation Board

### **Configuration Settings for the Tx Evaluation Board**

#### Table 1.

S1: Serializer Input Features Selection

| Reference                                                   | Description                                                         | Input = L                                                   | Input = H                        | S1                                                                                                |

|-------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------|

| RESVRDA<br><sup>1</sup> IMPORTANT<br>See user note<br>below | DCAOFF                                                              | MUST be<br>tied low for<br>normal<br>operation<br>(Default) | -                                |                                                                                                   |

| RESVRDB<br><sup>1</sup> IMPORTANT<br>See user note<br>below | DCBOFF                                                              | MUST be<br>tied low for<br>normal<br>operation<br>(Default) | -                                | RESVRDA<br>RESVRDA<br>TPWDNB<br>TRFB<br>VODSEL<br>VODSEL<br>VODSEL<br>CO<br>NDEN<br>DEN<br>UNUSED |

| TPWDNB                                                      | PoWerDowN Bar                                                       | Powers<br>Down                                              | Operational<br>( <b>Default)</b> |                                                                                                   |

| TRFB                                                        | Latch input data<br>on <b>R</b> ising or<br>Falling edge of<br>TCLK | Falling<br>Edge<br><mark>(Default)</mark>                   | Rising Edge                      |                                                                                                   |

| VODSEL                                                      | LVDS output <b>VOD</b><br>SELect                                    | ≈350mV<br><mark>(Default)</mark>                            | ≈700mV                           |                                                                                                   |

| RESVRD<br>(* IMPORTANT<br>See user note<br>below)           | RESeRVeD                                                            | MUST be<br>tied low for<br>normal<br>operation<br>(Default) |                                  |                                                                                                   |

| DEN                                                         | Output <b>D</b> ata<br><b>EN</b> abled                              | Disabled                                                    | Enabled<br>(Default)             |                                                                                                   |

| UNUSED                                                      | UNUSED                                                              | Don't care                                                  | Don't care                       |                                                                                                   |

<sup>1</sup>Note:

In user layout RESVRDA (pin 5), RESVRDB (pin 8), RESVRD (pin 13) **MUST** be tied low for proper operation.

National Semiconductor Corporation

#### Table 2.

JP3,VR1: Pre-Emphasis Feature Selection

| Reference    | Description                                                                                                                                                                                                                                                                              | OPEN<br>(floating)                                                                    | CLOSED<br>(Path to GND)                                                                           |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|

| JP3          | Pre-Emphasis – helps to<br>increase the eye pattern<br>opening in the LVDS stream                                                                                                                                                                                                        | Disabled –<br>no jumper<br>(Default)                                                  | Enabled –<br>With jumper                                                                          | JP3 |

| JP3 &<br>VR1 | Pre-Emphasis adjustment<br>(via screw)<br>JP3 <u>MUST</u> have a jumper to<br>use VR1 potentiometer.<br>VR1 = $0\Omega$ to $20K\Omega$ ,<br>JP3 + VR1 =<br>$3.01K\Omega$ (minimum) to<br>$23.01\Omega$ (maximum).<br>IPRE = $[1.2/(RPRE)] \times 20$ ,<br>RPRE (minimum) $\geq 3K\Omega$ | Clockwise<br>VR1<br>increases<br>RPRE value<br>which<br>decreases<br>pre-<br>emphasis | Counter-<br>Clockwise<br>VR1<br>decreases<br>RPRE value<br>which<br>increases<br>pre-<br>emphasis | VR1 |

Pre-emphasis user note:

Pre-emphasis must be adjusted correctly based on application frequency, cable quality, cable length, and connector quality. Maximum pre-emphasis should only be used under extreme worse case conditions; for example at the upper frequency specification of the part and/or low grade cables at maximum cable lengths. Typically all that is needed is minimum pre-emphasis. Users should start with no pre-emphasis first and gradually apply pre-emphasis until there is clock lock and no data errors. The best way to monitor the pre-emphasis effect is to hook up a differential probe to the 100 $\Omega$  termination resistor (R1) on the DS90UR124 Rx evaluation board (NOT to R27 on the DS90UR241 Tx evaluation board). The reason for monitoring R1 on the Rx side is because you want to see what the receiver will see the attenuation signal AFTER the cable/connector.

#### Table 3.

JP1, JP2: USB Red and Black wire

| Reference                             | Description                                                                                                  | VDD                       | VSS                                    | OPEN                                                      |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------|-----------------------------------------------------------|

| JP1                                   | Power wire in USB cable<br>thru P2 (and P1 not<br>mounted) connector<br>Jumper RED to VSS –                  | Red wire tied to VDD      | Red wire<br>tied to VSS<br>(Default)   | Red wire<br>floating<br>(not<br>recommended)              |

|                                       | recommended Note: Normally VDD in USB application                                                            | JP1 VDD<br>RED<br>VSS     | JP1 VDD<br>RED<br>VSS                  | JP1 VDD<br>RED<br>VSS                                     |

| JP2                                   | Power wire in USB cable<br>thru P2 (and P1 not<br>mounted) connector<br>Jumper BLACK to VSS –<br>recommended | Black wire<br>tied to VDD | Black wire<br>tied to VSS<br>(Default) | Black wire<br>floating<br>(not<br>recommended)<br>JP2 BLK |

| Note: Normally VSS in USB application |                                                                                                              | <b>●</b> VSS              | VSS                                    | <b>●</b> VSS                                              |

#### **Tx LVCMOS and LVDS Pinout by Connector**

The following three tables illustrate how the Tx inputs are mapped to the IDC connector J1, the LVDS outputs on the USB-A connector P2, and the mini USB P1 (not mounted) pinouts. Note – labels are also printed on the evaluation boards for both the  $3.3V\_LVCMOS$  input and LVDS outputs.

| J1         |              |       |            |  |  |  |

|------------|--------------|-------|------------|--|--|--|

|            | LVCMOS INPUT |       |            |  |  |  |

| pin<br>no. | name         | name  | pin<br>no. |  |  |  |

|            | GND          | DINO  |            |  |  |  |

| 1          | GND          | DIN1  | 2          |  |  |  |

| 3          |              |       | 4          |  |  |  |

| 5          | GND          | DIN2  | 6          |  |  |  |

| 7          | GND          | DIN3  | 8          |  |  |  |

| 9          | GND          | DIN4  | 10         |  |  |  |

| 11         | GND          | DIN5  | 12         |  |  |  |

| 13         | GND          | DIN6  | 14         |  |  |  |

| 15         | GND          | DIN7  | 16         |  |  |  |

| 17         | GND          | DIN8  | 18         |  |  |  |

| 19         | GND          | DIN9  | 20         |  |  |  |

| 21         | GND          | DIN10 | 22         |  |  |  |

| 23         | GND          | DIN11 | 24         |  |  |  |

| 25         | GND          | DIN12 | 26         |  |  |  |

| 27         | GND          | DIN13 | 28         |  |  |  |

| 29         | GND          | DIN14 | 30         |  |  |  |

| 31         | GND          | DIN15 | 32         |  |  |  |

| 33         | GND          | DIN16 | 34         |  |  |  |

| 35         | GND          | DIN17 | 36         |  |  |  |

| 37         | GND          | DIN18 | 38         |  |  |  |

| 39         | GND          | DIN19 | 40         |  |  |  |

| 41         | GND          | DIN20 | 42         |  |  |  |

| 43         | GND          | DIN21 | 44         |  |  |  |

| 45         | GND          | DIN22 | 46         |  |  |  |

| 47         | GND          | DIN23 | 48         |  |  |  |

| 49         | GND          | TCLK  | 50         |  |  |  |

| P2<br>(bottom side) |       |  |  |

|---------------------|-------|--|--|

| LVDS C              | UTPUT |  |  |

| pin no.             | name  |  |  |

| 1                   | JP1   |  |  |

| 2                   | DOUT+ |  |  |

| 3                   | DOUT- |  |  |

| 4                   | JP2   |  |  |

| P1<br>(topside) |                   |  |  |

|-----------------|-------------------|--|--|

| (not mo         | ounted)<br>OUTPUT |  |  |

| pin no.         | name              |  |  |

| 5               | JP2               |  |  |

| 4               | NC                |  |  |

| 3               | DOUT-             |  |  |

| 2               | DOUT+             |  |  |

| 1               | JP1               |  |  |

### BOM (Bill of Materials) Serializer PCB:

DS90C241 Tx USB Demo Board - Board StackupRevised: Thursday, March 23, 2006DS90C241 Tx USB Demo BoardRevision: 1Bill Of MaterialsMarch 23,200618:52:42

| ltem | Qty | Reference                                                                                          | Part               | PCB Footprint                   |

|------|-----|----------------------------------------------------------------------------------------------------|--------------------|---------------------------------|

| 1    | 2   | C1,C2                                                                                              | 0.1uF              | CAP/HDC-0402                    |

| 2    | 1   | C3                                                                                                 | 2.2uF              | 3528-21_EIA                     |

| 3    | 1   | C4                                                                                                 | 22uF               | CAP/N                           |

| 4    | 1   | C5                                                                                                 | 0.1uF              | CAP/HDC-1206                    |

| 5    | 5   | C6,C9,C10,C13,C20                                                                                  | 22uF               | CAP/EIA-B 3528-21               |

| 6    | 5   | C7,C11,C15,C16,C19                                                                                 | 0.01uF             | CAP/HDC-0603                    |

| 7    | 5   | C8,C12,C14,C17,C18                                                                                 | 0.1uF              | CAP/HDC-0603                    |

| 8    | 2   | JP2,JP1                                                                                            | 3-Pin Header       | Header/3P                       |

| 9    | 1   | JP3                                                                                                | 2-Pin Header       | Header/2P                       |

| 10   | 1   | J1                                                                                                 | IDC2X25_Unshrouded | IDC-50                          |

| 11   | 2   | J5,J4                                                                                              | BANANA             | CON/BANANA-S                    |

| 12   | 1   | P1                                                                                                 | mini USB 5pin_open | mini_USB_surface_mount          |

| 13   | 1   | P2                                                                                                 | USB A              | USB_TYPE_A_4P                   |

| 14   | 24  | R1,R2,R3,R4,R5,R6,R7,R8,<br>R9,R10,R11,R12,R13,R14,<br>R15,R16,R17,R18,R19,R20,<br>R21,R22,R23,R24 | 49.9ohm_open       | RES/HDC-0201                    |

| 15   | 1   | R25                                                                                                | 49.9ohm_open       | RES/HDC-0805                    |

| 16   | 1   | R26                                                                                                | 5.76K (3.01K)      | RES/HDC-0402                    |

| 17   | 1   | R27                                                                                                | 100 ohm,0402       | RES/HDC-0402                    |

| 18   | 5   | R28,R30,R32,R33,R35                                                                                | 0 Ohm,0402         | RES/HDC-0402                    |

| 19   | 8   | R38,R39,R40,R41,R42,R43,<br>R44,R45                                                                | 10K                | RES/HDC-0805                    |

| 20   | 1   | S1                                                                                                 | SW DIP-8           | DIP-16                          |

| 21   | 1   | U1                                                                                                 | DS90C241           | 48 ld TQFP<br>Surface Mount 4mm |

| 22   | 1   | VR1                                                                                                | SVR20K             | Square                          |

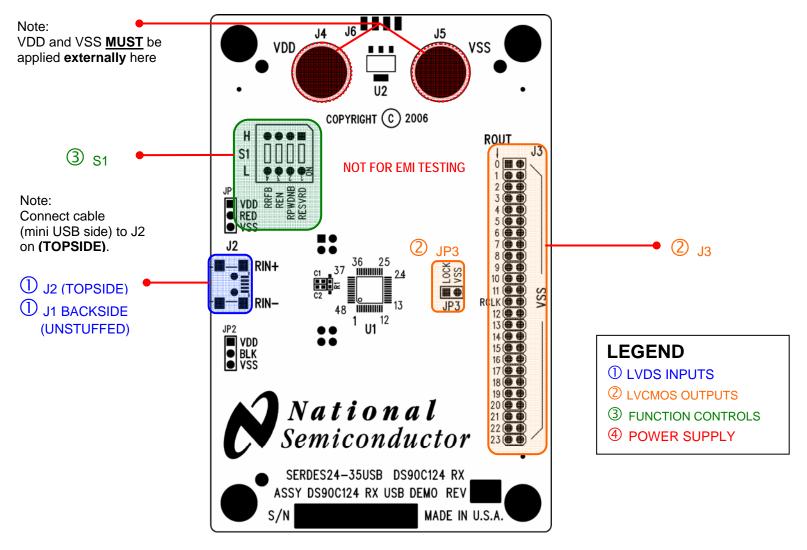

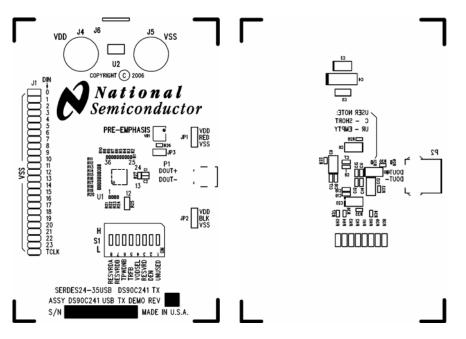

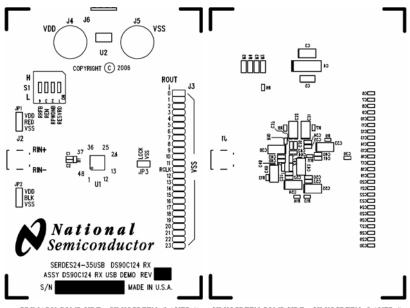

### DS90C124 Rx De-serializer Board Description:

The USB connector J2 (mini USB) on the topside of the board provides the interface connection for LVDS signals to the Serializer board. Note: J1 (mini USB) on the bottom side is un-stuffed and not used with the cable provided in the kit.

The De-serializer board is powered externally from the J4 (VDD) and J5 (VSS) connectors shown below. For the De-serializer to be operational, the Power Down (RPWDNB) and Receiver Enable (REN) switches on S1 must be set HIGH. Rising or falling edge reference clock is user selected by S1-RRFB: HIGH (for rising edge strobing) or LOW (for falling edge strobing).

The 50 pin IDC Connector J3 provides access to the 24 bit 3.3V\_LVCMOS and clock outputs.

Figure 3. DS90C124 Rx Evaluation Board

### **Configuration Settings for the Rx Evaluation Board**

#### Table 4.

S1: De-serializer Input Features Selection

| Reference                                                   | Description                                                                      | Input = L                   | Input = H                | S1                              |

|-------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------|--------------------------|---------------------------------|

| RFB                                                         | Latch output data on <b>R</b> ising<br>or <b>F</b> alling Data Strobe of<br>RCLK | Falling<br>(Default)        | Rising                   |                                 |

| REN                                                         | Receiver Output ENabled                                                          | Disabled                    | Enabled<br>(Default)     | S1 ↓ 0 0 ↓<br>L ♥ ♥ ♥ ♥ ♥ ₹     |

| RPWDNB                                                      | PoWerDowN Bar                                                                    | Power<br>Down<br>(Disabled) | Operational<br>(Default) | RRFB<br>REN<br>RPWDNB<br>RESVRD |

| RESVRD<br><sup>2</sup> IMPORTANT<br>See user note<br>below) | RESeRVeD                                                                         | Don't care                  | Don't care               |                                 |

#### Table 5.

JP3: Output Lock Monitor

| Reference | Description                                      | Output = L | Output = H | JP3 |

|-----------|--------------------------------------------------|------------|------------|-----|

| LOCK      | Receiver PLL LOCK                                | unlocked   | locked     |     |

|           | Note:<br>DO NOT PUT A SHORTING<br>JUMPER IN JP3. |            |            |     |

<sup>2</sup> Note: In user layout RESVRD (pin 2) **MUST** be tied low for proper operation.

#### Table 6.

JP1, JP2: USB Red and Black wire

| Reference | Description                                                                                           | VDD                    | VSS                                    | OPEN                                           |

|-----------|-------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------|------------------------------------------------|

| JP1       | Power wire in USB cable<br>thru J2 (and J1 not                                                        | Red wire tied to VDD   | Red wire<br>tied to VSS                | Red wire<br>floating                           |

|           | <i>mounted)</i> connector<br>Jumper RED to VSS –<br>recommended                                       |                        |                                        | (not<br>recommended)                           |

|           | Note: Normally VDD in USB application                                                                 | JP1 <b>RED</b><br>VSS  | JP1 RED<br>VSS                         | JP1 RED<br>VSS                                 |

| JP2       | Power wire in USB cable<br>thru J2 <i>(and J1 not<br/>mounted)</i> connector<br>Jumper BLACK to VSS – | Black wire tied to VDD | Black wire<br>tied to VSS<br>(Default) | Black wire<br>floating<br>(not<br>recommended) |

|           | recommended Note: Normally VSS in USB application                                                     | JP2 VDD<br>BLK<br>VSS  | JP2 VDD<br>BLK<br>VSS                  | JP2 VDD<br>BLK<br>VSS                          |

| J2        | pin 5 BLACK WIRE                                                                                      |                        |                                        |                                                |

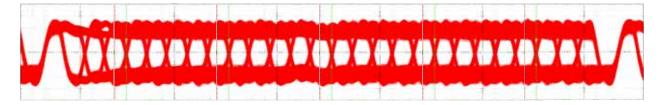

The following picture depicts a typical example of the LVDSe serial stream. This snapshot was taken with a differential probe across the 100 ohm termination resistor R1 on the DS90C124 Rx evaluation board. R1 is the termination resistor to the RxIN +/-. Note: The scope was triggered, with a separate probe, on TCLK, the input clock into the DS90C241 Tx. To view the serial stream correctly, do not trigger on the probe monitoring the serial stream.

#### **Rx LVDS Pinout and LVCMOS by Connector**

The following three tables illustrate how the Rx outputs are mapped to the IDC connector J1, the mini USB LVDS connector J2, and the mini USB LVDS connector J3 pinouts. Note – labels are also printed on the evaluation boards for both the LVDS inputs and 3.3V\_LVCMOS outputs.

| J1<br>LVCMOS OUTPUT       |        |     |    |  |  |

|---------------------------|--------|-----|----|--|--|

| pin no. name name pin no. |        |     |    |  |  |

| 1                         | ROUT0  | GND | 2  |  |  |

| 3                         | ROUT1  | GND | 4  |  |  |

| 5                         | ROUT2  | GND | 6  |  |  |

| 7                         | ROUT3  | GND | 8  |  |  |

| 9                         | ROUT4  | GND | 10 |  |  |

| 11                        | ROUT5  | GND | 12 |  |  |

| 13                        | ROUT6  | GND | 14 |  |  |

| 15                        | ROUT7  | GND | 16 |  |  |

| 17                        | ROUT8  | GND | 18 |  |  |

| 19                        | ROUT9  | GND | 20 |  |  |

| 21                        | ROUT10 | GND | 22 |  |  |

| 23                        | ROUT11 | GND | 24 |  |  |

| 25                        | RCLK   | GND | 26 |  |  |

| 27                        | ROUT12 | GND | 28 |  |  |

| 29                        | ROUT13 | GND | 30 |  |  |

| 31                        | ROUT14 | GND | 32 |  |  |

| 33                        | ROUT15 | GND | 34 |  |  |

| 35                        | ROUT16 | GND | 36 |  |  |

| 37                        | ROUT17 | GND | 38 |  |  |

| 39                        | ROUT18 | GND | 40 |  |  |

| 41                        | ROUT19 | GND | 42 |  |  |

| 43                        | ROUT20 | GND | 44 |  |  |

| 45                        | ROUT21 | GND | 46 |  |  |

| 47                        | ROUT22 | GND | 48 |  |  |

| 49                        | ROUT23 | GND | 50 |  |  |

| J2<br>(topside)<br>LVDS OUTPUT |       |  |

|--------------------------------|-------|--|

| pin no.                        | name  |  |

| 1                              | JP1   |  |

| 2                              | DOUT+ |  |

| 3                              | DOUT- |  |

| 4                              | NC    |  |

| 5                              | JP2   |  |

| J1            |       |  |

|---------------|-------|--|

| (bottom side) |       |  |

| (not mounted) |       |  |

| LVDS OUTPUT   |       |  |

| pin no.       | name  |  |

| 5             | JP2   |  |

| 4             | NC    |  |

| 3             | DOUT- |  |

| 2             | DOUT+ |  |

| 1             | JP1   |  |

|               |       |  |

#### BOM (Bill of Materials) De-serializer PCB:

DS90C124 Rx USB Demo Board - Board Stackup Revised: Thursday, March 23, 2006 DS90C124 Rx USB Demo Board Revision: 1 Bill Of Materials March 23,2006 19:19:22

| ltem | Qty | Reference                                                                                                           | Part               | PCB Footprint          |

|------|-----|---------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|

| 1    | 2   | C2,C1                                                                                                               | 0.1uF              | CAP/HDC-0402           |

| 2    | 1   | C3                                                                                                                  | 2.2uF              | 3528-21 EIA            |

| 3    | 1   | C4                                                                                                                  | 22uF               | CAP/N                  |

| 4    | 1   | C5                                                                                                                  | 0.1uF              | CAP/HDC-1206           |

| 5    | 26  | C6,C7,C8,C9,C10,C11,C12,<br>C13,C14,C15,C16,C17,C18,<br>C19,C20,C21,C22,C23,C24,<br>C25,C26,C27,C28,C29,C30,<br>C39 | open0402           | CAP/HDC-0402           |

| 6    | 8   | C31,C32,C33,C38,C43,C49,<br>C54,C55                                                                                 | 22uF               | CAP/EIA-B 3528-21      |

| 7    | 8   | C34,C37,C40,C44,C45,C48,<br>C52,C53                                                                                 | 0.1uF              | CAP/HDC-0603           |

| 8    | 8   | C35,C36,C41,C42,C46,C47,<br>C50,C51                                                                                 | 0.01uF             | CAP/HDC-0603           |

| 9    | 2   | JP2,JP1                                                                                                             | 3-Pin Header       | Header/3P              |

| 10   | 1   | JP3                                                                                                                 | 2-Pin Header       | Header/2P              |

| 11   | 1   | J1                                                                                                                  | mini USB 5pin_open | mini_USB_surface_mount |

| 12   | 1   | J2                                                                                                                  | mini USB 5pin      | mini_USB_surface_mount |

| 13   | 1   | J3                                                                                                                  | IDC2X25_Unshrouded | IDC-50                 |

| 14   | 2   | •                                                                                                                   | BANANA             | CON/BANANA-S           |

| 15   | 1   | R1                                                                                                                  | 100 ohm,0402       | RES/HDC-0402           |

| 16   | 1   | R2                                                                                                                  | 10K_open           | RES/HDC-0805           |

| 17   | 3   | R3,R4,R5                                                                                                            | 10K                | RES/HDC-0805           |

| 18   | 8   | R7,R8,R9,R10,R11,R12,R13,<br>R14                                                                                    | 0 Ohm,0402         | RES/HDC-0402           |

| 19   | 1   | S1                                                                                                                  | SW DIP-4           | DIP-4                  |

| 20   | 1   | U1                                                                                                                  | DS90C124           | 48 pin TQFP            |

### **Typical Connection and Test Equipment**

The following is a list of typical test equipment that may be used to generate signals for the TX inputs:

- 1) Digital Video Source for generation of specific display timing such as Digital Video Processor or Graphics Controller with digital RGB (3.3V\_LVCMOS) output.

- 2) Astro Systems VG-835 This video generator may be used for video signal sources for 18-bit Digital 3.3V\_LVCMOS/RGB.

- 3) Any other signal / video generator that generates the correct input levels as specified in the datasheet.

- 4) Optional Logic Analyzer or Oscilloscope

The following is a list of typical test equipment that may be used to monitor the input and output signals from the RX:

- 1) LCD Display Panel which supports digital RGB (3.3V\_LVCMOS) inputs.

- 2) Logic Analyzer or Oscilloscope

- 3) Any SCOPE with a bandwidth of at least 35MHz for 3.3V\_LVCMOS and/or 1GHz for looking at the differential signal.

LVDS signals may be easily measured with high impedance / high bandwidth differential probes such as the TEK P6247 or P6248 differential probes.

The picture below shows a typical test set up using a Graphics Controller and LCD Panel.

Figure 4. Typical SERDES Setup of LCD Panel Application

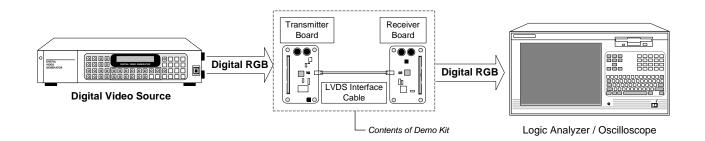

The picture below shows a typical test set up using a generator and scope.

Figure 5. Typical SERDES Test Setup for Evaluation

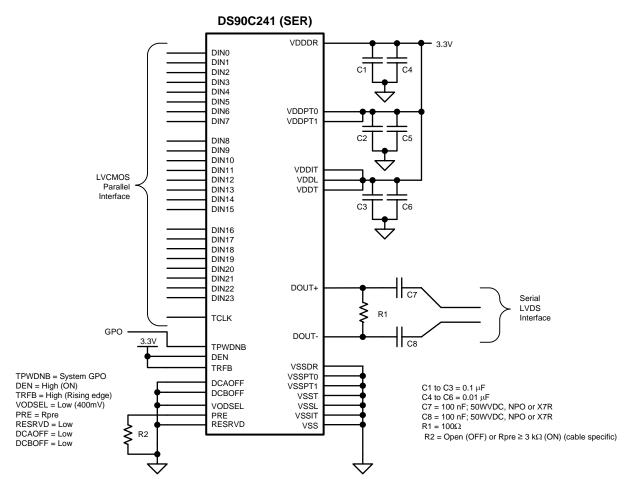

#### **Typical Connection Diagram Tx – User Quick Reference**

Note:

VDDs can be combined into a minimum of three (3) groupings as shown: Analog-LVDS, Analog-PLL/VCO, Digital Decoupling specified (C1-C6) is the minimum that should be used.

#### Figure 6. Typical DS90C241 Tx SERDES Hookup

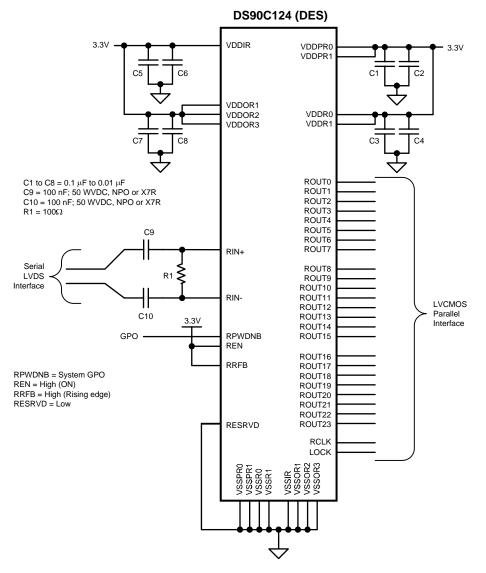

#### **Typical Connection Diagram Rx – User Quick Reference**

Note:

VDDs can be combined into a minimum of four (4) groupings as shown above: Analog-PLL/VCO, Digital-Logic, Analog-LVDS, Digital-LVCMOS O/P Decoupling specified (C1-C8) is the minimum that should be used.

#### Figure 7. Typical DS90C124 Rx SERDES Hookup

#### **Troubleshooting Demo Setup**

# NOTE: The DS90C241 and DS90C124 are NOT USB compliant and should not be plugged into a USB device nor should a USB device be plugged into the evaluation boards.

If the evaluation boards are not performing properly, use the following as a guide for quick solutions to potential problems. If the problem persists, please contact the local Sales Representative for assistance.

#### QUICK CHECKS:

- 1. Check that Powers and Grounds are connected to both Tx AND Rx boards.

- Check the supply voltage (typical 3.3V) and also current draw with both Tx and Rx boards. The Serializer board should draw about 40-50mA with clock and all data bits switching at 35MHz. The De-serializer board should draw about 70-80mA with clock and all data bits switching at 35MHz.

- 3. Verify input clock and input data signals meet requirements (VIL, VIH, tset, thold), Also verify that data is strobed on the selected rising/falling (RFB pin) edge of the clock.

- 4. Check that the Jumpers and Switches are set correctly.

- 5. Check that the cable is properly connected.

| Problem                                                                                                       | Solution                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| There is only the output clock.                                                                               | Make sure the data is applied to the correct input pin.                                                                                                                                |

| There is no output data.                                                                                      | Make sure data is valid at the input.                                                                                                                                                  |

| No output data and clock.                                                                                     | Make sure Power is on. Input data and clock are active and connected correctly.                                                                                                        |

|                                                                                                               | Make sure that the cable is secured to both evaluation boards.                                                                                                                         |

| Power, ground, input data and                                                                                 | Check the Power Down pins of both Serializer and                                                                                                                                       |

| input clock are connected correctly, but no outputs.                                                          | De-serializer boards to make sure that the devices<br>are enabled (/PD=VDD) for operation. Also check<br>DEN on the Serializer board and REN on the<br>Deserializer board is set HIGH. |

| The devices are pulling more than 1A of current.                                                              | Check for shorts in the cables connecting the TX and RX boards.                                                                                                                        |

| After powering up the<br>evaluation boards, the power<br>supply reads less than 3V<br>when it is set to 3.3V. | Use a larger power supply that will provide enough current for the evaluation boards, a 500mA minimum power supply is recommended.                                                     |

#### TROUBLESHOOTING CHART

Note: Please note that the following references are supplied only as a courtesy to our valued customers. It is not intended to be an endorsement of any particular equipment or hardware supplier.

#### **Equipment References**

Digital Video Pattern Generator – Astro Systems VG-835 (or equivalent):

Astro Systems 425 S. Victory Blvd. Suite A Burbank, CA 91502 Phone: (818) 848-7722 Fax: (818) 848-7799 www.astro-systems.com

#### Extra Component References

TDK Corporation of America 1740 Technology Drive, Suite 510 San Jose, CA 95110 Phone: (408) 437-9585 Fax: (408) 437-9591 <u>www.component.tdk.com</u> Optional EMI Filters – TDK Chip Beads (or equivalent)

#### Cable References

The LVDS interface cable included in the kit is a standard off-the-shelf high-speed USB 2.0 with a 4-pin USB A type on one end and a 5-pin mini USB on the other end and is included for demonstration purposes only.

NOTE: The DS90C241 and DS90C124 are NOT USB compliant and should not be plugged into a USB device nor should a USB device be plugged into the evaluation boards.

The inclusion of the USB cable in the kit is for:

- 1) Demonstrating the robustness of the LVDS link over ordinary twisted pair data cables.

- 2) Readily available and in different lengths without having custom cables made.

- For optimal performance, we recommend Shielded Twisted Pair (STP)  $100\Omega$  differential impedance cable for high-speed data applications.

### Appendix Serializer (Tx) PCB Schematic:

Date: 2/27/2008 Page 25 of 39

### **De-serializer (Rx) PCB Schematic:**

Date: 2/27/2008 Page 29 of 39

Date: 2/27/2008 Page 30 of 39

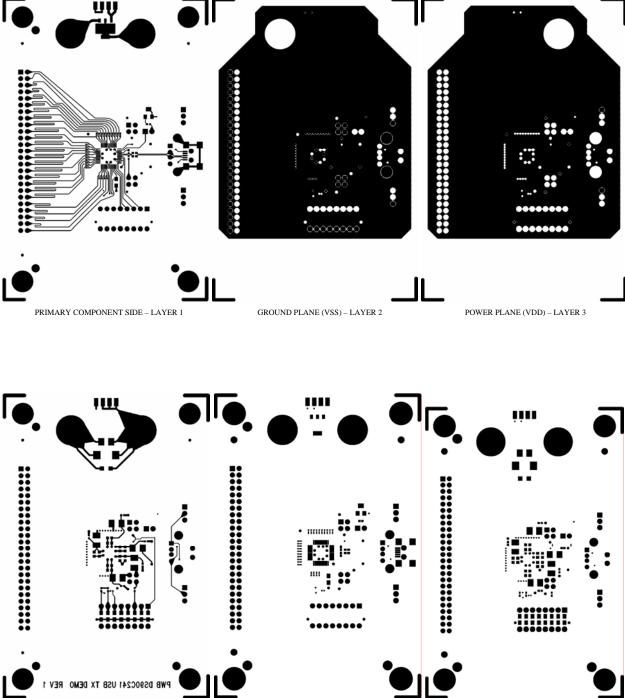

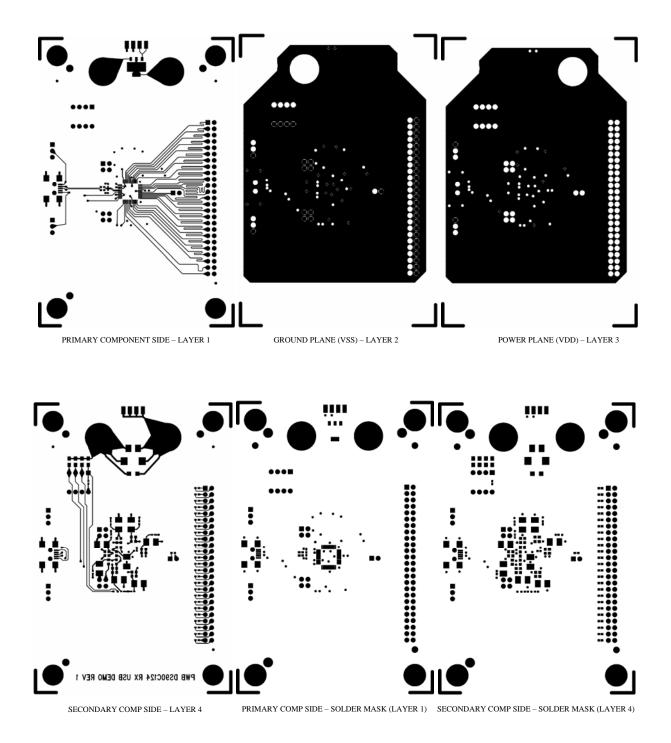

### Serializer (Tx) PCB Layout:

TOP VIEW

C3 C4 C5 USER NOTE: C - SHORT UR - EMPTY **E** R28 C6 P2 DOUT⊕ 2005555 C8 333 X. C20 R35 87**8 8**8 2 Ī R40 R41 R42 R43 838 39 R44 R45 PWB DS90C241 USB TX DEMO REV 1

BOTTOMSIDE VIEW

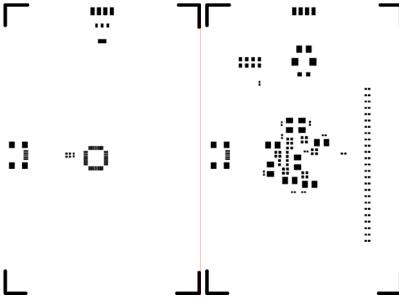

SECONDARY COMP SIDE - LAYER 4 PRIMARY COMP SIDE - SOLDER MASK (LAYER 1) SECONDARY COMP SIDE - SOLDER MASK (LAYER 4)

PRIMARY COMP SIDE – SOLDER PASTE (LAYER 1) SECONDARY COMP SIDE – SOLDER PASTE (LAYER 4)

PRIMARY COMP SIDE - SILKSCREEN (LAYER 1)

SILKSCREEN COMP SIDE - SILKSCREEN (LAYER 4)

### Serializer (Tx) PCB Stackup:

| HOLE CHART |       |     |        |               |

|------------|-------|-----|--------|---------------|

| CODE       | SIZE  | QTY | PLATED | TOL           |

| +          | 0.006 | 34  | YES    | ± .003        |

| X          | 0.014 | 20  | YES    | ± .003        |

|            | 0.036 | 6   | YES    | ± .003        |

| $\diamond$ | 0.043 | 82  | YES    | <u>±</u> .003 |

|            |       |     |        |               |

| Χ          | 0.091 | 2   | YES    | ± .003        |

| A          | 0.125 | 3   | NO     | +.003000      |

| В          | 0.156 | 4   | YES    | <u>±</u> .004 |

| С          | 0.265 | 2   | YES    | ± .005        |

|            |       |     |        |               |

|            |       |     |        |               |

NOTES: UNLESS OTHERWISE SPECIFIED

1. PRIMARY COMPONENT SIDE IS SHOWN.

2. HOLES MARKED " A " ARE TOOLING HOLES, UNPLATED, AND SHALL BE "ONCE" DRILLED.

- 3. FABRICATE USING MASTER FILM DS90C241 USB TX DEMO REV 1. USE GERBER FILE A457BOA.PHO FOR BOARD ROUTE.

- ACCEPTABILITY SHALL BE BASED ON IPC-A-600, CLASS 2 NATERIAL: BASE MATERIAL IS NEMAL-I GRADE FR-406, COLOR GREEN, 0.062 INCH NOM. THICKNESS. COPPER CLADDING SHALL BE 1/2 OZ FOR OUTSIDE LAYERS AND 1 OZ FOR INSIDE LAYERS.

- 6. PLATING: ALL HOLES AND CONDUCTIVE SURFACES SHALL BE PLATED WITH A MIN. OF .001 INCH COPPER.

- SURFACE FINISH: GOLD FLASH .000004 MIN

- 7. FABRICATION TOLERANCES: END PRODUCT CONDUCTOR WIDTHS AND LAND DIAMETERS SHALL NOT VARY MORE THAN .002 INCH FROM THE 1:1 DIMENSIONS OF THE MASTER PATTERN. THE CONDUCTIVE PATTERN SHALL BE POSITIONED SO THAT THE LOCATION OF ANY LAND SHALL BE WITHIN .010 INCH DIAMETER TO THE TRUE POSITION OF THE HOLE IT CIRCUMSCRIBES THE MINIMUM ANNULAR RING SHALL BE .002 INCH. BOW AND TWIST SHALL NOT EXCEED .010 INCH PER INCH.

- 8. SOLDERMASK BOTH SIDES PER IPC-SM-840, TYPE A, CLASS B. COLOR-GREEN. THERE SHALL BE NO SOLDERMASK ON ANY LAND.

- SILKSCREEN THE LEGEND ON BOTH SIDES USING NON CONDUCTIVE EPOXY INK, COLOR-WHITE. THERE SHALL BE NO INK ON ANY LAND.

- 10. THE .008 TRACES (LAYER 1) TO BE 50 OHM SINGLE ENDED IMPEDANCE THE .007 TRACES (LAYER 1) TO BE 100 OHM DIFFERENTIAL IMPEDANCE, AND THE DIELECTRIC REFERENCED IN BOARD STACK DETAIL IS SUGESTED. HOWEVER, TRACE WIDTHS AND OR DIELECTRIC THICKNESS MAY BE MICRO-MODIFIED IN ORDER TO FABRICATE BOARDS TO THE REQUIRED IMPEDANCE NOMINALS TO A TOLERANCE OF +/- 5%

- 11. BOARD TO BE FABRICATED IN COMPLIANCY TO ROHS REQUIREMENTS.

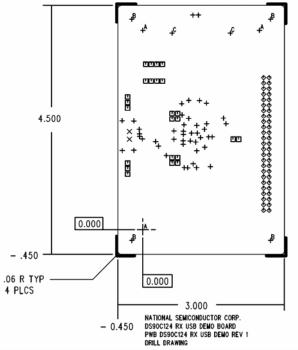

#### Deserializer (Rx) Demo PCB Layout:

BOTTOMSIDE VIEW

PRIMARY COMP SIDE - SOLDER PASTE (LAYER 1) SECONDARY COMP SIDE - SOLDER PASTE (LAYER 4)

PRIMARY COMP SIDE – SILKSCREEN (LAYER 1) SILKSCREEN COMP SIDE – SILKSCREEN (LAYER 4)

### **Deserializer (Rx) PCB Stackup:**

| HOLE CHART |       |     |        |           |

|------------|-------|-----|--------|-----------|

| CODE       | SIZE  | QTY | PLATED | TOL       |

| +          | 0.012 | 45  | YES    | ± .003    |

| Х          | 0.035 | 2   | YES    | ± .003    |

|            | 0.040 | 24  | YES    | ± .003    |

| $\diamond$ | 0.045 | 50  | YES    | ± .003    |

|            |       |     |        |           |

|            |       |     |        |           |

| A          | 0.125 | 3   | NO     | + .003000 |

| В          | 0.156 | 4   | YES    | ± .005    |

| C          | 0.265 | 2   | YES    | ± .005    |

|            |       |     |        |           |

|            |       |     |        |           |

|            |       |     |        |           |

#### NOTES: UNLESS OTHERWISE SPECIFIED

- PRIMARY COMPONENT SIDE IS SHOWN. HOLES MARKED " A " ARE TOOLING HOLES, UNPLATED, AND SHALL BE "ONCE" DRILLED. 2.

- FABRICATE USING MASTER FILM DS90C124 RX USB DEMO REV 1. USE BOARD OUTLINE FILE A459BOA.PHO FOR BOARD ROUTE. 3.

- ACCEPTABILITY SHALL BE BASED ON IPC-A-600, CLASS 2 MATERIAL: BASE MATERIAL IS NEMAL-1 GRADE FR-406, COLOR GREEN,

- 5: 0.062 INCH NOM. THICKNESS. COPPER CLADDING SHALL BE 1/2 OZ. OUTSIDE LAYERS AND 1 OZ INSIDE LAYERS.

- PLATING: ALL HOLES AND CONDUCTIVE SURFACES SHALL BE PLATED 6. WITH A MIN. OF .001 INCH COPPER. GOLD FLASH .000005 MIN.

- 7. FABRICATION TOLERANCES: END PRODUCT CONDUCTOR WIDTHS AND LAND DIAMETERS SHALL NOT VARY MORE THAN .003 INCH FROM THE 1:1 DIMENSIONS OF THE MASTER PATTERN. THE CONDUCTIVE PATTERN SHALL BE POSITIONED SO THAT THE LOCATION OF ANY LAND SHALL BE WITHIN .010 INCH DIAMETER TO THE TRUE POSITION OF THE HOLE IT CIRCUMSCRIBES THE MINIMUM ANNULAR RING SHALL BE .002 INCH. BOW AND TWIST SHALL NOT EXCEED .010 INCH PER INCH.

- 8. SOLDERMASK BOTH SIDES PER IPC-SM-840, TYPE A, CLASS B. COLOR-GREEN. THERE SHALL BE NO SOLDERMASK ON ANY LAND.

- 9. SILKSCREEN THE LEGEND ON BOTH SIDES USING NON CONDUCTIVE EPOXY INK, COLOR-WHITE. THERE SHALL BE NO INK ON ANY LAND.

- 10. THE .008 TRACES (LAYER 1) TO BE 50 OHM SINGLE ENDED IMPEDANCE AND THE .007 TRACES (LAYER 1) TO BE 100 OHM DIFFERENTAIL INPEDANCE AND THE DIELECTRIC REFERENCED IN BOARD STACK DETAIL IS SUGGESTED. HOWEVER, TRACE WIDTHS AND OR DIELECTRIC THICKNESS MAY BE MICRO-MODIFIED IN ORDER TO FABRICATE BOARDS TO THE REQUIRED IMPEDANCE NOMINALS TO A TOLERANCE OF +/- 5%.

- 11. BOARD TO BE FABRICATED IN COMPLIANCY TO ROHS REQUIREMENTS.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        | TI 505 0                        |                               |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated