EVM Application #1

# Creating a Pulse Width Modulated Signal with a Fixed Duty Cycle Using the TMS320F240 EVM

APPLICATION REPORT: SPRA410

David Figoli

Digital Signal Processing Solutions January 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty, or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

| Abstract                                          | 7    |

|---------------------------------------------------|------|

| Product Support                                   | 8    |

| World Wide Web                                    |      |

| Email                                             | 8    |

| Overview                                          | 9    |

| Module(s) Used:                                   |      |

| Input:                                            |      |

| Output:                                           | 9    |

| Background and Methodology:                       | 9    |

| PLL Module                                        |      |

| Digital I/O Ports                                 | . 10 |

| Event Manager Module - General Purpose (GP) Timer | . 10 |

## Contents

| Figures                                       |      |

|-----------------------------------------------|------|

| Figure 1. Active High and Active Low Polarity | . 12 |

# **EVM Application #1**

# Creating a Pulse Width Modulated Signal with a Fixed Duty Cycle Using the TMS320F240 EVM

#### Abstract

This document explains how the EVM Application #1 generates a Pulse Width Modulated (PWM) signal and includes the following information.

- An overview, background and methodology on what the EVM Application #1 is and how it works

- Listing of the three modules which must be configured

- Formula for performing period register and compare register value calculations

- A figure that shows the difference between active high and active low polarity

- □ Assembly code for generating a pulse width modulated signal for the target system, the Texas Instruments (TI<sup>™</sup>) TMS320F240 Evaluation Module (EVM)

### **Product Support**

#### World Wide Web

Our World Wide Web site at www.ti.com contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

#### Email

ļŀ

For technical issues or clarification on switching products, please send a detailed email to dsph@ti.com. Questions receive prompt attention and are usually answered within one business day.

### Overview

This application generates a pulse width modulated (PWM) signal asymmetrically (edge-triggered) using C2xx Assembly code. The PWM frequency is 20kHz with a 20% high duty cycle. The algorithm described in this application report was implemented using the TI TMS320F240 EVM.

#### Module(s) Used

- Event Manager Module

- General Purpose Timer 1

#### Input

None

#### Output

T1PWM / T1CMP

### **Background and Methodology**

The module used to create the PWM signal is the General Purpose Timer of the Event Manager Module. Although the primary module is the Event Manager Module, other components of the TMS320F240 need to be configured *prior* to creating the PWM signal.

#### PLL Module

The first module that needs to be configured is the PLL module. The PLL clock module provides all the necessary clock signals for the F240. It is important to know the speed of the CPUCLK in order to create the proper PWM frequency. The PLL receives its CLKIN from the 10MHz crystal oscillator of the EVM. Since the PLL is set up to divide the CLKIN frequency by 2 and then multiply the frequency by 4, the resulting CPUCLK frequency is 20MHz.

#### **Digital I/O Ports**

Because the Digital I/O Ports pins are shared with pins of other peripherals of the TMS320F240, the pins necessary to output the PWM signal need to be configured. The PWM output of GP Timer 1 shares its pin with I/O Port B3. If the pin is not configured properly (i.e. the pin is an I/O pin rather than a Timer 1 Output pin), the PWM may be generated internally, but the PWM signal will have no way of being output. As a result, Output Control Register A (OCRA) needs to be configured so that the pin (in this case, pin 105) to be T1PWM/T1CMP instead of IOPB3.

#### Event Manager Module–General Purpose (GP) Timer

Once the CPUCLK frequency has been determined from the PLL module and the output pin has been configured for the General Purpose Timer 1, the GP Timer 1 in the Event Manager Module can be configured. To create a PWM signal, the registers GPTCON, T1CNT, T1CMPR, T1PR, and T1CON need to be set.

To create an asymmetric PWM signal, the timer is set to the Continuous-Up Count Mode. (If a symmetric PWM signal is desired, then the Timer should be set to the Continuous-Up/Down Count Mode.) Since the CPUCLK is 20MHz, it is easy to obtain a 20kHz signal without pre-scaling the input clock, thus the prescale is set to divide by 1. Furthermore, to create a consistent duty cycle for the PWM, the compare register should be loaded when the counter value is 0 or when the counter equals the value in the period register. Since the compare value is constant in this application, the selection of the reload condition for the compare register is not crucial.

In other applications where the compare value will be changed, the reload condition of the compare register becomes important. However, the F240's compare registers are shadowed, as a result, new compare values can be loaded while a value is present in the compare register without affecting the current value in the register unless the reload condition is to load immediately. The reload condition is determined by bits 3-2 in TxCON.

To create a PWM signal with a specific frequency and duty cycle, the values for the period and the compare registers need to be calculated. In order to calculate the values, the proper CLKIN frequency needs to be known; in this application, the 10MHz crystal that is on the EVM board is used.

Period register value calculation:

|                | CLKIN(OSC)              | PLL Multiplication Ratio |

|----------------|-------------------------|--------------------------|

| Period Value = | Input Clock Prescaler × | PLL Divide by 2          |

|                | Desired Frequency       |                          |

Since the GP Timers start counting from zero, to calculate the value that should be loaded into the period register, 1 should be subtracted from the calculated value obtained to input into register T1PR. Similarly, to find the correct value in the compare register, the duty cycle should be multiplied by the period value and 1 should also be subtracted.

Compare register value calculation: Compare Value = Period Value × Duty Cycle

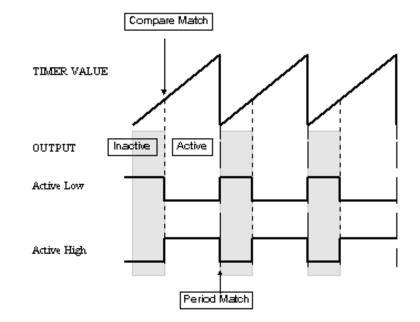

To determine whether the polarity of the Compare output should be active high or active low, one must understand the difference between the two modes (See Figure 1). If the pin is set to the active low state, during the inactive state, the output will be high and low when active. Setting the output to active high will produce opposite results.

As a result, when the output pin is inactive at the beginning of the period, if set to the active low state, the output will be high, and if it is set to the active high state, the output will be low. When a compare event occurs, the state will switch to active resulting in a low output for the active low state and a high output for the active high state. Depending on the state chosen, the pulse of the PWM signal in the active low state will be at the beginning of the period, and in the active high state, it will be at the end of the period. The point being, if a program is designed with the output pin in the active high state, the same program will have a duty cycle of 80%.

Figure 1. Active High and Active Low Polarity

ţi,

Once the proper registers have been set to create the PWM signal, the program can be ended (i.e., with an unconditional branch) and the PWM signal will continue to be output until the program stops the signal through software or the program is halted by the user.

; File Name: pwm0.asm ; Originator: Digital Control Systems Apps group - Houston ; Target System: 'C24x Evaluation Board Pulse Width Modulator - Sets up the registers ; Description: for an asymmetric PWM output. The output is a ; square wave with a fixed 20% duty cycle. ; ; PWM Period is 0.05ms => 20kHz ; ; Last Updated: 20 June 1997 .include f240regs.h ; Vector address declarations .sect ".vectors" RSVECT В START ; Reset Vector INT1 B PHANTOM ; Interrupt Level 1 INT2 B PHANTOM ; Interrupt Level 2 PHANTOM ; Interrupt Level 3 INT3 В PHANTOM ; Interrupt Level 4 INT4 В В INT5 PHANTOM ; Interrupt Level 5 В PHANTOM ; Interrupt Level 6 INT6 В PHANTOM ; Reserved RESERVED PHANTOM ; User S/W Interrupt В SW INT8 SW\_INT9 B PHANTOM ; User S/W Interrupt B PHANTOM ; User S/W Interrupt SW INT10 B PHANTOM ; User S/W Interrupt SW\_INT11 PHANTOM ; User S/W Interrupt SW INT12 В SW\_INT13 В PHANTOM ; User S/W Interrupt SW INT14 В PHANTOM ; User S/W Interrupt В PHANTOM ; User S/W Interrupt SW\_INT15 В PHANTOM ; User S/W Interrupt SW\_INT16 В TRAP PHANTOM ; Trap vector NMINT В PHANTOM ; Non-maskable Interrupt В PHANTOM ; Emulator Trap EMU\_TRAP В PHANTOM ; User S/W Interrupt SW\_INT20 В PHANTOM ; User S/W Interrupt SW\_INT21 B PHANTOM ; User S/W Interrupt SW INT22 SW INT23 B PHANTOM ; User S/W Interrupt ; MAIN CODE - starts here .text NOP START: SETC INTM ;Disable interrupts

Creating a Pulse Width Modulated Signal with a Fixed Duty Cycle Using the TMS320F240 EVM13

|                                                                                                                                                                                                                                                                                  | ]       | LACC                                   | #0000h,IMR<br>IFR<br>IFR                            | ;Mask all core interrupts<br>;Read Interrupt flags<br>;Clear all interrupt flags   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                  | (       |                                        | SXM<br>OVM<br>CNF                                   | ;Clear Sign Extension Mode<br>;Reset Overflow Mode<br>;Config Block B0 to Data mem |

| ;; Set up P                                                                                                                                                                                                                                                                      |         |                                        |                                                     |                                                                                    |

| ;                                                                                                                                                                                                                                                                                | ]       | LDP                                    | #00E0h                                              |                                                                                    |

| ;The following line is necessary if a previous program set the PLL<br>;to a different setting than the settings which the application;<br>;uses. By disabling the PLL, the CKCR1 register can be modified so<br>;that the PLL can run at the new settings when it is re-enabled. |         |                                        |                                                     |                                                                                    |

| SPLK<br>Disable,SY                                                                                                                                                                                                                                                               |         |                                        |                                                     | CKCR0 ;CLKMD=PLL                                                                   |

| ;<br>;CLKIN(OSC                                                                                                                                                                                                                                                                  |         |                                        | 5432109876543<br>#0000000010111<br>LK=20MHz         |                                                                                    |

| ;Bits 7-4<br>;<br>;Bit 3<br>;                                                                                                                                                                                                                                                    | (1011)( | CKINF<br>Freq<br>PLLD<br>Divi<br>PLLFB | uency = 10MHz<br>IV(2) - PLL div<br>de PLL input by | 7 2<br>PLL multiplication ratio                                                    |

| ;                                                                                                                                                                                                                                                                                | Š       | SPLK                                   | 5432109876543<br>#0000000011000                     | 210<br>)011b,CKCR0 ;CLKMD=PLL ENable,<br>SYSCLK=CPUCLK/2                           |

| ;CKCR0 - C<br>;Bits 7-6<br>;<br>;                                                                                                                                                                                                                                                |         | CLKM<br>Modu                           |                                                     | - Operational mode of Clock<br>; Run on CLKIN on exiting low                       |

| ;Bits 5-4<br>;Bits 3-2<br>;                                                                                                                                                                                                                                                      | . ,     | PLLO                                   | CK(1),PLLOCK(0<br>M(1),PLLPM(0)                     | ) - PLL Status. READ ONLY<br>- Low Power Mode                                      |

| ;Bit 1<br>;                                                                                                                                                                                                                                                                      | (0)     | ACLK<br>ACLK                           | ENA - 1MHz ACLI<br>Enabled                          |                                                                                    |

| ;Bit 0<br>;                                                                                                                                                                                                                                                                      | (1)     |                                        | S - System Cloo<br>sclk)=f(cpuclk                   | ck Prescale Value<br>)/2                                                           |

Ų

; 5432109876543210 SPLK #0100000011000000b,SYSCR ;CLKOUT=CPUCLK ;SYSCR - System Control Register ;Bit 15-14 (01) RESET1, RESET0 - Software Reset Bits No Action ;Bits 13-8 (000000) Reserved ;Bit 7-6 (11) CLKSRC1,CLKSRC0 - CLKOUT-Pin Source Select CPUCLK: CPU clock output mode ; ;Bit 5-0 (000000) Reserved SPLK #006Fh, WDCR ; Disable WD if VCCP=5V (JP5 in pos. 2-3) ;Reset Watchdog KICK DOG ;-----; Set up Digital I/O Port ; -----LDP #225 ;DP=225, Data Page to Configure OCRA ; 5432109876543210 SPLK #001110000000000b,OCRA ;OCRA - Output Control Register A ;Bit 15 (0) CRA.15 - IOPB7 ;Bit 14 (0) CRA.14 - IOPB6 ;Bit 13 (1) CRA.13 - T3PWM/T3CMP / Bit 12 (1) CRA.12 - T2PWM/T2CMP

/ Bit 11 (1) CRA.11 - T1PWM/T1CMP

/ Bit 10 (0) CRA.10 - IOPB2

/ Bit 9 (0) CRA.9 - IOPB1

/ Bit 8 (0) CRA.8 - IOPB0 ;Bits 7-4 (0000)Reserved ;Bit 3 (0) CRA.3 - IOPA3 (0) CRA.2 - IOPA2 ;Bit 2 ;Bit 1 (0) CRA.1 - IOPA1 ;Bit 0 (0) CRA.0 - IOPA0 ;- Event Manager Module Reset ;\* ;-This section resets all of the Event Manager Module Registers. ;\*This is necessary for silicon revsion 1.1; however, for ;-silicon revisions 2.0 and later, this is not necessary ;\* ; -LDP #232 ;DP=232 Data Page for the Event ;Manager SPLK #0000h,GPTCON ;Clear General Purpose Timer Control

Creating a Pulse Width Modulated Signal with a Fixed Duty Cycle Using the TMS320F240 EVM15

| SPLK<br>SPLK<br>SPLK                                                                                                                          | #0000h,T2CON                                                                                                                                                                                                                                     | ;Clear GP Timer 1 Control<br>;Clear GP Timer 2 Control<br>;Clear GP Timer 3 Control                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPLK                                                                                                                                          | #0000h,COMCON                                                                                                                                                                                                                                    | ;Clear Compare Control                                                                                                                                                                                                                                                                                                                                         |

| SPLK                                                                                                                                          | #0000h,ACTR<br>#0000h,SACTR                                                                                                                                                                                                                      | <pre>;Clear Full Compare Action Control ;Register ;Clear Simple Compare Action Control</pre>                                                                                                                                                                                                                                                                   |

| SPLK                                                                                                                                          |                                                                                                                                                                                                                                                  | ;Register<br>;Clear Dead-Band Timer Control<br>;Register                                                                                                                                                                                                                                                                                                       |

| SPLK                                                                                                                                          | #0000h,CAPCON                                                                                                                                                                                                                                    | ;Clear Capture Control                                                                                                                                                                                                                                                                                                                                         |

| SPLK<br>SPLK<br>SPLK                                                                                                                          | #0FFFFh,EVIFRB                                                                                                                                                                                                                                   | ;Clear Interrupt Flag Register A<br>;Clear Interrupt Flag Register B<br>;Clear Interrupt Flag Register C                                                                                                                                                                                                                                                       |

| SPLK<br>SPLK<br>SPLK                                                                                                                          | #0000h,EVIMRB                                                                                                                                                                                                                                    | ;Clear Event Manager Mask Register A<br>;Clear Event Manager Mask Register B<br>;Clear Event Manager Mask Register C                                                                                                                                                                                                                                           |

| <pre>;*_*_*_*_*_*_*_*_*_*_*_*_*_*_*_*_*_*_*_</pre>                                                                                            |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                |

| ;                                                                                                                                             |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                |

| ;<br>; Set up Event M<br>;<br>T1COMPARE                                                                                                       | lanager Module<br>                                                                                                                                                                                                                               | <br>;T1Compare 20% of T1Period<br>;T1Period value = 20kHz signal                                                                                                                                                                                                                                                                                               |

| ;<br>; Set up Event M<br>;<br>T1COMPARE                                                                                                       | lanager Module<br>                                                                                                                                                                                                                               | <pre>;TlCompare 20% of TlPeriod ;TlPeriod value = 20kHz signal</pre>                                                                                                                                                                                                                                                                                           |

| ;<br>; Set up Event M<br>;<br>T1COMPARE                                                                                                       | LDP #232                                                                                                                                                                                                                                         | <pre>;TlCompare 20% of TlPeriod ;TlPeriod value = 20kHz signal ;DP=232, Data Page for Event</pre>                                                                                                                                                                                                                                                              |

| ;<br>; Set up Event M<br>;<br>T1COMPARE                                                                                                       | LDP #232                                                                                                                                                                                                                                         | ;T1Compare 20% of T1Period<br>;T1Period value = 20kHz signal<br>;DP=232, Data Page for Event<br>;Manager Addresses<br>RE,T1CMPR ;Compare value for<br>; 20% duty cycle<br>543210                                                                                                                                                                               |

| ; Set up Event M<br>;<br>T1COMPARE<br>T1PERIOD<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | anager Module<br>.set 200<br>.set 1000<br>LDP #232<br>SPLK #T1COMPAN<br>2109876<br>SPLK #00000010<br>mer Control Regi<br>T3STAT - GP Ti<br>T2STAT - GP Ti                                                                                        | <pre> ;TlCompare 20% of TlPeriod ;TlPeriod value = 20kHz signal ;DP=232, Data Page for Event ;Manager Addresses RE,TlCMPR ;Compare value for ; 20% duty cycle 543210 010101b,GPTCON ster mer 3 Status. READ ONLY mer 2 Status. READ ONLY</pre>                                                                                                                 |

| ; Set up Event M<br>;<br>T1COMPARE<br>T1PERIOD<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | anager Module<br>.set 200<br>.set 1000<br>LDP #232<br>SPLK #T1COMPAN<br>2109876<br>SPLK #0000001<br>Mer Control Regi<br>T3STAT - GP Ti<br>T2STAT - GP Ti<br>T1STAT - GP Ti<br>T3TOADC - ADC<br>No event start                                    | <pre> ;T1Compare 20% of T1Period ;T1Period value = 20kHz signal ;DP=232, Data Page for Event ;Manager Addresses RE,T1CMPR ;Compare value for ; 20% duty cycle 543210 010101b,GPTCON ster mer 3 Status. READ ONLY mer 1 Status. READ ONLY mer 1 Status. READ ONLY start by event of GP Timer 3 s ADC</pre>                                                      |

| ; Set up Event M<br>;<br>T1COMPARE<br>T1PERIOD<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | Anager Module<br>.set 200<br>.set 1000<br>LDP #232<br>SPLK #T1COMPAN<br>2109876<br>SPLK #0000001<br>Mer Control Regi<br>T3STAT - GP Ti<br>T2STAT - GP Ti<br>T1STAT - GP Ti<br>T3TOADC - ADC<br>No event start<br>T2TOADC - ADC<br>No event start | <pre> ;TlCompare 20% of TlPeriod ;TlPeriod value = 20kHz signal ;DP=232, Data Page for Event ;Manager Addresses RE,TlCMPR ;Compare value for ; 20% duty cycle 543210 010101b,GPTCON ster mer 3 Status. READ ONLY mer 2 Status. READ ONLY mer 1 Status. READ ONLY mer 1 Status. READ ONLY start by event of GP Timer 3 s ADC start by event of GP Timer 2</pre> |

Ų

| i                |         | Enable all three GP timer compare outputs                                                                                                                                                                     |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ;Bits 5-4<br>;   | (01)    | T3PIN - Polarity of GP Timer 3 compare output<br>Active Low                                                                                                                                                   |

|                  | (01)    | T2PIN - Polarity of GP Timer 2 compare output<br>Active Low                                                                                                                                                   |

|                  | (01)    | T1PIN - Polarity of GP Timer 1 compare output<br>Active Low                                                                                                                                                   |

|                  |         | <pre>SPLK #T1PERIOD,T1PR ;Period value for 20kHz signal<br/>SPLK #0000h,T1CNT ;Clear GP Timer 1 Counter<br/>SPLK #0000h,T2CNT ;Clear GP Timer 2 Counter<br/>SPLK #0000h,T3CNT ;Clera GP Timer 3 Counter</pre> |

| ;                |         | 5432109876543210<br>SPLK #000100000000000b,T1CON                                                                                                                                                              |

| ;T1CON - GF      | Time    | r 1 Control Register                                                                                                                                                                                          |

|                  |         | FREE,SOFT - Emulation Control Bits                                                                                                                                                                            |

| ;                |         | Stop immediately on emulation suspend                                                                                                                                                                         |

| ;Bits 13-11<br>; | (010)   | TMODE2-TMODE0 - Count Mode Selection<br>Continuous-Up Count Mode                                                                                                                                              |

| ;Bits 10-8<br>;  | (000)   | TPS2-TPS0 - Input Clock Prescaler<br>Divide by 1                                                                                                                                                              |

|                  | (0)     | -                                                                                                                                                                                                             |

|                  | (0)     | TENABLE - Timer Enable                                                                                                                                                                                        |

| ;                |         | Disable timer operations                                                                                                                                                                                      |

| ;Bits 5-4        | (00)    |                                                                                                                                                                                                               |

| ;<br>;Bits 3-2   | (00)    | Internal Clock Source<br>TCLD1,TCLD0 - Timer Compare Register Reload                                                                                                                                          |

| ;                |         | Condition When counter is 0                                                                                                                                                                                   |

| ;Bit 1           | (1)     | TECMPR - Timer compare enable                                                                                                                                                                                 |

| ;<br>;Bit 0      | (0)     | Enable timer compare operation<br>Reserved                                                                                                                                                                    |

| /BIC U           | (0)     | Reserved                                                                                                                                                                                                      |

| ;                |         | 5432109876543210                                                                                                                                                                                              |

|                  |         | SPLK #000000000000000b,T2CON ;GP Timer 2-Not Used                                                                                                                                                             |

|                  | ) Timo: | r 2 Control Register                                                                                                                                                                                          |

|                  |         | FREE,SOFT - Emulation Control Bits                                                                                                                                                                            |

| ;                |         | Stop immediately on emulation suspend                                                                                                                                                                         |

| ;Bits 13-11      | (000)   | TMODE2-TMODE0 - Count Mode Selection                                                                                                                                                                          |

| ;<br>;Bits 10-8  | (000)   | Stop/Hold<br>TPS2-TPS0 - Input Clock Prescaler                                                                                                                                                                |

| ; BILS 10-0      | (000)   | Divide by 1                                                                                                                                                                                                   |

| ;<br>Bit 7       | (0)     | TSWT1 - GP Timer 1 timer enable bit                                                                                                                                                                           |

| ;                |         | Use own TENABLE bit                                                                                                                                                                                           |

| ;Bit 6           | (0)     | TENABLE - Timer Enable                                                                                                                                                                                        |

| ;<br>; Dita E 4  | (00)    | Disable timer operations                                                                                                                                                                                      |

| ;Bits 5-4<br>;   | (00)    | TCLKS1,TCLKS0 - Clock Source Select<br>Internal Clock Source                                                                                                                                                  |

| ;Bits 3-2        | (00)    | TCLD1,TCLD0 - Timer Compare Register Reload                                                                                                                                                                   |

|                  |         |                                                                                                                                                                                                               |

Ų

| ;<br>;Bit 1<br>;      | (0)    | Condition When counter is 0<br>TECMPR - Timer compare enable<br>Disable timer compare operation |

|-----------------------|--------|-------------------------------------------------------------------------------------------------|

| ;Bit 0<br>;           | (0)    | SELT1PR - Period Register select<br>Use own period register                                     |

| ;                     |        | 5432109876543210<br>SPLK #000000000000000b,T3CON ;GP Timer 3-Not Used                           |

| ;T3CON - G            | P Time | r 3 Control Register                                                                            |

| ;Bits 15-1            |        | FREE, SOFT - Emulation Control Bits                                                             |

| ;<br>;Bits 13-1;<br>; | 1(000) | Stop immediately on emulation suspend<br>TMODE2-TMODE0 - Count Mode Selection<br>Stop/Hold      |

| ;Bits 10-8            | (000)  | TPS2-TPS0 - Input Clock Prescaler<br>Divide by 1                                                |

| ;Bit 7<br>;           | (0)    | TSWT1 - GP Timer 1 timer enable bit<br>Use own TENABLE bit                                      |

| ;Bit 6                | (0)    |                                                                                                 |

| ;                     | ( )    | Disable timer operations                                                                        |

| ;Bits 5-4             | (00)   | TCLKS1,TCLKS0 - Clock Source Select<br>Internal Clock Source                                    |

| ,<br>;Bits 3-2<br>;   | (00)   |                                                                                                 |

| ;Bit 1<br>:           | (0)    | TECMPR - Timer compare enable<br>Disable timer compare operation                                |

| ;<br>;Bit 0<br>;      | (0)    |                                                                                                 |

| ,                     |        | obe own period regibter                                                                         |

| SBIT1                 |        | T1CON,B6_MSK ;Sets Bit 6 of T1CON                                                               |

| ;T1CON - G            | P Time | r 1 Control Register                                                                            |

| ;Bit 6                |        |                                                                                                 |

| i                     |        | Enable Timer Operations                                                                         |

| END                   |        | B END                                                                                           |

| ;=========            | ====== |                                                                                                 |

| ; I S R - PHANTOM     |        |                                                                                                 |

| ; Descript;           | ion:   | Dummy ISR, used to trap spurious interrupts.                                                    |

| ; Modifies            | :      | Nothing                                                                                         |

|                       |        | 16 June 95                                                                                      |

| PHANTOM               |        | KICK_DOG ;Resets WD counter<br>B PHANTOM                                                        |

÷