# How to Begin Development With the TMS320C6205 DSP

Zoran Nikolic

C6000 Applications Team

#### ABSTRACT

This document highlights the similarities and differences between the TMS320C6205 digital signal processor (DSP) and other TMS320C6000<sup>™</sup> devices. The similarities allow Tools designed for other C6000<sup>™</sup> DSPs to be used to develop software for the C6205. A listing of these tools and documents that aid in development is presented.

#### Contents

| 1 | How to Begin Development With the TMS320C6205 DSP | . 1 |

|---|---------------------------------------------------|-----|

| 2 | TMS320C6000 Compatibility                         | . 2 |

|   | 2.1 Similarities Between C6205 and C6201B DSPs    |     |

|   | 2.2 Differences Between the C6205 and C6201B DSPs | . 4 |

| 3 | Begin Writing Code for the C6205                  | . 5 |

|   | 3.1 C6000 Tools Support                           | . 5 |

| 4 | References                                        | . 6 |

#### **List of Figures**

| Figure 1. | TMS320C6200 Fixed-Point Roadmap | 2 |

|-----------|---------------------------------|---|

| Figure 2. | TMS320C6205 DSP Block Diagram   | 3 |

## 1 How to Begin Development With the TMS320C6205 DSP

The TMS320C6205 is one of the devices in the TMS320C6000<sup>™</sup> DSP platform of high-performance digital signal processors (DSPs). The C6205 is a version of the original C6000<sup>™</sup> DSP device, the C6201B, with the new peripheral interface to the PCI bus in addition to other enhancements. The C6205 is capable of achieving 1600 MIPS (million instructions per second) at 200 MHz.

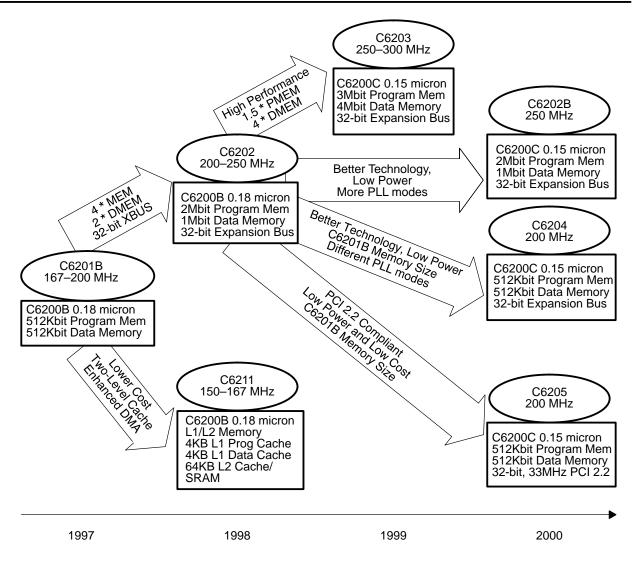

Introduced in February 1997, the C6000<sup>™</sup> DSP platform is based on TI's VelociTI<sup>™</sup> architecture, an advanced very long instruction word (VLIW) architecture for DSPs. Figure 1 shows the road-map for the fixed–point generation of the C6000<sup>™</sup> DSP platform.

All trademarks are the property of their respective owners.

TMS320C6000, C6000, and VelociTI are trademarks of Texas Instruments.

Figure 1. TMS320C6200 Fixed-Point Roadmap

## 2 TMS320C6000 Compatibility

All C6000<sup>™</sup> DSP devices are code-compatible with one another, with the exception that there are some floating–point instructions that are only valid on the floating-point (TMS320C67x<sup>™</sup>) members. All of the TMS320C62x<sup>™</sup> fixed-point devices are based on the same CPU core designed to achieve high performance through increased instruction-level parallelism. Surpassing the throughput of traditional superscalar designs, VelociTI provides eight execution units, including two multipliers and six arithmetic logic units (ALUs). These units operate in parallel and can perform up to eight instructions during a single clock cycle-up to 1600 MIPS at 200 MHz.

TMS320C67x and TMS320C62X are trademarks of Texas Instruments.

VelociTI's advanced features include instruction packing, conditional branching, variable-width instructions, and prefetched branching, all of which eliminate problems that were previously associated with VLIW implementations. The architecture is highly deterministic, with few restrictions on how or when instructions are fetched, executed, or stored. This architectural flexibility is key to the breakthrough efficiency levels of the C6000<sup>™</sup> DSP compiler.

This common architecture allows designers to begin development with existing C6000<sup>™</sup> DSP software tools for those devices currently in development. This also allows for migration from one C6000<sup>™</sup> DSP processor to another, as design requirements require.

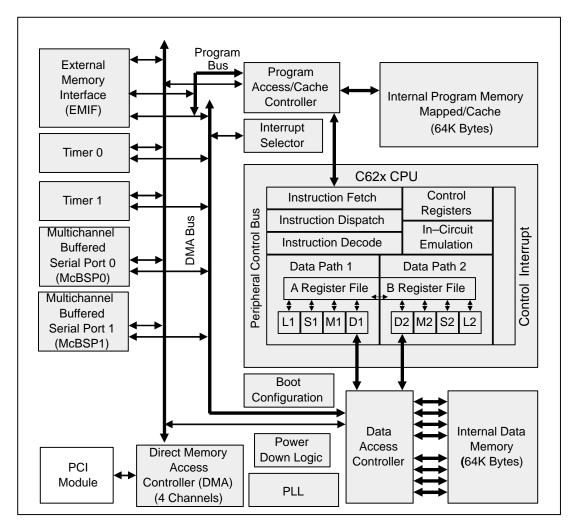

In addition to the CPU, many of the on-chip peripherals are common between C6000<sup>™</sup> DSP devices. Figure 2 shows a block diagram of the C6205. The blocks in gray are shared between the C6201 and C6205. It is important to note that the PCI module is the only truly different aspect of the C6205.

Figure 2. TMS320C6205 DSP Block Diagram

### 2.1 Similarities Between C6205 and C6201B DSPs

The C6205 is highly-compatible with the first C6000<sup>™</sup> DSP device, the C6201 and C6201B. The following device components are identical between the devices:

- **CPU:** The CPU of the C6205 is identical to that of the C6201B, which means that code written for the C6201 will run unmodified on the C6205.

- **Multichannel Buffered Serial Ports (McBSPs):** The McBSPs are unchanged on the C6205.

- **32-bit timers:** Two timers are on the C6205.

- Interrupt selection: There are 16 interrupt sources that may be used to interrupt the CPU or send an event to the DMA.

- Internal memory spaces: Both have 64K bytes each of program and data memory.

### 2.2 Differences Between the C6205 and C6201B DSPs

Several enhancements have been made to allow the C6205 greater performance capability. These include:

- External Memory Interface (EMIF): The EMIF has been modified slightly to reduce the pin count of the C6205. Synchronous DRAM (SDRAM) and Sync-Burst SRAM (SBSRAM) share control signals on the EMIF bus. The two are mutually exclusive, so only one of the two memory types is permissible in a system.

- Direct Memory Access (DMA) controller: Throughput enhancements have been made to the 4–channel DMA controller. Each channel now has a dedicated 9-deep FIFO; thus, avoiding arbitration for a single FIFO. More information is available in the *How to Begin Development and Migrate Across the TMS320C6202/C6202B/C6203/C6204 DSPs* application report (SPRA603).

- PCI module: The PCI module has been added to the C6205 to replace the Host Port Interface (HPI) of the C6201B. The PCI module functions as a high performance 32-bit Master/Slave PCI Plug-and-Play interface supporting 33 MHz for desktop applications. The PCI interface is compatible with the Revision 2.2 PCI Local Bus Specification. It implements PCI master and slave targets at 33 MHz, with 32-bit data and address. The module contains the requisite configuration registers, parity generation, parity- and system-error detection and reporting (PERR#, SERR#), and power management capabilities.

- **4–Wire EEPROM serial port interface:** TMS320C6205 allows the PCI configuration space registers to be loaded from an external serial EEPROM. The PCI module without DSP intervention performs the autoinitialization process.

- **PLL modes:** The TMS320C6205 PLL has x1, x4, x6, x7, x8, x9, x10, and x11 multiply options configured using CLKMODE0 pin and pullup/down resistor on the EMIF data pins.

- Better process technology: The C6205 uses 15C05 (0.15μm) process technology; thereby, providing lower core voltage and lower power.

- **Boot–Mode configuration:** The TMS320C6205 is configured using pullup/down resistors on the EMIF data bus.

## **3 Begin Writing Code for the C6205**

The identical CPUs in the C6205 and C6201 devices allow for code to be written for the C6205 using existing C6000<sup>™</sup> DSP tools. C6201 code will require no modification to use on the C6205. All peripheral-specific code, with the exception of the PCI module, will also be able to run unchanged on the C6205.

The C6000<sup>™</sup> DSP compiler may be used for all members of the C6000<sup>™</sup> DSP device platform. Fixed–point devices are object-code-compatible, so code written for the C6201 may be used by the C6205.

Code development for the C6205 may begin using the C6000<sup>™</sup> DSP fast simulator. The simulator provides a cycle-accurate account of device performance, assuming that all on-chip memory is used for code and data. The simulator provides a good environment to learn the C6000<sup>™</sup> DSP VLIW architecture.

The standard C6000<sup>™</sup> DSP simulator may be used to incorporate peripheral support. C6205 designs may be worked out in detail on the simulator prior to purchasing actual silicon, with cycle-accurate accounts of peripherals performance.

For a development start in hardware, the C6201 EVM may be used to understand the C6000<sup>™</sup> DSP functionality. With the exception of the PCI module, all of the peripherals on the C6205 are identical to those of the C6201, so the EVM is a good tool to understand how to incorporate the peripherals into a real-time system.

### 3.1 C6000 Tools Support

C6000<sup>™</sup> DSP tools are available now for use in all C6000<sup>™</sup> DSP designs. The C6000<sup>™</sup> DSP development tools available are:

- Code Composer Studio<sup>™</sup> IDE, which includes Code Composer Studio-Compile Tools and Code Composer Studio-Debug Tools

- C6000™ DSP Simulator Software

- C6000 DSP Optimizing C Compiler/Assembler

- XDS510 C6000 C Source Debugger Software

- XDS510 Emulator Hardware with JTAG Emulation Cable

- TMS320C6201 Evaluation Module (EVM)

- TMS320C6201 Multichannel Evaluation Module (McEVM)

- TMS3206211 DSP Starter Kit (DSK)

Code Composer Studio is a trademark of Texas Instruments.

### 4 References

- 1. TMS320C6000 CPU and Instruction Set Reference Guide (SPRU189).

- 2. TMS320C6000 Peripherals Reference Guide (SPRU190).

- 3. TMS320C6000 Technical Brief (SPRU197).

- 4. TMS320C6000 Programmer's Guide (SPRU198).

- 5. TMS320C6201/6701 Evaluation Module Reference Guide (SPRU269).

- 6. TMS320C6x Peripheral Support Library Programmer's Reference (SPRU273).

- 7. TMS320C6x Assembly Language Tools User's Guide (SPRU186).

- 8. TMS320C6x Optimizing C Compiler User's Guide (SPRU187).

- 9. TMS320C6x C Source Debugger User's Guide (SPRU188).

- 10. TMS320C6x C Source Debugger For SPARCstations (SPRU224).

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated