# Connecting TFT LCD Displays to the OMAP5910

Gerald Coley

DSPIEEE Catalog OMAP Applications

#### **ABSTRACT**

The OMAP5910 contains an integrated LCD controller. Utilizing internal memory and dedicated DMA channels, this architecture contains a very efficient LCD control interface. This appnote describes how to connect two different LCD displays to the OMAP5910. While there are many sizes and types of LCD displays in the industry, this appnote focuses on two  $240 \times 320$  color thin film transistor (TFT) displays and how they interface to the OMAP5910 processor.

#### Contents

| 1   | OMAP5   | 5910 LCD Controller        | 2  |

|-----|---------|----------------------------|----|

|     |         | atures                     |    |

|     |         | ock Diagram                |    |

|     |         | D Interface Signals        |    |

| •   |         |                            |    |

| 2   |         | 10 y 320 QVGA Display      |    |

|     |         | splay Description          |    |

|     |         | 1.1 LCD Display            |    |

|     |         | 1.2 Timing Controller      |    |

|     |         | CD Control Signals         |    |

|     |         | MAP5910 Interface          |    |

|     | 2.3     | 3.1 LCD Power              |    |

|     |         | 3.2 Touchscreen            |    |

|     | 2.3     | 3.3 LCD Panel Front Light  | C  |

| 3   | Sharp 2 | 240 y 320 Display          | 0  |

|     |         | splay Description          |    |

|     |         | 1.1 Timing Controller      |    |

|     |         | ontrol Signals             |    |

|     |         | MAP5910 Interface          |    |

|     |         | CD Panel Power             |    |

|     |         | D Frontlight Interface     |    |

|     |         | uchscreen                  |    |

|     |         |                            |    |

| 4   |         | ary                        |    |

| 5   | Refere  | nces 1                     | 6  |

| Ann |         | NEC Display Schematics1    |    |

|     |         |                            |    |

| App | enaix B | Sharp Display Schematics 2 | ĽU |

#### **List of Figures**

| Figure 1 | . OMAP5910 LCD Control Block Diagram |   |

|----------|--------------------------------------|---|

| Figure 2 | . NEC LCD Timing Controller          | 6 |

| Figure 3 | NEC LCD Power                        |   |

| Figure 4 | NEC LCD Power                        |   |

| Figure 5 | NEC LCD LED Frontlight Power         |   |

| Figure 6 | Sharp LCD Timing Controller          |   |

| Figure 7 | Sharp Power Supply                   |   |

| Figure 8 | Sharp LCD Frontlight Controller      |   |

|          |                                      |   |

|          | List of Tables                       |   |

| Table 1. | LCD Interface Signals                |   |

| Table 2. | NEC LCD Specifications               |   |

| Table 3. | LCD Control Signals                  |   |

|          | LCD Control Signals Connections      |   |

| Table 5. | LCD Control Signals Connections      |   |

| Table 6. | Sharp LCD Control Signals            |   |

| Table 7. | Sharp LCD OMA5910 Interface          |   |

### 1 OMAP5910 LCD Controller

This section provides a high-level description of the LCD controller as it pertains to the TFT mode of operation that is being used in this appnote.

#### 1.1 Features

The following features are provided by the OMAP5910 LCD controller:

- Mono passive: 1 BPP, 2 BPP, 4 BPP, and 8 BPP

- 1 BPP: Two palette entries selecting one of 15 grayscale

- 2 BPP: Four palette entries selecting one of 15 grayscale

- 4 BPP: 16 palette entries selecting one of 15 grayscale

- 8 BPP: 256 palette entries selecting one of 15 grayscale

- Color passive: 2 BPP, 4 BPP, 8 BPP, 12, and 16 BPP

- 2 BPP: Four palette entries from 3375 possible colors

- 4 BPP: 16 palette entries from 3375 possible colors

- 8 BPP: 256 palette entries from 3375 possible colors

- 12 BPP: 3375 possible on-screen colors

- 16 BPP: 3375 possible on-screen colors

- Active: 2 BPP, 4BPP, 8BPP, 12 BPP, and 16BPP

- 2 BPP: Four palette entries selecting from 4096 colors

- 4 BPP: 16 palette entries selecting from 4096 colors

- 8 BPP: 256 palette entries selecting from 4096 colors

- 12 BPP: Maximum 64K colors

- 16 BPP: Maximum 64K colors, depending on LCD panel

The TFT is the most commonly used display for hand-held type devices and offers the best overall quality in terms of color depth, clarity, and overall brightness.

The other modes listed above are not covered in this application note.

#### 1.2 Block Diagram

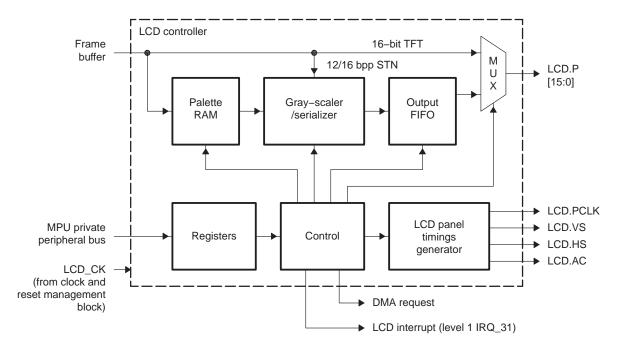

Figure 1 shows the block diagram of the LCD controller on the OMAP5910.

Figure 1. OMAP5910 LCD Control Block Diagram

In the TFT mode, the palette RAM, gray-scalar, and output FIFO are not used. The data is sent directly to the LCD display via the DMA controller from the internal frame buffer memory.

For more detailed information on the internal workings of the OMAP5910 LCD controller, refer to the OMAP5910 datasheet or Technical Reference Manual.

### 1.3 LCD Interface Signals

Table 1 defines the primary pins used by the OMAP5910 to control an external TFT LCD panel.

**Table 1. LCD Interface Signals**

| NAME        | TYPE | DESCRIPTION                                                                                                                                                                                                                          |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD.P[15:0] | OUT  | Pins used to transfer sixteen bit data values at a time to the LCD display.                                                                                                                                                          |

| LCD.PCLK    | OUT  | Pixel clock used by the LCD display to clock the pixel data into the line shift register. The pixel clock transitions continuously and the ac-bias pin is used as an output enable to signal when data is available on the LCD pins. |

| LCD.HS      | OUT  | Line clock used by the TFT displays as the horizontal synchronization signal.                                                                                                                                                        |

| LCD.VS      | OUT  | Frame clock used by the LCD displays to signal the start of a new frame of pixels. Used by TFT displays as the vertical synchronization signal.                                                                                      |

| LCD.AC      | OUT  | Used in TFT mode as the output enable to signal when data is latched from the data pins using the pixel clock.                                                                                                                       |

Additional signals may be required from the OMAP5910. These signals are typically GPIO pins and are used to control such things as:

- LCD power on/off

- Backlight on/off

- Brightness control

Depending on the system level design, several pins are available for these and similar functions. The designer of the board is free to choose if and how these functions are controlled by the OMAP5910 processor.

# 2 NEC 240 × 320 QVGA Display

The first display that we will discuss is the NEC NL2432DR22-11B LCD display. The features of this display include:

- 3.5" (8.9cm) diagonal

- 240 x 320 Resolution (QVGA)

- Reflective

- Portrait Mode

The remainder of this section describes how to interconnect the NEC LCD display and the OMAP5910.

### 2.1 Display Description

The NEC display is actually comprised of two components:

- NL2432DR22-11B LCD display

- The S1L50282F23k100 timing controller

### 2.1.1 LCD Display

Table 2 lists the specifications of the NEC LCD.

**Table 2. NEC LCD Specifications**

| Parameter           | Specification                                | Units  |

|---------------------|----------------------------------------------|--------|

| Screen Diagonal     | 3.52"(8.9)                                   | in(cm) |

| Display Area        | 2.11(53.64)H × 2.82 (71.53)V                 | in(mm) |

| Pixel Format        | 240 × 320                                    |        |

| Colors              | 262,144                                      |        |

| Pixel Configuration | R,G,B Vertical Stripe                        |        |

| Outline Dimensions  | $2.56(65)W \times 3.35(85)H \times 18(4.5)D$ | in(mm) |

# 2.1.2 Timing Controller

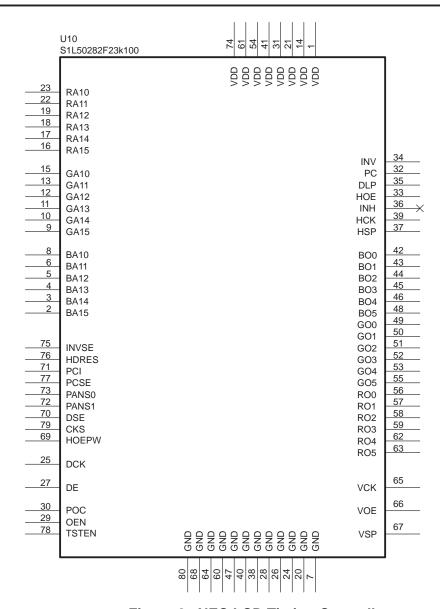

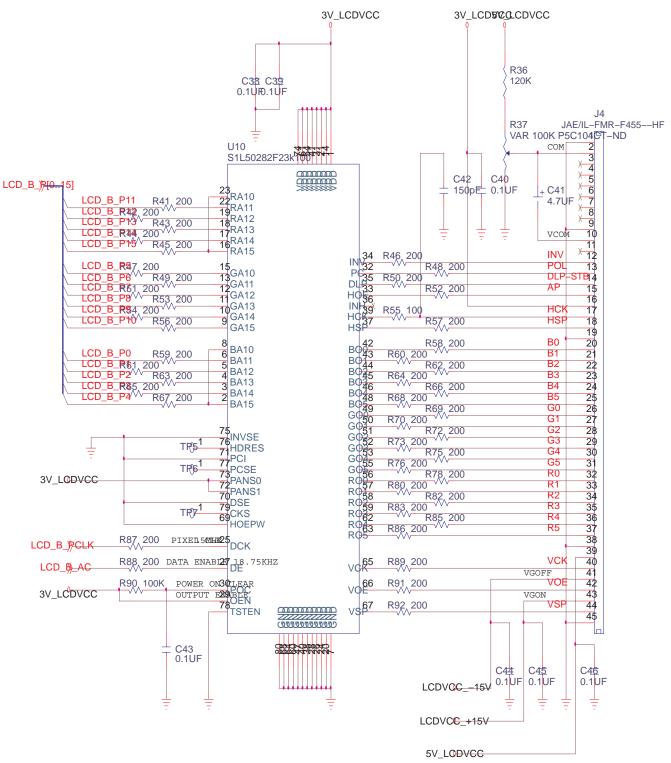

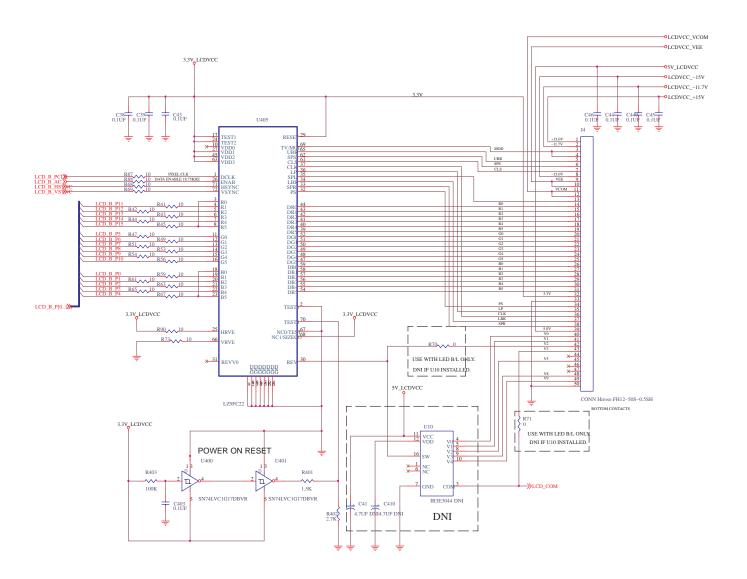

The OMAP5910 actually connects to the S1L50282F23k100 timing controller provided by NEC. The timing controller converts the 16-bit LCD data into the row and column scan data to drive the LCD panel itself. In some cases, the timing controller is integrated with the LCD panel. This is especially true of the larger size displays. However, in this case, the timing controller is separate from the LCD panel. Figure 2 shows the pinout of the timing controller.

Figure 2. NEC LCD Timing Controller

The individual signals are discussed in the following sections.

# 2.2 LCD Control Signals

Table 3 describes the functions of the control signals on the S1L50282F23k100 timing controller that connects to the OMAP5910 LCD interface. The LCD side of the controller is not covered. Refer to the schematic in Appendix A for more details.

Table 3. LCD Control Signals

| Number      | Name  | I/O | Freq      | Description                                         |

|-------------|-------|-----|-----------|-----------------------------------------------------|

| 6,8,5–2     | BI0-5 | 1   | 7.5 MHZ   | Input data for the color blue.                      |

| 15,13–9     | GI0-5 | 1   | 7.5 MHZ   | Input data for the color green.                     |

| 23,22,19–16 | RI0-5 | 1   | 7.5 MHZ   | Input data for the color red.                       |

| 25          | DCK   | I   | 15 MHZ    | Dot clock                                           |

| 27          | DE    | 1   | 18.75 KHZ | Data enable                                         |

| 29          | OEN   | I   | DC        | Gate driver output enable pin                       |

| 30          | POC   | I   | DC        | Power on clear                                      |

| 75          | INVSE | 1   | DC        | Output data reverse (0:off,1:on)                    |

| 76          | HDRES |     | DC        | Data reverse of Internal PC (0:off,1:on)            |

| 71          | PCI   | I   | DC        | Polarity inversion (0:line reverse,1:frame reverse) |

| 77          | PCSE  | 1   | DC        | PC switching (0:internal PC,1:Internal PC reverse)  |

| 73          | PANS0 | 1   | DC        | Switching resolution setup 0                        |

| 72          | PANS1 | 1   | DC        | Switching resolution setup 1                        |

| 70          | DSE   | 1   | DC        | Source driver switching                             |

| 79          | CKS   | I   | DC        | DCK reverse (0:no-reverse, 1:reversed)              |

| 69          | HOEPW | I   | DC        | HOE Pulse width selection.                          |

| 78          | TSTEN | I   | DC        | Test terminal (0:non-reversed'1=reversed.           |

NOTE: Not all of these signals are controlled by the OMAP5910 processor.

#### 2.3 OMAP5910 Interface

This section describes the interconnection of the LCD and timing controller into the OMAP5910 processor. Table 4 maps the LCD controller pins to the OMAP595910. In addition, those signals that do not connect to the OMAP5910, but need to be terminated, are also covered.

**Table 4. LCD Control Signals Connections**

| CONTROLLER SIGNAL | OMAP5910 SIGNAL | CONTROLLER SIGNAL | OMAP5910 SIGNAL |

|-------------------|-----------------|-------------------|-----------------|

| BIO               | LCD.P4          | DCK               | LCD.PCLK        |

| BI1               | LCD.P0          | DE                | LCD.AC          |

| BI2               | LCD.P1          | OEN               | HIGH            |

| BI3               | LCD.P2          | POC               | HIGH via RC     |

| BI4               | LCD.P3          | INVSE             | Ground          |

| BI5               | LCD.P4          | HDRES             | Open            |

**Table 4. LCD Control Signals Connections (Continued)**

| CONTROLLER SIGNAL | OMAP5910 SIGNAL | CONTROLLER SIGNAL | OMAP5910 SIGNAL |

|-------------------|-----------------|-------------------|-----------------|

| GI0               | LCD.P5          | PCI               | Ground          |

| GI1               | LCD.P6          | PCSE              | Open            |

| GI2               | LCD.P7          | PANS0             | High            |

| GI3               | LCD.P8          | PANS1             | High            |

| GI4               | LCD.P9          | DSE               | Ground          |

| GI5               | LCD.P10         | CKS               | Open            |

| RI0               | LCD.P15         | HOEPW             | Ground          |

| RI1               | LCD.P11         | TSTEN             | Ground          |

| RI2               | LCD.P10         |                   |                 |

| RI3               | LCD.P9          |                   |                 |

| RI4               | LCD.P8          |                   |                 |

| RI5               | LCD.P7          |                   |                 |

If you will note, BI0 and BI5 are connected to the same signal from the OMAP processor. This is because the timing controller is designed for 18-bit data, or R6:G6:B6, whereas OMAP5910 supports 16-bit data, or R5:G6:B5. Tying these two signals together, BI0, being the least significant bit, is an easy way of performing the conversion not only for the red component, but for the blue component as well. Green on the other hand, uses all available bits which results in a 5:6:5 configuration for the data.

What is unique about the NEC timing controller is that it does not require the vertical or horizontal sync data; only the pixel clock and the DE signal.

Refer to Appendix A for the complete schematic.

#### 2.3.1 LCD Power

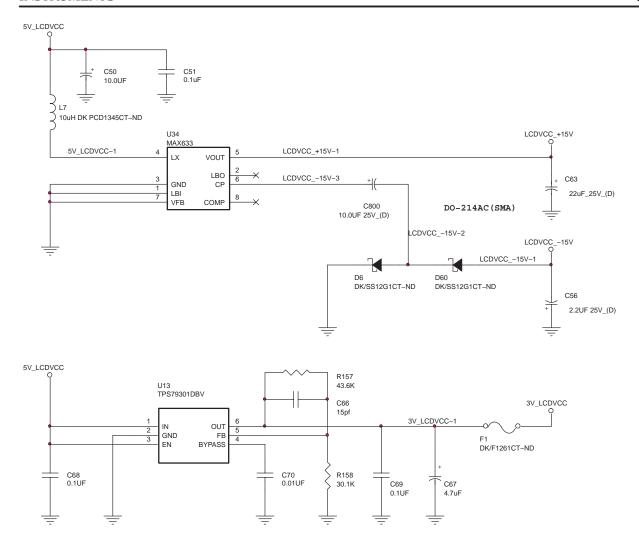

Figure 3 illustratess the design of the LCD power for the NEC display. The power does not necessarily need to be designed in this manner, only the required power must be provided.

Figure 3. NEC LCD Power

The NEC display requires a + 15 V and a - 15 V supply to power the LCD panel. The logic signals in the LCD panel are all at 3 VDC. In this design, all of the power is generated based on a 5 VDC supply. In the event the supply is different, Up converters can be used to create the required voltages.

Pin 2 on the LCD connector (refer to Appendix A) is the contrast control for the LCD panel. A potentiometer is used to adjust the voltage based on a 5v voltage source as needed.

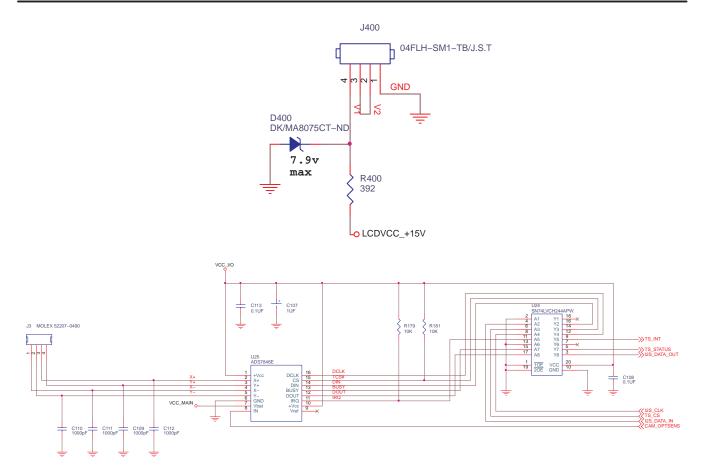

#### 2.3.2 Touchscreen

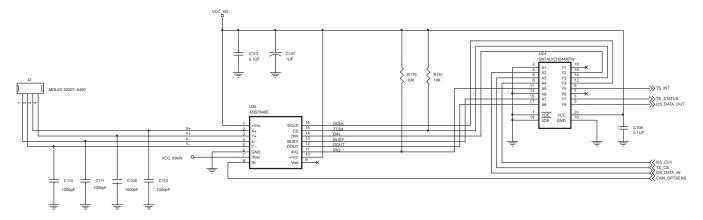

In addition to the LCD panel, the NEC display also has an integrated touch panel over the display. This touch panel provides the ability to connect to a 4-wire touchscreen controller in order to decode the x and Y coordinates and pressure on the display where a stylus is being used. Any 4-wire touchscreen controller decodes this information. A good device is the TI ADS7486 as depicted in Figure 4.

Figure 4. NEC LCD Power

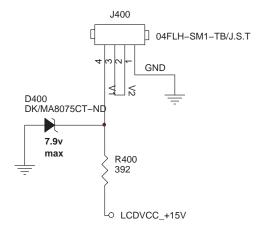

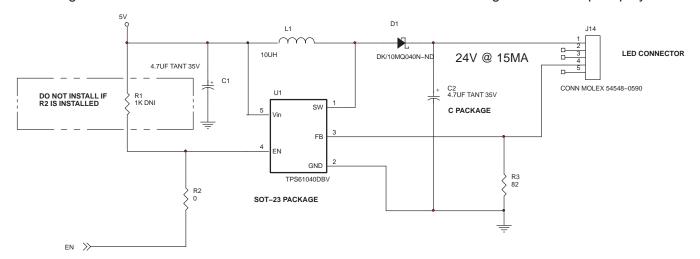

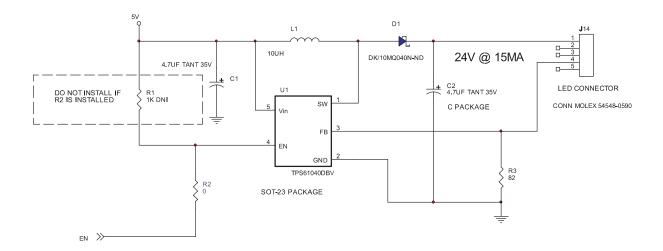

### 2.3.3 LCD Panel Front Light

The NEC display has an LED light source configured as a frontlight and integrated into the NEC panel. Figure 4 shows the frontlight power configuration. The LEDs require 7.9 V. In this case, however, a 15 V supply was used because it already existed for the LCD panel. The designer may choose to generate the required power differently.

Figure 5. NEC LCD LED Frontlight Power

# 3 Sharp 240 × 320 Display

This section describes connecting a Sharp LQ035Q7D color TFT display to the OMAP5910. The schematic for this implementation can be found in Appendix B.

### 3.1 Display Description

The LQ035Q7D LCD display is a color reflective module based on TFT technology. It has an LCD panel, Driver ICs, back light, touch panel, and a back sealed casing.

The specifications of this display are included Table 5.

**Table 5. LCD Control Signals Connections**

| Parameter           | Specification                                | Units  |

|---------------------|----------------------------------------------|--------|

| Screen diagonal     | 3.52"(8.9)                                   | in(cm) |

| Display area        | 2.11(53.64)H×2.82 (71.53) V                  | in(mm) |

| Pixel format        | 240 × 320                                    |        |

| Colors              | 262,144                                      |        |

| Pixel configuration | R,G,B Vertical stripe                        |        |

| Outline dimensions  | $2.56(65)W \times 3.35(85)H \times 18(4.5)D$ | in(mm) |

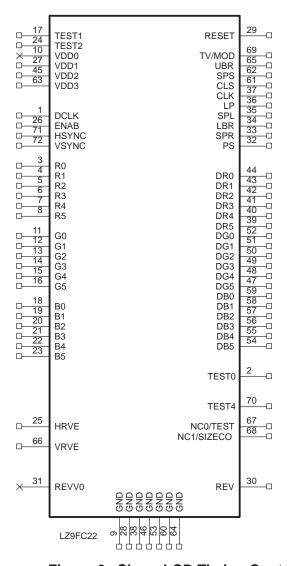

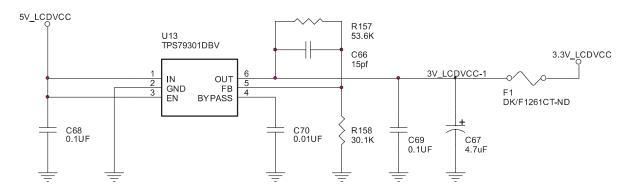

# 3.1.1 Timing Controller

The Sharp LCD also has a separate timing controller chip called the LZ9FC22. This chip converts the 16bi RGB digital data into the row and column driver information to drive the LCD panel. Figure 6 contains the pinout of the LCD timing controller.

Figure 6. Sharp LCD Timing Controller

# 3.2 Control Signals

Table 6 defines the signals on the LCD timing controller that are used to connect to the OMAP5910 processor.

Table 6. Sharp LCD Control Signals

| No.   | Name | I/O | Description                                                                |

|-------|------|-----|----------------------------------------------------------------------------|

| 1     | DCLK | 1   | Input terminal for data clock signal                                       |

| 2     | SETR | 1   | Input terminal for control signal for PS (SIZEC0 = "L" to the application) |

| 3–8   | R0-5 | 1   | Input data for the color red                                               |

| 11–16 | G0-5 | 1   | Input data for the color green                                             |

| 18–23 | B0-5 | I   | Input data for the color blue                                              |

| Table 6. Sharp LCD Control Signals (Continue | Table 6. | Sharp LCD | <b>Control Signals</b> | (Continued |

|----------------------------------------------|----------|-----------|------------------------|------------|

|----------------------------------------------|----------|-----------|------------------------|------------|

| No. | Name   | I/O | Description                                                                                                       |

|-----|--------|-----|-------------------------------------------------------------------------------------------------------------------|

| 25  | HREV   | 1   | Input terminal for setting up right/left reverse scanning H level: Normal L level: Reverse scanning               |

| 26  | ENAB   | I   | Input terminal for signal to settle the horizontal display position                                               |

| 66  | VREV   | 1   | Input terminal for setting up up/down reverse scannning (H:Normal L:Reverse scanning)                             |

| 68  | SIZECO | I   | Input signal for drive condition change SIZEC0 = H : Portrait QVGA(240RGB × 320) L : Landscape QVGA(320RGB × 240) |

| 70  | REM    | I   | Input terminal for reset signal                                                                                   |

| 71  | HS     | I   | Input terminal for horizontal sync. signal                                                                        |

| 72  | VS     | I   | Input terminal for vertical sync. Signal                                                                          |

### 3.3 OMAP5910 Interface

Table 7 defines the mapping between the Sharp LCD timing controller chip and the OMAP5910 processor LCD interface. It also shows the state of the pins that are not controlled directly by the OMAP5910 processor.

Table 7. Sharp LCD OMA5910 Interface

| CONTROLLER SIGNAL | OMAP5910 SIGNAL | CONTROLLER SIGNAL | OMAP5910 SIGNAL |

|-------------------|-----------------|-------------------|-----------------|

| В0                | LCD.P4          | DCK               | LCD.PCLK        |

| B1                | LCD.P0          | DE                | LCD.AC          |

| B2                | LCD.P1          | OEN               | HIGH            |

| В3                | LCD.P2          | POC               | HIGH via RC     |

| B4                | LCD.P3          | INVSE             | Ground          |

| B5                | LCD.P4          | HDRES             | Open            |

| G0                | LCD.P5          | PCI               | Ground          |

| G1                | LCD.P6          | PCSE              | Open            |

| G2                | LCD.P7          | PANS0             | High            |

| G3                | LCD.P8          | PANS1             | High            |

| G4                | LCD.P9          | DSE               | Ground          |

| G5                | LCD.P10         | CKS               | Open            |

| R0                | LCD.P15         | HOEPW             | Ground          |

| CONTROLLER SIGNAL | OMAP5910 SIGNAL | CONTROLLER SIGNAL | OMAP5910 SIGNAL |

|-------------------|-----------------|-------------------|-----------------|

| R1                | LCD.P11         | TSTEN             | Ground          |

| R2                | LCD.P12         |                   |                 |

| R3                | LCD.P13         |                   |                 |

| R4                | LCD.P14         |                   |                 |

| R5                | LCD.P15         |                   |                 |

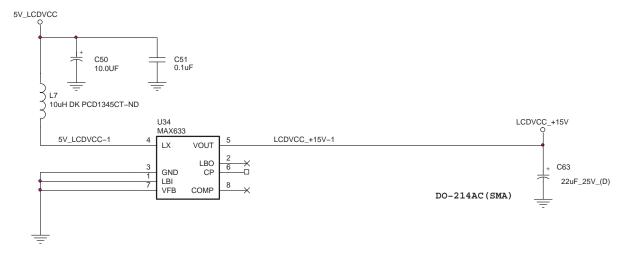

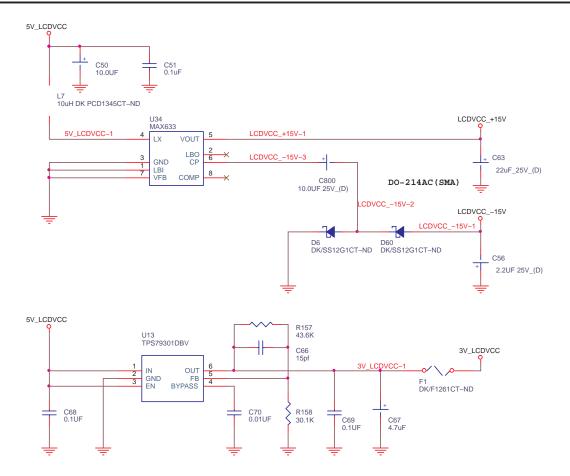

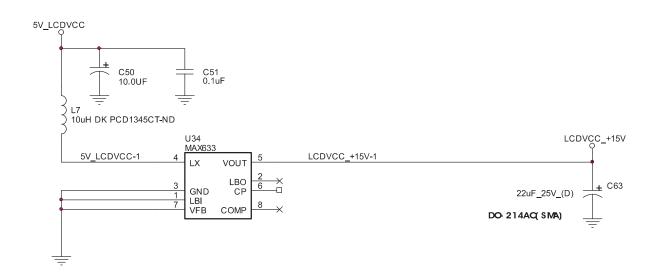

#### 3.4 LCD Panel Power

Figure 7 shows a possible design for the LCD power. The LCD requires a +15 V supply for the LCD panel itself. The logic section of the LCD requires a 3.3 V supply. The designer may choose a different way to supply the power to the LCD.

Figure 7. Sharp Power Supply

Both of these circuits use a 5 V source to create the required voltages. The fuse is not required and is a part of this design, only as a precautionary measure.

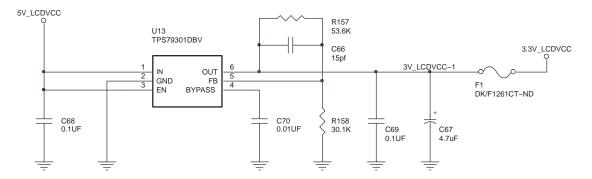

### 3.5 LED Frontlight Interface

Figure 8 is the schematic for the control interface for the LED frontlight of the Sharp display.

Figure 8. Sharp LCD Frontlight Controller

The power for the LED is supplied by U1, a 400-ma boost converter, which converts the 5 V input to the 24 V required by the LEDs. This design actually accepts and inputs a voltage range from 1.8 V to 6 V. So, depending on the individual designs, there is some flexibility here. Refer to the TPS61040 datasheet for more details.

The EN signal can be any GPIO pin on the OMAP5910. When it is Hi, U1 is active. As an option, R1 can be installed if the user wants the LCD to be on all the time.

#### 3.6 Touchscreen

The requirements for the Touchscreen panel on the Sharp LCD are the same as found on the NEC Touchscreen interface.

# 4 Summary

The NEC LCD design was verified and produced in the form of the Innovator Development Kit. The NEC design was used in the production units of the Innovator platform and is still being used.

A printed circuit board design was made, and 10 units were assembled and tested for the Sharp design. It was never produced in large quantities. It was intended as a backup in case the NEC displays could not be obtained.

## 5 References

- 1. OMAP1510 Dual-Core Processor Data Manual (literature number SPRS197)

- 2. OMAP1510 Dual-Core Processor Technical Reference Manual (literature number SPRU602)

- 3. Sharp LCD Panel Datasheet LQ035Q7 B02 (LCY-02024, March 14, 2002)

- 4. NEC LCD Panel Datasheet NL2432DR22-11B (8th Edition, March 4, 2002)

- 5. Sharp Control IC for TFT-LCD Module LZ9FC22 (LCY-00136, June 26, 2001)

- 6. NEC LCD Controller S1L50282F23k100 (DOD-N-0192, 3rd Edition)

# Appendix A NEC Display Schematics

# Appendix B Sharp Display Schematics

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated