## TI Designs

# Multi-Phase Energy Measurement With Isolated Shunt Sensors

#### **TI Designs**

TI Designs provide the foundation that you need including methodology, testing, and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

## **Design Resources**

| TIDA-00601   | Tool Folder Containing Design File |

|--------------|------------------------------------|

| AMC1304M05   | Product Folder                     |

| MSP430F67641 | Product Folder                     |

| SN6501       | Product Folder                     |

| TRS3232      | Product Folder                     |

| ISO7321      | Product Folder                     |

| TPS76333     | Product Folder                     |

| ISO7320      | Product Folder                     |

|              |                                    |

ASK Our E2E Experts

WEBENCH® Calculator Tools

## **Design Features**

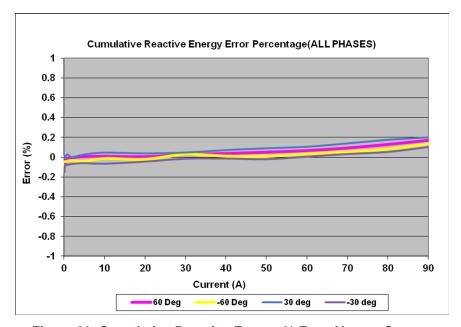

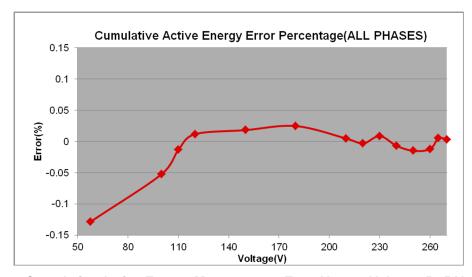

- Class 0.5% Three-Phase Metrology With Galvanically Isolated Shunt Current Sensors

- Isolation Performance of up to 1-kV AC (Working Voltage) and a Voltage of 7 kV (Peak)

- TI Energy Library Firmware Calculates All Energy Measurement Parameters Including Active and Reactive Power and Energy, Root Mean Square (RMS) Current and Voltage, Power Factor, and Line Frequency

- Isolated RS-232 With 3-kV<sub>RMS</sub> Operating Isolation Boundary for Communication to PC Graphical User Interface (GUI)

- Built-in 160-Segment Display for Display of Metrology Parameters

#### **Featured Applications**

- Metering

- Grid Monitoring

- Street Lighting

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

System Description www.ti.com

## 1 System Description

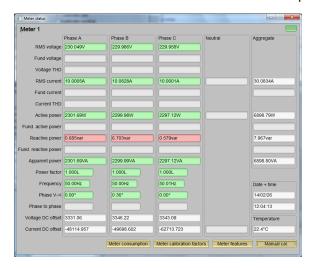

This design implements a class 0.5 three-phase energy measurement system with isolated shunt sensors. The isolation is achieved through the use of isolated delta-sigma modulators that have output circuitry capacitively isolated from input circuitry. An energy measurement system on chip (SoC) takes the different bit-streams from the isolated modulators and uses the SoC's on-board digital filters to produce ADC sample readings. The energy measurement SoC is also used for sensing voltages, calculating metrology parameter values, driving the boards liquid crystal display (LCD), and communication to a PC GUI through the board's isolated RS-232 circuitry.

In regard to metrology, the software energy library supports calculation of various parameters for up to three-phase energy measurement. The key parameters calculated during energy measurements are: RMS current and voltage; active power, reactive power, and energies; power factor; and frequency. These parameters can be viewed either from the calibration GUI or LCD. The design guide has a complete metrology source code provided as a downloadable zip file.

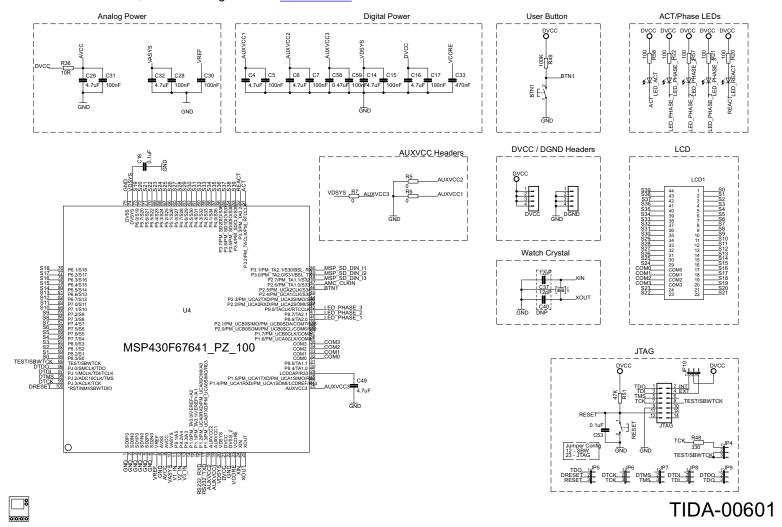

#### 1.1 MSP430F67641

For sensing and calculating the metrology parameters, the MSP430F67641 energy measurement SoC is used. This device is the latest metering SoC that belongs to the MSP430F67xx family of devices. This family of devices belongs to the powerful 16-bit MSP430F6xx platform, which brings in many new features and provides flexibility to support robust poly-phase metrology solutions. These chips are intended for energy measurement applications and have the necessary architecture to support this application.

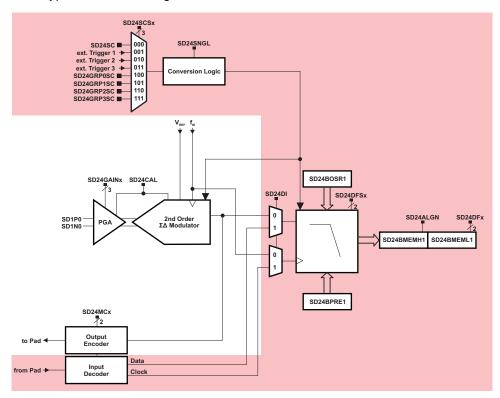

The MSP430F67xx devices have a delta-sigma ADC module (SD24\_B) with ADCs that have the capability to use their own internal modulator or an external modulator. In this design, the external modulator option is used so that the MSP430F67641s digital filter can be used with the isolated delta-sigma modulators that measure the current. Figure 1 shows the block diagram of one of these SD24\_B converters. In Figure 1, the items shaded red are used when the external modulation option is selected and the items that are unshaded are bypassed when using an external modulator.

Figure 1. SD24 B Converter Block Diagram

www.ti.com System Description

To minimize the number of isolated delta-sigma modulators in the design, the modulators are only used for measuring current. As a result of using these modulators, the modulation clock frequency used in the SD24\_B module is too high to be able to use the internal modulator of any extra SD24\_B ADCs that are not already connected to the external modulators. Because of this constraint, the integrated 10-bit SAR ADCs of the MSP430F67641 are used for sensing phase voltages as is done in the following design: TIDM-THREEPHASEMETER-F67641

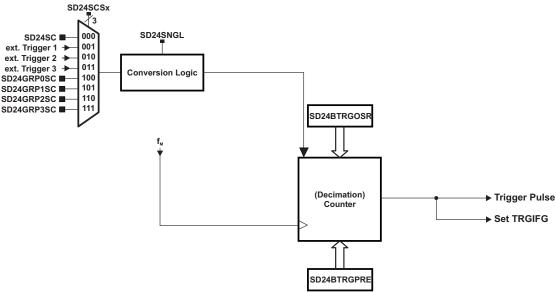

To synchronize the SAR ADCs and the SD24\_B, all of the MSP430F67xx poly-phase devices have a trigger generator that triggers the ADC10 to ensure that the timing between the ADC10 and SD24\_B modules are grouped and synchronized. Figure 2 shows the block diagram of this trigger generator.

#### **Trigger Generator**

Figure 2. SD24\_B Trigger Generator Block Diagram

#### 1.2 AMC1304M05

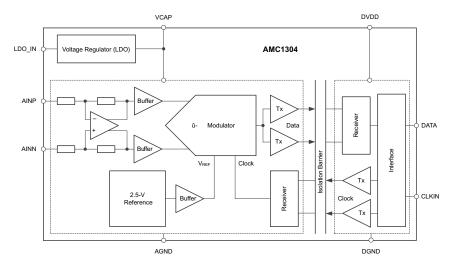

The AMC1304 is used to provide isolated current measurement for the designs shunt current sensors. This isolated current measurement is accomplished by the AMC1304 providing a modulation bit-stream output that is capacitively isolated from the analog signal fed from the shunts to the AMC1304, as Figure 3 shows.

Figure 3. AMC1304 Simplified Block Diagram

System Description www.ti.com

In Figure 3, the shunt current measurement is made across terminals AINP and AINN of the AMC1304. The third terminal of the shunt is then connected to AGND of the AMC1304. To perform measurements, 4 V to18 V must be fed between LDO\_IN and AGND. The AMC1304 then uses its integrated low dropout voltage (LDO) regulator to power the high-side of the chip, which includes the modulator.

To properly power the controller-side, pins DVDD and DGND on the AMC1304 must be connected to DVCC and DGND of the MSP430F67641. In addition, the modulation clock used by the MSP430F67641's SD24\_B digital filters must be connected to CLKIN. This modulation clock must be between 5 MHz to 20 MHz for the AMC1304 to properly work and can either be generated from the clock output of the MSP430 SD24\_B module or from an external clock generator that is fed to both the MSP430F67641 SD24\_B and the AMC1304s. With a proper clock fed into CLKIN, the bit-stream is output from the AMC1304s DATA pin. This DATA pin must be connected to the MSP430F67641 digital bit-stream input.

For selecting an AMC1304 chip, there are four device variations. Two of these variations correspond to a CMOS digital interface option (denoted with an "M" in the part name) and the other two correspond to a low-voltage differential signaling (LVDS) digital interface option (denoted with an "L" in the part name). To properly interface to the MSP430F67641, select the CMOS options. From the CMOS options, there is an option to choose from having a ±50-mV input range (denoted with a "05" in the part name) or a ±250-mV input range (denoted with a "25" in the part name). For e-meter applications, typically shunts with small resistances are used to reduce the power dissipation of the shunt; therefore, to use the full input range of the AMC1304, the ±50-mV input range must be used instead of the ±250-mV input range. As a result, the AMC1304M05 is the AMC1304 device variation that is best suited for this design.

For the AMC1304M05 device variant, if the input voltage value exceeds ±50 mV, there is degradation in the accuracy of readings. Also, to find out the density of ones that result from applying a certain differential input voltage (assuming it is not at the full-scale voltage or beyond this), use the following formula in Equation 1:

$$\%_{HIGH} = 100 \times \left(\frac{V_{input} + 0.625}{1.25}\right) \tag{1}$$

From this formula, a differential input voltage of 0 V corresponds to the associated bit-stream that has a stream of ones and zeros that are high 50% of the time, a differential input voltage of 50 mV has ones and zeros that are high 90% of the time, and a differential input of –50 mV produces a stream of ones and zeros that are high 10% of the time.

#### 1.3 SN6501

Each AMC1304 needs 4 V to 18 V fed into its LDO\_IN pin to power the high-side of the chip. In the design, this voltage can derive from an on-board isolated power supply. This isolated power supply uses DVCC as a voltage input, a transformer, and a transformer driver to provide the necessary isolated voltage that feeds into LDO\_IN. The transformer driver functionality is done by using the SN6501.

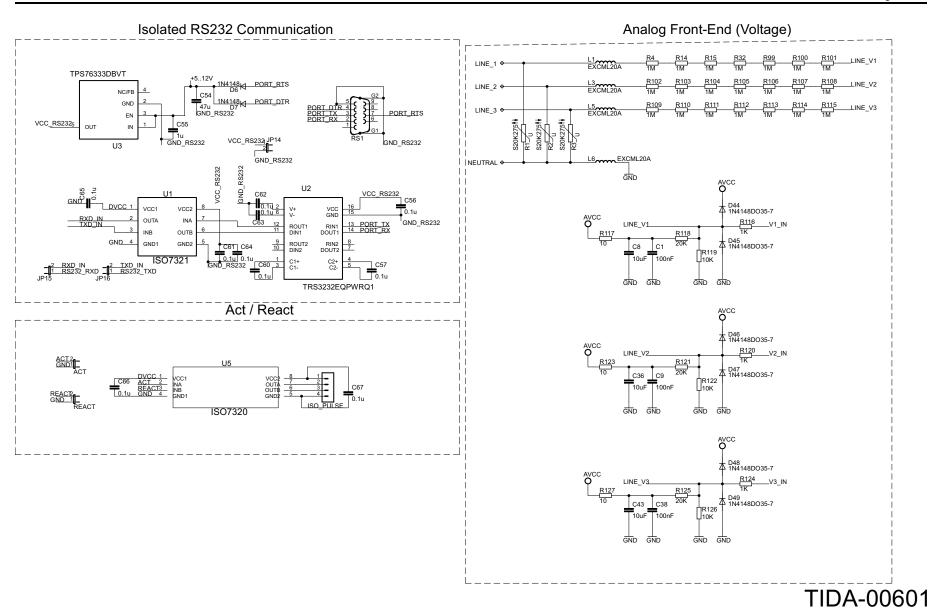

## 1.4 TRS3232

To properly interface with the RS-232 standard, a voltage translation system is required to convert between the 3.3-V domain on the board and from the 12 V on the port itself. To facilitate the translation, the design uses a TRS3232 device. The TRS3232 device is capable of driving the higher voltage signals on the RS-232 port from only the 3.3-V DVCC through a charge pump system.

www.ti.com System Description

#### 1.5 ISO7321

To add isolation to the RS-232 connection to a PC, the isolated RS-232 portion of this design uses capacitive galvanic isolation, which has an inherent lifespan advantage over an opto-isolator. In particular, industrial devices are usually pressed into service for much longer periods of time than consumer electronics; therefore, maintenance of effective isolation over a period of 15 years or longer is important.

The TI ISO7321 device is a simple dual-channel isolator that is capable of operating at 3.3 V or 5 V, enabling a wide range of devices that can connect to the data circuit-terminating equipment (DCE) side of the interface. The ISO7321 device can simply be inserted into a universal asynchoronous receiver/transmitter (UART) signal path, with the appropriate power supplies on each side to enable operation. The ISO7321 device also maintains 3 kV of isolation in order to meet the Underwriters Laboratories (UL) certification levels.

The ISO7321 device is available as the ISO7321C and ISO7321FC variants, where the difference of these variants is in whether the default output is high or low. Although both variants can be used in the design, this design specifically uses the ISO7321C device. In addition, as an alternative, other isolators such as the ISO7421 can also be used because they are pin-to-pin compatible with the ISO7321.

#### 1.6 TPS76333

To power the data terminal equipment (DTE) side of the isolation boundary and the RS-232 charge pump, there are two choices. The interface can either implement an isolated power supply or harvest power from the RS-232 line. Integrating a power supply adds cost and complexity to the system, which is difficult to justify in low-cost sensing applications.

To implement the second option of harvesting power from the RS-232 port itself, this design utilizes the flow control lines that are ignored in most embedded applications. The RS-232 specification (when properly implemented on a host computer or adapter cable), keeps the request to send (RTS) and data terminal ready (DTR) lines high when the port is active. As long as the host has the COM port open, these two lines retain voltage on them. This voltage can vary from 5 V to 12 V, depending on the driver implementation. The 5 V to 12 V is sufficient for the use requirements in this design.

The voltage is put through a diode arrangement to block signals from entering back into the pins. The voltage charges a capacitor to store energy. The capacitor releases this energy when the barrier and charge pump pull more current than what is instantaneously allowed. The TPS76333 is used to bring the line voltage down to a working voltage for the charge pump and isolation device.

#### 1.7 ISO7320

To test the active energy and reactive energy accuracy of a meter, pulses are output at a rate proportional to the amount of energy consumed. A reference meter can then determine the accuracy of a meter by calculating the error based on these pulses and how much energy is provided to the meter. In this design, pulses are output through headers for the cumulative active and reactive energy consumption. The use of the ISO7320 provides an isolated version of these headers for connection to non-isolated equipment. These isolated active and reactive signals can be set to have either a 3.3- or 5-V maximum voltage output by applying the selected maximum voltage output between the isolated sides VCC (ISO\_VCC) and the isolated sides GND (ISO\_GND).

The ISO7320 device is available as the ISO7320C and ISO7320FC variants, where the difference of these variants is in whether the default output is high or low. Although both variants can be used in the design, this design specifically uses the ISO7320C device. In addition, as an alternative, other isolators such as the ISO7420 can also be used because they are pin-to-pin compatible with the ISO7320.

Block Diagram www.ti.com

## 2 Block Diagram

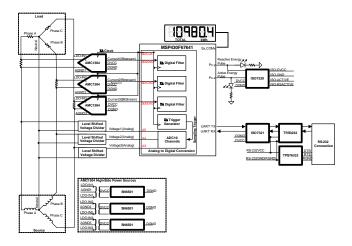

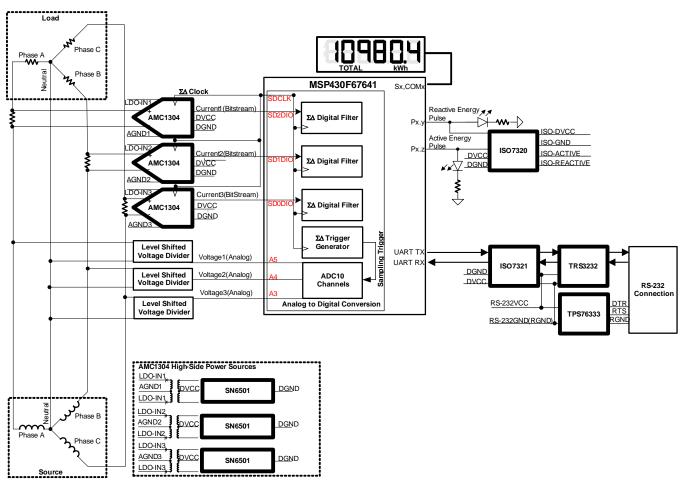

Figure 4. System Block Diagram

Figure 4 depicts a block diagram that shows the high-level interface used for an MSP430F67641-based three-phase energy measurement application with isolated shunts. Figure 4 shows a three-phase, four-wire star connection to the AC mains in this case. In this design, each phase has a shunt current sensor and an AMC1304 device for measuring the voltage across the shunt current sensor. The resistance of the shunt is selected based on the current range required for energy measurements and also the minimization of the maximum power dissipation of the shunt.

For powering the high-side of the AMC1304, each AMC1304 has an external isolated power supply. Please note that because each high-side of the AMC1304s must be referenced from a different line voltage, three isolated power supplies are used. Each implemented power supply provides power to the associated AMC1304 by using DVCC, a transformer, and the SN6501 transformer driver. In contrast, for powering the controller-side of the AMC1304 chips, all AMC1304s should be powered from the same source that powers the MSP430F67641 device.

To perform conversions, all AMC1304 chips must have the same external clock fed into them. In this design, the SD24\_B module outputs its modulation clock, which is generated internally within the MSP430F67641, and feeds the modulation clock to all of the AMC1304 chips. The AMC1304 chips then output their corresponding bit-streams, which are isolated from the high-side part of the chips. Each of these bit-streams is fed into a different MSP430F67641 converter's bit-stream input.

www.ti.com Block Diagram

For the voltage sensor, a combination of a voltage divider and level shifter are used to ensure that the input voltage to the ADC fits within the single-ended voltage range of operation. The range of operation is determined by the chosen reference voltage source of the SAR ADCs. The choice of voltage divider resistors for the voltage channel is selected to ensure the mains voltage is divided down to the normal input ranges that are valid for the SAR ADC, based on the selected reference voltage. To synchronize the SAR ADCs with the SD24\_B module, the trigger generator within the SD24\_B triggers the ADC10 to ensure that the timing between the ADC10 and SD24\_B modules are grouped and synchronized.

Other signals of interest in Figure 4 are the active and reactive energy pulses used for accuracy measurement and calibration. The ISO7320 provides an isolated connection for these pulses for connecting to non-isolated equipment. In addition to isolated pulses, the design supports isolated RS-232 communication through the use of the TPS76333, ISO7321, and TRS3232 devices. For more information on the isolated RS-232 portion of the design, consult from the following resource: TIDA-00163.

## 2.1 Highlighted Products

#### 2.1.1 MSP430F67641

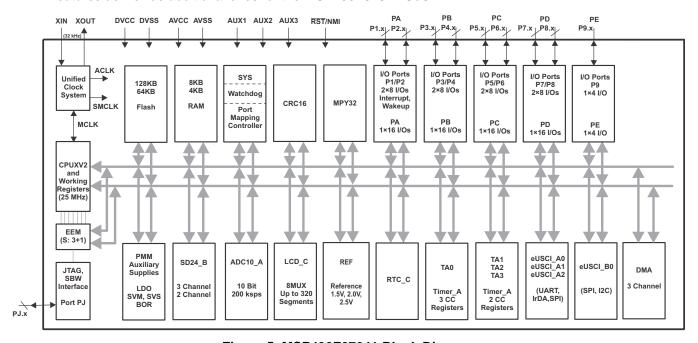

The MSP430F67641 poly-phase metering SoC is a powerful, highly-integrated energy measurement solution that offers accuracy and low system cost with few external components. The F67641 uses the low-power MSP430 CPU with a 32-bit multiplier to perform all energy calculations, metering applications such as tariff rate management, and communications with automatic meter reading (AMR) or advanced metering infrastructure (AMI) modules. The chip has an LCD controller with support for up to 320 segments, a real-time Clock (RTC) module with integrated offset and temperature calibration, and a separate auxiliary supply to power the RTC independently from the rest of the chip. Figure 5 shows these features as well as additional ones for the MSP430F67641 SoC.

Figure 5. MSP430F67641 Block Diagram

#### 2.1.2 AMC1304M05

The AMC1304 devices are precision, delta-sigma ( $\Delta\Sigma$ ) modulators with the output separated from the input circuitry by a capacitive isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced isolation of up to 7000 V<sub>PEAK</sub> according to the UL 1577 standard, VDE V-0884-10 standards, and also a working insulation voltage over the life of the part of up to 1.0-kV<sub>AC,RMS</sub>. On the high-side of the AMC1304, the modulator is supplied with an integrated LDO regulator that allows an unregulated voltage between 4 V and 18 V to power the high side of the chip.

Block Diagram www.ti.com

#### 2.1.3 SN6501

The SN6501 is a monolithic oscillator/power-driver, specifically designed for small-form factor, isolated power supplies in isolated interface applications. The device drives a low-profile, center-tapped transformer primary from a 3.3-V or 5-V DC power supply. The secondary can be wound to provide any isolated voltage based on the transformer turns ratio.

The SN6501 consists of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive the ground-referenced N-channel power switches. The internal logic ensures break-before-make action between the two switches.

#### 2.1.4 TRS3232

The TRS3232 device consists of two line drivers, two line receivers, and a dual charge-pump circuit with ±15-kV electrostatic discharge (ESD) protection pin-to-pin (serial-port connection pins, including GND). The device meets the requirements of the Telecommunications Industry Association and Electronic Industries Alliance TIA/EIA-232-F and provides the electrical interface between an asynchronous communication controller and the serial-port connector. The charge pump and four small external capacitors allow operation from a single 3- to 5.5-V supply. The devices operate at data signaling rates up to 250 kbit/s and a maximum of 30-V/µs driver output slew rate.

#### 2.1.5 ISO7321

The ISO7321 provides galvanic isolation up to 3 kV<sub>RMS</sub> for one minute per UL. This digital isolator has two isolated channels where one is a forward channel and the other is a reverse channel. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. This chip supports a signaling rate of 25 Mbps. The chips can operate from 3.3- and 5-V supply and logic levels. At the rated voltage, the ISO7321 has over a 25-year isolation integrity.

#### 2.1.6 TPS76333

The TPS763xx family of LDO voltage regulators offers the benefits of low dropout voltage, low power operation, and miniaturized packaging. These regulators feature low dropout voltages and quiescent currents compared to conventional LDO regulators. A combination of new circuit design and process innovation has enabled the usual PNP pass transistor to be replaced by a PMOS pass element. Because the PMOS pass element functions as a low-value resistor, the dropout voltage is very low—typically 300 mV at 150 mA of load current (for the TPS76333)—and is directly proportional to the load current. Because the PMOS pass element is a voltage-driven device, the quiescent current is very low (140  $\mu$ A maximum) and is stable over the entire range of output load current (0 mA to 150 mA). The TPS763xx also features a logic-enabled sleep mode to shut down the regulator, reducing quiescent current to 1  $\mu$ A maximum at  $T_J = 25^{\circ}$ C.

#### 2.1.7 ISO7320

The ISO7320 provides galvanic isolation up to 3 kV<sub>RMS</sub> for 1 minute per UL. This digital isolator has two isolated forward channels. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. This chip supports a signaling rate of 25 Mbps. The chips can operate from 3.3- and 5-V supply and logic levels. At the rated voltage, the ISO7320 device has over a 25-year isolation integrity.

## 3 System Design Theory

#### 3.1 Design Hardware Implementation

#### 3.1.1 Analog Inputs

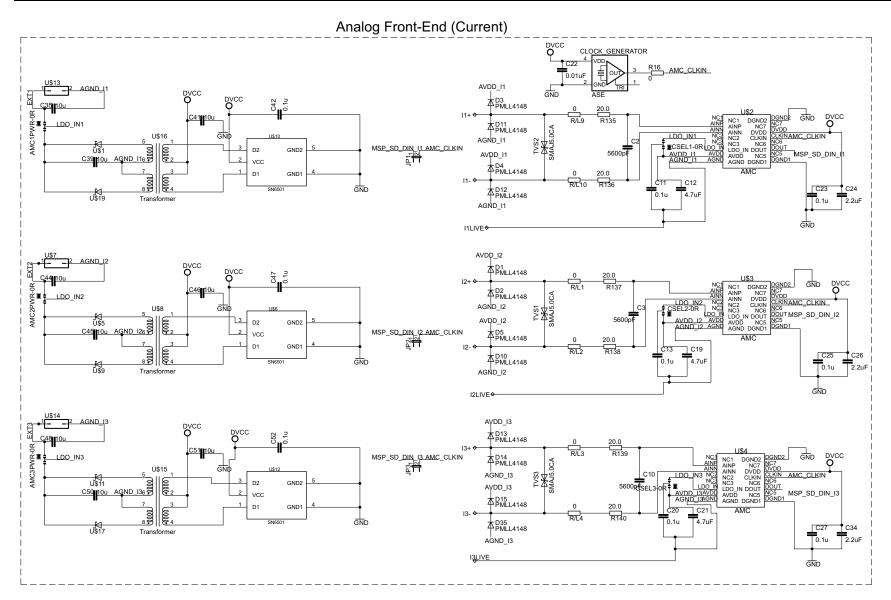

The design of the front end consists of the three AMC1304 chips used for measuring current, the MSP430F67641s three digital filters that are connected to each AMC1304, a 10-bit SAR ADC (ADC10\_A), and a mechanism to synchronize the digital filters with the SAR ADC.

For maximum accuracy, the AMC1304 requires that the input analog signal voltage does not exceed ±50 mV. In addition, the AMC1304 has differential inputs; therefore, the AC current signal from mains can be directly interfaced without the requirement for level shifters.

In contrast, the ADC10\_A module has single-ended inputs. Therefore the ADC10\_A requires that the sensed voltage is between 0-V<sub>REF</sub> Volts, with the option to select the V<sub>REF</sub> source and voltage in the software. As a result, after the mains voltage is divided down for sensing, the voltage front-end circuitry requires a level shifter to properly interface to the ADC10\_A module.

## 3.1.1.1 Voltage Analog Front-End

The voltage from the mains is usually 230 V or 120 V and must be brought down to within  $V_{REF}$  Volts. The analog front-end for voltage consists of spike protection varistors followed by a voltage divider and shifter network, and a RC low-pass filter that functions like an anti-alias filter.

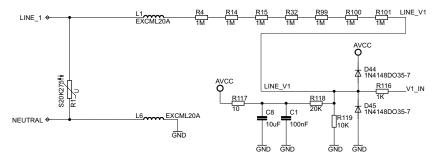

Figure 6. Analog Front-End for Voltage Inputs

Figure 6 shows the analog front-end for the voltage inputs for a mains voltage of 230 V. The voltage is brought down to a range within  $V_{REF}$  volts, where  $V_{REF}$  is selected to be the 2.0-V reference produced by the chips reference module. The maximum voltage that is fed to the ADC is usually a certain margin below the maximum  $V_{REF}$  voltage. As an example, when the 2.0-V reference is selected, the front end may be built to produce a maximum voltage of 1.4 V to 1.6 V when the maximum mains voltage is applied. This margin helps prevent ADC clipping when the system is exposed to harmonics or an over-voltage condition.

#### 3.1.1.2 Current Front-End

## 3.1.1.2.1 AMC1304 High-Side Power Supply

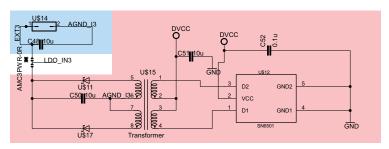

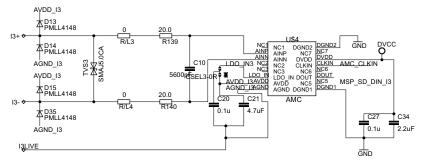

To sense the voltage across the shunt, the high-side of each AMC1304 device must be powered. Because each AMC1304 should be referenced from a different line voltage, a different power supply is required for each AMC1304. Figure 7 shows the designs different power options for the AMC1304.

Figure 7. AMC1304 High-Side Power Options

In Figure 7, LDO\_IN3 is fed directly into the AMC1304 to provide power to it. Because the AMC1304 has an integrated LDO, LDO\_IN3 can be unregulated as long as the voltage fed into LDO\_IN of the AMC1304 is within the 4- to 18-V operating range.

In this design, there are two options for powering the high side of the AMC1304. The first option (shaded blue in Figure 7), is to provide the necessary 4- to 18-V from an external isolated voltage supply to its associated terminal block (U\$14 in Figure 7). The second option (shaded red in Figure 7), is to use the on-board isolated power supply that uses DVCC as a voltage input, a transformer, and the SN6501 transformer driver to provide an unregulated voltage into the AMC1304s integrated LDO input. In this design, a ferromagnetic core transformer is used; however, the SN6501 can also be used with an air-core transformer instead.

For further details on this power supply implementation, please refer to Section 3.6 of the *Isolated, Shunt-Based Current Sensing Reference Design* (TIDU384).

#### 3.1.1.2.2 Current Sensing

The analog front-end for current inputs is different from the analog front-end for the voltage inputs. Figure 8 shows the analog front-end used for a current channel.

Figure 8. Analog Front-End for Current Inputs

The analog front-end for current consists of diodes and transorbs for any additional transient voltage suppression, footprints (R/L3 and R/L4) that could be replaced with inductors for EMI suppression (these footprints are populated with  $0-\Omega$  resistors by default), an anti-alias filter (R139, R140, and C10), and the AMC1304 isolated delta-sigma modulator.

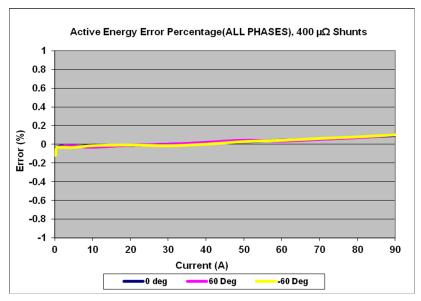

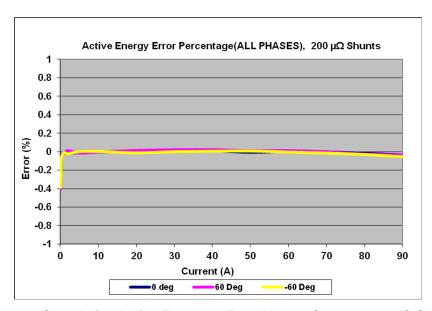

In Figure 8, the three-terminal shunt used for current measurement is to be connected at I3+, I3-, and I3Live. The value of this shunt is selected based on balancing maximizing the peak analog voltage input into the AMC1304 with minimizing the power dissipation of the shunt. In particular, for optimal accuracy, the peak DC voltage fed into the AMC1304 must be as close as possible to 50 mV without surpassing this voltage. This peak voltage is dependent on the rated maximum current of the system and the resistance of the selected shunt. For example, this design uses 400- $\mu$ 0 shunts (utilized shunts are shown here: http://www.vishay.com/docs/30173/wsms3124.pdf). With these 400- $\mu$ 0 shunts and a maximum RMS current of 90 A, the maximum DC voltage fed into the AMC1304 is 90 x  $\sqrt{2}$  x (400 x 10<sup>-6</sup>)  $\approx$  50 mV. To minimize the power dissipation in the shunt, a smaller value shunt can also be used. In this design, 200- $\mu$ 0 shunts are also used. However, by using smaller value shunts, the voltage fed into the AMC1304 is also reduced. As a result, there is a tradeoff in accuracy. Based on the requirements of the system, the tradeoff in accuracy from using a shunt with a small resistance and the reduced power dissipation from choosing the smaller shunt must be taken into account when selecting the proper shunt value.

#### 3.2 Metrology Software Implementation

This section discusses the software for the implementation of three-phase metrology. The first subsection discusses the setup of various peripherals of the metrology and application processors. Subsequently, the metrology software is described as two major processes: the foreground process and background process.

#### 3.2.1 Peripherals Setup

#### 3.2.1.1 SD24 B Setup

The MSP430F67641 has three delta-sigma data converters, with each of them having the ability to bypass its internal modulator and accept an external bit-stream to be used with its associated digital filters. This feature is used to obtain ADC samples using the bit-stream input that is output from the AMC1304.

In addition, the SD24\_B has a trigger generator module that is used to trigger the ADC10, which in turn is used to sense the corresponding three voltages of the three-phase system. In this application, all of the digital filters for the SD24\_B ADCs and the trigger generator are grouped together for synchronization.

The modulation clock (fM) to the trigger generator and the digital filters of the SD24\_B ADCs is derived from system clock, which is configured to run at 19,798,016 Hz. Because the AMC1304 can support a clock from 5 MHz to 20 MHz, this clock can be used as the modulation clock for the AMC1304 without being further divided down. Similarly, the digital filters of the MSP430F67641s SD24\_B ADC can also operate at this 20-MHz modulation clock frequency (unlike the internal modulators of the SD24\_B ADC, which are bypassed in this application). In this design, the modulation clock used in the SD24\_B is derived internally and output from the SD24\_B module to the AMC1304 device.

To reduce the central processing unit (CPU) utilization, the effective sample rate is divided down to 4833.5 samples per second for the digital filters. This reduction is first accomplished by choosing the highest oversampling ratio (OSR) setting for the digital filters and trigger generator, which is 1024. Because the sampling frequency is defined as  $F_s = fM / OSR$ , this results in a sampling frequency of 19334. To further divide this sample rate, the software skips the ADC samples produced from the digital filter. In this design, three samples are skipped for every four samples, which results in an effective sample rate of 4833.5 samples per second for the ADC samples produced from the digital filter. For every sample that is not skipped, it is used for performing metrology calculations.

In contrast, because the trigger generator is used to keep track of when to skip samples, the trigger generator still has a triggering frequency of 19334 samples per second. Despite having a trigger frequency of 19334, the sample rate for the voltage samples is still 4833.5 because the ADC10\_A used for sensing voltages is only re-enabled for conversions one time every four samples.

In the application, the following SD24 B channels associations are used:

SD0DIO (Converter 0 digital filter) → Current I1 (Current I<sub>A</sub>)

SD1DIO (Converter 1 digital filter) → Current I2 (Current I<sub>B</sub>)

SD2DIO (Converter 2 digital filter)  $\rightarrow$  Current I3 (Current I<sub>C</sub>)

#### 3.2.1.2 ADC10\_A Setup

The ADC10 is used to sample the three mains voltages and is triggered by the SD24\_Bs trigger generator once every four samples. When triggered by the  $\Sigma\Delta$ , the ADC10 enters autoscan mode and samples 6 of its channels once. In the software, the clock to the ADC10 is set to 4 MHz. The sample and hold time for each converter is 8 cycles and the conversion time is 12 cycles, which results in an approximate 20-cycle (approximately 5  $\mu$ s) delay between conversion results of adjacent converters. In addition, the ADC10\_A uses the 2.0-V reference from the REF module and is configured to output 10-bit results that are scaled to 16-bit twos complement numbers (ADC10DF = 1). This configuration allows the ADC results from the ADC10 to be treated as a 16-bit signed number when performing mathematical operations.

In this application, the following are the relevant ADC10 channel associations:

A10 (internal channel) → Temperature sensor

A5 → Voltage V1

A4 → Voltage V2

A3 → Voltage V3

#### 3.2.1.3 Real Time Clock (RTC C)

The RTC\_C is a real-time clock module that is configured to give precise one second interrupts. Based off of these one second interrupts, the time and date are updated in software, as necessary.

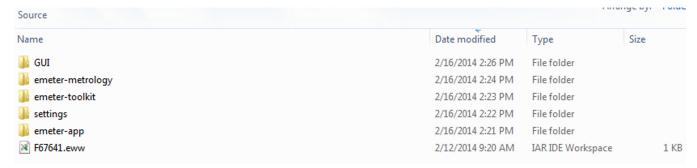

## 3.2.1.4 LCD Controller (LCD\_C)

The LCD controller on the MSP430F67641 can support up to 8-mux displays and 320 segments. The LCD controller is also equipped with an internal charge pump that can be used for good contrast. In the current design, the LCD controller is configured to work in 4-mux mode using 160 segments with a refresh rate set to ACLK/64, which is 512 Hz.

#### 3.2.1.5 Port Map

The MSP430F67641 has a port mapping controller that allows a flexible mapping of digital functions to port pins. The set of digital functions that can be ported to other pins is dependent on the device. For the MSP430F67641 device in particular, the digital bit-stream inputs for the three SD24\_B converters and the delta-sigma modulation clock output are all available options to port to ports P1, P2, and P3. In this design, this port mapping feature is used for providing flexibility in the PCB layout.

Using the port mapping controller, the following mappings are used:

SDCLK (SD24\_B modulation clock output) → Port P2.6

SD0DIO (SD24\_B Converter 0 digital filter input)  $\rightarrow$  Port P3.1

SD1DIO (SD24\_B Converter 1 digital filter input) → Port P3.0

SD2DIO (SD24\_B Converter 2 digital filter input)  $\rightarrow$  Port P2.7

#### 3.2.1.6 DMA

The direct memory access (DMA) module is used to transfer all of the ADC10 conversion results automatically from the ADC10 to memory. Each time all of the six sampled ADC channels are converted and placed into memory, the DMAIFG flag is set; as a result, this flag can be used to determine the completion of each ADC10 autoscan sequence.

#### 3.2.2 Foreground Process

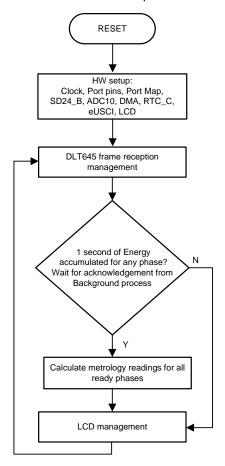

The foreground process includes the initial setup of the MSP430 hardware and software immediately after a device RESET. Figure 9 shows the flowchart for this process.

Figure 9. Foreground Process

The initialization routines involve the setup of the SD24\_B module; ADC10\_A module; DMA; clock system; general purpose input/output (GPIO) port pins and associated port map controller; RTC module for clock functionality; LCD; and the USCI\_A0 for UART functionality.

After the hardware is setup, any received frames from the GUI are processed. Subsequently, the foreground process checks whether the background process has notified the foreground process to calculate new metering parameters. This notification is accomplished through the assertion of the "PHASE\_STATUS\_NEW\_LOG" status flag whenever a frame of data is available for processing. The data frame consists of the processed dot products that were accumulated for one second in the background process. This is equivalent to an accumulation of 50 or 60 cycles of data synchronized to the incoming voltage signal. In addition, a sample counter keeps track of how many samples accumulate over this frame period. This count can vary as the software synchronizes with the incoming mains frequency.

The processed dot products include the  $V_{RMS}$ ,  $I_{RMS}$ , active power, and reactive power. These dot products are used by the foreground process to calculate the corresponding metrology readings in real-world units. Processed voltage dot products are accumulated in 48-bit registers. In contrast, processed current dot products, active energy dot products, and reactive energy dot products are accumulated in separate 64-bit registers to further process and obtain the RMS and mean values. Using the foreground's calculated values of active and reactive power, the apparent power is calculated. The frequency (in Hz) and power factor are also calculated using parameters calculated by the background process using the formulas in Section 3.2.2.1.

The foreground process also updates the LCD. The LCD display item is changed every two seconds. Refer to Section 7.1 for more information about the different items displayed on the LCD.

#### 3.2.2.1 Formulae

This section briefly describes the formulas used for the voltage, current, energy, and temperature calculations.

As previous sections describe, voltage and current samples are obtained at a sampling rate of 4833.5 Hz. All of the samples that are taken in one second are kept and used to obtain the RMS values for voltage and current for each phase. The RMS values are obtained by the following formulas:

$$V_{RMS,ph} = K_{v,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample} v_{ph}(n) \times v_{ph}(n)}{Sample count} - v_{offset,ph}}$$

$$I_{RMS,ph} = K_{i,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample} i_{ph}(n) \times i_{ph}(n)}{Sample count} - i_{offset,ph}}$$

(2)

where

- ph = Phase parameters that are being calculated [that is, Phase A(=1), B(=2), or C(=3)]

- $V_{ph}(n) = Voltage sample at a sample instant n$

- V<sub>offset.ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the voltage converter

- $I_{ph}(n)$  = Each current sample at a sample instant n

- I<sub>offset on</sub>= Offset used to subtract effects of the additive white Gaussian noise from the current converter

- Sample count = Number of samples in one second

- K<sub>v.ph</sub> = Scaling factor for voltage

Power and energy are calculated for a frames worth of active and reactive energy samples. These samples are phase corrected and passed on to the foreground process, which uses the number of samples (sample count) to calculate phase active and reactive powers through the following formulas:

$$P_{ACT,ph} = K_{ACT,ph} \frac{\sum_{n=1}^{Sample} v(n) \times i_{ph}(n)}{Sample count}$$

$$P_{REACT,ph} = K_{REACT,ph} \frac{\sum_{n=1}^{Sample} v_{90}(n) \times i_{ph}(n)}{Sample count}$$

$$P_{APP,ph}^{2} = \sqrt{P_{ACT,ph}^{2} + P_{REACT,ph}^{2}}$$

(5)

where

- V<sub>90</sub>(n) = Voltage sample at a sample instant 'n' shifted by 90°

- K<sub>ACT.ph</sub> = Scaling factor for active power

Please note that for reactive energy, the 90° phase shift approach is used for two reasons:

- 1. This approach allows accurate measurement of the reactive power for very small currents.

- 2. This approach conforms to the measurement method specified by IEC and ANSI standards.

The calculated mains frequency is used to calculate the 90 degrees-shifted voltage sample. Because the frequency of the mains varies, it is important to first measure the mains frequency accurately to phase shift the voltage samples accordingly (see Section 3.2.3.1.2 for details).

To get an exact 90° phase shift, interpolation is used between two samples. For these two samples, a voltage sample slightly more than 90 degrees before the current sample and a voltage sample slightly less than 90 degrees before the current sample are used. The application's phase shift implementation consists of an integer part and a fractional part. The integer part is realized by providing an N samples delay. The fractional part is realized by a one-tap FIR filter. In the software, a lookup table provides the filter coefficients that are used to create the fractional delays.

In addition to calculating the per-phase active and reactive powers, the cumulative sum of these parameters are also calculated by the following Equation 7, Equation 8, and Equation 9:

$$P_{ACT,Cumulative} = \sum_{ph=1}^{3} P_{ACT,ph}$$

(7)

$$P_{REACT,Cumulative} = \sum_{ph=1}^{3} P_{REACT,ph}$$

(8)

$$P_{APP,Cumulative} = \sum_{ph=1}^{3} P_{APP,ph}$$

(9)

Using the calculated powers, energies are calculated by the following formulas in Equation 10:

$$E_{ACT,ph} = P_{ACT,ph} \times Sample count$$

$$E_{REACT.ph} = P_{REACT.ph} \times Sample count$$

$$E_{APP,ph} = P_{APP,ph} \times Sample count$$

(10)

From there, the energies are also accumulated to calculate the cumulative energies, by the following Equation 11, Equation 12, and Equation 13:

$$E_{ACT,Cumulative} = \sum_{ph=1}^{3} E_{ACT,ph}$$

(11)

$$E_{REACT,Cumulative} = \sum_{ph=1}^{3} E_{REACT,ph}$$

(12)

$$\mathsf{E}_{\mathsf{APP},\mathsf{Cumulative}} = \sum_{\mathsf{ph}=1}^{3} \mathsf{E}_{\mathsf{APP},\mathsf{ph}} \tag{13}$$

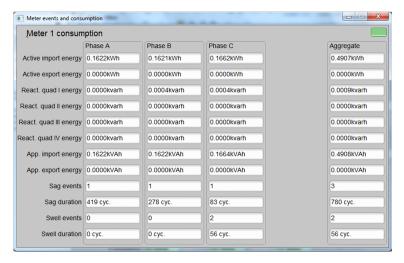

The calculated energies are then accumulated into buffers that store the total amount of energy consumed since system reset. Please note that these energies are different from the working variables used to accumulate energy for outputting energy pulses. There are four sets of buffers that are available: one for each phase and one for the cumulative of the phases. Within each set of buffers, the following energies are accumulated:

- 1. Active import energy (active energy when active energy ≥ 0)

- 2. Active export energy (active energy when active energy < 0)

- 3. React. Quad I energy (reactive energy when reactive energy ≥ 0 and active power ≥ 0; inductive load)

- 4. React. Quad II energy (reactive energy when reactive energy ≥ 0 and active power < 0; capacitive generator)

- 5. React. Quad III energy (reactive energy when reactive energy < 0 and active power < 0; inductive generator)

- 6. React. Quad IV energy (reactive energy when reactive energy < 0 and active power ≥ 0; capacitive

- 7. App. import energy (apparent energy when active energy  $\geq 0$ )

- 8. App. export energy (apparent energy when active energy < 0)

The background process also calculates the frequency in terms of samples per mains cycle. The foreground process then converts this samples per mains cycle to Hertz by the following formula:

Frequency (Hz) =

$$\frac{\text{Sample Rate (samples / sec ond)}}{\text{Frequency (samples / cycle)}}$$

(14)

After the active power and apparent power have been calculated, the absolute value of the power factor is calculated. In the system's internal representation of power factor, a positive power factor corresponds to a capacitive load; a negative power factor corresponds to an inductive load. The sign of the internal representation of power factor is determined by whether the current leads or lags voltage, which is determined in the background process. Therefore, the internal representation of power factor is calculated by the following formula:

Internal Representation of Power Factor =

$$\begin{cases} \frac{P_{Act}}{P_{Apparent}}, & \text{if capacitive load} \\ -\frac{P_{Act}}{P_{Apparent}}, & \text{if inductive load} \end{cases}$$

(15)

In addition, temperature is also calculated in the software. Temperature is calculated using the TLV entries on the MSP430F67641 and is calculated in units of Celsius. The measured values for 30°C ±3°C and 85°C ±3°C for the 2.0-V reference are used for calculating temperature. The following Equation 16 shows the exact formula that is used to calculate temperature:

$$Temp = (ADC(raw) - CAL\_ADC\_20T30) \times \left(\frac{85 - 30}{CAL\_ADC\_20T85 - CAL\_ADC\_20T30}\right)$$

(16)

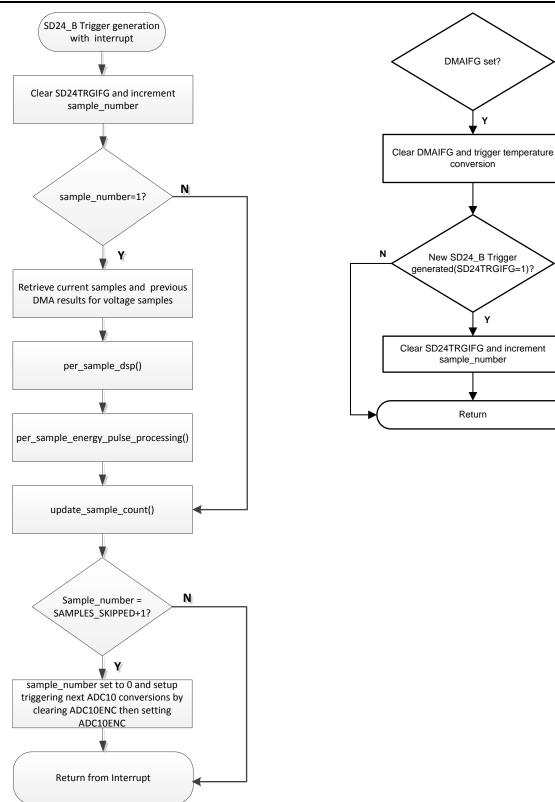

## 3.2.3 Background Process

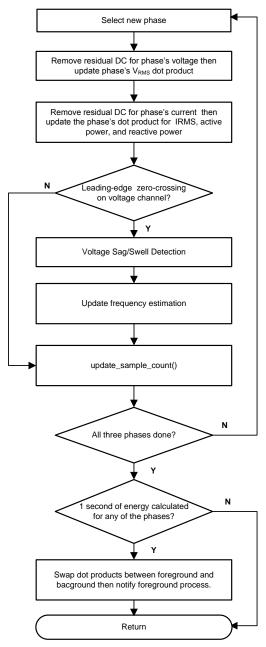

Figure 10 shows the background process, which mainly deals with timing critical events in software. The background process uses the SD24\_B trigger generation to collect voltage and current samples. The SD24\_B provides a trigger 19334 times per second. For a certain number of these triggers, sample processing is done on the previously obtained voltage and current samples. This sample processing is done by the "per\_sample\_dsp ()" function. After sample processing, the background process uses the "per\_sample\_energy\_pulse\_processing ()" for the calculation and output of energy-proportional pulses. In the software, the "SAMPLES\_SKIPPED" macro determines how many triggers to skip between successive calculations. Because the default value of this macro is 3, sample processing and energy pulse processing is done once every four SD24\_B triggers. As a result, three out of four current samples are skipped and not used for calculations, which leads to an effective sample rate of 4833.5 samples per second for the current channels.

To keep track of when to skip samples, the "sample\_number" variable is used to keep track of how many trigger pulses have been produced since the last time sample and energy pulse processing has occurred. Due to the high frequency of triggers, triggers may occur in the middle of sample processing within the SD24\_B ISR. Because interrupts are disabled within the ISR, the trigger pulse flag (SD24TRGIFG) is checked in various places within the ISR code to keep track of triggers that occur during the SD24\_B interrupt. These checks are done by calling the "update\_sample\_count ()" function (Figure 11). The places where the update\_sample\_count is called are set so that the time between checks is less than the period of the triggers.

Figure 10. Background Process

Figure 11. update\_sample\_count ()

Ν

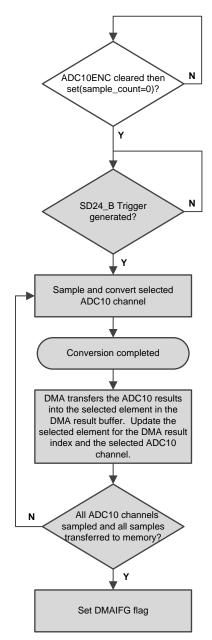

Similar to the current samples, the sample rate for voltage samples is also 4833.5 samples per second; however, unlike the current samples, this sample rate is not achieved by skipping samples. Instead, the sample rate is caused by only re-enabling the ADC10 for conversions to measure the phase voltage channels only once every SAMPLES\_SKIPPED + 1 samples. Re-enabling the ADC10 for conversions is accomplished by clearing and then setting the ADC10ENC bit. As Figure 10 shows, this clearing and setting is done when the sample\_number = (SAMPLES\_SKIPPED + 1). As a result, the ADC10 converts the voltage samples in parallel to the sample processing done in the background process. Figure 12 shows this parallel activity. In Figure 12, the gray containers represent items that are automatically done by the configuration of the ADC10, DMA, and  $\Sigma\Delta$  modules. For these gray items, CPU intervention is not required.

Figure 12. ADC10 Triggering Process

As Figure 12 represents, whenever the ADC10 is triggered, the ADC10 enters autoscan mode and samples six ADC channels once. After each channel has a conversion result, the DMA automatically places these results in memory and the next channel's conversion is automatically started. For each converter, there is a memory location that stores the conversion results for that particular converter. The procedure of sampling a converter and storing the results in memory is repeated until the last converter (ADC10INCH = 0) is sampled. Because the clock to the ADC10 is set to 4 MHz, the sample and hold time for each converter is 8 cycles, and the conversion time is 12 cycles, there is an approximate 20-cycle (approximately 5-µs) delay between the conversion results of adjacent converters.

Once all of the ADC10 channels are sampled and the samples are transferred to memory, the DMAIFG flag is set to indicate that the ADC10 has completed its operation and may be used for other conversions.

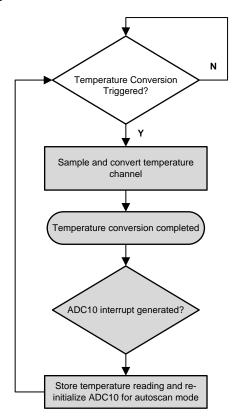

To sense the internal temperature sensor using the ADC10, a recommended sample period of at least 30 µs must be used. As a result, the autoscan mode that is used to measure the phase voltages cannot be extended to also measure the temperature channel. To prevent this loss of temperature channel measurement, a single conversion of the ADC10 temperature channel is triggered (see Figure 13). The temperature conversion is triggered when the DMAIFG flag is asserted (see Figure 12) to indicate that the phase voltages have just been completely converted and transferred to memory so that other conversions can be started. The check for the completion of the phase voltage sampling is done within the update\_sample\_count function (see Figure 11). Because the update\_sample\_count function is called multiple times within the SD24\_B interrupt, this ensures that the temperature conversion can be started relatively quickly. After a temperature reading has been received and its associated ISR has been called, temperature reading is stored in memory and the ADC10 settings are then reset to support autoscan mode for the next conversion.

Figure 13. Temperature Triggering Mechanism

#### 3.2.3.1 per sample dsp ()

Figure 14 shows the flowchart for the per\_sample\_dsp () function. The per\_sample\_dsp function() is used to calculate intermediate dot product results that are fed into the foreground process for the calculation of metrology readings. The ADC10 is configured to represent the 10-bit voltage results as a 16-bit signed result. Because 16-bit voltage samples are used, the voltage samples are further processed and accumulated in dedicated 48-bit registers. In contrast, as a result of using an oversampling ratio of 1024, current samples have more bits. Because many of these bits are unnecessary, they are shifted out so that 24-bit current samples are used. As a result, the current samples are processed and accumulated in dedicated 64-bit registers. Per-phase active power and reactive power are also accumulated in 64-bit registers.

Figure 14. per\_sample\_dsp ()

After sufficient samples (approximately one seconds worth) have been accumulated, then the foreground function is triggered to calculate the final values of  $V_{RMS}$ ;  $I_{RMS}$ ; active, reactive, and apparent powers; active, reactive, and apparent energy; and frequency, temperature, and power factor. In the software, there are two sets of dot products: at any given time, one is used by the foreground for calculation and the other used as the working set by the background. After the background process has sufficient samples, it swaps the two dot products so that the foreground uses the newly acquired dot products just calculated by the background process and the background process uses a new empty set to calculate the next set of dot products.

Whenever there is a leading-edge zero-crossing (- to + voltage transition) on a voltage channel, the per\_sample\_dsp function () is also responsible for updating the corresponding phases frequency (in samples per cycle) and voltage sag and swell conditions. For the sag conditions, whenever the RMS voltage is below a certain user-defined threshold percentage, the number of mains cycles where this condition persists is logged as the sag duration. The number of periods in time where there was a sag condition is logged as the sag events count. Please note that the sag duration corresponds to the total number of cycles in a sag condition since being reset, and is therefore, not cleared for every sag event. Also, when the RMS voltage is above a certain threshold percentage, swell events and duration are logged in a similar way.

## 3.2.3.1.1 Voltage and Current Signals

The output of each SD24\_B digital filter and ADC10 converter is a signed integer and any stray DC or offset value on these converters are removed using a DC tracking filter. Separate DC estimates for all voltages and currents are obtained using the filter and voltage and current samples, respectively. These estimates are then subtracted from each voltage and current sample. The resulting instantaneous voltage and current samples are used to generate the following intermediate dot product results:

- Accumulated squared values of voltages and currents, which is used for V<sub>RMS</sub> and I<sub>RMS</sub> calculations, respectively.

- Accumulated energy samples to calculate active energies.

- Accumulated energy samples using current and 90° phase shifted voltage to calculate reactive energies.

These accumulated values are processed by the foreground process.

#### 3.2.3.1.2 Frequency Measurement and Cycle Tracking

The instantaneous voltage of each phase is accumulated in 48-bit registers. In contrast, the instantaneous current, active power, and reactive power are accumulated in 64-bit registers. A cycle tracking counter and sample counter keep track of the number of samples accumulated. When approximately one seconds worth of samples has been accumulated, the background process switches the foreground and background and then notifies the foreground process to produce the average results such as RMS and power values. Cycle boundaries are used to trigger the foreground averaging process because this process produces very stable results.

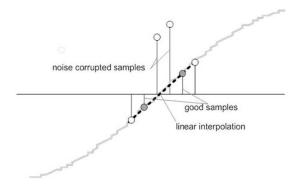

For frequency measurements, a straight-line interpolation is used between the zero-crossing voltage samples. Figure 15 shows the samples near a zero cross and the process of linear interpolation.

Figure 15. Frequency Measurement

Because noise spikes can also cause errors, the application uses a rate of change check to filter out the possible erroneous signals and make sure that the two points that are interpolated are from genuine zero crossing points. For example, with two negative samples, a noise spike can make one of the samples positive, thereby making the negative and positive pair look as if there is a zero crossing.

The resultant cycle-to-cycle timing goes through a weak low-pass filter to further smooth out cycle-to-cycle variations. This filtering results in a stable and accurate frequency measurement that is tolerant of noise.

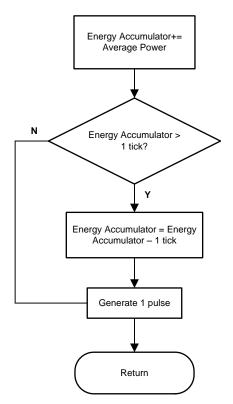

#### 3.2.3.2 LED Pulse Generation (per sample energy pulse processing)

In electricity meters, the active energy consumed is normally measured in a fraction of kilowatt-hour (kWh) pulses. This information can be used to calibrate any meter for accurate measurement. Typically, the measuring element (the MSP430 microcontroller) is responsible for generating pulses proportional to the energy consumed. To serve both these tasks efficiently, pulse generation must be accurate with relatively little jitter. Although time jitters are not an indication of bad accuracy, they give a negative indication of the overall accuracy of the meter, which is why the jitter is averaged out.

This application uses average power to generate these energy pulses. The average power (calculated by the foreground process) accumulates every time the per\_sample\_energy\_pulse\_processing is called, thereby spreading the accumulated energy from the previous one second time frame evenly for each interrupt in the current one second time frame. This process is equivalent to converting it to energy. When the accumulated energy crosses a threshold, a pulse is generated. The amount of energy above this threshold is kept and a new energy value is added on top of the energy above the threshold in the next interrupt cycle. Because the average power tends to be a stable value, this way of generating energy pulses is very steady and free of jitter.

The threshold determines the energy "tick" specified by meter manufacturers and is a constant. The "tick" is usually defined in pulses per kWh or just in kWh. One pulse is generated for every energy "tick". For example, in this application, the number of pulses generated per kWh is set to 6400 for active and reactive energies. The energy "tick" in this case is 1 kWh/6400. Energy pulses are generated and available on a header and also through light-emitting diodes (LEDs) on the board. GPIO (port) pins are used to produce the pulses.

In the EVM, the LEDs that are labeled "Phase 1", "Phase 2", "Phase 3", and "Active" correspond to the active energy consumption for phase A, phase B, phase C, and the cumulative three-phase sum, respectively. "Reactive" corresponds to the cumulative three-phase reactive energy sum. The number of pulses per kWh and each pulse duration can be configured in software. Figure 16 shows the flow diagram for pulse generation. This flow diagram is valid for pulse generation of individual or accumulative phase active, reactive, and apparent energy.

Figure 16. Pulse Generation for Energy Indication

The average power is in units of 0.001 W and the 1-kWh threshold is defined as:

1 kWh threshold =  $(1 / 0.001) \times 1$  kW × (number of interrupts per second) × (number of seconds in one hour) =  $1000000 \times 4833.5 \times 3600 = 0$ xFD36494F600

## 3.2.3.3 Phase Compensation

In order to ensure accurate measurements, the relative phase shift between voltage and current samples must be compensated. This phase shift may be caused by the passive components of the voltage and current input circuit or even the sequential sampling on the voltage channel.

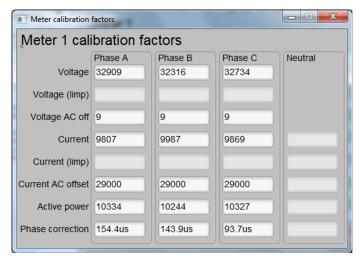

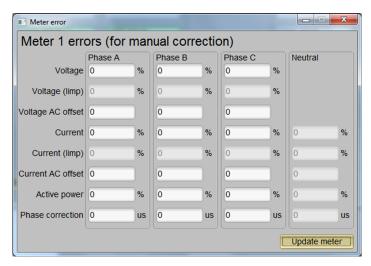

The implementation of the phase shift compensation consists of an integer part and a fractional part. The integer part is realized by providing an N samples delay. The fractional part is realized by a one-tap finite impulse response (FIR) filter that interpolates between two samples, similar to the FIR filter used for providing 90°-shifted voltage samples for reactive energy measurements. In the software, a lookup table provides the filter coefficients that are used to create the fractional delays. The lookup table provides fractional phase shifts as small as 1/256th of a sample. The 4833.5 sample rate used in this application corresponds to a 0.0145° degree resolution at 50 Hz. In addition to the filter coefficients, the lookup table also has an associated gain variable for each set of filter coefficients. This gain variable is used to cancel out the resulting gain from using a certain set of filter coefficients.

## 4 Getting Started Hardware

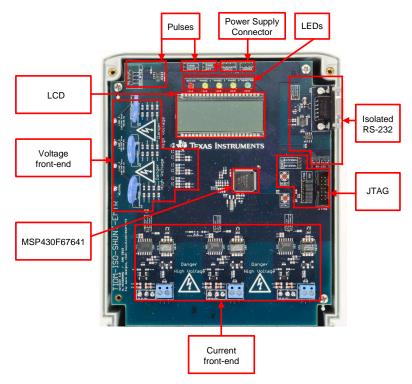

The following figures of the EVM best describe the hardware: Figure 17 is the top view of the energy measurement system and Figure 18 shows the location of various pieces of the EVM based on functionality.

Figure 17. Top View TIDA-00601 Design

Figure 18. Top View of TIDA-00601 Design With Components Highlighted

## 4.1 Connections to the Test Setup for AC Voltages

AC voltages can be applied to the board for testing purposes at these points:

- Pad "LINE1" corresponds to the line connection for phase A.

- Pad "LINE2" corresponds to the line connection for phase B.

- Pad "LINE3" corresponds to the line connection for phase C.

- Pad "Neutral" corresponds to the neutral voltage. The voltage between any of the three line connections to the neutral connection must not exceed 230-V AC at 50/60 Hz.

- I1+, I1-, and I1Live are connected to the output terminals of the shunt that is used for measuring the current for Phase A. When a shunt is selected, the differential voltage that is output across I1+ and I1must not exceed 50 mV.

- I2+, I2-, and I2Live are connected to the output terminals of the shunt that is used for measuring the current for Phase B. When a shunt is selected, the differential voltage that is output across I2+ and I2must not exceed 50 mV.

- I3+, I3-, and I3Live are connected to the output terminals of the shunt that is used for measuring the current for Phase C. When a shunt is selected, the differential voltage that is output across I3+ and I3must not exceed 50 mV.

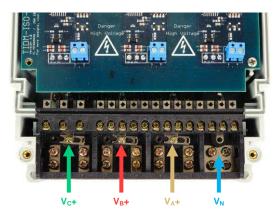

Figure 19 and Figure 20 show the various connections that must be made to the test setup for proper functionality of the EVM. When a test AC source must be connected, the connections have to be made according to the EVM design. Figure 19 shows the connections from the top view. VA+, VB+, and VC+ correspond to the line voltages for phases A, B, and C, respectively. VN corresponds to the neutral voltage from the test AC source.

Figure 19. Top View of EVM With Test Setup Connections

Figure 20 shows the connections from the front view. IA+ and IA- correspond to the current inputs for phase A, IB+, and IB- correspond to the current inputs for phase B; IC+ and IC- correspond to the current inputs for phase C. VN corresponds to the neutral voltage from the test setup.

Figure 20. Front View of EVM With Test Setup Connections

## 4.2 Power Supply Options and Jumper Settings

The entire board is powered by a single DC voltage rail (DVCC), which can be derived either by JTAG or external power. Various jumper headers and jumper settings are present to add to the flexibility to the board. Some of these headers require that jumpers be placed appropriately for the board to correctly function. Table 1 indicates the functionality of each jumper on the board.

**Table 1. Header Names and Jumper Settings**

| HEADER/HEADER OPTION NAME        | TYPE                            | MAIN<br>FUNCTIONALITY                                                 | VALID USE-CASE                                                                          | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|---------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACT (Not isolated, do not probe) | 1-pin header                    | Active energy pulses (WARNING)                                        | Probe between here and ground for cumulative three-phase active energy pulses.          | This header is not isolated from AC voltage, so do not connect measuring equipment unless isolators external to the EVM are available. See Isolated ACT instead.                                                                                                                                                                                                                                            |

| AMC1PWR                          | 3-pad jumper resistor footprint | Selection for the<br>AMC1304 high-side<br>power supply for<br>Phase A | This header is used to select the power source for the AMC1304 associated with Phase A. | To enable powering the high-side using the on-board isolated power supply, place a 0- $\Omega$ resistor on the two top-most terminals (when the board is oriented as Figure 17 shows). To enable powering the high side by providing 4 V to 18 V directly to the U\$16-terminal block , place a 0- $\Omega$ resistor on the two bottom-most terminals (when the board is oriented as Figure 17 shows).      |

| AMC2PWR                          | 3-pad jumper resistor footprint | Selection for the<br>AMC1304 high-side<br>power supply for<br>Phase B | This header is used to select the power source for the AMC1304 associated with Phase B. | To enable powering the high side using the on-board isolated power supply, place a $0$ - $\Omega$ resistor on the two top-most terminals (when the board is oriented as Figure 17 shows). To enable powering the high side by providing 4 V to 18 V directly to the U\$8-terminal block , place a $0$ - $\Omega$ resistor on the two bottom-most terminals (when the board is oriented as Figure 17 shows). |

| AMC3PWR                          | 3-pad jumper resistor footprint | Selection for the<br>AMC1304 high-side<br>power supply for<br>Phase C | This header is used to select the power source for the AMC1304 associated with Phase C. | To enable powering the high side using the on-board isolated power supply, place a 0- $\Omega$ resistor on the two top-most terminals (when the board is oriented as Figure 17 shows). To enable powering the high side by providing 4 V to 18 V directly to the U\$15-terminal block place a 0- $\Omega$ resistor on the two bottom-most terminals (when the board is oriented as Figure 17 shows).        |

Table 1. Header Names and Jumper Settings (continued)

| Table 1. Header Names and Jumper Settings (continued)                    |                                 |                                                               |                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

|--------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| HEADER/HEADER<br>OPTION NAME                                             | TYPE                            | MAIN<br>FUNCTIONALITY                                         | VALID USE-CASE                                                                                                                                                                                                                                                                    | COMMENTS                                                                                                                                     |

| AMC_CLK (Not isolated, do not probe)                                     | 1-pin header                    | Modulation clock fed into the AMC1304                         | Probe between here and ground for the clock fed into the AMC1304 chips. An external clock can also be fed into this header to be used as the modulation clock; however, the software must be changed to accept a modulation clock input instead of providing one from the SD24_B. | Each AMC1304 has its own associated AMC_CLK header. However, all AMC_CLK headers are connected to each other.                                |

| BIT-STREAM_I1 (Not isolated, do not probe without isolated equipment)    | 1-pin header                    | Bit-stream output for<br>the AMC associated<br>with Phase A.  | Probe between here and ground for the bit-stream output from the AMC1304 chip associated with Phase A.                                                                                                                                                                            |                                                                                                                                              |

| BIT-STREAM_I2 (Not isolated, do not probe without isolated equipment)    | 1-pin header                    | Bit-stream output for<br>the AMC associated<br>with Phase B.  | Probe between here and ground for the bit-stream output from the AMC1304 chip associated with Phase B.                                                                                                                                                                            |                                                                                                                                              |

| BIT-STREAM_I3 (Not isolated, do not probe without isolated equipment)    | 1-pin header                    | Bit-stream output for<br>the AMC associated<br>with Phase C.  | Probe between here and ground for the bit-stream output from the AMC1304 chip associated with Phase C.                                                                                                                                                                            |                                                                                                                                              |

| CSEL1                                                                    | 3-pad jumper resistor footprint | Capacitor Connection<br>Select for the<br>AMC1304 for Phase A | For this design, place a 0- $\Omega$ resistor on the two leftmost terminals (when the board is oriented as Figure 17 shows).                                                                                                                                                      |                                                                                                                                              |

| CSEL2                                                                    | 3-pad jumper resistor footprint | Capacitor Connection<br>Select for the<br>AMC1304 for Phase B | For this design, place a 0- $\Omega$ resistor on the two leftmost terminals (when the board is oriented as Figure 17 shows).                                                                                                                                                      |                                                                                                                                              |

| CSEL3                                                                    | 3-pad jumper resistor footprint | Capacitor Connection<br>Select for the<br>AMC1304 for Phase C | For this design, place a 0- $\Omega$ resistor on the two leftmost terminals (when the board is oriented as Figure 17 shows).                                                                                                                                                      |                                                                                                                                              |

| DGND (Not isolated, do not probe)                                        | Header                          | Ground voltage header (WARNING)                               | Not a jumper header,<br>probe here for GND<br>voltage. Connect negative<br>terminal of bench or<br>external power supply<br>when powering the board<br>externally.                                                                                                                | Do not probe if AC mains is not isolated.                                                                                                    |

| DVCC (Not isolated, do not probe)                                        | Header                          | VCC voltage header (WARNING)                                  | Not a jumper header, probe here for VCC voltage. Connect positive terminal of bench or external power supply when powering the board externally.                                                                                                                                  | Do not probe if AC mains is not isolated.                                                                                                    |

| DVCC EXTERNAL<br>(Do not connect<br>JTAG if AC mains is<br>not isolated) | Jumper header option            | JTAG external power<br>selection option<br>(WARNING)          | Place a jumper at this<br>header option to select<br>external voltage for JTAG<br>programming.                                                                                                                                                                                    | This jumper option and the DVCC INTERNAL jumper option comprise one three-pin header used to select the voltage source for JTAG programming. |

Table 1. Header Names and Jumper Settings (continued)

| HEADER/HEADER TYPE MAIN WALLD LIGE CASE COMMENTS                                                   |                      |                                                |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTION NAME                                                                                        | TYPE                 | FUNCTIONALITY                                  | VALID USE-CASE                                                                                                                      | COMMENTS                                                                                                                                                                                                                                                                                                                                                                |

| DVCC INTERNAL<br>(Do not connect<br>JTAG if AC mains is<br>not isolated; isolated<br>JTAG is fine) | Jumper header option | JTAG internal power selection option (WARNING) | Place a jumper at this header option to power the board using JTAG and to select the voltage from the USB FET for JTAG programming. | This jumper option and the DVCC EXTERNAL jumper option comprise one three-pin header used to select the voltage source for JTAG programming.                                                                                                                                                                                                                            |

| ISO_ACT                                                                                            | 1-pin header         | Isolated active energy pulses                  | Probe between here and ground for cumulative three-phase active energy pulses.                                                      | This header is isolated from AC voltage so it is safe to connect to scope or other measuring equipment because isolators are already present. However, either 3.3 V or 5 V must be applied between ISO_GND and ISO_VCC to produce pulses on this pin. The produced pulses have a logical high voltage that is equal to the voltage applied between ISO_GND and ISO_VCC. |

| ISO_GND                                                                                            | 1-pin header         | Isolated ground For energy pulses              | Ground connection for the isolated active and reactive energy pulses.                                                               |                                                                                                                                                                                                                                                                                                                                                                         |

| ISO_REACT                                                                                          | 1-pin header         | Isolate reactive energy pulses                 | Probe between here and ground for cumulative three-phase reactive energy pulses.                                                    | This header is isolated from AC voltage so it is safe to connect to scope or other measuring equipment since isolators are already present. However, either 3.3 V or 5 V must be applied between ISO_GND and ISO_VCC to produce pulses on this pin. The produced pulses have a logical high voltage that is equal to the voltage applied between ISO_GND and ISO_VCC.   |

| ISO_VCC                                                                                            | 1-pin header         | Isolated VCC for energy pulses                 | VCC connection for the isolated active and reactive energy pulses.                                                                  | Either 3.3 V or 5 V must be applied between ISO_GND and ISO_VCC to produce isolated active and reactive pulses on the respective isolated ISO_ACT and ISO_REACT pins. The produced pulses have a logical high voltage that is equal to the voltage applied between ISO_GND and ISO_VCC.                                                                                 |

| JTAG (Do not connect JTAG if AC mains is not isolated)                                             | Jumper header option | 4-wire JTAG programming option (WARNING)       | Place jumpers at the JTAG header options of all of the six JTAG communication headers to select 4-wire JTAG.                        | There are six headers that jumpers must be placed at to select a JTAG communication option. Each of these six headers has a JTAG option and an SBW option to select either 4-wire JTAG or SBW. To enable 4-wire JTAG, all of these headers must be configured for the JTAG option. To enable SBW, all of the headers must be configured for the SBW option.             |

www.ti.com

## **Table 1. Header Names and Jumper Settings (continued)**

| HEADER/HEADER<br>OPTION NAME                                | TYPE                            | MAIN<br>FUNCTIONALITY                           | VALID USE-CASE                                                                                                                                                                                                                                                                                                                                                                                                   | COMMENTS                                                                                                                                                                                                                                                                                                                                                  |

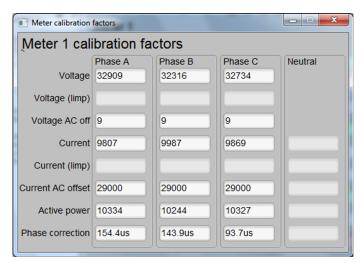

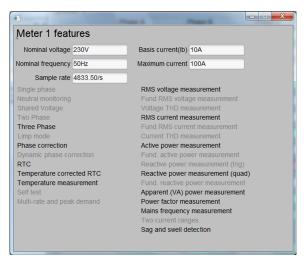

|-------------------------------------------------------------|---------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|