## TI Designs: TIDA-01442 Direct RF-Sampling Radar Receiver for L-, S-, C- and X-Band Using ADC12DJ3200 Reference Design

# Texas Instruments

### Description

The TIDA-01442 TI Design utilizes the ADC12DJ3200 EVM to demonstrate a direct RF-sampling receiver for a radar operating in HF, VHF, UHF L, S, C, and part of X-band. The wide analog input bandwidth and high sampling rate (6.4 GSPS) of the analog-to-digital converter (ADC) provides multi-band coverage with a single receiver or ADC. The direct RF-sampling capabilities of the ADC reduces the component count by eliminating several down-conversion stages, thereby reducing overall system complexity.

### Resources

| Design Folder  |

|----------------|

| Product Folder |

| Product Folder |

| Product Folder |

| Product Folder |

|                |

TI E2E<sup>™</sup> Community

A

### Features

- High Input Frequency Capability of ADC Allows RF Sampling of Signals From L-Band to X-Band

- Max Sample Rate of 6.4 GSPS in Single-Channel (Interleaved Mode) and 3.2 GSPS in Dual-Channel Mode

- Four Independent NCOs per DDC Allow Fast Frequency Hopping Among Bands

- Clocking Solution Optimized for Low Jitter and JESD204B Operation

### Applications

- Military Radar

- Weather Radar

- Air Traffic Control Radar

- Test and Measurement

ASK Our E2E Experts

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

1

### 1 System Description

The TIDA-01442 reference design demonstrates an AC-coupled, dual-channel wideband digitizer used for radar receiver applications. This design is based on the dual-channel, 12-bit, 3.2-GSPS ADC12DJ3200. Both channel A and channel B are AC coupled using a 9-GHz bandwidth balun. This design showcases the high sample rate 6.4 GSPS and wide bandwidth capabilities of the ADC12DJ3200. Both input channels have been optimized for wide bandwidth performance. This design focuses on demonstrating the performance of the device over 9 GHz of bandwidth in addition to discussing clocking and power management.

### 1.1 Key System Specifications

| PARAMETER                     | SPECIFICATIONS                                                                       |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Analog input signal bandwidth | 9 GHz                                                                                |  |  |  |

| Resolution                    | 12 bit                                                                               |  |  |  |

| Max sampling rate             | 6.4 GSPS in single channel interleaved<br>and 3.2 GSPS in dual-channel input<br>mode |  |  |  |

| Number of channels            | 2                                                                                    |  |  |  |

| SNR                           | > 44 dBFS across full bandwidth                                                      |  |  |  |

| Harmonic distortion           | < –46 dBFS HD2/HD3 across full<br>bandwidth                                          |  |  |  |

| Table 1. Key System Specifications |

|------------------------------------|

|------------------------------------|

### 2 System Overview

### 2.1 Block Diagram

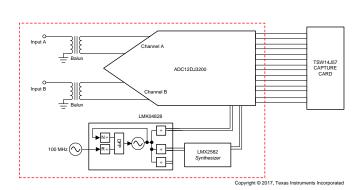

Figure 1 shows the block diagram for the TIDA-01442 reference design. As the figure shows, a singleended input signal can be applied at each input channel. The single-ended input signal is converted to a differential signal with a 9-GHz bandwidth balun. Both input paths can also be modified to accept differential input signals. The clocking for ADC is also implement on the evaluation module (EVM). LMX2582 is used for clocking the ADC and LMK04828 is used for providing the SYSREF signal for the ADC and field-programmable gate array (FPGA), along with any additional clocking required by the FPGA.

Figure 1. TIDA-01442 Block Diagram

3

### 2.2 Highlighted Products

### 2.2.1 ADC12DJ3200

The ADC12DJxx00 family are RF-sampling gigasample ADCs that can directly sample input frequencies from DC to above 9 GHz. In dual-channel mode, the ADC12DJ3200, ADC12DJ2700, and ADC12DJ1600 can sample up to 3200 MSPS, 2700 MSPS or 1600 MSPS. In single-channel mode, the devices can sample up to 6400 MSPS, 5400 MSPS, or 3200 MSPS, respectively. With a –3-dB input bandwidth exceeding 9 GHz in either dual- or single-channel mode, the ADC12DJ3200/2700/1600 can be used to sample signals in the first, second, and higher Nyquist zones.

ADC12DJxx00s use a high-speed JESD204B output interface with up to 16 serialized lanes and support subclass-1 for deterministic latency and multi-device synchronization. The serial output lanes support up to 12.8 Gbps and can be configured to trade off bit rate versus number of lanes. In dual-channel mode, optional digital-down converters can tune and decimate a band from RF to a complex baseband signal to reduce the interface data rate in bandwidth-limited applications.

### 2.2.2 LMK04828

The LMK0482x family is the industry's highest-performance clock conditioner with JEDEC JESD204B support. The 14 clock outputs from PLL2 can be configured to drive seven JESD204B converters or other logic devices using device and SYSREF clocks. SYSREF can be provided using both DC and AC coupling. This device is available in a 64-pin QFN package (9 mm × 9 mm).

### 2.2.3 LMX2582

4

The LMX2582 is a low-noise, wideband RF phase-locked loop (PLL) with integrated VCO that supports a frequency range from 20 MHz to 5.5 GHz. The device supports both fractional-N and integer-N modes with a 32-bit fractional divider allowing fine frequency selection. Integrated noise of 47 fs for a 1.8-GHz output allows for an ideal low-noise source. The device is available in a 40-pin WQFN (6 mm × 6 mm).

### 3 System Design Theory

### 3.1 Clocking

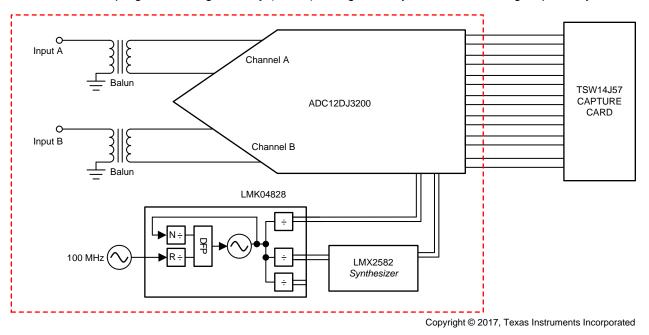

Figure 2 shows a block diagram of the clocking subsystem, which comprises an LMK04828 JESD204B clock conditioner, LMX2582 synthesizer, 100-MHz voltage-controlled crystal oscillator (VCXO), ADC, and LMK SMA clock inputs. The two main ways to clock the ADC are onboard clocking and external clocking.

### **Onboard clocking:**

By default, the ADC12DJ3200EVM is set up to use onboard clocking. When using the default onboard clocking option for the ADC EVM, the LMX2582 is used as a clock source for the ADC and LMK04828 is used for providing the SYSREF for the ADC and the FPGA, in addition to being used for clocking the FPGA. The VCXO is used as a reference for both LMK04828 and LMX2582. In this mode, there is an option to lock the VCXO to an external source by providing a 10-MHz reference clock to connector J38.

### External clocking:

If external clocking is desired, the clock from the external signal generator is provided to the ADC EXT CLK (J18) input connector and LMK EXT CLK (J22) connector. The LMK04828 device is used to provide the SYSREF and CLK to the FPGA as well as the SYSREF to ADC. In external clock mode, the LMX2582 is powered down. When using external clocking mode, C49 and C52 must be installed and C48, C50, C51, and C53 must be uninstalled.

Figure 2. Clocking

5

### System Design Theory

### 3.2 Power

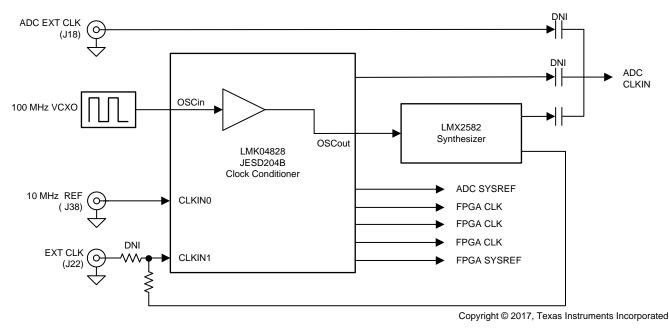

This ADC12DJ3200EVM operates from a single +5-V power supply, which powers a combination of switching and linear regulators that are used to power the various domains on the board. Figure 3 shows a block diagram of the power management.

Figure 3. Power Management Block Diagram

#### 4 **Getting Started Hardware and Software**

#### 4.1 **Required Hardware**

The required hardware for the TIDA-01442 design is as follows:

- ADC12DJ3200 EVM

- TSW14J57 EVM

- Signal generator

#### 4.1.1 ADC12DJ3200

See the ADC12DJ3200EVM tool folder at http://www.ti.com/tool/ADC12DJ3200EVM for a detailed description.

#### 4.1.2 **TSW14J57**

See the TSW14J57 EVM tool folder at http://www.ti.com/tool/tsw14j57evm for a detailed description.

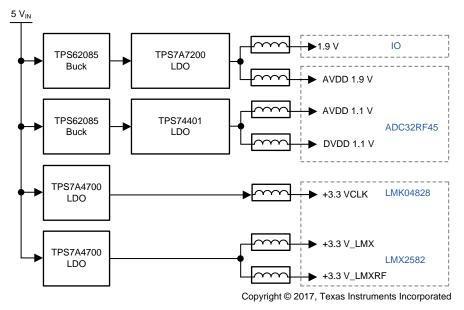

#### 4.1.3 **Test Setup**

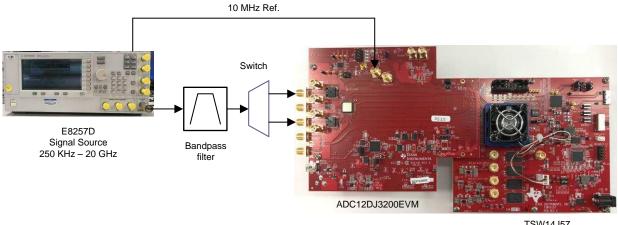

The performance measurements of the ADC were taken using the setup shown in Figure 4. In the setup, a 3.2-GHz clock signal generated by LMX2582 (onboard) is sent to the ADC and LMK04828 (onboard). The LMK04828 is a JESD204B-compliant clock jitter cleaner and is used to provide the SYSREF signals and other required clock signals to the ADC and TSW14J57. The input signal for the ADC is provided by the Agilent Technologies E8257D signal source. The input signal is filtered using a tunable band-pass filter and applied at the channel A or channel B input of the ADC. The input signal and clock are synchronized to each other by feeding a 10-MHz reference signal from the signal source to the LMK04828 device. The ADC12DJ3200 EVM is connected to the TSW14J57 capture card to capture the output digital data of the ADC. The captured data is processed using the High Speed Data Converter (HSDC) Pro software. Both boards are powered by +5-V supplies (through barrel connectors) and connect to a PC through USB cables.

TSW14J57

7

Copyright © 2017, Texas Instruments Incorporated

Figure 4. Test Setup Diagram

### 4.2 Software

### 4.2.1 ADC12DJ3200 GUI

The ADC12DJ3200EVM board must be configured through the ADC12DJ3200 GUI before conversions can be captured. After launching the GUI, the first step is to select the *On-board* option using the drop-down menu under the *#1. Clock Source* field. Then set the clocking frequency to *Fclk* = *3200 MHz* using the drop-down menu under the *#2a. On-board Fclk Selection* (see Figure 5). The next step is to select JMODE0 if taking single-channel interleaved measurements or *JMODE3* if taking dual-channel measurements. In single-channel interleaved mode, the input single is applied to the single input channel. In this mode, both the rising edge and falling edge of the FCLK are used to sample the input signal, thus making the effective sampling rate 6.4 GSPS with a 3.2-GHz clock. Alternatively, in dual-channel mode, both the input channels are used with each channel to sample an input signal at 3.2 GSPS with a 3.2-GHz clock. The last step is to click the *Program Clocks and ADC* button and wait for the script to finish execution. This step completes the configuration and then the user can launch and configure the HSDC Pro GUI.

|                               | ADC12DJxx00 GUI            |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

|-------------------------------|----------------------------|------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------------|-----------------------------------|--|--|--|--|

|                               | File Debug Settings Help   |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

|                               | ADC12DJxx00 GUI            |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

|                               | EVM                        | Control                            | JESD204B                                       | NCO Configuration                                                                                                                                                                         | Trim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LMK04828 | LMX2582 | Low Level View | USB 🥥 🗇 Reconnect?                |  |  |  |  |

|                               | 1. User Inputs START HERE! |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

|                               | #1. Cl                     | ock Source<br>On-bo                | ard $ ard$                                     |                                                                                                                                                                                           | This tab is used to control the EVM to program the clocks, basic mode of the ADC, and read the temperature. Once the EVM is<br>programmed, the other tabs allow the user to configure the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |         |                |                                   |  |  |  |  |

|                               | #2b. E<br>1000<br>#3. D    | ecimation a<br>JMOE                | 00 MHz<br>Selection<br>MHz<br>nd Serial Data M | <ul> <li>#1. Clock Sourt<br/>is selected, cht<br/>#2a. On-board<br/>DEVCLK, as with<br/>#2b. External Fi<br/>Wars Guide for<br/>#3. Decimation<br/>#4. Program Cl<br/>and ADC.</li> </ul> | 1. User Inputs - How to program the EVM clocks and ADC: #1. Clock Source - the DEVCLK to the ADC may be supplied by the on-board PLL/VCO or externally by the user. If the on-board clock is selected, choose the Fs at #2a. If the external clock is selected, enter the Fs at #2b. #2a. On-board Fclk Selection - The PLL/VCO will be programmed to provide any of the available sampling clock frequencies to the DEVCLK, as well as provide the clock for distribution via the LMK04828 for the JESD204B clocks. #2b. External Fclk Selection - The user must enter the external Fclk supplied (in MHz). The PLL/VCO will be provered down; see the Users Guide for details regarding external clocks required. #3. Decimation and Serial Data Mode - Choose the decimation mode and serial data mode for the ADC. #4. Program Clocks and ADC - once all modes have been selected, press this button to write selections to the PLL/VCO, LMK04828, |          |         |                |                                   |  |  |  |  |

|                               | 2. Temp                    | Sensor:                            |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

| THE REAL PROPERTY AND INCOME. | ADC 1<br>0<br>LM95<br>0    | degrees<br>233 Local Te<br>degrees | mp                                             |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

| -                             | Idle                       |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         | HARDWAR        | e connected 🛛 🐇 Texas Instruments |  |  |  |  |

|                               |                            |                                    |                                                |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |                |                                   |  |  |  |  |

Figure 5. ADC12DJ3200 GUI—Quick Setup

### 4.2.2 HSDC Pro GUI

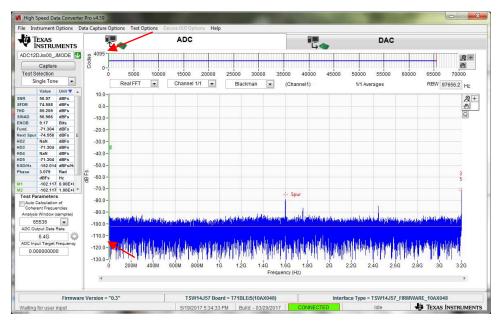

HSDCpro GUI works with a TSW14J57 capture card and is used to process and display data captured from the ADC12DJ3200. Download the HSDC Pro software from http://www.ti.com/tool/dataconverterprosw. As Figure 6 shows, click on the drop-down menu and select "ADC32RF45\_LMF\_82820". Next set the *ADC Output Data Rate* to "6.4G" for single-channel interleaved mode and "3.2G" for dual-channel mode. The HSDC Pro software is now configured and data can be captured by clicking the *Capture* button.

Getting Started Hardware and Software

Figure 6. HSDC Pro GUI—Configuring Device and Sample Rate

Figure 6 also shows the fast Fourier transform (FFT) of captured data from the ADC12DJ3200EVM board. The HSDC Pro software provides a time domain and frequency domain analysis. The HSDC Pro software also provides single-tone FFT statistic parameters such as signal-to-noise ratio (SNR), spurious free dynamic range (SFDR), total harmonic distortion (THD), signal-to-noise and distortion ratio (SINAD), effective number of bits (ENOB), fundamental tone power, and HD2-5.

#### 5 **Testing and Results**

A variety of measurements were taken to demonstrate the performance of ADC12DJ3200EVM board. A clean, filtered signal was fed into the ADC12DJ3200EVM board to test the performance and the SNR, HD2, HD3, and other various parameters were measured. The measurements were performed for both the single-channel interleaved mode (6.4 GSPS) and dual-channel mode (3.2 GSPS for each channel). JMODE0 was used for the single-channel interleaved mode. In JMODE0, the digital data from the ADC is sent to the capture card (FPGA) over eight serializer/deserialzer (SerDes) lanes with a lane rate of 12.8 Gbps. JMODE3 was used for dual-channel measurements. In JMODE3, the digital data from the ADC is sent to the FPGA over 16 SerDes lanes with half the lane rate of JMODE0, which is 6.4 Gbps.

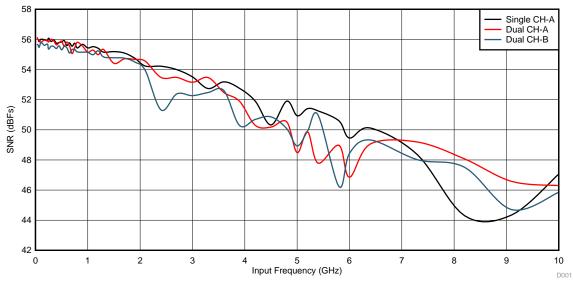

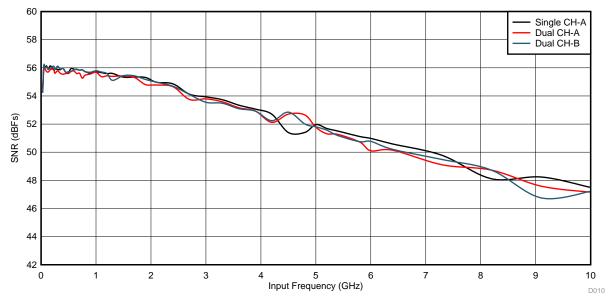

Figure 7 shows the SNR performance with a -1-dBFs input signal swept from 30 MHz to 10 GHz. The input signal was applied to channel A for single-channel interleaved mode. The input signal was applied to both channel A and channel B for dual-channel input measurement.

Figure 7. SNR for Interleaved Single- and Dual-Channel Modes

80 Single CH-A Dual CH-A 75 Dual CH-B 70 65 THD (dBFs) 60 55 50 45 40 35 1 2 3 7 8 0 4 5 6 9 10 Input Frequency (GHz) D002

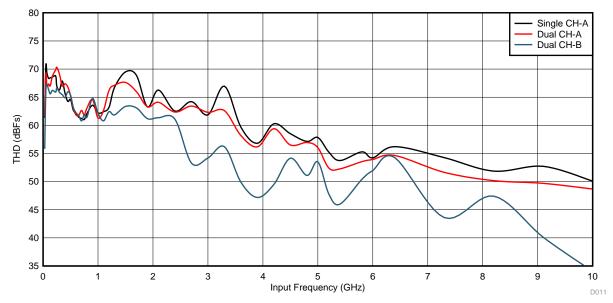

Figure 8 shows the THD for both single-channel interleaved mode and dual-channel mode.

Figure 8. THD Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

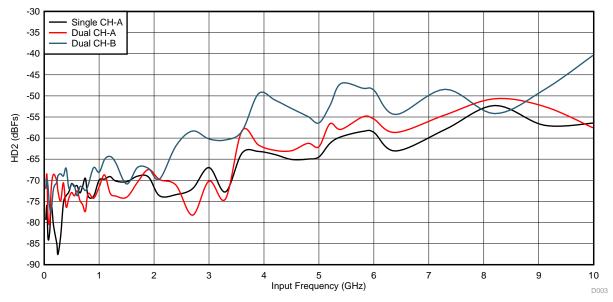

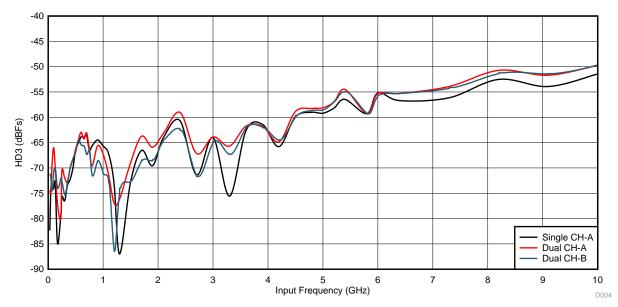

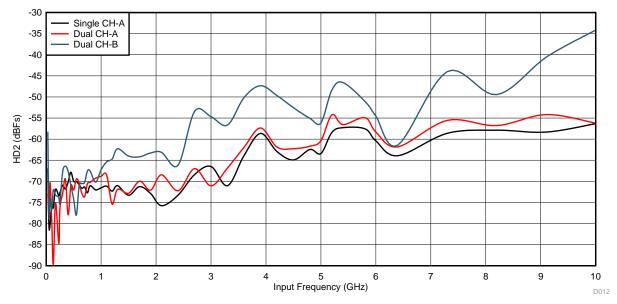

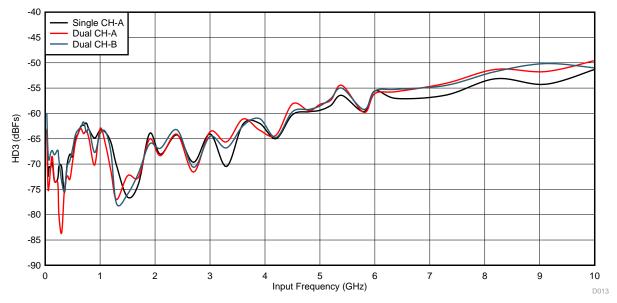

Figure 9 and Figure 10 show the HD2 and HD3 performance for both single-channel interleaved mode and dual-channel mode.

Figure 9. HD2 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 10. HD3 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

### Testing and Results

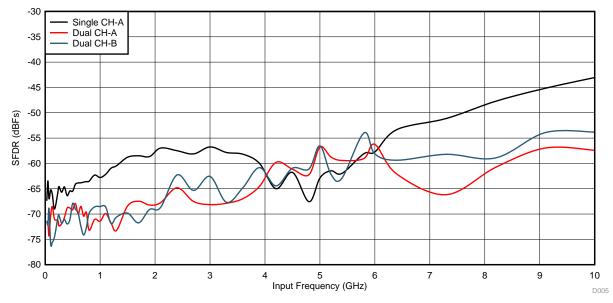

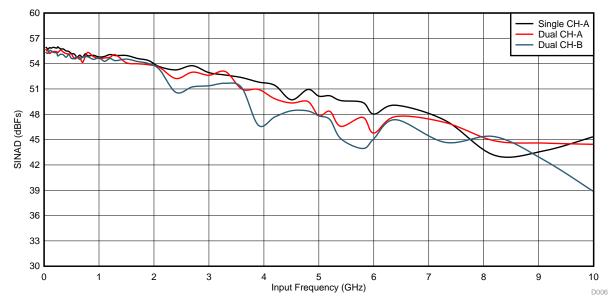

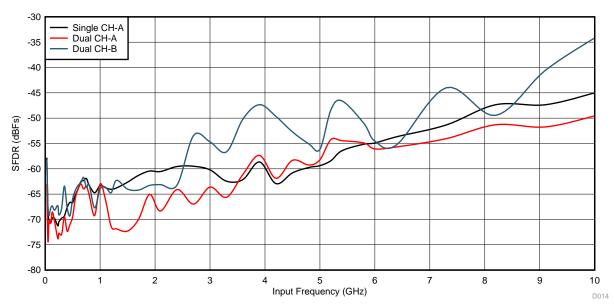

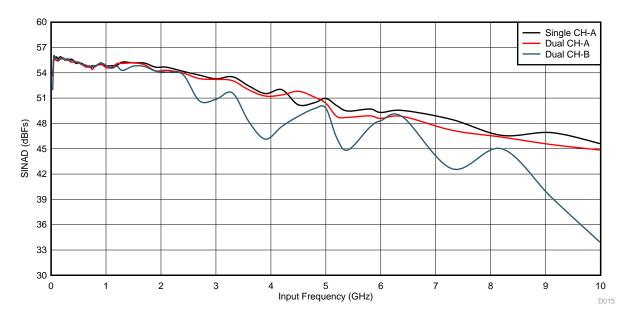

Figure 11 and Figure 12 show the SFDR and SINAD performance for both single-channel interleaved mode and dual-channel mode.

Figure 11. SFDR Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 12. SINAD Performance for Single-Channel Interleaved Mode and Dual-channel Code

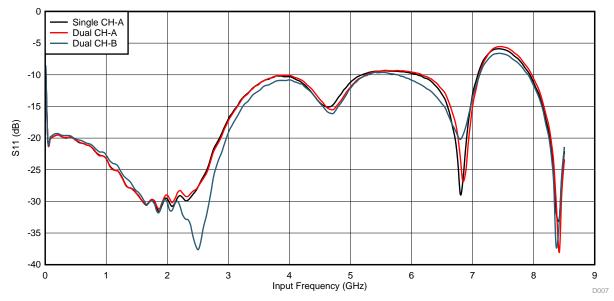

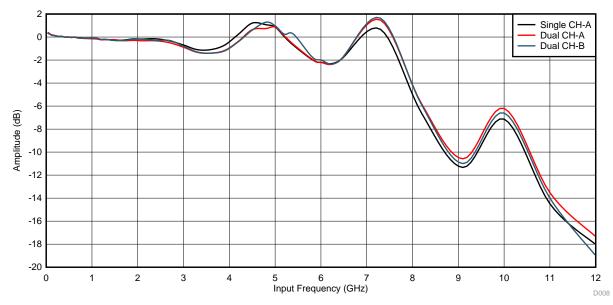

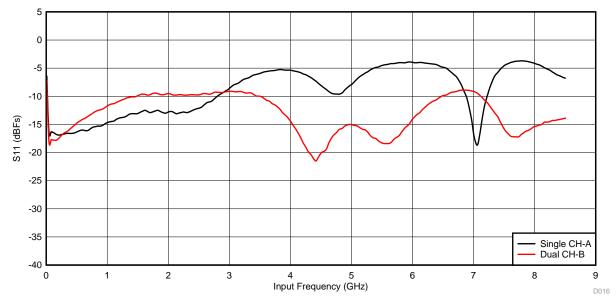

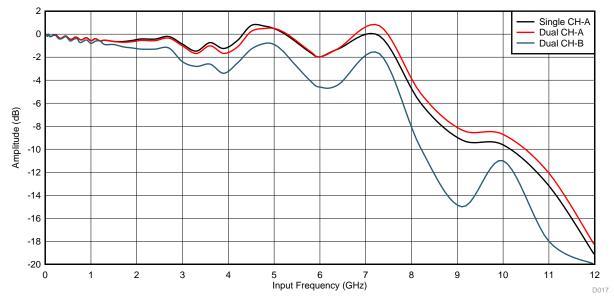

Figure 13 and Figure 14 show the S11 and frequency response performance for both single-channel interleaved mode and dual-channel mode.

Figure 13. S11 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 14. Frequency Response for Single-Channel Interleaved Mode and Dual-Channel Mode

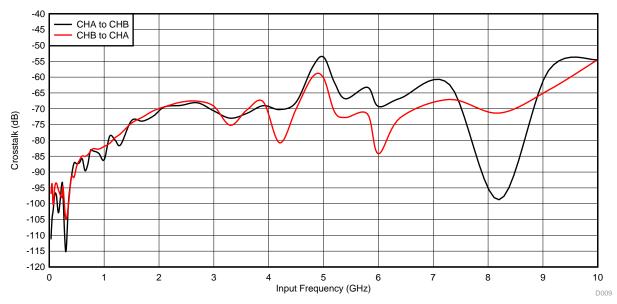

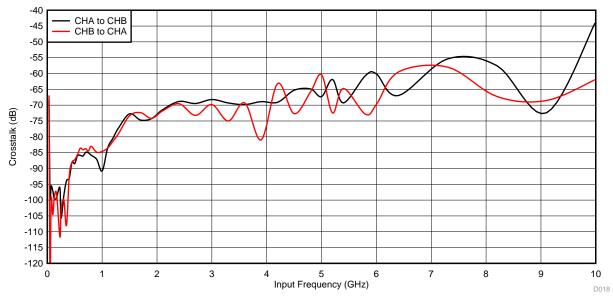

Figure 15 shows the channel-to-channel isolation performance for dual-channel mode.

Figure 15. Crosstalk Performance in Dual-Channel Mode for Channel A and Channel B

The board was modified by replacing both the input baluns with BALH-0009SMG. This balun has a better performance at higher frequencies.

Figure 16. SNR for Interleaved Single-Channel and Dual-Channel Mode

Figure 17 shows the THD for both single-channel interleaved mode and dual-channel mode.

Figure 17. THD Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 18 and Figure 19 show the HD2 and HD3 performance for both single-channel interleaved mode and dual-channel mode.

Figure 18. HD2 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 19. HD3 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 20 and Figure 21 show the SFDR and SINAD performance for both single-channel interleaved mode and dual-channel mode.

Figure 20. SFDR Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 21. SINAD Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 22 and Figure 23 show the S11 and frequency response performance for both single-channel interleaved mode and dual-channel mode.

Figure 22. S11 Performance for Single-Channel Interleaved Mode and Dual-Channel Mode

Texas

www.ti.com

TRUMENTS

Figure 23. Frequency Response for Single-Channel Interleaved Mode and Dual-Channel Mode

Figure 24 shows the channel-to-channel isolation performance for dual-channel mode.

Figure 24. Crosstalk Performance in Dual-Channel Mode for Channel A and Channel B

### 6 Design Files

### 6.1 Schematics

To download the schematics, see the design files at TIDA-01442.

### 6.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01442.

### 6.3 PCB Layout Recommendations

### 6.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01442.

### 6.4 PCB Project

To download the Altium project files, see the design files at TIDA-01442.

### 6.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01442.

### 6.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01442.

### 7 Software Files

To download the software files, see the design files at TIDA-01442.

### 8 Trademarks

All trademarks are the property of their respective owners.

### 9 About the Author

**NEERAJ GILL** is an application engineer in high-speed catalog converters group at Texas Instruments. Gill received his BSEE from University of New Hampshire in 2011 and then his Masters in Electrical Engineering also from University of New Hampshire in 2013.

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated