# TI Designs: TIDA-01510 Two-Sided Layout Reference Design to Increase Power Density With DC/DC Converters

# **TEXAS INSTRUMENTS**

# Description

This reference design demonstrates the correct way to design a two-sided DC/DC layout in an effort to achieve higher power-supply density. The design guide highlights common mistakes and how to avoid them, along with test results showing that proper implemenation of the TPS54824 device in a two-sided layout does not hinder performance. If the 8-A output of the TPS54824 buck converter is too much, this design can also use the TPS54424 device, a 4-A, pinto-pin compatible alternative.

This solution is ideal for powering noise sensitive data converter systems such as communications equipment, medical, test and measurement, and avionics applications that benefit from board space savings.

## Resources

| TIDA-01510 |

|------------|

| TPS54824   |

| TPS54424   |

| WEBENCH®   |

Design Folder Product Folder

### **Features**

- Input range: 4.5 V to 17 V, 1.8  $V_{OUT}$  at 8-A  $I_{OUT}$

- Peak efficiency: 94.7% at 5 V <sub>IN</sub>, 2-A I<sub>OUT</sub>

- Load regulation:  $< \pm 0.04\%$

- Switching frequency: 700 kHz

- Total solution size: 280 mm<sup>2</sup>

### Applications

- Medical Ultrasound Scanners

- Semiconductor Test Equipment

- Small Cell Base Station •

- Massive MIMO (Active Antenna Systems)

- Macro Remote Radio Unit (RRU)

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

1

2

#### 1 System Description

A small footprint, fixed frequency, high efficiency, and low cost are all key factors needed in power solutions for telecom, datacom, and industrial systems. This reference design focuses on creating a small form-factor while maintaining peak performance. More and more systems are being densely packed onto printed-circuit boards (PCB). A recent necessity is to have components on both sides of the PCB. Some examples of end-equipments benefitting from this are 4G and 5G remote radio units in wireless infrastructure and bench-top test equipment such as oscilloscopes or portable ultrasound equipment. However, many engineers are skeptical of separating a power design to both sides of the board due to the probable performance degradation.

This reference design guide covers the steps to properly design a two-sided layout and includes measurement results of the TPS54824 device implemented in a two-sided and one-sided layout to illustrate the small performance differences between the two options.

#### 1.1 **Key System Specifications**

Table 1 lists the key system specifications.

| PARAMETER                                                 | VALUE                 |

|-----------------------------------------------------------|-----------------------|

| Output ripple                                             | < 20 mV               |

| Efficiency (at 12 V <sub>IN</sub> / 8 A <sub>LOAD</sub> ) | 88%                   |

| Load transient                                            | < 5% V <sub>OUT</sub> |

| Load regulation                                           | ±0.04%                |

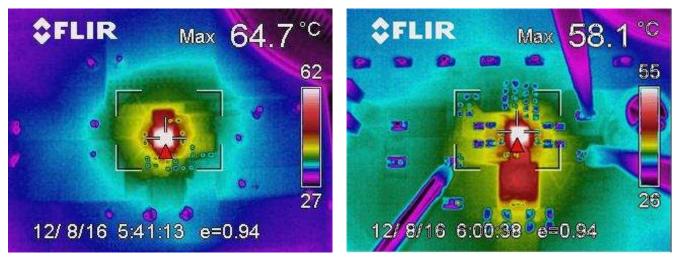

| Temperature (max load)                                    | 64.7°C                |

| Switch node overshoot                                     | 3.59 V                |

### **Table 1. Key System Specifications**

# 2 System Overview

# 2.1 Block Diagram

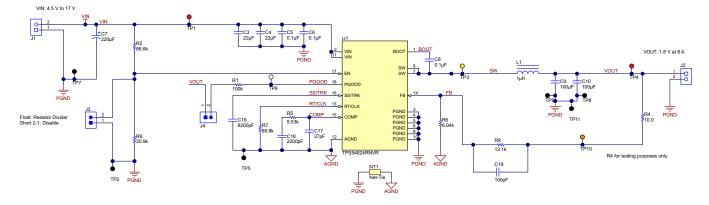

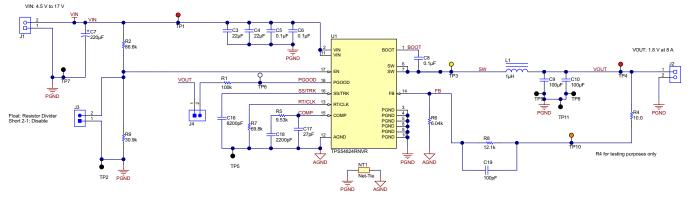

Figure 1 illustrates the TIDA-01510 block diagram.

Figure 1. TIDA-01510 Block Diagram

# 2.2 Highlighted Products

# 2.2.1 TPS54824

The TPS54824 device is a full featured 17-V, 8-A synchronous, step-down converter in a 3.5-mm × 3.5mm HotRod<sup>™</sup> QFN package. The device is optimized for a small solution size through high efficiency and integrating the high-side and low-side MOSFETs. Further space savings are achieved through peak current mode control, which reduces component count, and by selecting a high switching frequency, reducing the inductor footprint.

# 2.3 System Design Theory

Often the recommended layout places most, if not all, components on one side of the PCB. Some applications that are space constrained or require the highest power density have to place components on the top and bottom side of the PCB. This section provides recommendations on how to do a two-sided layout.

3

4

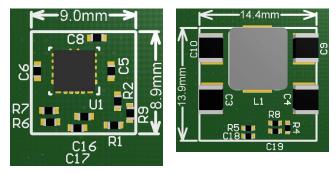

### 2.3.1 Component Placement

When designing a two-sided layout, first consider the placement of the input capacitors, inductor, and output capacitors.

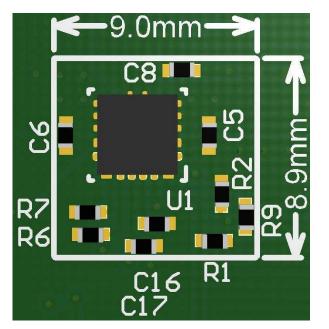

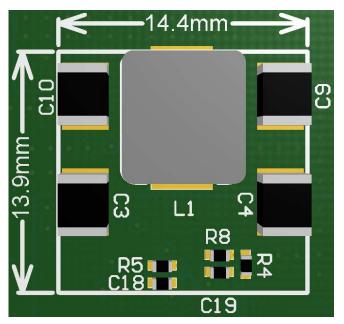

Figure 2. Bottom-Side Solution Dimensions

Figure 3. Top-Side Solution Dimensions

The larger-sized input capacitors with a 1210 package and with a larger value (C3 and C4) are placed on the top side. The IC is placed on the bottom side, and it is important to still include some bypass capacitance as close as possible to the IC. Therefore, the high-frequency bypass capacitors (C5 and C6) are placed as close as possible to the two VIN pins of the TPS54824. Use as many vias as possible between the IC and the input capacitors to reduce parasitic inductance.

The inductor is placed on the top side, opposite of the TPS54824. Placing the inductor on the opposite side is acceptable because any parasitic inductance between it and the IC is very small compared to the inductance of the inductor. For best performance, it is important to maximize the number of vias between the IC and the inductor to reduce parasitic inductance and resistance.

The output capacitors are also placed on the top-side because they are in a larger-sized 1210 package. They are placed with their connection to ground as close as possible to the ground of the input capacitors. The larger-sized components are purposely placed on the top side because it is typically the side allowing components with greater height.

Next, complete the placement of the components connected to the analog control circuits. It is important to try to place the components connected to the RT/CLK, FB, COMP, and SS/TRK pins on the same side as the IC with a short return path to AGND. There are two exceptions. R5 and C18 connected to the COMP pin are on the top side; this connection is acceptable because C17 provides bypass for the COMP pin. R8 and C19 connected to the FB pin are on the top side and this is acceptable because the size of the FB node is still kept very small. The trace from the FB divider is kept away from signals that generate noise and is connected to the output at the point of regulation. Lastly, AGND is connected to PGND outside of the critical switching loop to minimize switching noise in the control loop.

#### 3 Hardware, Testing Requirements, and Test Results

#### 3.1 **Required Hardware**

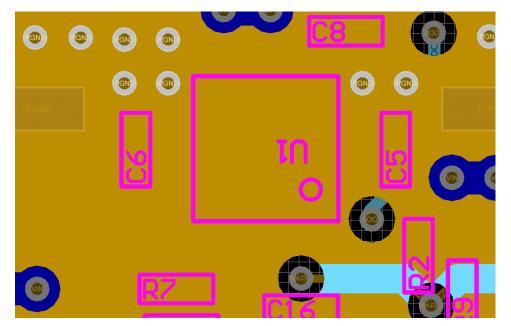

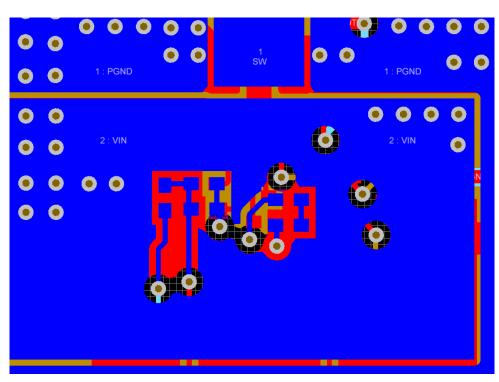

Figure 4 and Figure 5 illustrate the top and bottom of the TIDA-01510, respectively.

Figure 4. TIDA-01510 Board Top

Figure 5. TIDA-01510 Board Bottom

TPS54824 2-sided

#### 3.2 Testing and Results

For the following tests, a TPS54824 EVM is modified to have the same LC filter with the exact components from the reference design board. This modification highlights that when done right, a twosided layout does not have any performance degradation compared to a one-sided layout.

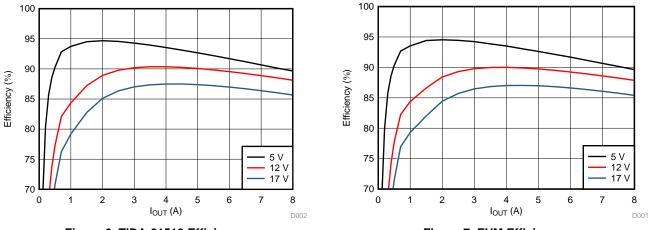

#### 3.2.1 Efficiency and Power Loss

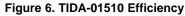

Efficiency data is taken from the design board and from the modified TPS54824 EVM to compare. Figure 6 and Figure 7 show the efficiency data for the reference design and EVM, respectively, at three different input voltages.

Figure 7. EVM Efficiency

5

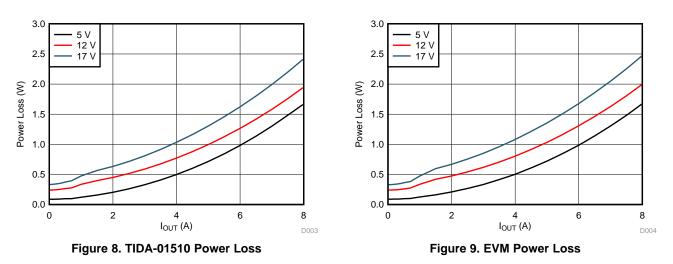

Power loss is also graphed for both boards to represent the amount of power being lost at different loads. The data is gathered at the same three input voltages as the efficiency testing. Figure 8 shows the power loss for the reference design from a 0-A to 8-A load. Figure 9 shows the power loss of the EVM with the same parameters.

From these graphs, the efficiency and power loss is not affected when using a well-designed, two-sided layout versus a one-sided layout.

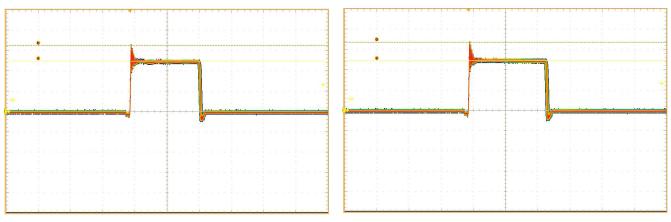

## 3.2.2 Switch Node

Because the switch node is now going through the board for the TIDA-01510 board, the switching waveform is observed to compare performance with the TPS54824 EVM to verify if there is any negative impact from the vias. The waveforms are captured at 12-V input, 1.8-V output, and with a 4-A load. The oscilloscope is set to 5 V/div at 500 MHz for the vertical scale and 100 ns/div at 1 Gsps for the horizontal scale. Figure 10 and Figure 11 show the switching waveforms of the TIDA-01510 board and EVM, respectively.

Figure 10. TIDA-01510 Switch Node Waveform

Figure 11. EVM Switch Node Waveform

Both boards have ringing on the switch node with a peak voltage of roughly 16.5 V. Both switch nodes are nearly identical with less than 0.5 V difference in their peak amplitudes. This value concludes that the added inductance of the vias on the two-sided layout have a negligible impact on the ringing versus the one-sided layout. This inductance results in no issues with additional EMI or stress on the MOSFET.

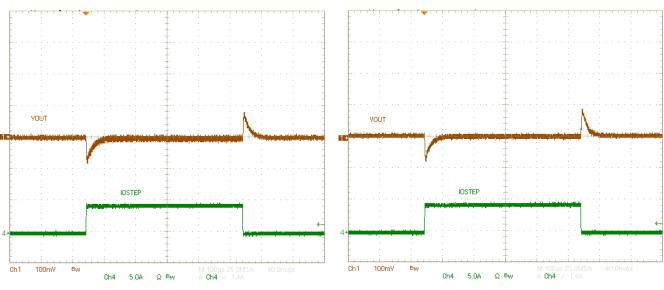

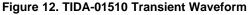

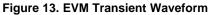

## 3.2.3 Load Transient

This section gathers data accumulated from a load transient test to verify that the response to load transients is not affected when using the two-sided layout. The parameters of this test are as follows:

12-V input

6

1.8-V output

Hardware, Testing Requirements, and Test Results

• 4-A load step from 0 A to 4 A with a slew rate of 10 A/µs

Figure 12 and Figure 13 show the load transient results of this reference design and the EVM, respectively.

Both the reference design and the EVM have an output deviation of less than 5% during the load step, and the transient response waveforms are identical. Therefore, the transient response is not affected going from a one-sided layout to a properly designed two-sided layout.

# 3.2.4 Thermal Performance

Thermal data is gathered for both the reference design and the TPS54824 EVM to see the difference in performance. This test is run at room temperature and no air flow with a 10-minute thermal soak period. The input is set to 12 V and the output is set to 1.8 V with an 8-A load. Figure 14 and Figure 15 show the temperatures of the IC and the inductor, respectively.

Figure 14. TIDA-01510 IC Thermal Readout

Figure 15. EVM IC Thermal Readout

These images show that the reference design suffers in thermal performance compared to the EVM. However, with roughly a 6° difference, the trade-off for having a smaller solution size is reasonable. The designer must decide because this choice limits the use of the device at higher ambient temperatures.

**Design Files**

#### 4 **Design Files**

#### 4.1 **Schematics**

To download the schematics, see the design files at TIDA-01510.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01510.

#### 4.3 PCB Layout Recommendations

Take special care when creating a layout for a two-sided DC/DC design. This section provides insight for a few issues that could potentially be encountered with the layout.

When putting components on both sides of the board, the via count will be high. Do not let these vias affect the integrity of the ground plane. Figure 16 shows the ground plane under the TPS54824 device.

Figure 16. Ground Plane Layout

Notice how the ground plane is completely solid with no cutouts between the PGND pins, which are located on each side of the device near C5 and C6. This is necessary to reduce the impedance between the PGND pins. These vias can also affect the input of the device. Figure 17 shows a VIN plane that connects to the input capacitors and uses vias to connect to both input pins of the device.

Copyright © 2018, Texas Instruments Incorporated

Figure 17. VIN Plane Layout

Keep the connection between the two VIN pins as solid as possible. With all the vias and passive components, the VIN plane can be easily cut up. Even so, this design still has enough copper left to provide a wide, short, and direct current path between the two VIN pins without adding any unwanted resistance.

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01510.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01510.

# 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01510.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01510.

## 5 Trademarks

E2E, HotRod are trademarks of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

## 6 About the Authors

**ANTHONY FAGNANI** is an applications engineer at Texas Instruments, where he supports DC/DC power converter products. Anthony earned his BSEE from Clarkson University.

**DYLAN HUBBARD** is an applications engineer at Texas Instruments, where he is responsible for Standard Logic product support. Dylan obtained his bachelor's degree in electronic systems engineering technology (ESET) from Texas A&M University.

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | nanges from Original (May 2018) to A Revision | Page | Э |

|----|-----------------------------------------------|------|---|

| •  | Added second paragraph to Description         | 1    | 1 |

| •  | Changed list of Applications                  | 1    | 1 |

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated