# SEE Sensitivities of Selected Advanced Flash and First-In-First-Out Memories

R. Koga, V. Tran, J. George, K. Crawford, S. Crain, M. Zakrzewski, and P. Yu The Aerospace Corporation, El Segundo, CA 90245

*Abstract*—Single event effects sensitivity measurements of advanced flash and first-in-first-out memories have been made. While many upsets are transients, other upsets initiated by high LET ions are semi-permanent.

Keywords-single event effects; first-in-first-out memory; flash memory

# INTRODUCTION

Memory devices considered for use in space vehicles include SRAMs (static random access memories) and SDRAMs (synchronous dynamic random access memories) as well as FIFO (first-in-first-out) and flash memories. Single event effects (SEE) test results of FIFO (mostly 4K x 9 devices), which were reported within the last several years, will be compared with those that we obtained more recently [1,2,3]. The FIFO test devices included in our SEE investigations are shown in Table 1. Results of flash memories (manufactured by Aeroflex, Intel, etc), which were reported within the last several years, show sensitivities to various types of SEE [4,5,6]. These sensitivities will be compared with SEE results that we obtained using RC28F640C3BC (64 Mb) and RC28F320C3BC (32 Mb) flash memories.

## TEST DEVICES

Microcircuits such as FIFO and flash memories are made up of both memory and complex control sections. Our test samples are COTS (commercial-off-the-shelf) devices that are presently available. Most of these devices incorporate the CMOS (complementary metal-oxide-semiconductor) technology.

## *A. First-in-first–out Memories*

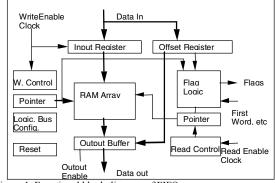

Samples considered for testing are shown in Table 1. Many of these are capable of operating up to about 160 MHz clock rate. These may be compared to some FIFOs (mostly 4K x 9 devices) which were tested within the last several years [1,2,3]. A FIFO is made up of various sections in the die as shown in Figure 1. It has been expected that upsets may occur at various sections in addition to the memory section. The RAM (random access memory) array in a FIFO is normally made up of 4-T (4-transistor) cells or 6-T cells. Even though the RAM array occupies the largest section in a FIFO die, an SEU (single event upset) in the RAM array may affect a small number of bits. On the other hand, an SEU in the control section such as the read control section, including the byte pointer, may introduce a large number of upset bits (for example through a systematic miss-match in byte pointing while reading).

TABLE 1. SELECTED FIFO TEST DEVICES

| Device ID | Mfr | Memory Org. | Tech. | Bias |

|-----------|-----|-------------|-------|------|

| 72V36110  | IDT | 128k x 36   | CMOS  | 3.3V |

| SN74V3690 | TI  | 32k x 36    | CMOS  | 3.3V |

| FQV36110  | HBA | 128k x 36   | CMOS  | 3.3V |

Figure 1. Functional block diagram of FIFO.

#### B. Flash Memories

The RC28F640C3BC (64 Mb) and RC28F320C3BC (32 Mb) devices belonging to the "3-Volt Advanced + Boot Block Memories (C3)" family are manufactured by Intel [7]. In this family 64 Mb devices have the highest capacity. The feature size is about 0.18 microns for the version C devices in this family. The name of the family appeares to have originated from one of its features, which allows locking/unlocking of any block (There are 63 32-Kword blocks) in the memory array.

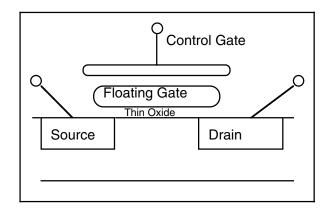

The memory cell is made up of a source, a drain, a floating gate, and a thin oxide below the floating gate as shown in Figure 2 [8,9]. This transistor is a type of the FLOating gate Thin OXide (FLOTOX) cell [8]. A single bit cell may be accessed in random in this so called "NOR flash cell" structure [7]. A cell may be erased by removing the charge (electrons) from the floating gate through the source, which is at a high voltage near +12V, via tunneling. An internal charge pump provides +12 V to the source during the erase operation [7]. The write (or program) operation is accomplished by

introducing +12 V to the control gate (with grounded source), which helps accelerate electrons in the source through the channel toward the floating gate. The internal charge pump is utilized for this operation also. An internal Write State Machine (WSM) automatically executes the timing and algorithms necessary for programming and erasure [7]. Both the erase and write operations require a much longer time than the read timer, which is comparable to that of an SDRAM.

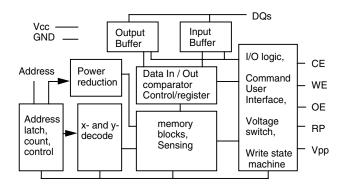

After an erasure, the cell is designed to hold a logic "1" state, while a written (or programmed) cell provides a logic "0" state in this family. In order to accomplish the erase, write, and read operations, a device is made up of various control sections as well as the memory section, as shown in Figure 3.

## TEST METHOD

It has been expected that upsets may occur at various sections in a die in addition to the memory section (see Figures 1 and 3.) Therefore, SEE may encompass single event upset (SEU), single event latchup (SEL), single event transient (SET), and single event functional interrupt (SEFI) [10]. While running the test, the upset rate was kept below about 10 events per second. This made the dead time caused by controlling the device under test negligible compared to the total test time. After a sufficient number of errors had been recorded, the test was stopped and the total fluence of particles and total number of errors were recorded. The device error probability for each type of upset or cross-section,  $\sigma$  is calculated from the expression

$\sigma = (N/F) \sec \theta$

where N and F are the number of errors and beam fluence, respectively, and  $\theta$  is the incident angle of the beam measured with respect to the chip-surface normal. We have used various ion species including protons available at the Lawrence Berkeley Laboratory 88-inch cyclotron. Characteristics of some of these ions are shown in Table 2.

Figure 2. Schematic of a flash memory cell

Figure 3. Functional block diagram of flash memory.

| <u>Ions</u> | <u>AMU</u> | <u>Energy</u><br>(MeV) | <u>LET [MeV/(mg/cm2)]</u> | <u>Range in Si</u><br>(µm) |

|-------------|------------|------------------------|---------------------------|----------------------------|

| В           | 10         | 45                     | 1.5                       | 80                         |

| Ne          | 20         | 90                     | 5.6                       | 50                         |

| Ne          | 20         | 214                    | 3.2                       | 190                        |

| Ar          | 40         | 180                    | 15                        | 45                         |

| Kr          | 86         | 387                    | 41                        | 46                         |

| Xe          | 136        | 1471                   | 53                        | 115                        |

| Bi          | 209        | 950                    | 95                        | 50                         |

# TEST RESULTS

We show test results for FIFO memories followed by those for flash memories.

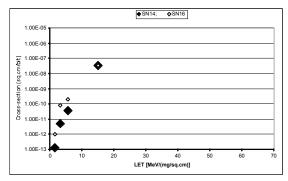

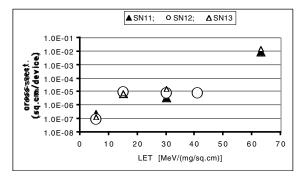

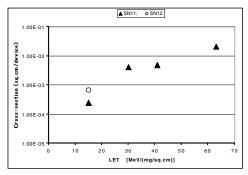

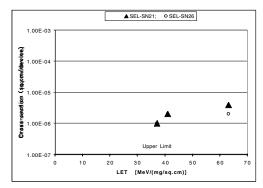

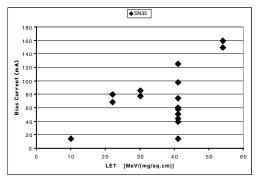

## A. FIFO Memory Sensitivities to SEE

We observed upsets, which most likely occurred in the memory section. These are shown as SEU in Figures 4, 5, and 6 for IDT, TI, and HBA devices, respectively. The saturation cross-section is somewhere between  $1 \times 10^{-7}$  and  $1 \times 10^{-6}$  cm<sup>2</sup>/bit for IDT and TI devices. HBA devices were very sensitive to latchup at high LET regions. Therefore, we could not obtain SEU cross-sections at high LET values. The threshold LET values are relatively low. Most SEUs are of "one-bit error/word" type. However, IDT devices showed some sensitivity to "two-bit error/word" type. Weibull curve fits to heavy ion SEU cross-sections have been made. The coefficients for the two SEU curves are shown in Table 3.

TABLE 3. WEIBULL PARAMETERS FOR TWO SEU TEST SAMPLE TYPES

| Device type | Onset | Power | Width | Limit    |

|-------------|-------|-------|-------|----------|

| IDT         | 1.4   | 1.65  | 25    | 8x 10-7  |

| TI          | 0.99  | 0.85  | 7     | 1 x 10-7 |

Figure 4. SEU results for IDT FIFO.

Figure 6. SEU results for HBA FIFO.

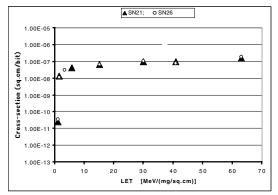

Figure 8. SEL results for IDT FIFO.

Figure 10. Proton induced SEU sensitivity for IDT FIFO. Measured and estimated values are shown.

Figure 5. SEU results for TI FIFO.

Figure 7. SEFI results for IDT FIFO.

Figure 9. SEL results for TI FIFO.

Figure 11. Proton induced SEU sensitivity for TI FIFO. Measured and estimated values are shown.

Figure 12. Proton induced SEU sensitivity for HBA FIFO.

Some devices such as the IDT FIFO are sensitive to SEFI (single event functional interrupt) as shown in Figure 7. Upon encountering SEFI, the device output often shows unusual patterns such as "all 0's" or "all 1's" for consecutive address locations. IDT FIFO showed a relatively high sensitivity to SEL as compared with TI devices as shown in Figures 8 and 9, respectively. The SEL current often exceeded 100 mA.

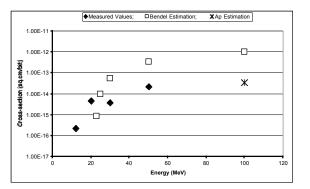

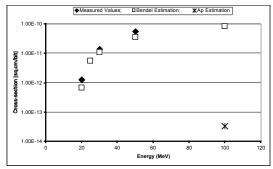

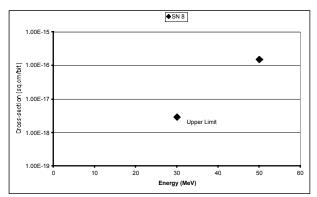

Proton irradiation was carried out at the LBL 88-inch cyclotron soon after heavy ion irradiation. We used 12, 20, 30, and 50 MeV protons. The three device types responded very differently to protons as shown below:

IDT FIFO: The energy threshold for this device type was about 10 MeV as shown in Figure 10. The cross-sections were relatively flat at the energy levels between 20 and 30 MeV. The cross-section increased to 2 x 10<sup>-14</sup> cm<sup>2</sup>/bit at 50 MeV. All upsets appeared to have taken place at memory cell area, since most upsets were isolated errors representing one upset bit per word. In Figure 10 the SEU cross-sections are compared to those which are model dependent estimations derived with the use of an old method (by Petersen [11]) as well as a new method (by Chiba [12]). The latter method provides the saturation cross-section only. We have plotted the estimated saturation cross-section at an arbitrary energy of 100 MeV. The saturation cross-section seems to provide a good agreement for this device type. Both methods attempt to deduce proton crosssections utilizing respective heavy ion results, as briefly described in SUMMARY. The old method yields a crosssection curve with the use of the Bendel model [13]. The curve provides a much larger cross-sections at higher energy values. No SEFI or SEL was observed for this device type with protons.

TI FIFO: The threshold energy of this device type was about 20 MeV as shown in Figure 11. The cross-sections increased to about  $5 \times 10^{-11}$  cm<sup>2</sup>/bit at 50 MeV. Most upsets appeared to have originated in the control section. Once an error emerged at one address location (while we were reading the device), some following address locations showed upsets. The affected locations varied. Also the number of affected locations was not constant. It was as small as a few locations and as many as 10 locations in some cases. In Figure 11 the

SEU cross-sections are compared to those which are model dependent estimations. The derived Bendel curve appears to show a good agreement for this device type. No SEFI or SEL was observed with protons.

HBA FIFO: This device type showed a relatively low sensitivity to protons as shown in Figure 12. We did not detect any sign of upsets at the energy levels of 20 and 30 MeV. The upper limit of the cross-section was about 3 x  $10^{-18}$  cm<sup>2</sup>/bit at 30 MeV. At 50 MeV we observed upsets resulting in an upset cross-section of about 1.5 x  $10^{-16}$  cm<sup>2</sup>/bit. No SEFI or SEL was observed for this device type with protons.

## B. Flash Memory Sensitivities to SEE

Flash memories were programmed to hold a 5555(hex), AAAA(hex), FFFF(hex), or 0000(hex) at each address location during irradiation with heavy ions. Any deviation in the pattern at any location was reported as an error during read operations. All address locations were continuously interrogated starting from 0 to the maximum address location. A write (or program) instruction was used to write over with "0's". If an error were to occur during the write operation, it would be detected during subsequent read operations. An erase instruction was used to "write over" specified address locations (e.g., one entire block) with "1's". If an error were to occur during the erase operation, it would be detected during subsequent read operations. All exposures were carried out while keeping the test device at room temperature. The bias voltage was 3.0 volts.

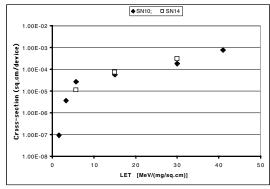

SEU sensitivities during READ operations were measured as shown in Figure 13 for 28F640C3BC. The "saturation crosssections" were about 5 x  $10^{-4}$  cm<sup>2</sup>/device. The threshold (associated with 1 % of the saturation value) LET value was about 4 MeV/(mg/cm<sup>2</sup>). Since these upsets were not "written in the memory", it was expected that they were induced in the readout buffers and/or control sections of the device.

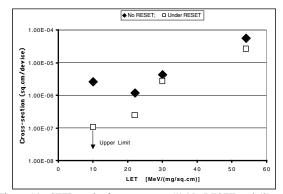

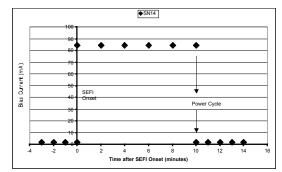

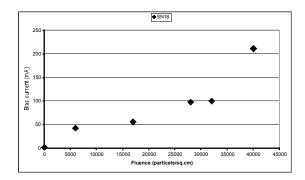

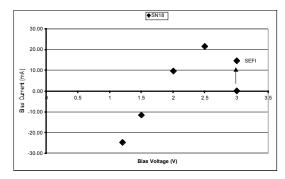

SEFI sensitivities were measured. The SEFI events were expected to have originated from upsets in the control section of the device. As is often the case, some SEFI events were accompanied by an increased bias current (e.g., 30 mA). SEFI cross-sections of 28F640C3s are shown in Figure 14, for two cases of reset conditions. Assertion of reset (during which the device was in the RESET condition) normally reduced the occurrence of SEFIs. The reduction was more pronounced for measurements made at low LET values. SEFI events took place during WRITE (or PROGRAM) and ERASE operations. The cross-sections during these operations were similar to what we observed during READ operations. Test samples were not permanently damaged after SEFI. We kept test samples in the high current condition for an extended time. An example is shown in Figure 15. In each case, a proper application of the power cycle ("off" followed by "on") restored normal operating conditions. The bias current increased with increasing fluence, if the power was not cycled, and multiple occurrences of SEFI appeared to have taken place. These increases are shown in Figure 16 for 28F640C3BC. We used Kr ions (LET of 41) in order to observe these events. It was

expected that multiple SEFI sites in a die were the cause of the raised bias current values.

For low LET values near 10 MeV/(mg/cm<sup>2</sup>), the current increase due to SEFI was limited to below 20 mA as shown in Figure 17 for 28F640C3BC. In this figure all SEFI current values were those associated with the occurrence of the first SEFI (no multiple SEFIs were included.)

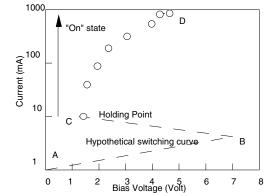

We consider that the current increase due to SEFI is somewhat different from the current increase due to SEL, which is assumed to be caused by an activation of parasitic SCR (silicon controlled rectifier). A typical I-V characteristic of SEL with AT22V10B is shown in Figure 18 [14]. When an SEL takes place, the bias current jumps to about 1 A at 5V. As the bias voltage is reduced, the bias current decreases to the holding point, at which the bias current suddenly returns to a low value and the SEL condition is removed. In Figures 19 we show I-V characteristics associated with a SEFI event for 28F640C3BC. For these devices, (1) the holding points are not well specified, (2) the bias current decrease (in association with reduced bias voltage) is not always monotonic, and (3) the current decrease is not semi-logarithmic.

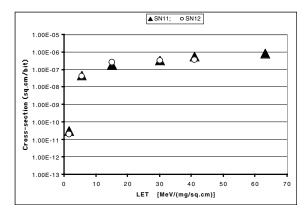

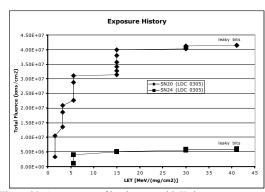

We observed the phenomenon of "leaky bits" (hard errors) in flash memories, that is, bits that appear to lose their stored charge so that they revert to the erased state (a "1" in this device). We saw leaky bits even when the device was not powered during irradiation with ions of a large LET value. We investigated the threshold for these bits by irradiating the devices with low LET ions and progressively increasing the LET of the ions until leaky bits were observed. Two fresh devices were used to investigate the threshold for the leaky bit effect. Each device was irradiated in stages beginning with low-LET ions and progressing to higher LET to see when the leaky bits began. Neither device showed any sign of leaky bits after exposure to a fluence of more than 1.0 X 10<sup>6</sup> ions/cm<sup>2</sup> of ions up to Cu [LET= 30 MeV/(mg/cm<sup>2</sup>)], in several cases more than  $1.0 \ge 10^7$  ions/cm<sup>2</sup> were used. Leaky bits occurred in both devices after exposure to Kr ions [LET= 41 MeV/(mg/cm<sup>2</sup>)]. For one device they appeared at a fluence greater than  $8.4 \times 10^4$ Kr ions/cm<sup>2</sup> (4.7krad integral dose from all ions), for another they were produced at a fluence less than 4.1 x  $10^4$  Kr ions/cm<sup>2</sup> (1krad integral dose) as shown in Figure 20. Conclusions regarding leaky bits: None of the tested devices have shown leaky bits without exposure to Kr ions [LET= 41] MeV/(mg/cm<sup>2</sup>)]. Persistent errors (leaky bits or hard errors) can appear with lower LET ions after a Kr exposure as the total dose accumulates. Once exposed to Kr ions, the onset of leaky bits is highly variable among devices. SEU sensitivity during WRITE and ERASE operations were measured vielding negative results. The upper limit of the cross-section was about  $5 \times 10^{-4} \text{ cm}^2/\text{device}$ .

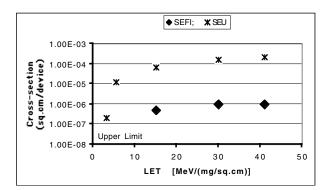

Similar results were observed with 28F320C3BC devices. Examples for SEU and SEFI are shown in Figure 21. SEFI cross-sections in Figure 21 were measured while RESET was not asserted.

Figure 13. SEU results during READ operation.

Figure 14. SEFI results for two cases: (1) No RESET and (2) under RESET conditions.

Figure 15. Onset and recovery (via power cycle) from SEFI.

Figure 16. SEFI bias current increased due to multiple SEFIs. RESET was not asserted. Ions with LET of 41  $MeV/(mg/cm^2)$  were used.

Figure 17. SEFI induced bias current vs. LET. No multiple SEFIs are included.

Figure 18. I-V characteristics for SEL in AT22V10B.

Figure 19. I-V characteristics for SEFI.

Figure 20. Appearance of hard errors with Kr ions.

Figure 21. SEU and SEFI test results for 28F320C3BC during read cycles.

### SUMMARY

Heavy ion induced SEE test results of the three FIFO types showed that TI devices vielded the lowest sensitivities to SEFI as well as to SEL. HBA devices were most sensitive to SEL. Proton induced SEU results for the three devices types (see Figures 10 through 12) are presented. In Figures 10 and 11 the results are shown along with predicted (estimated) values derived from associated heavy ions results. In 1992 Petersen showed that one could obtain the Bendel parameter A via A =  $L_{01}$  + 15, where  $L_{01}$  is the LET value at which the crosssection is 10 % of the saturation value [11]. The Bendel parameter A may be used to show proton induced crosssections at any proton energy [13]. As we can see in Figure 10, this formulation dose not seem to always work properly. For TI devices the formulation seems to work well (see Figure 11). Another method may be used to estimate proton induced saturation cross-sections [12]. They are shown at an arbitrarily chosen energy level of 100 MeV (see Figures 10 and 11.) For IDT FIFO, the derived value seems to fit well. In general SEE sensitivity of present FIFO test samples is similar to that observed with smaller memory devices several years ago [1,2,3]. For example SEU LET<sub>th</sub> is at about 3 MeV/(mg/cm<sup>2</sup>) for Matra 67204EV-50 (4K x 9) FIFO [2].

Various types of SEE were observed with the present flash memory samples. Similar observations with other devices were reported by other investigators [4,5,6]. Since many cross-sections were relatively small (e.g.,  $1 \times 10^{-5}$  cm<sup>2</sup>/device for SEU at LET of 6 in Figure 13), we have used a rather large fluence. After many irradiations, test samples seem to approach the total dose limit [5,6,15,16]. Therefore, it is essential to have a large number of test samples in order to measure various types of SEE cross-sections.

The thickness of the oxide between the floating gate and the channel is about 100 Angstroms in the area where the tunneling takes place [7]. In this region, stored charges may be lost along an ionization track introduced by an incoming ion [15,16]. For the present devices, these ion tracks, produced by ions with a large LET value, seem to leave some "latent damage", if it is not an outright "short circuit". After latent damage has been created, an ion with lower LET value may cause a short across

the floating gate and the channel removing the stored charge in the floating gate.

SEFIs seem to take place in various sections in the present test samples. They emerge during any of READ, WRITE, or ERASE operations as well as in the stand-by condition. The SEFI cross-section is reduced when the device is RESET (and held) during irradiation. Various types of SEFI were reported to have existed in other flash memories manufactured by Aeroflex and Intel [4,5,6].

Testing of present FIFO and flash memories tend to take a longer time than some devices that we tested only several years ago. It is another indication that the complexity of these devices is expanding.

#### ACKNOWLEGEMENT

The authors wish to acknowledge the on-site-staff at the Lawrence Berkeley National Laboratory 88-inch cyclotron facility.

## REFERENCES

- K.A. LaBel, et al., "Single Event Effect Test Results for Candidate Spacecraft Electronics," 1997 NSREC Workshop Record, 14, 1997.

- [2] M.V. O'Bryan, et al., "Single Event and Radiation Damage Results for Candidate Spacecraft Electronics," 1998 NSREC Workshop Record, 39, 1998.

- [3] M.V. O'Bryan, et al., "Recent Radiation Damage and Single Event Effect Results for Microelectronics," 1999 NSREC Workshop Record, 1, 1999.

- [4] H.R. Schwarts, et al., "Single-Event Upset in Flash memories," IEEE Trans. Nuc. Sci., 44, 2315-2324, 1997.

- [5] D.N. Nguyen and L.Z. Scheick, "SEE and TID of emerging Non-volatile memories," IEEE NSREC Workshop Record, 62-66, 2002.

- [6] D.N. Nguyen and L.Z. Scheick, "TID, SEE and radiation induced failures in advanced flash memories," IEEE NSREC Workshop Record, 18-23, 2003.

- [7] Intel Application Note 740, 29228802.pfd, September 2001.

- [8] R. Bez, D. Cantarelli, and P. Cappelletti, "Experimental Transient Analysis of the Tunnel Current in EEPROM Cells," IEEE Trans. Electron Devices, 37, 1081-1086, 1990.

- [9] M. Lanzoni, et al., "Advanced Electrical-Level Modeling of EEPROM Cells," IEEE Trans. Electron Devices, 40, 951-957, 1993.

- [10] R. Koga, et al, "Single event functional interrupt (SEFI) sensitivity in microcircuits," Proceedings of RADECS, 311-318, 1997.

- [11] E.L. Petersen, "The Relationship of Proton and Heavy Ion Upset Thresholds," IEEE Trans. Nucl. Sci., 39, 1600-1604, 1992.

- [12] K. Chiba, et al., "Correlation between Proton and Heavy-ion SEUs in Commercial Memory Devices," IEEE NSREC Workshop Record, 127-132, 2003.

- [13] W.L. Bendel and E.L. Petersen, "Proton Upsets in Orbit," IEEE Trans. Nucl. Sci., 30, 4481-4485, 1983.

- [14] R. Koga, et al., "Ion-induced sustained high current condition in a bipolar device," IEEE Trans Nucl Sci, Vol. 41, pp2172-2179, December 1994.

- [15] G. Cellere, et al., "Charge loss after <sup>60</sup>Co irradiation on flash arrays," Proceedings of RADECS, 2003.

- [16] G. Cellere, et al., "A model for TID effects on floating gate memory cells," IEEE Trans Nucl Sci, Vol. 51, December 2004.