SBAS860 August 2017 ADC31RF80

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 AC Performance Characteristics: fS = 2949.12 MSPS

- 6.7 AC Performance Characteristics: fS = 2457.6 MSPS (Performance Optimized for F + A + D Band)

- 6.8 AC Performance Characteristics: fS = 2457.6 MSPS (Performance Optimized for F + A Band)

- 6.9 Digital Requirements

- 6.10 Timing Requirements

- 6.11 Typical Characteristics

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Analog Inputs

- 8.3.2 Clock Input

- 8.3.3 SYSREF Input

- 8.3.4 DDC Block

- 8.3.5 NCO Switching

- 8.3.6 SerDes Transmitter Interface

- 8.3.7 Eye Diagrams

- 8.3.8 Alarm Outputs: Power Detectors for AGC Support

- 8.3.9 Power-Down Mode

- 8.3.10 ADC Test Pattern

- 8.4

Device Functional Modes

- 8.4.1 Device Configuration

- 8.4.2

JESD204B Interface

- 8.4.2.1 JESD204B Initial Lane Alignment (ILA)

- 8.4.2.2 JESD204B Frame Assembly

- 8.4.2.3 JESD204B Frame Assembly with Decimation (Single-Band DDC): Complex Output

- 8.4.2.4 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

- 8.4.2.5 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

- 8.4.2.6 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Complex Output

- 8.4.2.7 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Real Output

- 8.4.3 Serial Interface

- 8.5

Register Maps

- 8.5.1 Example Register Writes

- 8.5.2

Register Descriptions

- 8.5.2.1

General Registers

- 8.5.2.1.1 Register 000h (address = 000h), General Registers

- 8.5.2.1.2 Register 002h (address = 002h), General Registers

- 8.5.2.1.3 Register 003h (address = 003h), General Registers

- 8.5.2.1.4 Register 004h (address = 004h), General Registers

- 8.5.2.1.5 Register 010h (address = 010h), General Registers

- 8.5.2.1.6 Register 011h (address = 011h), General Registers

- 8.5.2.1.7 Register 012h (address = 012h), General Registers

- 8.5.2.1

General Registers

- 8.5.3

Master Page (M = 0)

- 8.5.3.1 Register 020h (address = 020h), Master Page

- 8.5.3.2 Register 032h (address = 032h), Master Page

- 8.5.3.3 Register 039h (address = 039h), Master Page

- 8.5.3.4 Register 03Ch (address = 03Ch), Master Page

- 8.5.3.5 Register 05Ah (address = 05Ah), Master Page

- 8.5.3.6 Register 03Dh (address = 3Dh), Master Page

- 8.5.3.7 Register 057h (address = 057h), Master Page

- 8.5.3.8 Register 058h (address = 058h), Master Page

- 8.5.4 ADC Page (FFh, M = 0)

- 8.5.5 Digital Function Page (610000h, M = 1)

- 8.5.6 Offset Corr Page (610000h, M = 1)

- 8.5.7 Digital Gain Page (610005h, M = 1)

- 8.5.8

Main Digital Page (680000h, M = 1)

- 8.5.8.1 Register 000h (address = 000h), Main Digital Page

- 8.5.8.2 Register 0A2h (address = 0A2h), Main Digital Page

- 8.5.8.3 Register 0A5h (address = 0A5h), Main Digital Page

- 8.5.8.4 Register 0A9h (address = 0A9h), Main Digital Page

- 8.5.8.5 Register 0B0h (address = 0B0h), Main Digital Page

- 8.5.8.6 Register 0B1h (address = 0B1h), Main Digital Page

- 8.5.8.7 Register 0B2h (address = 0B2h), Main Digital Page

- 8.5.8.8 Register 0B3h (address = 0B3h), Main Digital Page

- 8.5.8.9 Register 0B4h (address = 0B4h), Main Digital Page

- 8.5.8.10 Register 0B5h (address = 0B5h), Main Digital Page

- 8.5.8.11 Register 0B6h (address = 0B6h), Main Digital Page

- 8.5.8.12 Register 0B7h (address = 0B7h), Main Digital Page

- 8.5.8.13 Register 0B8h (address = 0B8h), Main Digital Page

- 8.5.8.14 Register 0B9h (address = 0B9h), Main Digital Page

- 8.5.8.15 Register 0BAh (address = 0BAh), Main Digital Page

- 8.5.8.16 Register 0BBh (address = 0BBh), Main Digital Page

- 8.5.9

JESD Digital Page (6900h, M = 1)

- 8.5.9.1 Register 001h (address = 001h), JESD Digital Page

- 8.5.9.2 Register 002h (address = 002h ), JESD Digital Page

- 8.5.9.3 Register 003h (address = 003h), JESD Digital Page

- 8.5.9.4 Register 004h (address = 004h), JESD Digital Page

- 8.5.9.5 Register 006h (address = 006h), JESD Digital Page

- 8.5.9.6 Register 007h (address = 007h), JESD Digital Page

- 8.5.9.7 Register 016h (address = 016h), JESD Digital Page

- 8.5.9.8 Register 017h (address = 017h), JESD Digital Page

- 8.5.9.9 Register 032h-035h (address = 032h-035h), JESD Digital Page

- 8.5.9.10 Register 036h (address = 036h), JESD Digital Page

- 8.5.9.11 Register 037h (address = 037h), JESD Digital Page

- 8.5.9.12 Register 03Ch (address = 03Ch), JESD Digital Page

- 8.5.9.13 Register 03Eh (address = 03Eh), JESD Digital Page

- 8.5.10

Decimation Filter Page

- 8.5.10.1 Register 000h (address = 000h), Decimation Filter Page

- 8.5.10.2 Register 001h (address = 001h), Decimation Filter Page

- 8.5.10.3 Register 002h (address = 2h), Decimation Filter Page

- 8.5.10.4 Register 005h (address = 005h), Decimation Filter Page

- 8.5.10.5 Register 007h (address = 007h), Decimation Filter Page

- 8.5.10.6 Register 008h (address = 008h), Decimation Filter Page

- 8.5.10.7 Register 009h (address = 009h), Decimation Filter Page

- 8.5.10.8 Register 00Ah (address = 00Ah), Decimation Filter Page

- 8.5.10.9 Register 00Bh (address = 00Bh), Decimation Filter Page

- 8.5.10.10 Register 00Ch (address = 00Ch), Decimation Filter Page

- 8.5.10.11 Register 00Dh (address = 00Dh), Decimation Filter Page

- 8.5.10.12 Register 00Eh (address = 00Eh), Decimation Filter Page

- 8.5.10.13 Register 00Fh (address = 00Fh), Decimation Filter Page

- 8.5.10.14 Register 010h (address = 010h), Decimation Filter Page

- 8.5.10.15 Register 011h (address = 011h), Decimation Filter Page

- 8.5.10.16 Register 014h (address = 014h), Decimation Filter Page

- 8.5.10.17 Register 016h (address = 016h), Decimation Filter Page

- 8.5.10.18 Register 01Eh (address = 01Eh), Decimation Filter Page

- 8.5.10.19 Register 01Fh (address = 01Fh), Decimation Filter Page

- 8.5.10.20 Register 033h-036h (address = 033h-036h), Decimation Filter Page

- 8.5.10.21 Register 037h (address = 037h), Decimation Filter Page

- 8.5.10.22 Register 038h (address = 038h), Decimation Filter Page

- 8.5.10.23 Register 039h (address = 039h), Decimation Filter Page

- 8.5.10.24 Register 03Ah (address = 03Ah), Decimation Filter Page

- 8.5.11

Power Detector Page

- 8.5.11.1 Register 000h (address = 000h), Power Detector Page

- 8.5.11.2 Register 001h-002h (address = 001h-002h), Power Detector Page

- 8.5.11.3 Register 003h (address = 003h), Power Detector Page

- 8.5.11.4 Register 007h-00Ah (address = 007h-00Ah), Power Detector Page

- 8.5.11.5 Register 00Bh-00Ch (address = 00Bh-00Ch), Power Detector Page

- 8.5.11.6 Register 00Dh (address = 00Dh), Power Detector Page

- 8.5.11.7 Register 00Eh (address = 00Eh), Power Detector Page

- 8.5.11.8 Register 00Fh, 010h-012h, and 016h-019h (address = 00Fh, 010h-012h, and 016h-019h), Power Detector Page

- 8.5.11.9 Register 013h-01Ah (address = 013h-01Ah), Power Detector Page

- 8.5.11.10 Register 01Dh-01Eh (address = 01Dh-01Eh), Power Detector Page

- 8.5.11.11 Register 020h (address = 020h), Power Detector Page

- 8.5.11.12 Register 021h (address = 021h), Power Detector Page

- 8.5.11.13 Register 022h-025h (address = 022h-025h), Power Detector Page

- 8.5.11.14 Register 027h (address = 027h), Power Detector Page

- 8.5.11.15 Register 02Bh (address = 02Bh), Power Detector Page

- 8.5.11.16 Register 032h-035h (address = 032h-035h), Power Detector Page

- 8.5.11.17 Register 037h (address = 037h), Power Detector Page

- 8.5.11.18 Register 038h (address = 038h), Power Detector Page

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RMP|72

Thermal pad, mechanical data (Package|Pins)

Orderable Information

11 Layout

11.1 Layout Guidelines

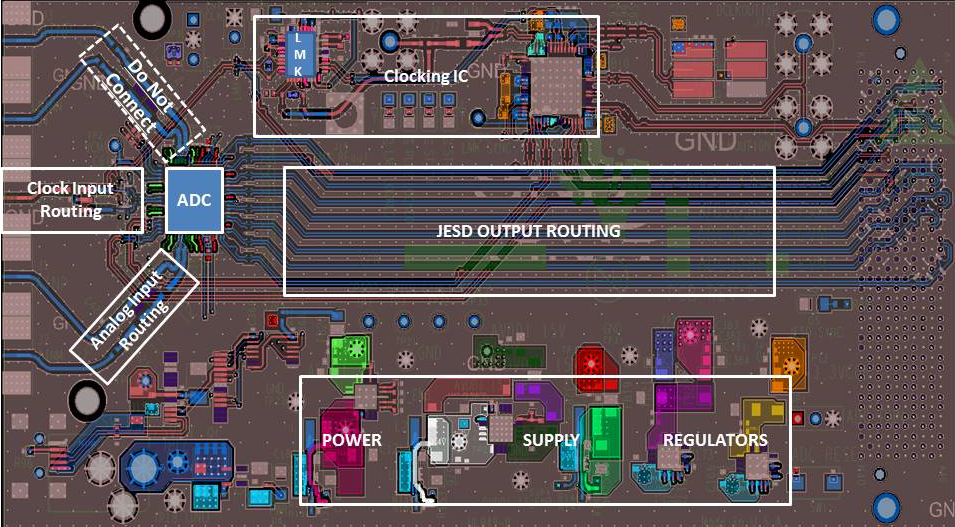

The device evaluation module (EVM) layout can be used as a reference layout to obtain the best performance. A layout diagram of the EVM top layer is provided in Figure 275. The ADC32RF45/RF80 EVM Quick Startup Guide provides a complete layout of the EVM. Some important points to remember during board layout are:

- Analog inputs are located on opposite sides of the device pinout to ensure minimum crosstalk on the package level. To minimize crosstalk onboard, the analog inputs must exit the pinout in opposite directions, as shown in the reference layout of Figure 275 as much as possible.

- In the device pinout, the sampling clock is located on a side perpendicular to the analog inputs in order to minimize coupling. This configuration is also maintained on the reference layout of Figure 275 as much as possible.

- Keep digital outputs away from the analog inputs. When these digital outputs exit the pinout, the digital output traces must not be kept parallel to the analog input traces because this configuration can result in coupling from the digital outputs to the analog inputs and degrade performance. All digital output traces to the receiver [such as field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs)] must be matched in length to avoid skew among outputs.

- At each power-supply pin (AVDD, DVDD, or AVDD19), keep a 0.1-µF decoupling capacitor close to the device. A separate decoupling capacitor group consisting of a parallel combination of 10-µF, 1-µF, and 0.1-µF capacitors can be kept close to the supply source.

11.2 Layout Example

Figure 275 is an example for the dual-channel device, the ADC32RF80, which shares the same pin-out. For the ADC31RF80, the unused channel is not required to be connected to the board and can be left floating.

Figure 275. ADC32RF80EVM Layout

Figure 275. ADC32RF80EVM Layout