DLPS048C March 2015 – June 2019 DLPC150

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics Over Recommended Operating Conditions

- 6.6 Electrical Characteristics

- 6.7 High-Speed Sub-LVDS Electrical Characteristics

- 6.8 Low-Speed SDR Electrical Characteristics

- 6.9 System Oscillators Timing Requirements

- 6.10 Power-Up and Reset Timing Requirements

- 6.11 Parallel Interface Frame Timing Requirements

- 6.12 Parallel Interface General Timing Requirements

- 6.13 Flash Interface Timing Requirements

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1

Layout Guidelines

- 11.1.1 PCB Layout Guidelines For Internal Controller PLL Power

- 11.1.2 DLPC150 Reference Clock

- 11.1.3 General PCB Recommendations

- 11.1.4 General Handling Guidelines for Unused CMOS-Type Pins

- 11.1.5 Maximum Pin-to-Pin, PCB Interconnects Etch Lengths

- 11.1.6 Number of Layer Changes

- 11.1.7 Stubs

- 11.1.8 Terminations

- 11.1.9 Routing Vias

- 11.2 Layout Example

- 11.3 Thermal Considerations

- 11.1

Layout Guidelines

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZEZ|201

Thermal pad, mechanical data (Package|Pins)

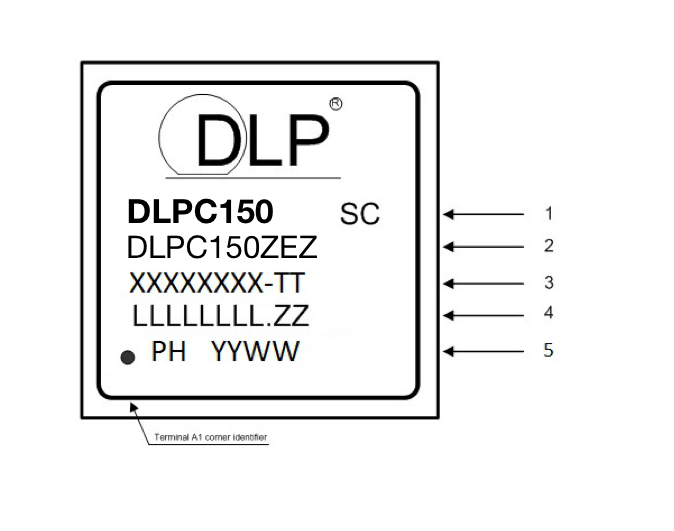

12.1.1.1 Device Markings

| Line 1: | DLP Device Name: DLPC150

SC: Solder ball composition e1: Indicates lead-free solder balls consisting of SnAgCu G8: Indicates lead-free solder balls consisting of tin-silver-copper (SnAgCu) with silver content less than or equal to 1.5% and that the mold compound meets TI's definition of green. |

| Line 2: | TI Part Number

|

| Line 3: | XXXXXXXX-TT manufacturer part number |

| Line 4: | LLLLLLLL.ZZ Foundry lot code for semiconductor wafers and lead-free solder ball marking

|

| Line 5: | PH YYWW: Package assembly information

|