SBOS792A August 2017 – January 2018 INA828

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

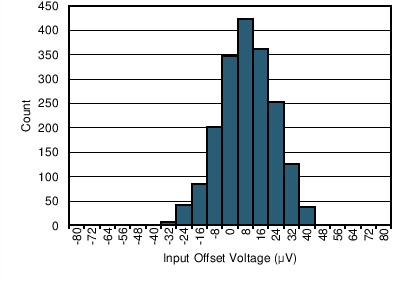

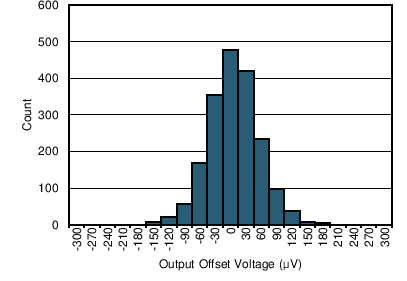

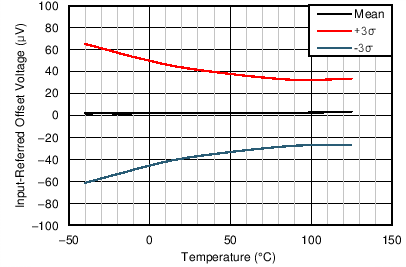

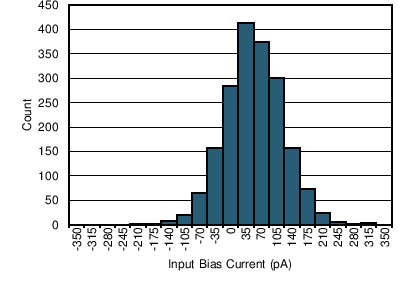

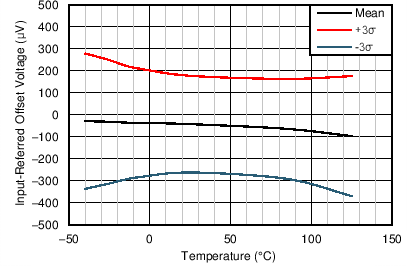

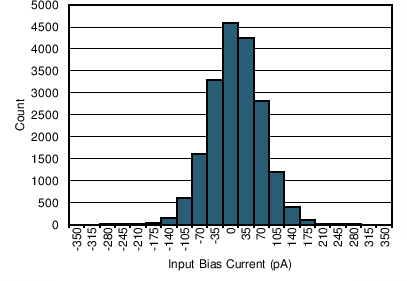

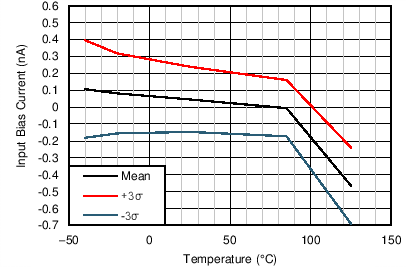

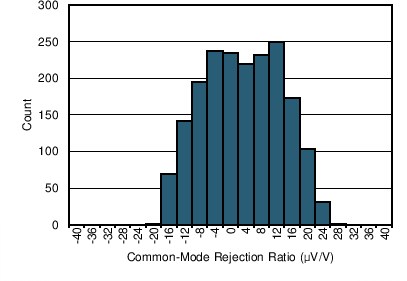

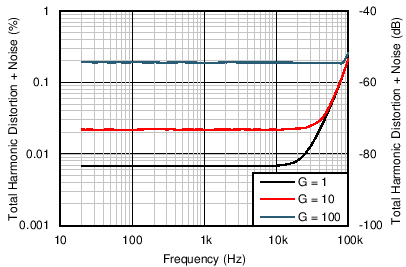

6.6 Typical Characteristics

At TA = 25°C, VS = ±15 V, RL = 10 kΩ, VREF = 0 V, and G = 1 (unless otherwise noted)

| N = 1886 | Mean = 4.73 µV |

| Std. Dev. = 13.98 µV | |

| N = 1886 | Mean = –8.71 µV |

| Std. Dev. = 48.57 µV | |

| G = 100 |

| 88 units, 3 wafer lots |

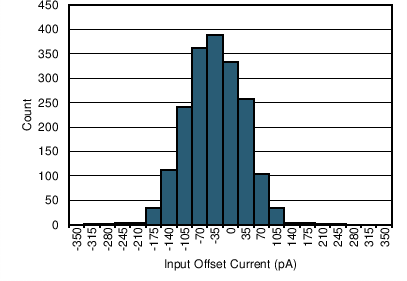

| N = 1886 | Mean = 36.25 pA |

| Std. Dev. = 65.31 pA | |

| N = 1886 | Mean = –52.64 pA |

| Std. Dev. = 63.86 pA | |

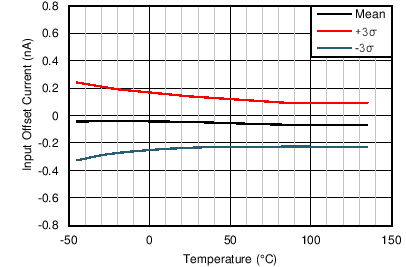

Figure 11. Input Offset Current vs Temperature

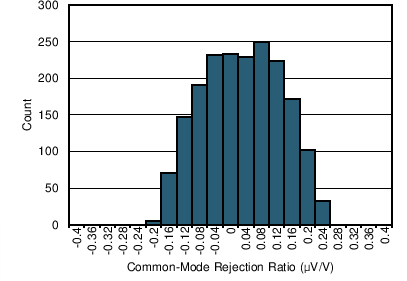

| N = 1886 | Mean = 0.01 µV/V |

| Std. Dev. = 0.1 µV/V | |

1.

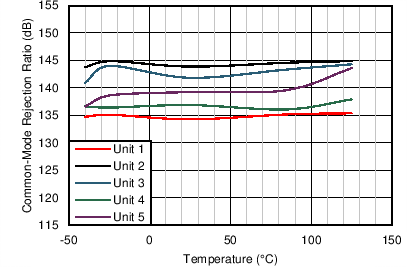

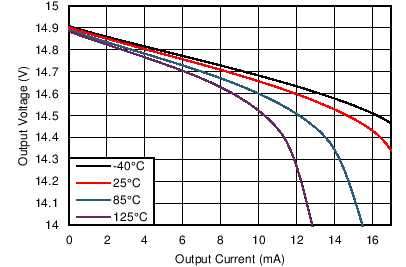

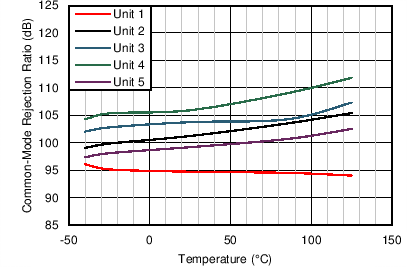

Figure 15. CMRR vs Temperature (G = 100)

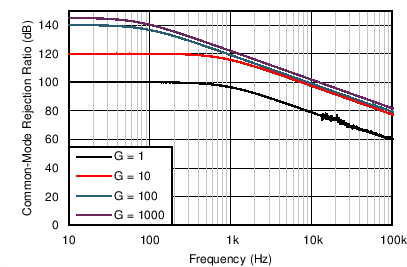

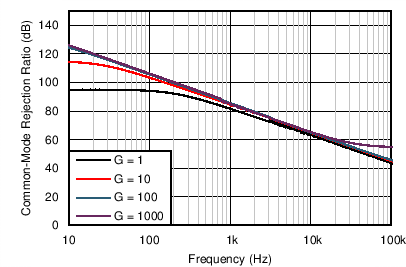

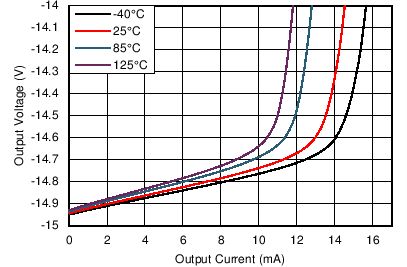

Figure 17. CMRR vs Frequency (RTI)

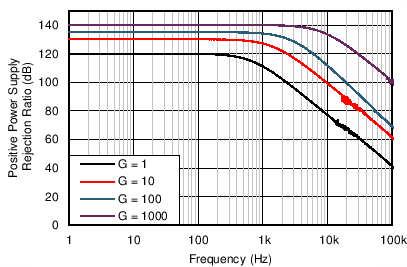

Figure 19. Positive PSRR vs Frequency (RTI)

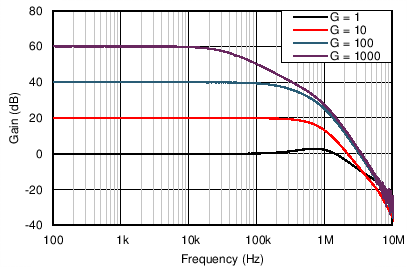

Figure 21. Gain vs Frequency

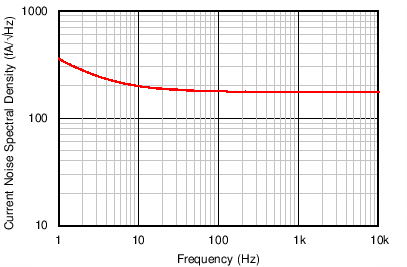

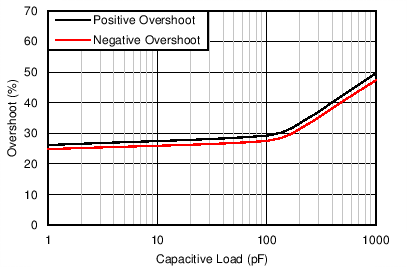

Figure 23. Current Noise Spectral Density

vs Frequency (RTI)

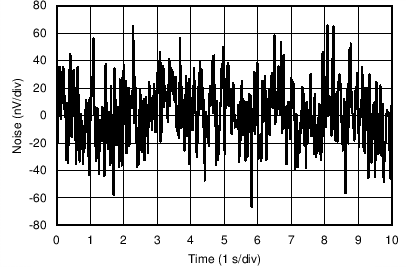

Figure 25. 0.1-Hz to 10-Hz RTI Voltage Noise (G = 1000)

| VS = ±15 V |

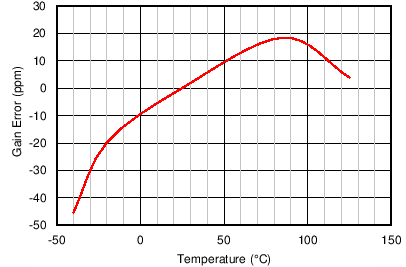

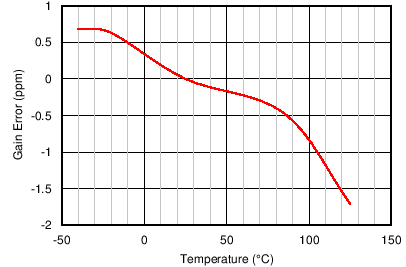

Figure 29. Gain Error vs Temperature (G = 100)

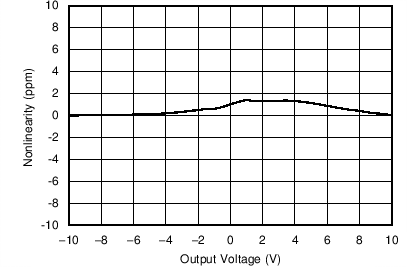

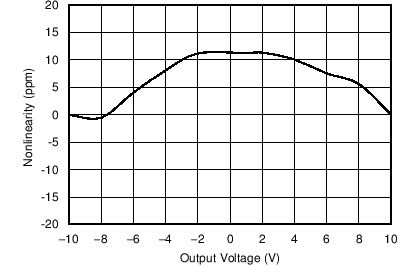

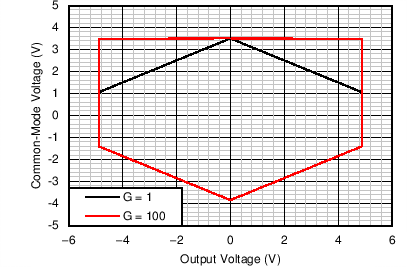

Figure 31. Gain Nonlinearity (G = 1)

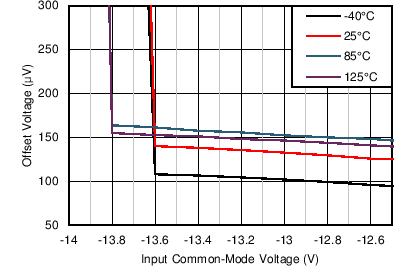

Figure 33. Offset Voltage vs Negative Common-Mode Voltage

Figure 35. Positive Output Voltage Swing vs Output Current

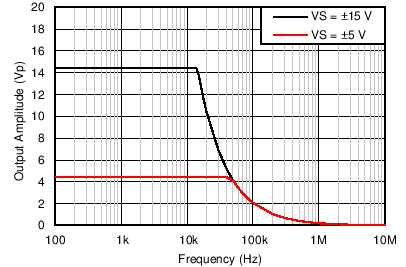

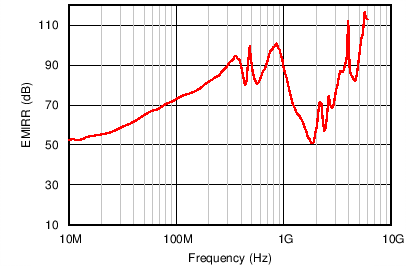

Figure 37. Large-Signal Frequency Response

Figure 39. Overshoot vs Capacitive Loads

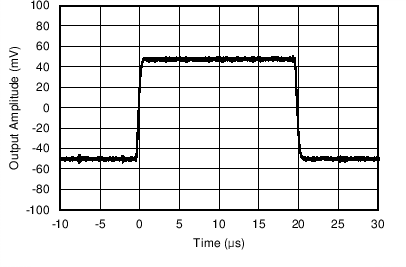

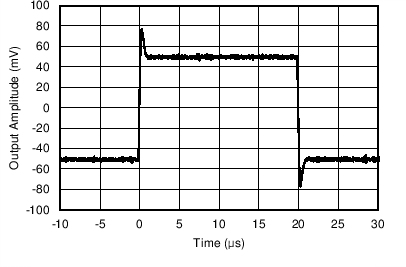

| G = 10, RL = 10 kΩ, CL = 100 pF |

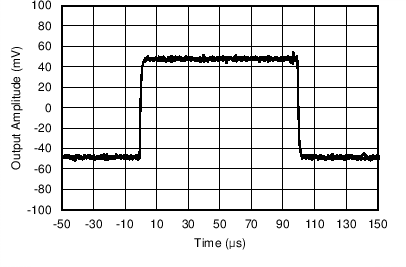

| G = 1000, RL = 10 kΩ, CL = 100 pF |

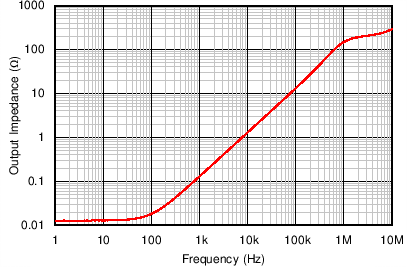

Figure 45. Closed-Loop Output Impedance

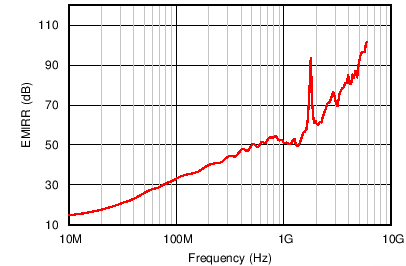

Figure 47. Common-Mode EMI Rejection Ratio

| VS = 5 V, G = 100 |

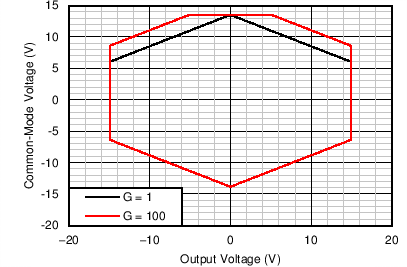

| VS = ±15 V, VREF = 0 V |

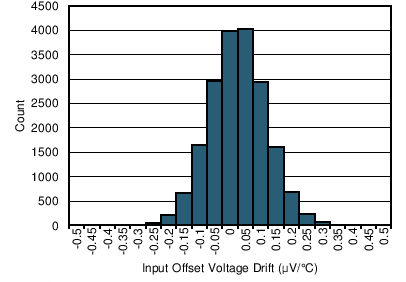

| N = 19081 | Mean = 0.16 nV/°C |

| Std. Dev. = 0.09 µV/°C | |

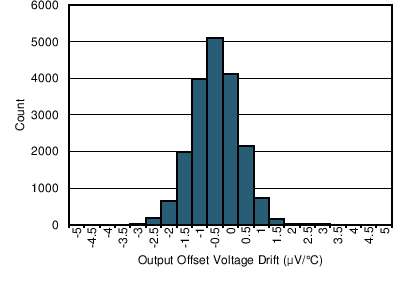

| N = 19081 | Mean = –0.73 µV/°C |

| Std. Dev. = 0.74 µV/°C | |

| G = 1 |

| 88 units, 3 wafer lots |

| N = 19081 | Mean = –5.32 pA |

| Std. Dev. = 57.46 pA | |

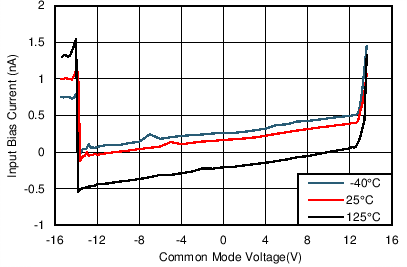

Figure 10. Input Bias Current vs Temperature

| N = 1886 | Mean = 1.18 µV/V |

| Std. Dev. = 10.04 µV/V | |

| 5 Typical Units |

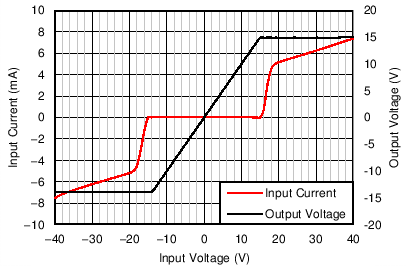

Figure 16. Input Current vs Input Overvoltage

Figure 18. CMRR vs Frequency

(RTI, 1-kΩ Source Imbalance)

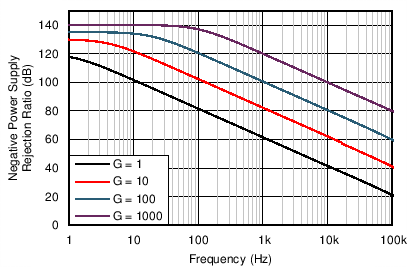

Figure 20. Negative PSRR vs Frequency (RTI)

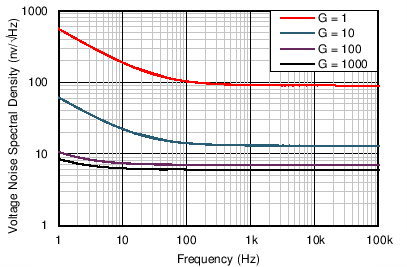

Figure 22. Voltage Noise Spectral Density

vs Frequency (RTI)

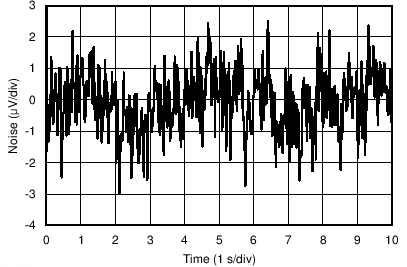

Figure 24. 0.1-Hz to 10-Hz RTI Voltage Noise (G = 1)

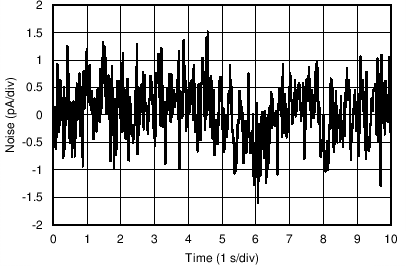

Figure 26. 0.1-Hz to 10-Hz RTI Current Noise

Figure 28. Gain Error vs Temperature (G = 1)

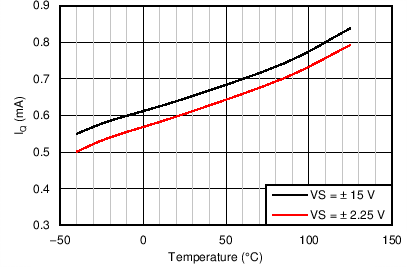

Figure 30. Supply Current vs Temperature

Figure 32. Gain Nonlinearity (G = 100)

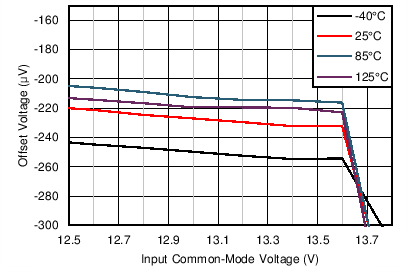

Figure 34. Offset Voltage vs Positive Common-Mode Voltage

Figure 36. Negative Output Voltage Swing vs Output Current

| 500-kHz Measurement bandwidth | 1-VRMS Output voltage |

| 100-kΩ Load |

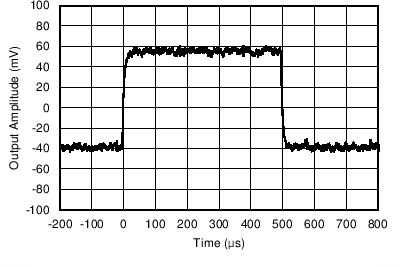

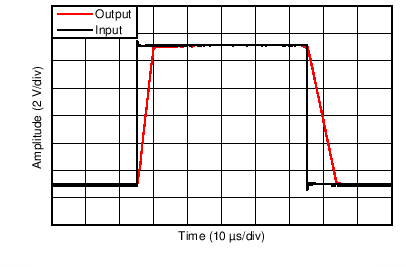

| G = 1, RL = 10 kΩ, CL = 100 pF |

| G = 100, RL = 10 kΩ, CL = 100 pF |

Figure 44. Large Signal Step Response

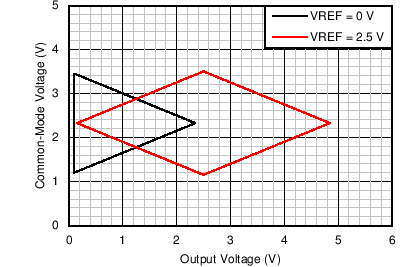

Figure 46. Differential-Mode EMI Rejection Ratio

| VS = 5 V, G = 1 |

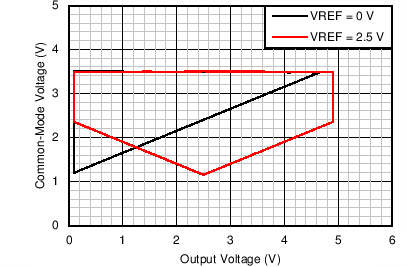

| VS = ±5 V, VREF = 0 V |