SNOSD60 June 2017 LMC6001-MIL

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

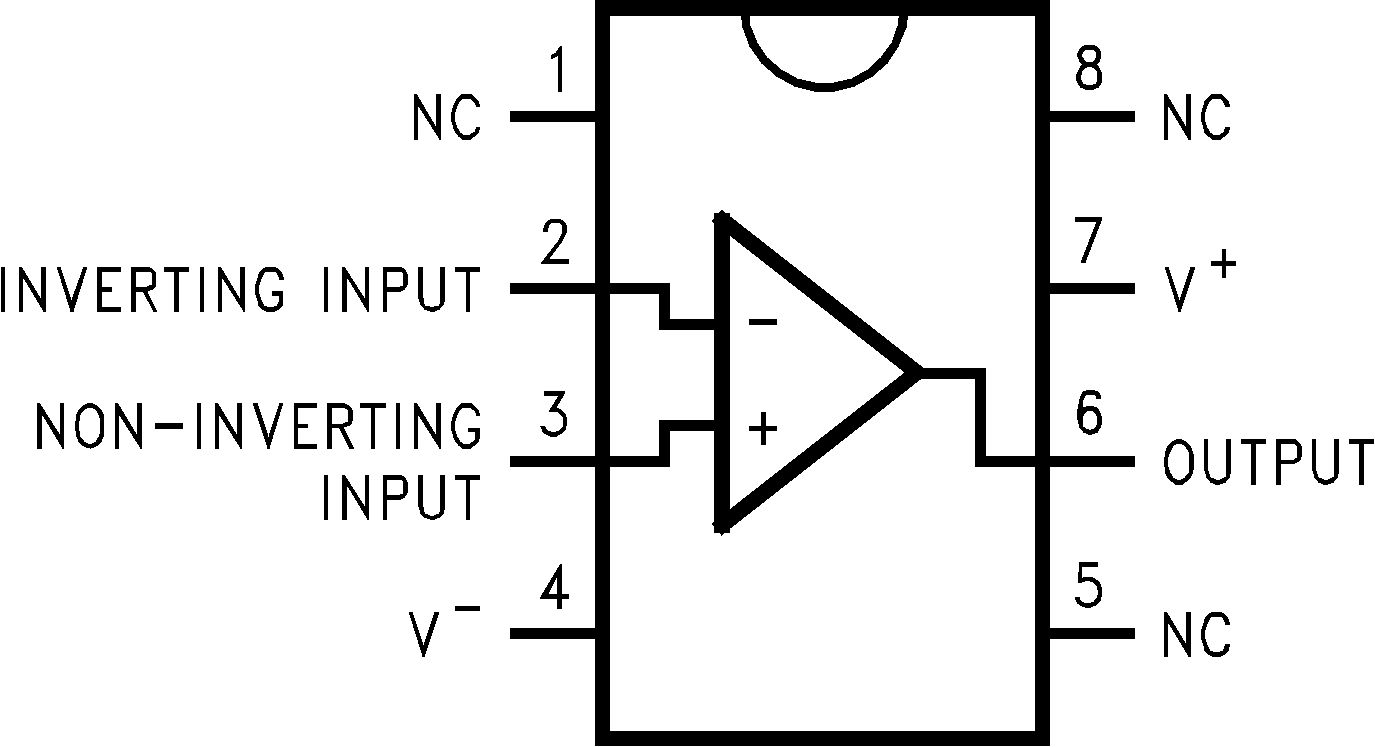

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Applications and Implementation

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- Y|0

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6 Detailed Description

6.1 Overview

LMC6001-MIL has an extremely low input current of 25 fA. In addition, its ultra-low input current noise of 0.13 fA/√Hz allows almost noiseless amplification of high-resistance signal sources. LMC6001-MIL is ideally suited for electrometer applications requiring ultra-low input leakage current such as sensitive photodetection transimpedance amplifiers and sensor amplifiers.

6.2 Functional Block Diagram

6.3 Feature Description

6.3.1 Amplifier Topology

The LMC6001-MIL incorporates a novel op amp design topology that enables it to maintain rail-to-rail output swing even when driving a large load. Instead of relying on a push-pull unity gain output buffer stage, the output stage is taken directly from the internal integrator, which provides both low output impedance and large gain. Special feed-forward compensation design techniques are incorporated to maintain stability over a wider range of operating conditions than traditional op amps. These features make the LMC6001-MIL both easier to design with, and provide higher speed than products typically found in this low-power class.

6.3.2 Latch-up Prevention

CMOS devices tend to be susceptible to latch-up due to their internal parasitic SCR effects. The (I/O) input and output pins look similar to the gate of the SCR. There is a minimum current required to trigger the SCR gate lead. The LMC6001-MIL is designed to withstand 100-mA surge current on the I/O pins. Some resistive method should be used to isolate any capacitance from supplying excess current to the I/O pins. In addition, like an SCR, there is a minimum holding current for any latch-up mode. Limiting current to the supply pins will also inhibit latch-up susceptibility.

6.4 Device Functional Modes

The LMC6001-MIL has a single functional mode and operates according to the conditions listed in Recommended Operating Conditions.