SBOS839J March 2017 – September 2019 TLV9061 , TLV9062 , TLV9064

UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information: TLV9061

- 8.5 Thermal Information: TLV9061S

- 8.6 Thermal Information: TLV9062

- 8.7 Thermal Information: TLV9062S

- 8.8 Thermal Information: TLV9064

- 8.9 Thermal Information: TLV9064S

- 8.10 Electrical Characteristics

- 8.11 Typical Characteristics

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- DPW|5

Orderable Information

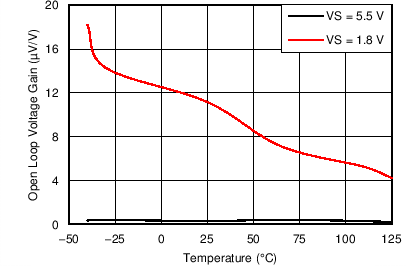

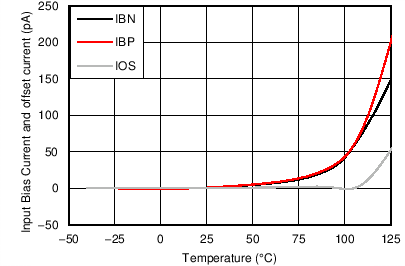

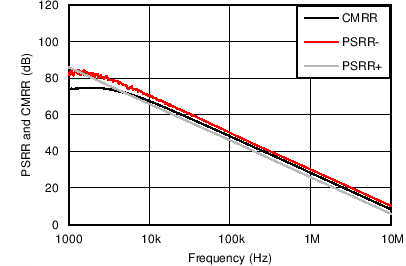

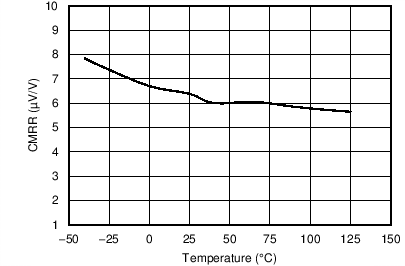

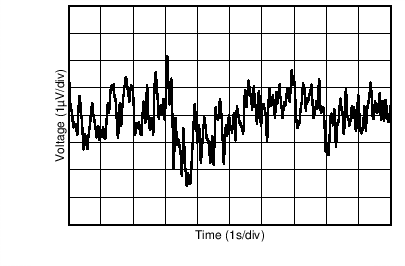

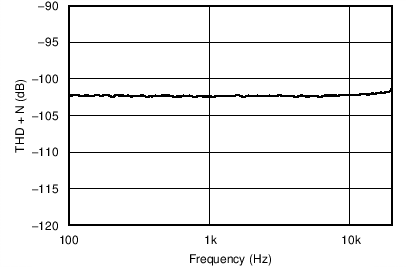

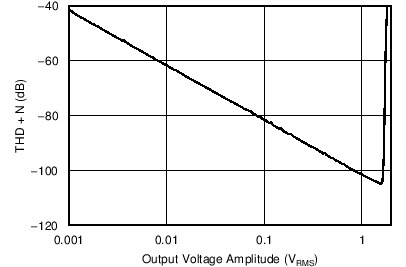

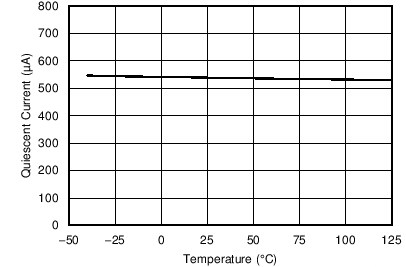

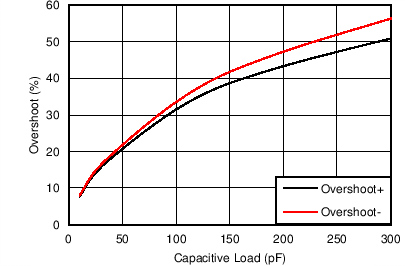

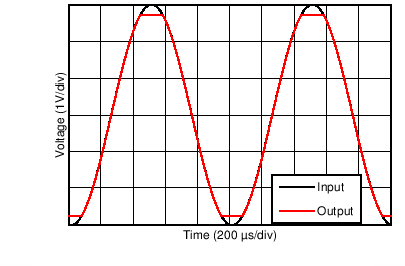

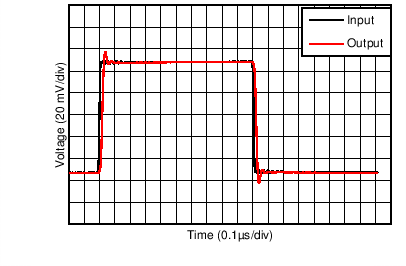

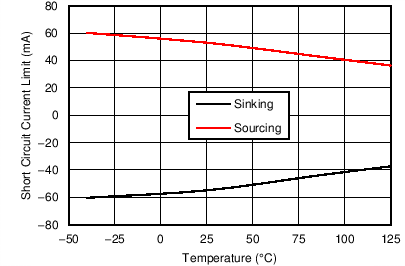

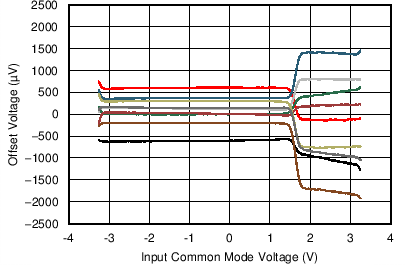

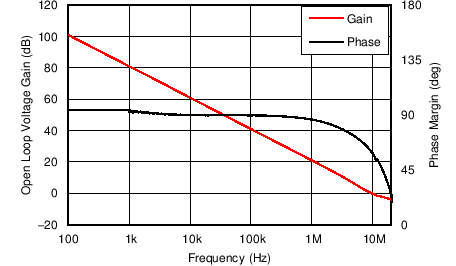

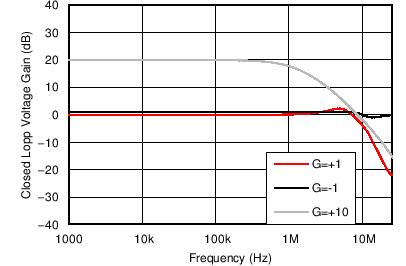

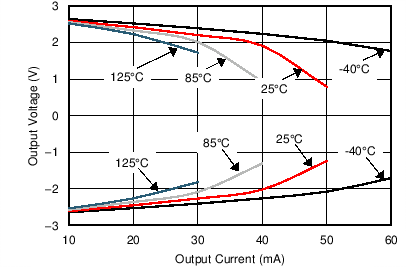

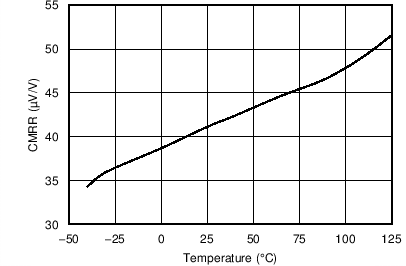

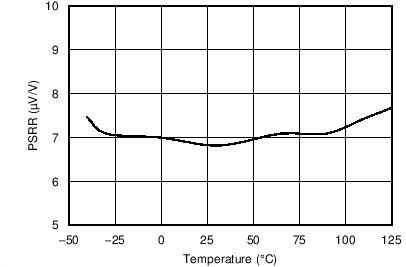

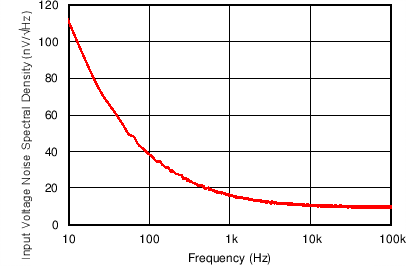

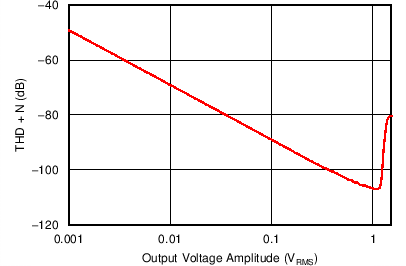

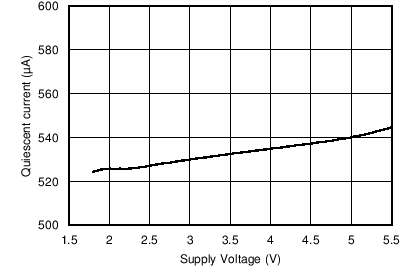

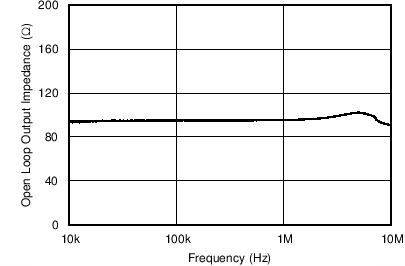

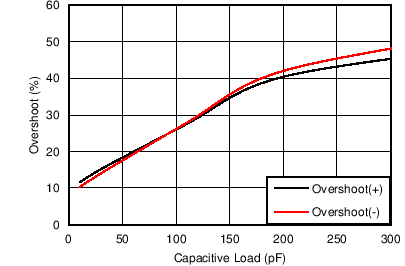

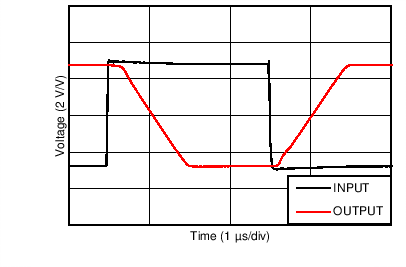

8.11 Typical Characteristics

at TA = 25°C, VS = 5.5 V, RL = 10 kΩ connected to VS / 2, VCM = VS / 2, and VOUT = VS / 2 (unless otherwise noted)

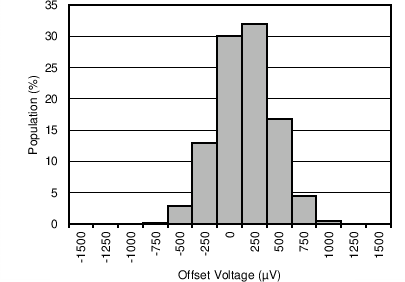

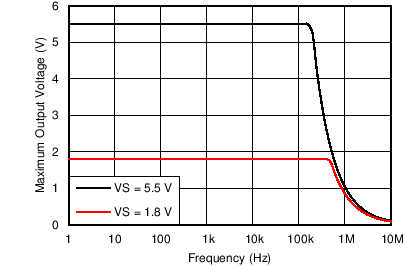

| VS = 1.8 V to 5.5 V | ||

| RL = 2 kΩ | ||

(Referred to Input)

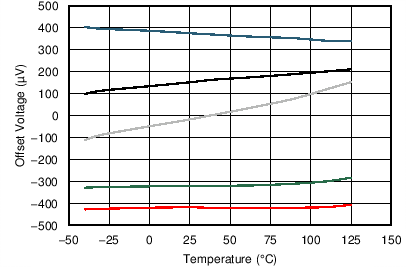

| VCM = (V–) – 0.1 V to (V+) – 1.4 V | ||

| TA= –40°C to 125°C | RL= 10 kΩ | VS = 5.5 V |

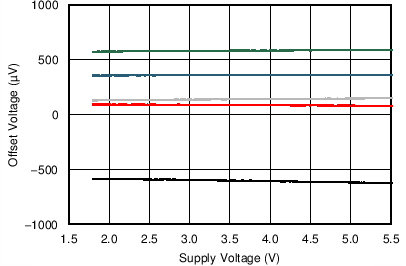

| VS = 1.8 V to 5.5 V | ||

| VS = 5.5 V | VCM = 2.5 V | RL = 2 kΩ |

| VOUT = 0.5 VRMS | BW = 80 kHz | G = +1 |

| VS = 5.5 V | VCM = 2.5 V | RL = 2 kΩ |

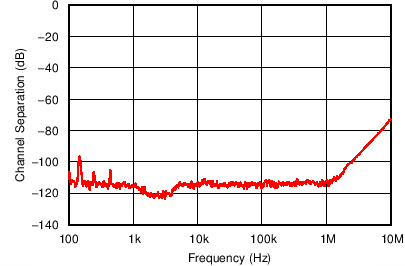

| G = –1 | BW = 80 kHz | f = 1 kHz |

| V+ = 2.75 V | V– = –2.75 V | G = +1 V/V |

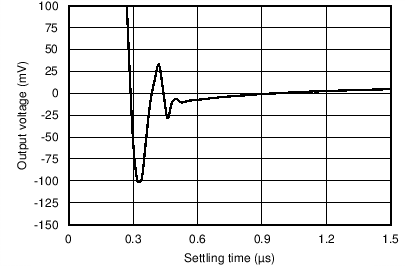

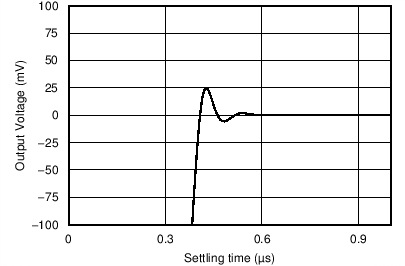

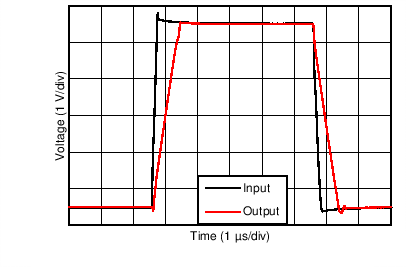

| VOUT step = 100 mVp-p | RL = 10 kΩ |

| V+ = 2.75 V | V– = –2.75 V | |

| V+ = 2.75 V | V– = –2.75 V | G = 1 V/V |

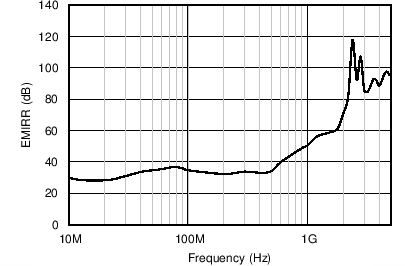

| PRF = –10 dBm | ||

| VS = 5.5 V | ||

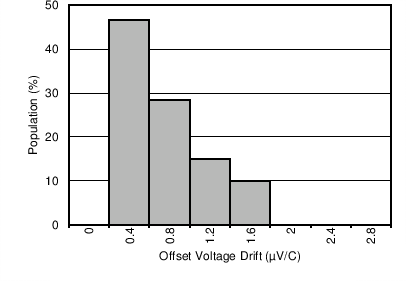

| TA = –40°C to 125°C | ||

| V+ = 2.75 V | V– = –2.75 V |

| CL = 10 pF | ||

| V+ = 2.75 V | V– = –2.75 V | |

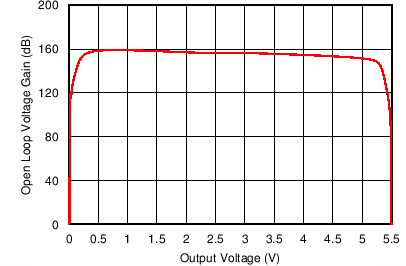

| VS = 5.5 V | VCM = –0.1 V to 5.6 V | TA= –40°C to 125°C |

| RL= 10 kΩ |

| VS = 1.8 V to 5.5 V | ||

| VS = 5.5 V | RL = 2 kΩ | G = +1 |

| VCM = 2.5 V | BW = 80 kHz | f = 1 kHz |

| V+ = 2.75 V | V– = –2.75 V | G = –1 V/V |

| VOUT step = 100 mVp-p | RL = 10 kΩ |

| V+ = 2.75 V | V– = –2.75 V | G = –10 V/V |

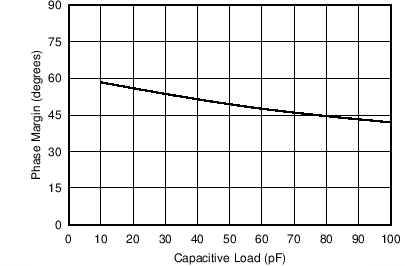

| V+ = 2.75 V | V– = –2.75 V | CL = 100 pF |

| G = 1 V/V |

| RL = 10 kΩ | CL = 10 pF | |

| V+ = 2.75 V | V– = –2.75 V | |

| VS = 5.5 V | ||