# Designing a reinforced isolated I<sup>2</sup>C-Bus<sup>®</sup> interface by using digital isolators

# By Thomas Kugelstadt

Senior Applications Engineer

The continuing changes in legislation concerning both the design and use of machinery and equipment require the isolation of almost any type of industrial system or interface. The inter-integrated circuit bus ( $I^2C$  Bus<sup>®</sup>) is a single-ended, multi-master, two-wire bus; and, while designed only for short-distance  $I^2C$  communication, it is no exception to isolation requirements.

The particular challenge in designing an isolated I<sup>2</sup>C interface by using standard digital isolators lies in the different operation modes between the two. The I<sup>2</sup>C Bus operates in bidirectional, half-duplex mode, while standard digital isolators are unidirectional devices. To make efficient use of one technology supporting the other, external circuitry is required that separates the bidirectional bus into two unidirectional signal paths without introducing significant propagation delay.

This article provides a short introduction to I<sup>2</sup>C Bus operation and then describes how to design an isolated I<sup>2</sup>C interface by adding only a few external components to a digital capacitive isolator.

# I<sup>2</sup>C Bus operation

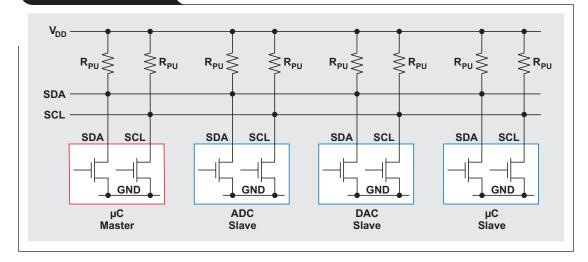

The  $I^2C$  uses open-drain technology, thus requiring the serial data line (SDA) and serial clock line (SCL) to be connected to  $V_{DD}$  by resistors (see Figure 1). Pulling the line to ground is considered a logic "0," and letting the line float is a logic "1." This logic configuration is used as a channel-access method. Transitions of logic states must occur while SCL is low, because transitions while SCL is high indicate START and STOP conditions. Typical supply voltages are 3.3 V and 5 V, although systems with higher or lower voltages are permitted.

I<sup>2</sup>C communication uses a 7-bit address space with 16 reserved addresses, so a theoretical maximum of 112 nodes can communicate on the same bus. In praxis, however, the number of nodes is limited by the specified total bus capacitance of 400 pF, which restricts communication distances to a few meters. The specified signaling rates are 100 kbps (standard mode), 400 kbps (fast mode), 1 Mbps (fast mode plus), and 3.4 Mbps (high-speed mode).

Figure 1. The I<sup>2</sup>C Bus<sup>®</sup>

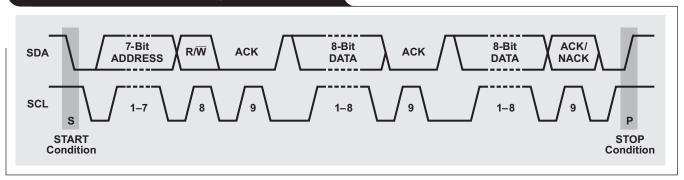

Figure 2. Timing diagram of a complete data transfer

The bus has two roles for nodes: master and slave. A master issues the clock and slave addresses and also initiates and ends data transactions. A slave receives the clock and addresses and responds to requests from the master. Figure 2 shows a typical data transfer between master and slave.

The master initiates a transaction by creating a START condition, then transmits the 7-bit address of the slave it wishes to communicate with. This is followed by a single READ/WRITE (R/W) bit, representing whether the master wishes to write to "0" or to read from "1," the slave. The master then releases the SDA line to allow the slave to acknowledge the receipt of data.

The slave responds with an acknowledge (ACK) bit by pulling SDA low during the entire high time of the ninth clock pulse on SCL. Then the master continues in either transmit or receive mode (according to the R/W bit sent), while the slave continues in the complementary mode (receive or transmit, respectively).

The address and 8-bit data bytes are sent with the most significant bit (MSB) first. The START bit is indicated by a high-to-low transition of SDA while SCL is high. The STOP condition is created by a low-to-high transition of SDA while SCL is high.

If the master writes to a slave, it repeatedly sends a byte to the slave, which sends an ACK bit for each byte received. In this case, the master is in master-transmit mode and the slave is in slave-receive mode.

If the master reads from a slave, it repeatedly receives a byte from the slave while sending an ACK bit to acknowledge the receipt of every byte but the last one (see Figure 3). In this situation the master is in master-receive mode and the slave is in slave-transmit mode.

The master ends the transmission with a STOP bit or may send another START bit to maintain bus control for further transfers.

When writing to a slave, a master mainly operates in transmit mode and changes to receive mode only when receiving acknowledgment from the slave.

When reading from a slave, the master starts in transmit mode and then changes to receive mode after sending a READ request (R/W bit = 1) to the slave. The slave continues in the complementary mode until the end of a transaction.

Note that the master ends a reading sequence by not acknowledging the last byte received—i.e., by sending a NACK bit. This procedure resets the slave state machine and allows the master to send the STOP command.

Figure 3. Changes in transmit/receive modes during a data transfer From Master to Slave From Slave to Master S Slave Address W A **DATA** A P **DATA** A = Acknowledged **Master Transmitter Writing to Slave Receiver** (ACK) A = Not acknowledged (NACK) S = Start **DATA** S Slave Address R A **DATA** A P P = Stop R = Read Master Receiver Reading from Slave Transmitter W = Write

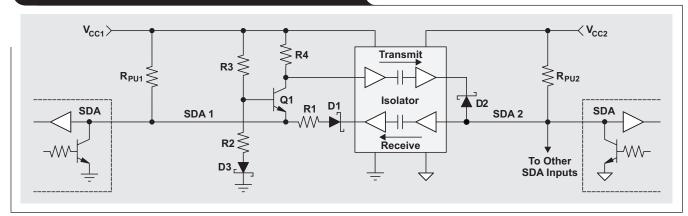

Figure 4. Isolating an I<sup>2</sup>C line by using a digital isolator

# Isolator design

Isolating an I<sup>2</sup>C signal path by using standard digital isolators requires splitting the half-duplex line into separate transmit and receive paths and converting the isolator's push-pull outputs into open-collector outputs via Schottky diodes (Figure 4). To prevent a transmitted signal from feeding back to its source, a comparator function is implemented that detects the direction of the signal flow and switches the signal paths accordingly.

Transistor Q1 and its surrounding resistor network provide the comparator function. Since the dominant switching level in  $I^2C$  is logic low, the base of Q1 is so biased that a low level applied to SDA1 turns the transistor on, and a low level sent from SDA2 keeps Q1 at high impedance. While the R3/R2 voltage divider primarily determines the biasing, diode D3 provides temperature compensation. To prevent SDA2 from turning Q1 on, the low-level output at D1 is raised by a voltage drop across R1, which raises Q1's emitter potential,  $V_E$ , and decreases the base-emitter voltage below the minimum turn-on level. However, care must be taken to maintain  $V_E$  below the minimum input high-level threshold of SDA1, which the  $I^2C$  specification lists as  $V_{IHmin}=0.3\times V_{CC}$ .

So, when the I<sup>2</sup>C Bus at SDA2 is pulled low, the low state passing in receive direction causes a voltage increase at

SDA1 that is just enough to block Q1 but well below  $V_{IHmin}$ , thus presenting a valid low for an  $I^2C$  input. At the same time, R4 provides a logic high to the isolator input in transmit direction, preventing diode D2 from conducting. Once SDA2 is released and returns to the level of  $V_{CC2}$ , SDA1 follows after one propagation delay through the isolator. When the isolator is driven from the bus side (SDA2), the added signal delays for both the falling and the rising edges mainly consist of only one propagation delay through the isolator.

In the opposite direction, when SDA1 is pulled low, its maximum low-level output,  $V_{OLmax}$ , is significantly lower than  $V_E$  and causes Q1 to conduct. The low-state signal passing through the isolator in transmit direction forward biases D2, and SDA2 goes low. However, when SDA1 is released, its voltage cannot return to the level of  $V_{CC1}$  immediately due to the remaining low-level signal at SDA2. Instead, SDA1 rises to the necessary  $V_E$  potential that blocks Q1, and it will stay at this level until a high-impedance Q1 allows R4 to provide a logic high to the isolator input, thus releasing SDA2 and D1. Only then will SDA1 be able to return to the level of  $V_{CC1}$ .

When the isolator is driven from the device side (SDA1), the added signal delays for both edges increase due to the involvement of the comparator function.

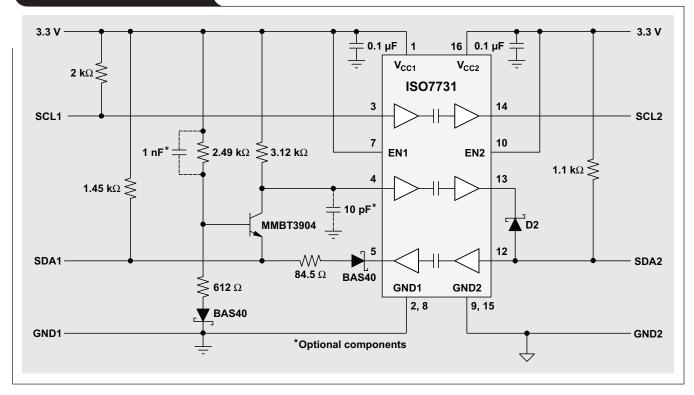

Figure 5. Final isolator circuit

Figure 5 shows the final isolator circuit for the majority of  $I^2C$  applications where the master is isolated from a slave bus. In this case, only the SDA line is bidirectional, while the SCL is unidirectional. For a multi-master system in which both lines must be bidirectional, the SDA circuit design can also be applied to the SCL when an ISO7742 isolator is used.

## **Related Web sites**

Product information:

www.ti.com/isolation

ISO7731

ISO7742

# TI Worldwide Technical Support

# **TI Support**

Thank you for your business. Find the answer to your support need or get in touch with our support center at

www.ti.com/support

China: http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp Japan:

# <u>Technical support forums</u>

Search through millions of technical questions and answers at TI's E2E™ Community (engineer-to-engineer) at

e2e.ti.com

China: http://www.deyisupport.com/ Japan: http://e2e.ti.com/group/jp/

# **TI Training**

From technology fundamentals to advanced implementation, we offer on-demand and live training to help bring your next-generation designs to life. Get started now at

training.ti.com

China: http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

Japan: https://training.ti.com/jp

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute Ti's approval, warranty or endorsement thereof.

A011617

E2E is a trademark of Texas Instruments. I2C Bus is a registered trademark of NXP B.V. Corporation. All other trademarks are the property of their respective owners.

All rights reserved.

SLYT403A

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated