# TI Precision Designs: Verified Design

# Single Supply Single-Ended Input to Differential Output

#### **TI Precision Designs**

TI Precision Designs are analog solutions created by TI's analog experts. Verified Designs offer the theory, component selection, simulation, complete PCB schematic & layout, bill of materials, and measured performance of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed.

#### **Design Resources**

Design Archive TINA-TI™ OPA333 All Design files SPICE Simulator Product Folder

# Circuit Description

This single ended input to differential output circuit converts a single ended input of +0.1V to +2.4V into a differential output of ± 2.3V on a single +2.7V supply. The output range is intentionally limited to maximize linearity. The circuit is composed of two amplifiers. One amplifier acts as a buffer and creates a voltage, Vout+. The second amplifier inverts the input and adds a reference voltage to generate Vout-. Both Vout+ and Vout- range from 0.1V to 2.4V. The difference, Vdiff, is the difference between Vout+ and Vout-. This makes the differential output voltage range +2.3V

Ask The Analog Experts

WEBENCH® Design Center

TI Precision Designs Library

M

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments

# 1 Design Summary

The design requirements are as follows:

Supply Voltage: 2.7V

• Reference Voltage: 2.5V

• Input: 0.1V - 2.4V

Output Differential: ±2.3V

Output Common Mode Voltage: +1.25V

Small Signal Bandwidth: 100kHz

Low Power: 100μA

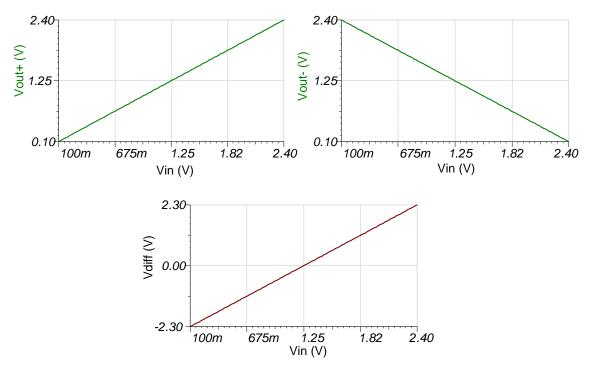

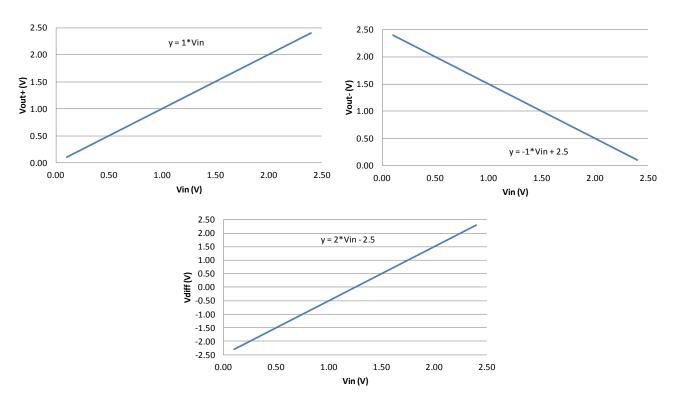

The design goals and performance are summarized in Table 1. Figure 1 depicts the measured transfer function of the design.

Table 1. Comparison of Design Goals, Simulation, and Measured Performance

|                                      | <b>Test Condition</b> | Goal       | Hand Calculation | Simulated  | Measured |

|--------------------------------------|-----------------------|------------|------------------|------------|----------|

| Uncalibrated Error for Vdiff (%FSR)  | 0.1 < Vin < 2.4V      | ±0.1%      | -                | -0.2%      | 0.07%    |

| Calibrated Error for<br>Vdiff (%FSR) | 0.1 < Vin < 2.4V      | ±0.01%     | -                | -          | 0.002%   |

| Total Current                        | Vcc = 2.7V            | 100µA      | 84.1µA           | 68.3µA     | 68.5µA   |

| Bandwidth                            | Vcc = 2.7V            | 100kHz     | 200kHz           | 300kHz     | 300kHz   |

| Noise                                | Total Integrated      | 100 µV rms | -                | 67.4uV rms | -        |

Figure 1: Measured Transfer Function for Vout+, Vout-, and Vdiff

## 2 Theory of Operation

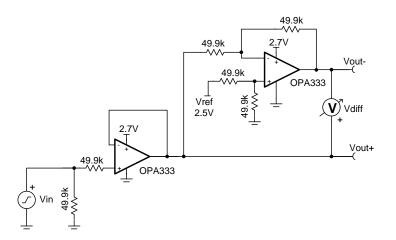

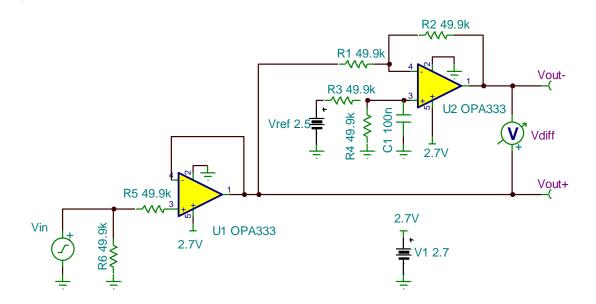

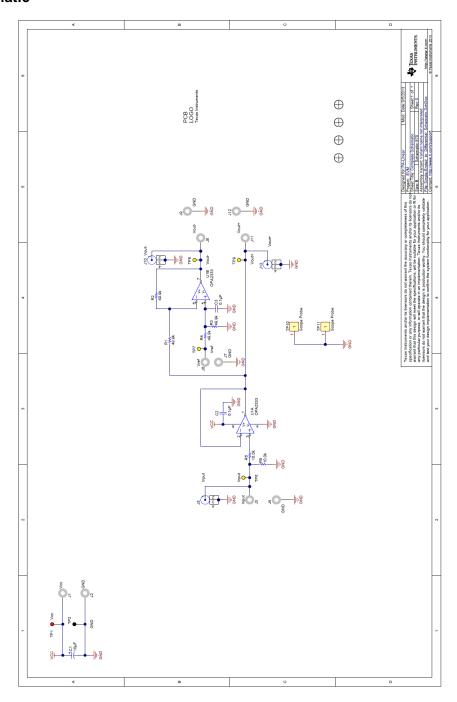

Figure 2 illustrates the detailed schematic.

Figure 2: Detailed Schematic

#### 2.1 Design Overview

The circuit takes a single ended input signal, Vin, and generates two output signals, Vout+ and Vout- using two amplifiers and a reference voltage, Vref. The differential output signal, Vdiff, is the difference between the two single-ended output signals. Vout+ is the output of the first amplifier and is a buffered version of the input signal, Vin; see Equation (1). Vout- is the output of the second amplifier which uses Vref to add an offset voltage to Vin and feedback to add inverting gain. The transfer function for Vout- is Equation (2).

$$V_{out+} = V_{in} \tag{1}$$

$$V_{\text{out-}} = V_{\text{ref}} * \left(\frac{R4}{R3 + R4}\right) * \left(1 + \frac{R2}{R1}\right) - V_{\text{in}} * \frac{R2}{R1}$$

(2)

Vdiff is the differential output voltage between Vout+ and Vout-. The transfer function for Vdiff is shown in Equation (3). By applying the conditions that R1 = R2 and R3 = R4 the transfer function is simplified into Equation (6). Using this configuration the maximum input signal is equal to the reference voltage and the maximum output of each amplifier is equal to the Vref. The differential output range is twice the Vref. Furthermore, the common mode voltage will at one half of Vref; see Equation (7).

$$V_{diff} = V_{out+} - V_{out-} = V_{in} * \left(1 + \frac{R2}{R1}\right) - V_{ref} * \left(\frac{R4}{R3 + R4}\right) * \left(1 + \frac{R2}{R1}\right)$$

(3)

$$V_{out+} = V_{in} \tag{4}$$

$$V_{out-} = V_{ref} - V_{in} \tag{5}$$

$$V_{diff} = 2 * V_{in} - V_{ref}$$

(6)

$$V_{\rm cm} = \frac{V_{\rm out+} + V_{\rm out-}}{2} = \frac{1}{2} V_{\rm ref}$$

(7)

## 3 Component Selection

This section will cover the reasoning behind the selected component values.

#### 3.1 Amplifier Selection

In this design our goal is to achieve good dc accuracy and low noise while maintaining low power. Linearity over the input range is key for good dc accuracy. The common mode input range and the output swing limitations will determine the linearity. In general an amplifier with rail-to-rail input and output swing is required. Low input offset voltage and offset drift are also key considerations for dc accuracy. Bandwidth is not a key concern for this design; however, in section 7.1 we will discuss circuit modifications that allow for a higher bandwidth design.

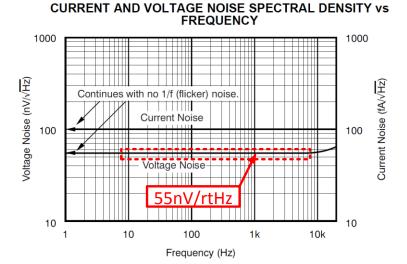

The OPA333 meets all of the key considerations for this circuit. The OPA333 is a high-precision CMOS op amp with  $5\mu V$  offset,  $0.05\mu V/^{\circ}C$  drift, and 55nV/rtHz output noise. The OPA333 uses chopping techniques to provide low initial offset voltage and near-zero drift over time and temperature. It is optimized for low-voltage, single supply operation with an output swing to within 50 mV of the positive rail Additionally, the quiescent current is typically  $25\mu A$ , allowing for low power operation. The typical unity gain bandwidth for the OPA333 is approximately 350kHz, which is above our design requirement. While this is a relatively low bandwidth, the key concern for designing this circuit was low power. In general, increasing bandwidth on an op amp will increase the quiescent current and power used by the amplifier.

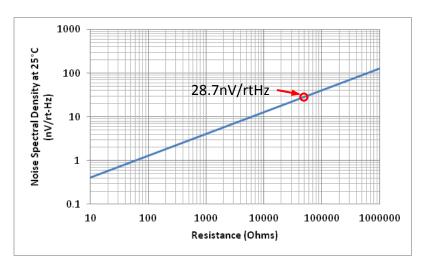

## 3.2 Passive Component Selection

Because the transfer function of Vout- is heavily reliant on resistors R1, R2, R3, and R4, resistors with low tolerances should be used to maximize performance and minimize error. To fit the design requirement of low power, we also selected the resistance to minimize the op amp load current. However, the resistance cannot be too high, or noise from the resistor will be too large. For this design, resistors with resistance values of 49.9k and tolerances of 0.1% were used to fit these criteria. Using these resistances, the maximum current drawn by the circuit is 84.1µA (see Equations (8) and (9)). This current is a combination of the quiescent current, the output of U1b, and the reference current.

$$I_{\text{max}} = \frac{V_{\text{out\_max}} - 0.5 * \text{Vref}}{R2} + \frac{\text{Vref}}{R3 + R4} + 2 * I_{\text{Q}}$$

(8)

Where

- I<sub>max</sub> is the maximum current drawn by the entire circuit

- Vout max is the maximum output at Vout-

- I<sub>Q</sub> is the typical quiescent current of the amplifier

$$I_{max} = \frac{(2.5V) - 0.5 * (2.5V)}{49.9k\Omega} + \frac{2.5V}{49.9k\Omega + 49.9k\Omega} + 2 * (17\mu\text{A}) = 84.1\mu\text{A}$$

(9)

From Figure 3, the noise spectral density of the resistors is less than 28.7nV/rtHz. Figure 3.3 shows that the noise of the OPA333 is approximately 55nV/rtHz. For low noise design it is recommended that the amplifier noise is larger than the resistor noise. The op amp is generally the most expensive part, and it would be counter-intuitive to purchase a low noise amplifier only to have more noise from the resistors. The resistor noise is lower than the amplifier noise which confirms our selection is correct (i.e. 28.7nV/rtHz).

Figure 3: Noise Spectral Density vs. Resistance

Figure 4: Noise Spectral Density for OPA333

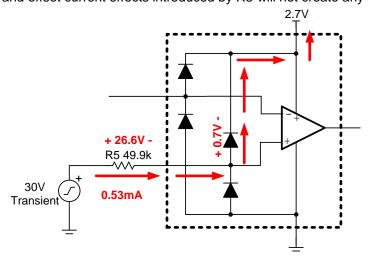

The resistor R5 protects the input of the amplifier by limiting the current in case transient input voltages exceed the supply voltage of the amplifier. According to the absolute maximum device ratings for the amplifier, the input current must be less than 10mA. The example in Figure 5 shows that the current would be limited to 0.53mA for a 30V transient. Equation (10) and (11) show the calculation for a 30V transient. Note, for negative transients V<sub>supply</sub> is zero. Equations (12) and (13) show the maximum transient for this configuration. Note that the transient protection in this example is beyond what is generally needed, however, the resistance is consistent with other resistors in the circuit to simplify the BOM. Furthermore, the noise contribution and offset current effects introduced by R5 will not create any significant errors.

Figure 5: Protection Resistor

$$I_{\rm in} = \frac{V_{\rm in} - V_{\rm diode} - V_{\rm supply}}{R_{\rm lim}}$$

(10)

$$I_{\rm in} = \frac{30V - 0.7V - 2.7V}{49.9k\Omega} = 0.53\text{mA}$$

(11)

$$V_{in} = I_{in} * R_{lim} + V_{diode} + V_{supply}$$

(12)

$$V_{\rm in} = (10 \,\mathrm{mA}) * (49.9 \,\mathrm{k}\Omega) + 0.7 \,\mathrm{V} + 2.7 \,\mathrm{V} = 502.4 \,\mathrm{V}$$

(13)

The remaining components, R6 and C1, ensure accuracy. Resistor R6 prevents floating inputs. For convenience, R6 is set to have a resistance of  $49.9k\Omega$ . Resistors R5 and R6 do not have to have 0.1% tolerances because they do not affect the transfer function. The capacitor, C1 is a filter capacitor.

#### 4 Simulation

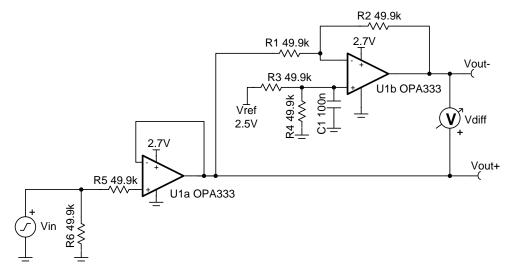

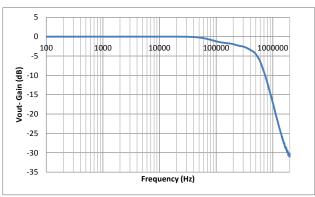

Figure 6 gives the TINA SPICE schematic used for the simulations in this section.

Figure 6: TINA SPICE Simulation Schematic

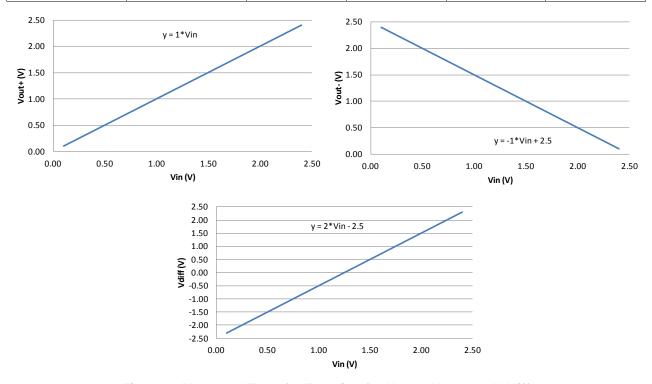

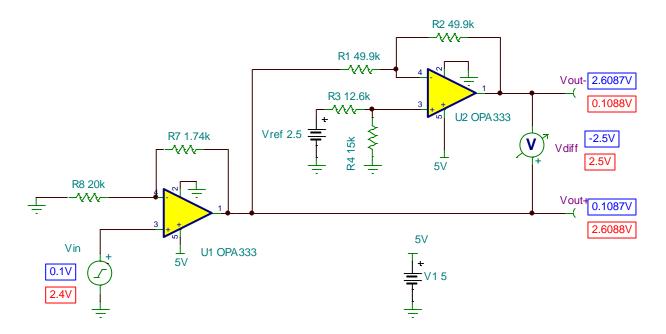

# 4.1 Transfer Function (dc)

The plots in Figure 7 were created by sweeping the dc voltage from 0.1V to 2.4V. Note that the input is restricted by 0.1V to maintain linearity of the OPA333 by keeping its outputs at least 100mV away from either power supply rail.

Figure 7: Simulated dc Transfer Function

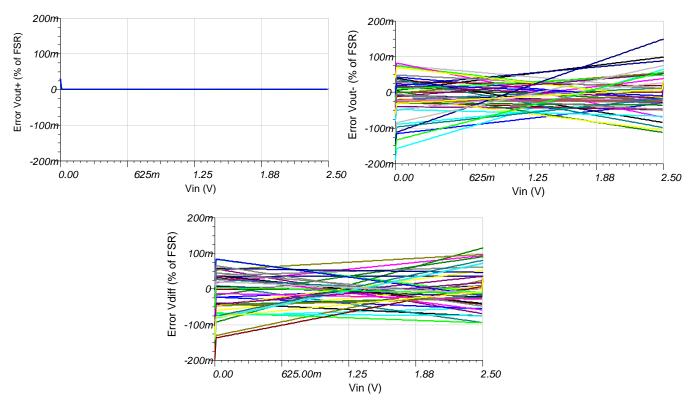

The error plots in Figure 8 were generated using a Monte Carlo Analysis where the input (Vin) was swept from 0V to 2.5V to show total error. The error was measured as a percentage of the full scale range (%FSR). The different slopes are caused by the statistical variation of the resistance due to tolerance. In this case, the tolerance of each resistor is set to 0.1%. Notice that at the ends of the input range the error increases. This is because of output swing limitations on the OPA333. Also the open loop gain (AoI) decreases when the output is less than 100mV from the power supply rails (see Figure 9).

Figure 8: Monte Carlo Error Analysis of dc Transfer Function

Figure 9: Excerpt from OPA333 Data Sheet

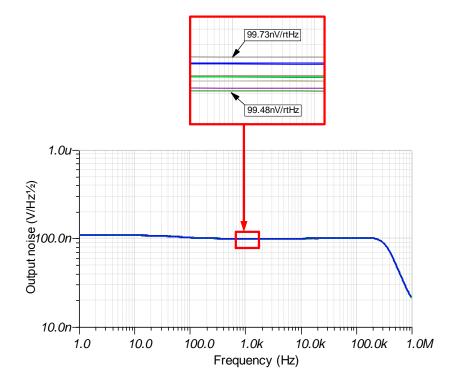

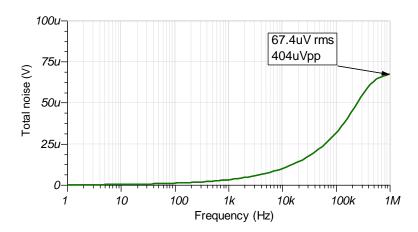

The noise analysis in Figure 10 shows the varying noise of Vdiff across different values of resistances due to the tolerance. By inspection, the thickness of the line is not large, suggesting that noise does not vary greatly with our chosen tolerances. The Figure 11 is the integral of Figure 10 and represents the total noise. Overall, the total noise is approximately  $67.4\mu V$  rms or  $404\mu Vpp$ .

Figure 10: Noise Spectral Density Out (Monte Carlo Analysis)

Figure 11: Total Integrated Noise Output (V rms)

#### 4.2 Bandwidth

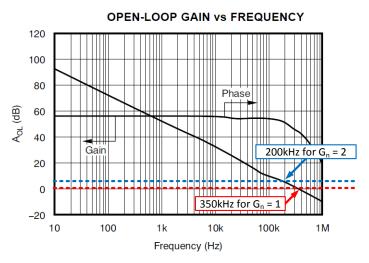

Figure 12 is the Aol curve taken from the OPA333 data sheet. The bandwidth of the buffer configuration, where gain  $(G_n)$  is equal to one, of the OPA333 is the point where the Aol curve equals 0dB. Consistent with the data sheet table, this appears to be approximately 350kHz. The second op amp is in noise gain configuration of 2 (6dB). Noise gain is the non-inverting gain of an op amp configuration. When using an Aol curve, noise gain must always be used. The bandwidth for  $G_n = 2$  appears to be approximately 200kHz. These should be consistent with the results of the small signal input found in section 6.3.

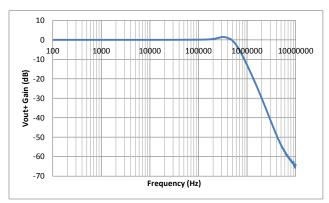

Figure 12: Estimating Bandwidth for OPA333 Using the Aol Curve

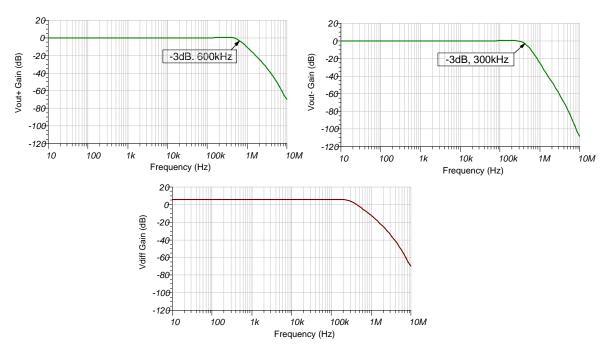

Figure 13 shows the simulated bandwidth limitations for each output. Vout+ has a wider bandwidth than Vout- because the noise gain is lower for Vout+ ( $G_n = 1$  for Vout+ and  $G_n = 2$  for Vout-). Notice that the simulated results differ from the calculated results (compare Figure 12 and Figure 13). The differences between simulated and calculated results occur because the model only approximates the data sheet and secondary effects, such as gain peaking, may affect results.

Figure 13: Simulated Bandwidth limits

# 4.3 Large Signal Step Response

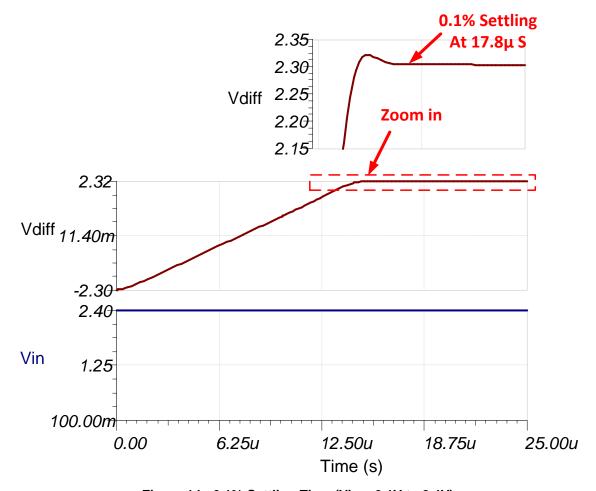

A step input wave from 0.1V to 2.4V was applied to measure the settling time to an accuracy of 0.1%. From Figure 4.10, the approximate settling time is 17.8µs for 0.1% tolerance.

Figure 14: 0.1% Settling Time (Vin = 0.1V to 2.4V)

# 5 PCB Design

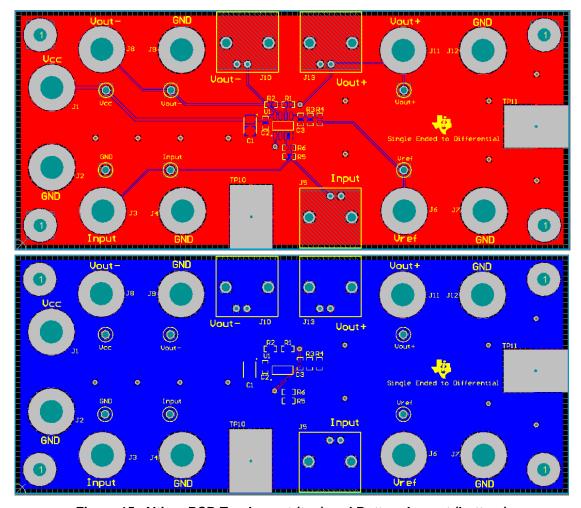

The PCB schematic and bill of materials can be found in Appendix A.

# 5.1 PCB Layout

The general guidelines for precision PCB layout were used on this design. For example, trace lengths are kept to minimum length especially input signals.

Figure 15: Altium PCB Top Layout (top) and Bottom Layout (bottom)

#### 6 Verification & Measured Performance

#### 6.1 Transfer Function (dc)

The measured transfer functions in Figure 16 were generated by sweeping the input voltage from 0.1V to 2.4V. The full input range is actually 0V to 2.5V, but it is restricted by 0.1V to maintain optimal linearity. A two point calibration was used to optimize the accuracy of the system (see Appendix B). The results in this section are all measured post calibration.

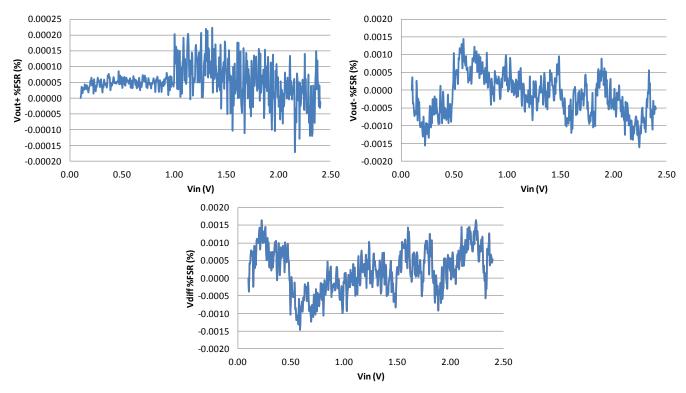

Figure 16: Measured dc Transfer Function (post calibration)

Figure 17 shows the post calibration error. The major sources of error in this circuit are resistor tolerance, and offset voltage. Calibration eliminates these errors. The error remaining after calibration is from noise, temperature drift, common mode rejection, and other non-repeatability errors. Overall, the errors are very small: 0.000222%, -0.00161%, and 0.00164% for Vout+, Vout-, and Vdiff respectively. These errors are voltage differences in the tens of microvolts.

Figure 17: Measured Error as % FSR (Post Calibration)

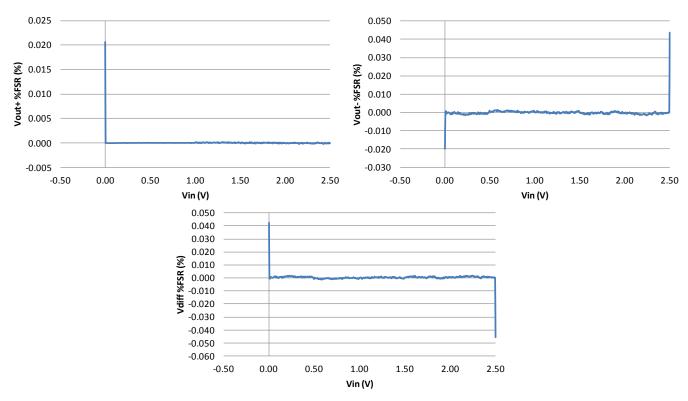

Figure 18 illustrates error as a % of FSR for entire input range (0V < Vin < 2.5V). Notice that the errors increase dramatically as the input approaches either end of its range. This is why the input range is restricted to 0.1V < Vin < 2.4V during calibration to optimize accuracy.

This non-linearity is the result of the output swing limitations of the OPA333 (see section 4.1). Overall, the errors for Vout+, Vout-, and Vdiff are 0.0207%, 0.0438% and -0.0457% respectively. These are errors of millivolts, two orders of magnitude larger than the errors in the linear region, showing non-linearity near 0V and 2.5V.

Figure 18: Error as % FSR Including Non-linear Region

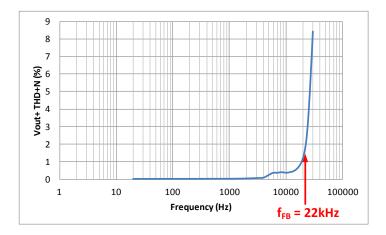

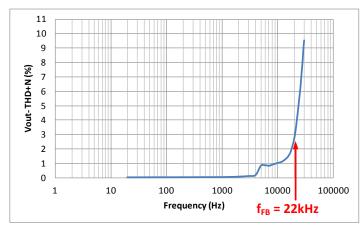

# 6.2 Slew Induced Distortion (THD+N)

When applying sinusoidal waveforms to this circuit, it is possible to cause slew induced distortion. Slew induced distortion occurs when the rise time of the sine wave exceeds the amplifiers slew rate. Both the frequency and amplitude of the input signal affect the rise time and are factors in determining if slew induced distortion is an issue. The relationship between slew rate limit, frequency, and peak output signal is given in Equation (14).

$$SR \ge 2\pi f V_{pk} \tag{14}$$

Where

- SR is the minimum amplifier slew rate required to avoid slew induced distortion

- **f** is the frequency of the input signal

- V<sub>pk</sub> is the peak voltage of the output signal

Equation (14) can be rearranged into Equation (15) to find the full power bandwidth, f<sub>FB</sub>.

$$f_{FB} = \frac{SR}{2\pi V_{pk}} \tag{15}$$

Where

f<sub>FB</sub> is the full power bandwidth. This is the maximum frequency that can be applied without slew induced distortion.

The full power bandwidth can also be seen as a maximum output frequency that can be achieved without having slew induced distortion. For a full-scale input signal, the full power bandwidth is calculated below.

$$f_{FB} = \frac{0.16V/\mu s}{2\pi (1.15V)} \approx 22kHz$$

(16)

Where

- SR is 0.16V/µs for the OPA333 (found in the data sheet)

- V<sub>pk</sub> is the peak amplitude. For a sine wave, this is half the peak-topeak amplitude. In this case, the peak amplitude is 1.15V (i.e. half of 2.3V)

The data in Figure 19 was generated by sweeping frequency from 20Hz to 30kHz and measuring the total harmonic distortion and noise (THD+N) with automated test equipment optimized for measuring THD+N. The objective is to show that distortion will dramatically increase as we approach the slew induced distortion frequency limit ( $f_{FB} = 22kHz$ ).

THD+N approaches 0.1% at approximately 3kHz for Vout- and 4kHz for Vout+. THD+N of 0.1% is sometimes thought of as the maximum distortion allowable for reasonable performance. As a rule of thumb, the full power bandwidth should be a decade less than the frequency calculated by the slew rate to ensure minimal distortion.

Figure 19: THD+N for Both Outputs

#### 6.3 Bandwidth

The small signal response data was generated by using a function generator to generate a sine wave of amplitude 10Vpp and an offset of 1.25V for the input. The small signal was offset such that the signal was entirely in the linear operating region. Using the same bandwidth calculation as above, the bandwidth is calculated below.

$$f_{FB} = \frac{0.16V/\mu s}{2\pi (5mV)} \approx 5MHz$$

(17)

However, the bandwidth of the OPA333 is shown in Section 4.2 to be 350kHZ for the first op amp and 200kHz for the second op amp. Since these limits are lower, they will control the bandwidth.

The data for Vout+ in Figure 20 was calculated by plotting the ratio of the peak-to-peak value of Vout+ to Vin in decibels verses the frequency. The formula to calculate the gain in decibels is Equation (18).

$$Gain(db) = 20 * log Vout+/Vin$$

(18)

The data for Vout- in Figure 20 was calculated in a similar manner. However, the ratio was of the peak-to-peak value of Vout- to Vout+, as shown in Equation (19).

$$f_{FB} = \frac{0.16V/\mu s}{2\pi (5mV)} \approx 5MHz$$

(19)

The ratio is Vout- to Vout+ because the input to the second op amp is Vout+.

The measured -3dB frequencies for Vout+ and Vout- are 600kHz and 300kHz respectively. The bandwidth of the circuit is therefore 300kHz. This is higher than the calculated bandwidth due to effects of peaking near unity gain

Figure 20: Bode Plots for Vout+ and Vout-

#### 6.4 Large Signal Step Response

The large signal step response was generated with a function generator creating a square wave with frequency 1kHz, amplitude of 2.3Vpp, and offset of 1.25V. The results are shown in Figure 21.

Figure 21: Large Signal Step Response of Vdiff

The settling time to 0.1% tolerance could not be measured. The measured settling time to 1% was approximately  $20\mu s$ .

#### 7 Modifications

#### 7.1 Increasing Bandwidth

To increase bandwidth, a different amplifier must be chosen. The tradeoff with increasing bandwidth is increasing the power dissipated by the circuit. In general, amplifiers with wider bandwidth consume more power. In general, amplifiers with lower noise will consume more power. Smaller resistances must then be used (see Figure 3). This further decreases noise and increases power. Table 2 lists possible alternative amplifiers with their respective maximum specifications.

**Table 2: Alternative Amplifiers**

|                            | OPA314 | OPA376 | OPA374 | OPA320 |

|----------------------------|--------|--------|--------|--------|

| Bandwidth<br>(MHz)         | 3      | 5.5    | 6.5    | 20     |

| Noise at 1kHz<br>(nV/rtHz) | 14     | 7.5    | 15     | 7      |

| Offset Voltage<br>(μV)     | 2500   | 25     | 5000   | 150    |

| Offset Drift<br>(μV/°C)    | 1      | 2      | 3      | 1.5    |

| Quiescent Current (µA)     | 210    | 950    | 750    | 1600   |

# 7.2 Changing Input and Output Range

Another modification to the circuit is changing the input range and output differential range (see Figure 22). Both changes can be implemented by adding a gain in the first stage. This also changes the common mode voltage of the outputs. Initially, the common mode is 1.25V. The new common mode voltage will depend on the resistances chosen and may possibly not be constant. To make the common mode voltage constant, R2 must equal R1 (see Equation (23)). This also makes Vout+ and Vout- symmetric about the common mode. The new transfer functions and the common mode voltage are shown as Equations (20), (21), (22), and (23) with R2 = R1.

$$V_{out+} = \left(1 + \frac{R8}{R7}\right) * V_{in}$$

(20)

$$V_{out-} = 2 * V_{ref} * \left(\frac{R4}{R3 + R4}\right) * - \left(1 + \frac{R8}{R7}\right) * V_{in}$$

(21)

$$V_{diff} = 2 * \left(1 + \frac{R8}{R7}\right) * V_{in} - 2 * V_{ref} * \left(\frac{R4}{R3 + R4}\right)$$

(22)

$$V_{cm} = \frac{1}{2} * \left( \left( \frac{R4}{R3 + R4} \right) * \left( 1 + \frac{R2}{R1} \right) * V_{ref} + \left( 1 - \frac{R2}{R1} \right) * V_{out+} \right) = \left( \frac{R4}{R3 + R4} \right) V_{ref}$$

(23)

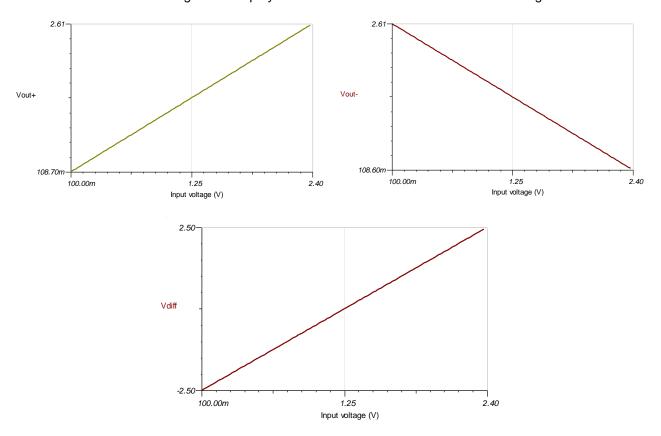

Figure 22: Modified Circuit

To explain the process, consider an example with an input range of 0.1V to 2.4V to and output differential range of  $\pm 2.5V$  and a reference of 2.5V. Because R1 = R2, we know that both Vout+ and Vout- must have full scale ranges of 2.5V. The input full scale range is 2.3V (i.e. 2.4V - 0.1V). The gain of the first amplifier must scale the full scale input range to the full scale output range (i.e. gain is equal to 2.5V/2.3V). Therefore, the relationship between R8 and R7, which controls the gain of the first amplifier, is defined (see Equation (24)). Note that if the gain is too large, the output swing of Vout+ may be in the non-linear region of the amplifier. In this example, 0.1087V < Vout + < 2.6088V. The maximum output is less than 100mV away from the power supply, so the power supply must be changed to maintain linearity. The circuit was modified to use a 5V power supply

$$\frac{R8}{R7} = \frac{2.5V}{2.3V} - 1 = 0.0870 \tag{24}$$

This gain defines the output range of Vout+, which also defines the output range of Vout- (see Table 3 or Figure 22: Modified CircuitFigure 22).

Vin (V)

Vout+ (V)

Vdiff V (V)

Vout- (V)

Minimum Voltage

0.1

0.10870

-2.5

2.60870

Maximum Voltage

2.4

2.60880

2.5

0.10880

Table 3: Voltage Range for Vin and all Outputs

Both outputs are symmetric about some common mode, so the common mode is the midpoint of the either output range. Using this information and Equation (23), we can determine the relationship of R3 and R4 (see Equation (25)).

$$\frac{R4}{R3} = \frac{0.5 * (2.60870V + 0.10880V)}{2.5V - 0.5 * (2.60870V + 0.10880V)} = 1.1906$$

(25)

The resistances chosen need to fulfill the ratios, follow the guidelines set in section 3.2, and be consistent with standard resistances. Figure 23 displays the simulated transfer functions of the designed circuit.

Figure 23: Simulated Transfer Functions for Modified Circuit

#### 8 About the Author

Thanh-Phong Nguyen was an intern for the Precisions Linear group at Texas Instruments. He currently is an undergraduate student pursuing a B.S. in Electrical Engineering at the Georgia Institute of Technology.

## 9 Acknowledgements & References

- 1. A. Kay, Operational Amplifier Noise: Techniques and Tips for Analyzing and Reducing Noise. Elsevier, 2012.

- 2. J. Vega. (2013, August 7). Harmonic Distortion: Part I Understanding Harmonic Distortion Vs. Frequency Measurements in Op Amps. Available: http://www.engenius.net/site/zones/acquisitionZone/technical\_notes/acqt\_013012

# Appendix A.

# A.1 Electrical Schematic

Figure A-1: Electrical Schematic

# A.2 Bill of Materials

| Item | Qty | Value  | Designator                                  | Description                           | Manufacturer    | Manufacturer Part # | Supplier Part # |

|------|-----|--------|---------------------------------------------|---------------------------------------|-----------------|---------------------|-----------------|

|      |     |        |                                             | CAP, TANT, 10uF, 20V, 20%, 1 ohm,     |                 |                     |                 |

| 1    | 1   | 10uF   | C1                                          | 3528-21 SMD                           | AVX             | TPSB106M020R1000    | 478-4087-1-ND   |

| 2    | 2   | 0.1uF  | C2, C3                                      | CAP, CERM, 0.1uF, 50V, 10%, X7R, 0603 | MuRata          | GRM188R71H104KA93D  | 490-1519-1-ND   |

| 3    | 10  |        | J1, J2, J3, J4, J6, J7,<br>J8, J9, J11, J12 | JACK NON-INSULATED .218" Keystone"    | 575-4           | 575-4K-ND           |                 |

| 4    | 5   |        | J2, J4, J7, J9, J12                         | JACK NON-INSULATED .218" Keystone"    | 575-4           | 575-4K-ND           |                 |

| 5    | 3   |        | J5, J10, J13                                | BNC Connector                         | TE Connectivity | 1-1478032-0         | A97560-ND       |

| 6    | 6   | 49.9k  | R1, R2, R3, R4, R5, R6                      | RES, 49.9k ohm, 0.1%, 0.1W, 0603      | Panasonic       | ERA-3AEB4992V       | P49.9KDBCT-ND   |

| 7    | 1   | Vcc    | TP1                                         | Test Point, TH, Compact, Red          | Keystone        | 5005                | 5005K-ND        |

| 8    | 1   | Black  | TP2                                         | Test Point, TH, Compact, Black        | Keystone        | 5006                | 5006K-ND        |

| 9    | 4   | Yellow | TP6, TP7, TP8, TP9                          | Test Point, TH, Compact, Yellow       | Keystone        | 5009                | 5009K-ND        |

|      |     |        |                                             | 1.8V, 17μA, microPower, Precision,    | Texas           |                     |                 |

| 10   | 1   | LF353M | U1                                          | Zero Drift CMOS Op Amp                | Instruments     | OPA2333AID          | 296-19543-5-ND  |

|      |     |        |                                             | Machine Screw, Round, #4-40 x 1/4,    | B&F Fastener    |                     |                 |

| 11   | 4   |        | U90, U91, U92, U93                          | Nylon, Philips panhead                | Supply          | NY PMS 440 0025 PH  | H542-ND         |

Figure A-2: Bill of Materials

# Appendix B.

#### **B.1** Calibration

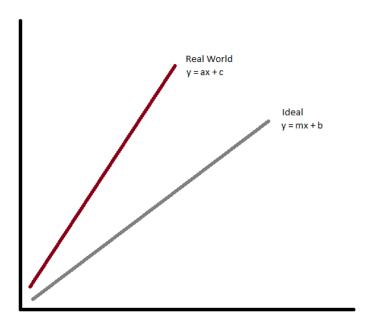

Due to amplifier offset voltage and resistor tolerance, the data will have an offset and a gain error. Figure 24 illustrates this point with great exaggeration. One source of gain error is due to the tolerances of the resistors. This was simulated in the Monte Carlo analysis in section 4.1. Another source of gain error is limitations of Aol; it is not infinite nor constant. The offset is due to uncertainties in the reference voltage, Vref. Calibration will remove these uncertainties.

Figure 24: Measured Data with Offset and Gain Error

To calibrate the data, we assume the data is linear. We assume that there is a gain error,  $G_{error}$ , and an offset,  $V_{offset}$ . In other words, Equation (26) mathematically defines the relationship between the ideal voltage reading and the measured one.

$$V_{\text{measured}} = G_{\text{error}} * V_{\text{ideal}} + V_{\text{offset}}$$

(26)

Assuming good linearity,  $G_{\text{error}}$  and  $V_{\text{offset}}$  should be constant for all measured values. To find these constants, the maximum and the minimum of the linear range will only be considered. Therefore, we will have a system of two equations with two unknowns: Equations (27) and (28).

$$V_{\text{measured max}} = G_{\text{error}} * V_{\text{ideal, max}} + V_{\text{offset}}$$

(27)

$$V_{\text{measured min}} = G_{\text{error}} * V_{\text{ideal min}} + V_{\text{offset}}$$

(28)

Solving Equations (27) and (28) for G<sub>error</sub> and V<sub>offset</sub> yields Equations (29) and (30).

$$G_{error} = \frac{V_{measured\_max} - V_{measured\_min}}{V_{ideal\_max} - V_{ideal\_min}}$$

(29)

$$V_{offset} = \frac{V_{measured\_min} * V_{ideal\_max} - V_{measured\_max} * V_{ideal\_min}}{V_{ideal\_max} - V_{ideal\_min}}$$

(30)

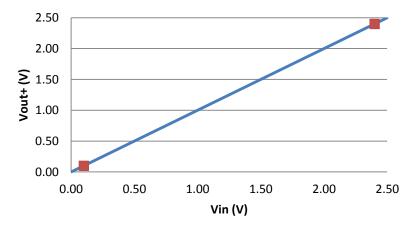

In Figure 25, the uncalibrated data for Vout+ is displayed. The red squares indicate the endpoints of the linear range.

Figure 25: Uncalibrated Vout+ Data

The maximum Vout+ in the linear range is 2.39973V and the minimum is 0.10017V. The values of the ideal Vout+ are 2.39978V and 0.10017V respectively. Using Equations (29) and (30), we can find the offset and gain error.

$$G_{\text{error}} = \frac{2.39973V - 0.10017V}{2.39978V - 0.10017V} = 0.999980 \text{ V/V}$$

(31)

$$V_{\text{offset}} = \frac{(0.10017\text{V}) * (2.39978\text{V}) - (2.39973\text{V}) * (0.10017\text{V})}{(2.39978\text{V}) - (0.10017\text{V})}$$

$$= 1.68 \times 10^{-6} \text{ V}$$

(32)

This procedure must be repeated for all 3 outputs. The gain errors and offsets for the measured data are summarized in Table 4.

Table 4: Calculated Gain Error and Offset Voltage

| Reading | Gain Error (V/V) | Offset (V) |

|---------|------------------|------------|

| Vout+   | 0.999980         | 1.68e-6    |

| Vout-   | 0.999995         | -1.20e-3   |

| Vdiff   | 0.99999          | 1.18e-3    |

To calibrate the data, the offset is subtracted, and the gain error is divided out for all measured values, as shown in Equation (33).

$$V_{calibrated} = \frac{V_{measured} - V_{offset}}{G_{error}}$$

(33)

The calibrated error is shown in section 6.1.

Even with calibration, there will be errors in the output due to inherent op amp errors such as input offset voltage, offset drift, and noise. The error in %FSR is defined in Equation (34). In error analysis, error in %FSR will be used to avoid complications near an ideal value of 0V.

$$\%FSR_{error} = \frac{V_{measured} - V_{ideal}}{|Measurement Range|}$$

(34)

The measurement range is 4.6V for Vout+, Vout-, and Vdiff to allow for comparison.

#### IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have *not* been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.