# Analog Engineer's Circuit Circuit for detecting input floating on ADS8681 ADC

TEXAS INSTRUMENTS

#### Data Converters

Dale Li

| Normal Bipolar Input Signal Range |                    | Bipolar Input<br>Range on ADS8681 |                      | Supply and Voltage Reference |       |                  |

|-----------------------------------|--------------------|-----------------------------------|----------------------|------------------------------|-------|------------------|

| V <sub>G_Min</sub>                | V <sub>G_Max</sub> | V <sub>ADC_Min</sub>              | V <sub>ADC_Max</sub> | AVDD                         | DVDD  | V <sub>REF</sub> |

| -12.88V                           | +12.88V            | -12.88V                           | +12.88V              | +5V                          | +3.3V | 4.096V           |

#### **Design Description**

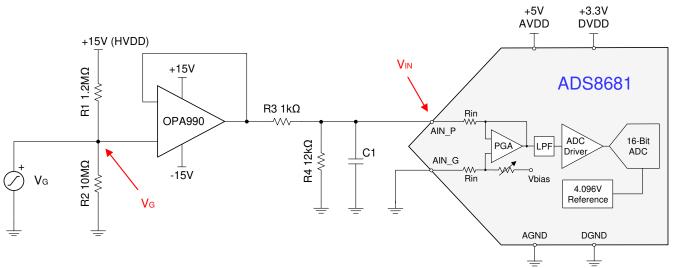

This circuit shows a solution to detect if the ADS8681 successive approximation register (SAR) analog-to-digital converter (ADC) input is floating. The ADS8681 device features a significant amount of signal chain integration, including high resistive input impedance, a programmable gain amplifier (PGA), and an ADC input driver. These features eliminate the requirement for driving the ADC inputs with a high-bandwidth amplifier. Therefore, a low-bandwidth, low-cost amplifier in a non-inverting unity gain configuration can be used in a solution for detecting a floating input. This solution has a minimal impact on the system performance metrics including signal-to-noise ratio (SNR) and total harmonic distortion (THD). This circuit is useful in end equipment such as: Analog input module, Servo drive functional safety module, Motor drives, and Factory automation and control.

1

#### Normal Operation:

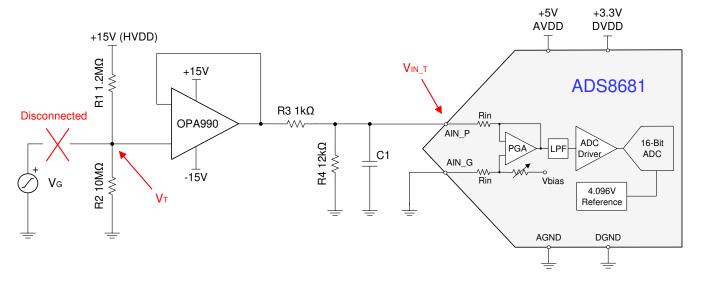

## Input Floating:

Texas Instruments

www.ti.com

## **Specifications**

| Specification | Goal   | Calculated and Simulated Value         |

|---------------|--------|----------------------------------------|

| Noise         | < 10µV | Calculated: 4.3µV<br>Simulated: 4.38µV |

| Phase Margin  | > 45°  | 64°                                    |

## **Design Notes**

- The resistors (R1 and R2) divide the power supply (HVDD) to create a biasing voltage, V<sub>T</sub>, that is outside of the expected input voltage range which is used to detect whether the V<sub>G</sub> input is floating.

- 2. The amplifier (OPA990) is configured as a non-inverting unity gain buffer to offer a high input impedance for the signal source (V<sub>G</sub>).

- 3. The resistors (R3 and R4) are used to scale down the input signal for a margin to detect if the input is floating.

- 4. Select 0.1% or better accuracy resistors for R3 and R4 to minimize the gain error.

- 5. Select C0G type capacitor for C1 in the front-end RC filter to minimize the distortion.

## **Component Selection**

The normal input signal range (V<sub>G</sub>) is ±12.88V. V<sub>G</sub> is scaled down by the resistor divider (R3 and R4) to provide margin above the normal input voltage range for the floating input detection voltage. The following table lists the input range on the ADS8681 in this design, the input voltage range (V<sub>G</sub>), and the expected normal voltage (V<sub>IN</sub>) on the ADC input for 1-V margin.

|         | Input Signal Voltage<br>(V <sub>G</sub> ) | ADS8681 Input Range<br>(V <sub>ADC</sub> ) | Expected Normal<br>Voltage on ADC Input<br>(V <sub>IN</sub> ) | Expected Voltage on<br>ADC Input for Float<br>(V <sub>IN_T</sub> ) |

|---------|-------------------------------------------|--------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|

| Maximum | +12.88V                                   | +12.88V                                    | +11.88V                                                       | +12.38V                                                            |

| Minimum | -12.88V                                   | -12.88V                                    | -11.88V                                                       | +12.38V                                                            |

R3 is selected as  $1k\Omega$  for a small gain and offset error. Therefore, R4 is determined by the following equation:

$$V_{IN} = \frac{R_4}{R_3 + R_4} \times V_G$$

$$R_4 = \frac{V_{IN}}{V_G + V_{IN}} \times R_3 = \frac{11.88V}{12.88V - 11.88V} \times 1k\Omega = 11.88k\Omega$$

A 12-k $\Omega$  and 0.1% tolerance resistor is finally selected for R4. The resistor value can be adjusted according to the noise and margin required in the system.

The objective of this step is to select the ADC input voltage under which a float is detected (called V<sub>IN\_T</sub>). This voltage is selected to be 0.5V higher than the highest normal operating input voltage (+11.88V) for margin to prevent a false detection of a float condition. Therefore, the V<sub>IN\_T</sub> can be calculated from the equation:

$$V_{IN}$$

T =  $V_{IN}$  + 0.5V = 11.88V + 0.5V = 12.38V

3. The objective of this step is to select a voltage divider on the input of the amplifier (OPA990) that will set the float voltage at the input of the ADC as selected in step 2. V<sub>IN\_T</sub> is the divided input down threshold voltage (V<sub>T</sub>) during a floating input condition. Use the following equations to calculate the required VT voltage to achieve the desired V<sub>IN\_T</sub>:

$$V_{IN_{T}} = \frac{R_4}{R_3 + R_4} \times V_T$$

$$V_T = \frac{R_3 + R_4}{R_4} \times V_{IN_{T}} = \frac{1k\Omega + 12k\Omega}{12k\Omega} \times 12.38V = 13.4V$$

R1 and R2 are selected to create the VT voltage during floating inputs. To achieve higher input impedance, R2 is selected as  $10M\Omega$ . R1 is determined by the following equation:

$$V_T = \frac{R_2}{R_1 + R_2} \times HVDD$$

$$R_1 = \frac{HVDD - V_T}{V_T} \times R_2 = \frac{15V - 13.4V}{13.4V} \times 10M\Omega = 1.194M\Omega$$

R1 is selected as  $1.2M\Omega$  which is a standard resistor value. Note that the tolerance on these resistors only impacts the float voltage accuracy.

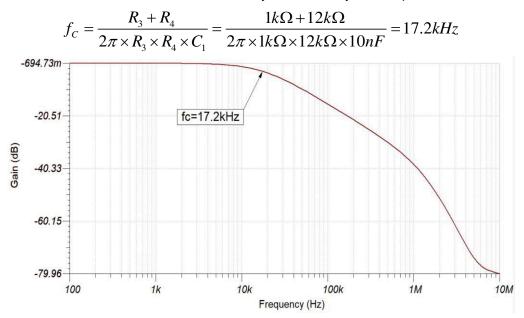

4. The capacitor C1 in parallel with R3||R4 is used to filter the noise from the front-end circuit. The equation for the cutoff frequency based on the input resistors and capacitors follows. The exact value may not be critical so we use a standard value of 10nF in this design.

$$f_{c} = \frac{R_{3} + R_{4}}{2\pi \times R_{3} \times R_{4} \times C_{1}} = \frac{1k\Omega + 12k\Omega}{2\pi \times 1k\Omega \times 12k\Omega \times 10nF} = 17.2kHz$$

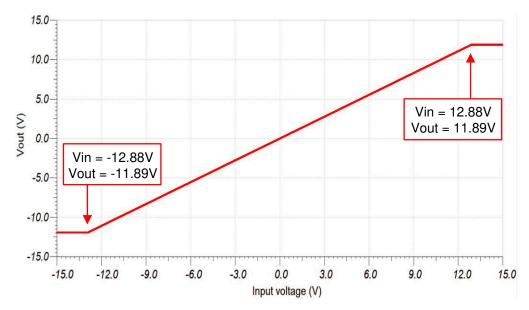

## **DC Transfer Characteristics**

The following graph shows a linear output response of the front-end circuit for input from single-ended –12.88V to +12.88V. See Determining a SAR ADC's Linear Range when using Instrumentation Amplifiers for detailed theory on this subject. The full-scale range (FSR) of the ADC falls within the linear range of the amplifier (OPA990).

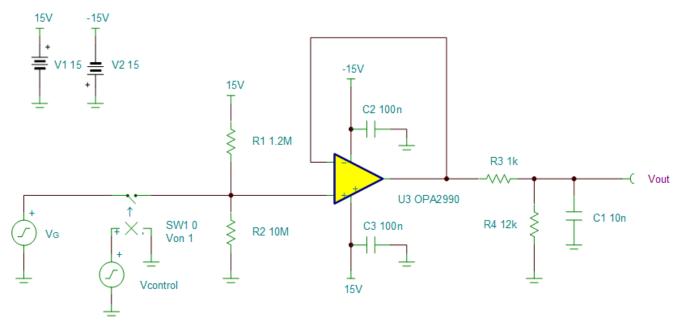

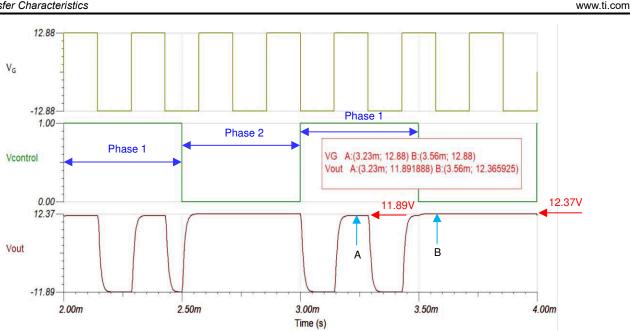

## **Simulation Verification for Floating Input**

The following circuit is used in TINA-TI to simulate and verify if the output voltage is correct as expected when the input of amplifier is floating. A voltage-controlled switch (SW1) is intentionally added to simulate the connection and disconnection status. The switch (SW1) is controlled by a periodic voltage signal (Vcontrol) for open and close.

The simulated result is shown in the following graph. The continuous input signal (V<sub>G</sub>) sweeps within the normal voltage range of  $\pm 12.88$ V. The control signal (Vcontrol) forces the switch (SW1) to turn on for a connected state in phase 1. The simulation shows a  $\pm 11.89$ -V output signal (Vout) in phase 1. The control signal (Vcontrol) forces the switch (SW1) to turn off for a floating state in phase 2. The simulation shows a 12.37-V output signal (Vout) in phase 2. Note that the simulated value and calculated value (12.38V) match well.

### **AC Transfer Characteristics**

The bandwidth for this circuit is limited by the RC filter (R3||R4 and C1). The hand calculation and the simulated results compare well (hand calculation f<sub>C</sub> = 17.2kHz, simulated f<sub>C</sub> = 17.2kHz). See the Op Amp Bandwidth video series for more details on this subject. Note that the internal 2nd-order low pass filter of the ADS8681 has a 15-kHz bandwidth. The bandwidth for this circuit is mainly dominated by the low-pass filter of the ADC.

Texas

STRUMENTS

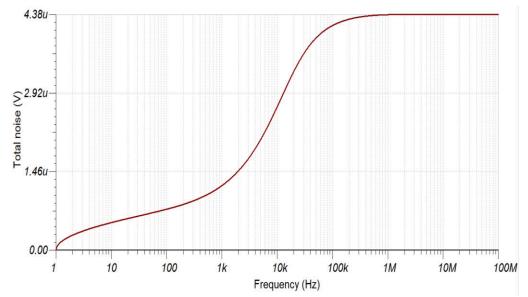

#### **Noise Simulation**

This section walks through a simplified noise calculation for the front-end circuit, providing an estimate to compare with simulated results in TI-TINA. In this circuit example, the resistor noise from the large resistance ( $R_1$  and  $R_2$ ) is a significant portion of the overall noise of the system. However, the output impedance ( $R_S$ ) of the signal source ( $V_G$ ) is usually low so the noise from the combination of  $R_S$ ,  $R_1$ , and  $R_2$  is small. See the following equation for noise calculation with  $R_S = 100\Omega$ .

Thermal noise from the resistors ( $R_S$ ,  $R_1$ , and  $R_2$ ):

$$\begin{aligned} R_{eq1} = R_{S} \| R_{1} \| R_{2} = \frac{R_{S} \times R_{1} \times R_{2}}{(R_{S} \times R_{1}) + (R_{S} \times R_{2}) + (R_{1} \times R_{2})} = \frac{100\Omega \times 1.2M\Omega \times 10M\Omega}{(100\Omega \times 1.2M\Omega) + (100\Omega \times 10M\Omega) + (1.2M\Omega \times 10M\Omega)} = 99.99\Omega \\ e_{n_{-}Req1} = \sqrt{4 \times k_{n} \times T_{n} \times R_{eq1}} = \sqrt{4 \times (1.38 \times 10^{-23}) \times 298 \times 99.99\Omega} = 1.282nV / \sqrt{Hz} \\ E_{n_{-}Req1_{-}RTI} = e_{n_{-}Req1} \times \sqrt{K_{n} \times f_{c}} = (1.282nV / \sqrt{Hz}) \times \sqrt{1.57 \times 17.2kHz} = 0.21uV_{rms} \\ E_{n_{-}Req1_{-}RTO} = E_{n_{-}Req1_{-}RTI} \times \frac{R_{4}}{R_{3} + R_{4}} = (0.21uV_{rms}) \times \frac{12k\Omega}{1k\Omega + 12k\Omega} = 0.194uV_{rms} \end{aligned}$$

Thermal noise from the resistors ( $R_3$  and  $R_4$ ):

$$R_{eq2} = R_3 || R_4 = \frac{R_3 \times R_4}{R_3 + R_4} = \frac{1k\Omega \times 12k\Omega}{1k\Omega + 12k\Omega} = 0.923k\Omega$$

$$e_{n_Req2} = \sqrt{4 \times k_n \times T_n \times R_{eq2}} = \sqrt{4 \times (1.38 \times 10^{-23}) \times 298 \times 0.923k\Omega} = 3.89nV / \sqrt{Hz}$$

$$E_{n_Req2} = e_{n_Req2} \times \sqrt{K_n \times f_C} = (3.89nV / \sqrt{Hz}) \times \sqrt{1.57 \times 17.2kHz} = 0.64uV_{rms}$$

Noise from OPA990 amplifier:

$$E_{n_{-}OPA_{-}RTI} = e_{n_{-}OPA} \times \sqrt{K_n \times f_C} = (28nV / \sqrt{Hz}) \times \sqrt{1.57 \times 17.2kHz} = 4.6uV_{rms}$$

$$E_{n_{-}OPA_{-}RTI} = E_{n_{-}OPA_{-}RTI} \times \frac{R_4}{R_3 + R_4} = (4.6uV_{rms}) \times \frac{12k\Omega}{1k\Omega + 12k\Omega} = 4.25uV_{rms}$$

Total noise applied to input of the ADC:

$$E_{n\_total} = \sqrt{E_{n\_Req1\_RTO}^{2} + E_{n\_Req2}^{2} + E_{n\_OPA\_RTO}^{2}} = \sqrt{0.194uV_{rms}^{2} + 0.64uV_{rms}^{2} + 4.25uV_{rms}^{2}} = 4.3uV_{rms}$$

The calculated and simulated noise match well (calculated noise =  $4.3 \mu V_{rms}$  and simulated =  $4.38 \mu V_{rms}$  as in the following graph). See TI Precision Labs - Op Amps: Noise 4 for detailed theory on amplifier noise calculations, Amplifier Noise Simulations (Op Amps: Noise 5) for detailed theory on amplifier noise simulations, and Calculating the Total Noise for ADC Systems for data converter noise.

7

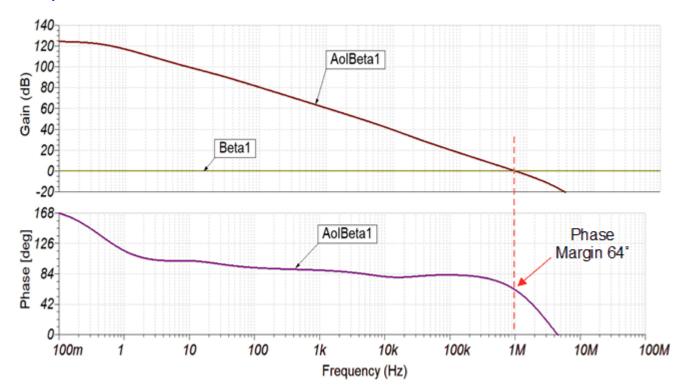

## **Stability Simulation**

The following simulation shows a stability check for the solution previously shown. This design has 64 degrees of phase margin which indicates that the circuit is stable. Generally, the circuit which has more than 45 degrees of phase margin is considered to be stable. For more information on stability analysis checks, see the Op Amps: Stability video series.

9

#### **Design References**

See the Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See TINA-TI simulation software.

#### **Design Featured Devices**

| Device  | Key Features                                                                                         | Link                               | Other Possible<br>Devices |

|---------|------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------|

| ADS8681 | 16-bit, 1-MSPS, single-channel, single supply with bipolar inputs SAR ADC                            | http://www.ti.com/product/ADS8681  | http://www.ti.com/adcs    |

| ADS8688 | 16-bit, 500-kSPS, 8-channel non-simultaneous-<br>sampling, single supply with bipolar inputs SAR ADC | http://www.ti.com/product/ADS8688  | http://www.ti.com/adcs    |

| ADS8686 | 16-bit, 1MSPS, 16-channel, dual simultaneous-<br>sampling, single supply with bipolar inputs SAR ADC | http://www.ti.com/product/ADS8686S | http://www.ti.com/adcs    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated