# Protecting automotive motor-drive systems from reverse polarity conditions

Michael Bifalco

Advanced Protection Motor Drivers

#### **ABSTRACT**

Electronics are integrated into virtually every system of the modern automobile, from safety to infotainment. Now more than ever it is important for manufacturers to build robust protection into the electrical systems of their vehicles.

One danger that all electrical systems face is a reversed polarity from the power source. This event can be caused by a short circuit, but is usually caused by simply switching the power and ground terminals when connecting a power supply. In the case of an automobile, the power for most electronics is supplied from the battery. A car battery that is installed with the terminal connections reversed could damage the electrical systems if they are not protected. The electronics could also be damage from reverse polarity if a jump-start is attempted with the jumper cables reversed.

Several techniques exist that can be used to provide reverse battery protection when designing electrical systems, but all have the common purpose of preventing current flow when the battery terminals are connected in reverse.

#### Contents

| 1 | Technique 1: Series Diode Method                                                                     | 2 |

|---|------------------------------------------------------------------------------------------------------|---|

| 2 | Technique 2: Single FET                                                                              |   |

| 3 | Technique 3: IC Solution                                                                             | 2 |

| 4 | Technique 4: NMOS and BJT                                                                            |   |

|   | 4.1 Using Technique 4 With an Integrated Boost Regulator Or An Integrated Charge Pump Motor Drive IC | 3 |

| 5 | Comparison of Power Dissipation                                                                      |   |

|   | List of Figures                                                                                      |   |

| 1 | Reverse Battery Protection With Diode at Supply Terminal                                             | 2 |

| 2 | Reverse Battery Protection With Diode at Ground Terminal                                             | 2 |

| 3 | Reverse Battery Protection With Supply Side PMOS FET                                                 | 2 |

| 4 | Reverse Battery Protection With Ground Side NMOS FET                                                 | 2 |

| 5 | Reverse Battery Protection With BJT and NMOS                                                         | 3 |

| 6 | Reverse Battery Protection With Motor Drive IC                                                       | 4 |

| 7 | Regulator Voltage versus VS                                                                          | 5 |

<sup>(1)</sup> All trademarks are the property of their respective owners.

#### 1 Technique 1: Series Diode Method

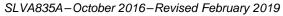

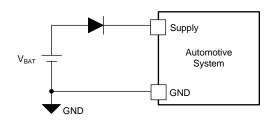

The first technique for implementing reverse battery protection is to include a diode in series with the power supply path, as shown in Figure 1 and Figure 2. If the battery terminals are connected in reverse, the diode will be reverse biased and will not allow current to flow through the system. This technique prevents the reversed polarity condition from harming the electronics or the battery.

Figure 1. Reverse Battery Protection With Diode at Supply Terminal

Figure 2. Reverse Battery Protection With Diode at Ground Terminal

This technique is cost effective as it requires only a single diode to implement in the simplest form, but it comes with the drawbacks of lower efficiency and a smaller usable battery range because of the voltage drop introduced by the diode. Furthermore, the diode could overheat in high-current applications. A heatsink can be added to the diode or multiple diodes can be connected in parallel to spread out the power dissipation, but both of these solutions increase the component cost and use valuable board space.

#### 2 Technique 2: Single FET

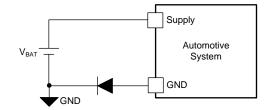

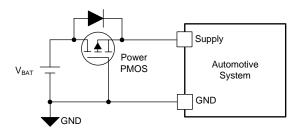

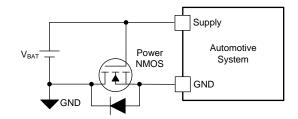

Another technique for reverse battery protection is to include a power FET in series with the power supply path. Either a p-channel power FET (PMOS) or an n-channel power FET (NMOS) can be used as shown in Figure 3 and Figure 4. When properly connected, the battery will briefly conduct current into the system through the body diode of the FET while the FET is switching on. Afterwards, the FET conducts the current with an extremely low on resistance. When the battery is connected in reverse, the FET will be off in either implementation and no current can flow. This technique helps protect the system and the battery from the reversed polarity condition.

Figure 3. Reverse Battery Protection With Supply Side PMOS FET

Figure 4. Reverse Battery Protection With Ground Side NMOS FET

This technique is more efficient than using only a diode because of the low Rdson of power MOSFETs. With an Rdson value in the tens of milliohms or lower, the voltage drop introduced by the FET is often far lower than the forward voltage of a diode, resulting in better efficiency, lower loss of usable battery voltage, and less heat. However, using this circuit has some drawbacks. The Rdson of a PMOS is higher than that of an NMOS of the same size, so an NMOS is usually the better choice from a cost perspective. The ground side NMOS implementation can lift up the ground reference which could affect sensitive circuits.

#### 3 Technique 3: IC Solution

Integrated circuits designed specifically to accomplish reverse battery protection are also an option in an automotive system. Texas Instruments' LM74610-Q1 or LM74700-Q1 smart diode controllers are examples of those type of devices. For a reference design using those devices, go to <a href="https://www.ti.com/tool/PMP9498">www.ti.com/tool/PMP9498</a> or <a href="https://www.ti.com/tool/DRV8912-Q1EVM">www.ti.com/tool/PMP9498</a> or <a href="https://www.ti.com/tool/DRV8912-Q1EVM">www.ti.com/tool/DRV8912-Q1EVM</a>.

If the motor drive IC doesn't have an external accessible high side supply to provide a reverse protection switching control signal, such as: DRV8912-Q1, the above three techniques can be adopted for the input source reverse protection.

#### 4 Technique 4: NMOS and BJT

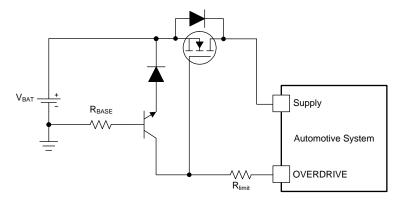

The circuit in Figure 5 makes use of a power NMOS and an NPN bipolar junction transistor (BJT) to achieve reverse battery protection. If the battery is connected in reverse, the body diode of the NMOS will not conduct current nor will the NMOS turn on, thereby protecting the system from the reverse polarity condition. When the battery is connected correctly, the circuit permits current to flow with very little power lost because of the low Rdson of the NMOS.

Figure 5. Reverse Battery Protection With BJT and NMOS

For the power NMOS to turn on, the gate voltage must be higher than the source voltage which cannot be accomplished with VBAT alone. Therefore the gate is tied to a signal called OVERDRIVE, representing a gate driving voltage. This technique usually requires additional circuitry to produce a suitable gate-to-source voltage to turn on the NMOS, often in the form of a charge pump or boost regulator.

The BJT is used to ground the NMOS gate during the reverse polarity condition to ensure the NMOS turns off. When the battery is connected correctly, the base voltage is lower than the collector and emitter voltages so the BJT will be off. When the battery terminals are connected in reverse, the ground node becomes the positive battery terminal and the VBAT node becomes the negative battery terminal. A positive voltage is present from the base to the emitter of the BJT, so the BJT will turn on which connects the NMOS gate to ground through the BJT and turns off the NMOS.

The resistor, R<sub>BASE</sub>, is used to limit the current into the base of the BJT, and the diode prevents current from entering the BJT when the battery is connected correctly.

The low Rdson of the NMOS results in excellent efficiency and less loss in battery voltage range from the protection circuit. This technique also removes the disadvantage of lifting the ground up that is caused by the single NMOS solution.

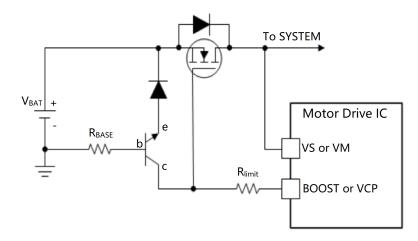

## 4.1 Using Technique 4 With an Integrated Boost Regulator Or An Integrated Charge Pump Motor Drive IC

This technique is particularly well-suited for motor drive applications. Many TI motor drive devices include integrated boost regulator device DRV3205-Q1 and integrated charge pump devices, such as: DRV3245Q-Q1, DRV8343-Q1, DRV8703-Q1 and DRV8873-Q1 can support the required overdrive voltage for the NMOS gate without the need for additional external circuitry.

Figure 6 shows the circuit for reverse battery protection using a motor drive device.

Figure 6. Reverse Battery Protection With Motor Drive IC

The body diode of the FET allows current to flow into the device initially, allowing the device to power on. When the device is powered on, the boost regulator output BOOST or the charge pump output VCP provides a voltage above the supply voltage which is high enough to turn on the reverse blocking FET, ensuring low Rdson to maximize efficiency of the reverse battery protection circuit. To minimize cost and simplify the bill of materials (BOM), the same power NMOS model used for the half bridges of the driver stage can be used as the reverse battery protection NMOS.

A system designer must select a BJT that supports the different voltages it can be exposed to in the system. When the battery is connected correctly, the collector-to-emitter voltage of the BJT is effectively the same as the BOOST or VCP pin voltage is with respect to supply. Most BJTs designed for power applications can accept that level of collector-to-emitter voltage. The BJT must also have a sufficiently large collector-to-base voltage specification to avoid damage from the BOOST or VCP pin voltage. This voltage specification is required because the base will remain grounded when the battery is connected correctly, but the BOOST or VCP pin output will increase with respect to ground as the supply increases. For example, the DRV8703-Q1 will regulate at 24 V when the battery is 14 V (typical) so the BJT must support at least 24 V from collector to base. When selecting the BJT, also consider automotive conditions such as load dump that can effect the voltages that the system is exposed to.

When the battery is connected in reverse, the specified base-to-emitter voltage must be greater than the battery voltage because the battery voltage will appear from base to emitter. The base resistor must be selected to limit the current into the base. Most BJT data sheets recommend a resistor of a few kilo-Ohms.

The resistor between the BOOST or VCP pin and the gate of the FET should be sized so that the external current limit of the BOOST or VCP pin is not exceeded, including any additional load from other external circuitry. As an example, assume that the current is limited to half the maximum external load to give margin for powering other external loads in the system. For DRV8703-Q1, this current limit is 12 mA and the typical voltage is 10 V above supply. The BJT will be in cutoff mode when the battery is connected correctly, so current will be sourced only into the gate of the FET. Use Equation 1 to calculate a value for the current limiting resistor (R<sub>limit</sub>).

(1)

$$R_{limit} > \frac{V_{VCP} - V_{BAT}}{I_{load}}$$

$$R_{limit} > \frac{10V}{12mA}$$

$$R_{limit} > 833\Omega$$

For other devices, BOOST or VCP pin can provide different output current limit and voltage, please check the datasheet and EVM design file to adjust the value.

The slew rate of the charge pump or boost regulator at startup will also limit the current. The FET will take longer to turn on for larger values of  $R_{\text{limit}}$ , which decreases efficiency at startup. Allowing for a larger current limit when possible will improve the efficiency.

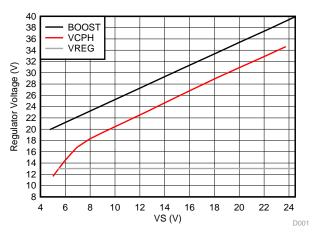

As shown in Figure 7, both integrated boost regulator output (such as: DRV3205-Q1) or integrated charge pump output VCP (such as: DRV8703-Q1) are referenced to the input supply and increase as it increases. Either of these regulators could supply the VGS required to turn on the NMOS even as the supply voltage changes.

Figure 7. Regulator Voltage versus VS

### 5 Comparison of Power Dissipation

A comparison of the power dissipation of the different circuits can be made by choosing a current and solving for the power. For an example, assume that 10 mA flows into the device DRV8703-Q1.

For Technique 1, if the forward voltage of the diode is 300 mV, use Equation 2 to calculate the power dissipation ( $P_D$ ).

$$P_D = IV$$

$$P_{D(diode)} = 10 \text{mA} \times 0.3 \text{V}$$

$$P_{D(diode)} = 3mW$$

(2)

For Technique 2, either a PMOS or NMOS can be used. With a 10-mA current, and assuming a PMOS with Rdson of 10 m $\Omega$ , use Equation 3 to calculate the P<sub>D</sub>.

$$P_D = IV = I^2R$$

$$P_{D(PMOS)} = (10mA)^2 \times 10m\Omega$$

$$P_{D(PMOS)} = 1uW$$

(3)

In general, a PMOS will have a higher Rdson for the same area (and therefore a higher cost) as an NMOS. With a 10-mA current and an NMOS with a 2-m $\Omega$  Rdson, use Equation 4 to calculate the P<sub>D</sub>.

$$P_D = IV = I^2R$$

$$P_{D(NMOS)} = (10mA)^2 \times 2m\Omega$$

$$P_{D(NMOS)} = 0.2uW$$

(4)

Technique 4 will have nearly identical performance as the single NMOS case. The power dissipated across the current limiting resistor at startup is negligible. Using an NMOS over a PMOS or diode for reverse battery protection has a clear power advantage.

The improvement in power dissipation offered by Technique 4 is clear when considering that the current of the entire system flows through the reverse polarity protection circuit. For example, if the average system current is 20 A the NMOS will dissipate only 0.8 W, while the single diode solution in Technique 1 would dissipate 6 W. The diode solution contributes significantly more heat and drives the efficiency of the system down.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated