ZHCSAJ2-DECEMBER 2012

# 可比吸了 NasePPTM 共宏/M

# 同步降压 NexFET™ 功率级

#### 特性

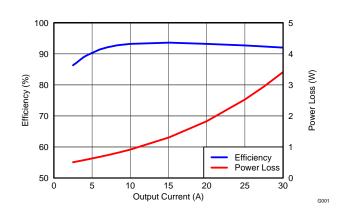

- 30A 电流下 92% 的系统效率

- 高频工作(高达 2MHz)

- 高密度 小外形尺寸无引线 (SON) 5mm × 6mm 封装

- 低功率损耗, 30A 时为 3.4W

- 超低电感封装

- 系统已优化的印刷电路板 (PCB) 封装

- 3.3V 和 5V 脉宽调制 (PWM) 信号兼容

- 3 态 PWM 输入

- 集成型自举二极管

- 预偏置启动保护

- 击穿保护

- 符合 RoHS 绿色环保标准-无铅端子镀层无卤素

# 应用范围

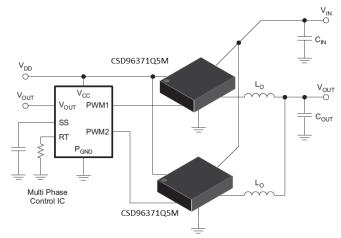

- 同步降压转换器

- 多相位同步降压转换器

- 负载点 (POL) 直流 (DC)-DC 转换器

- 内存和图形卡

- 台式机和服务器 VR11.x 和 VR12 V 内核同步降压 转换器

#### 订购信息

|     | 器件       | 封装                     | 介质          | 数量   | 出货   |

|-----|----------|------------------------|-------------|------|------|

| CSD | 96371Q5M | SON 5mm × 6mm 塑<br>料封装 | 13 英寸<br>卷带 | 2500 | 卷带封装 |

# 说明

CSD96371Q5M NexFET™ 功率级的设计针对高功率高密度同步降压转换器中的使用进行了优化。 这个产品集成了栅极驱动器集成电路 (IC) 和功率金属氧化物半导体场效应晶体管 (MOSFET) 来完善功率级开关功能。 这个组合在小型 5mm x 6mm 外形尺寸封装中提供高电流、高效和高速开关功能。 此外,已经对 PCB 封装进行了优化以帮助减少设计时间并简化总体系统设计。

Figure 2. Efficiency and Power Loss

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

NexFET is a trademark of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**(1)

$T_A = 25$ °C (unless otherwise noted)

|                                                    |                                                 | VALUE                         | UNIT |  |

|----------------------------------------------------|-------------------------------------------------|-------------------------------|------|--|

| V <sub>IN</sub> to P <sub>GND</sub> (2)            |                                                 | -0.3 to 16                    | V    |  |

| V <sub>DD</sub> to P <sub>GND</sub>                |                                                 | -0.3 to 6                     | V    |  |

| V <sub>SW</sub> to P <sub>GND</sub> -0.3 to 25     |                                                 |                               |      |  |

| V <sub>SW</sub> to P <sub>GND</sub> (              |                                                 |                               |      |  |

| ENABLE to $P_{GND}^{(3)}$ = -0.3 to $V_{DD}$ + 0.3 |                                                 |                               |      |  |

| PWM to P <sub>GND</sub>                            | PWM to $P_{GND}^{(3)}$ = -0.3 to $V_{DD}$ + 0.3 |                               |      |  |

| BOOT to BOO                                        | T_R <sup>(3)</sup>                              | -0.3 to V <sub>DD</sub> + 0.3 | V    |  |

| CCD Dating                                         | Human Body Model (HBM)                          | 2000                          | V    |  |

| ESD Rating                                         | Charged Device Model (CDM)                      | 500                           | V    |  |

| Power Dissipa                                      | ower Dissipation, P <sub>D</sub>                |                               | W    |  |

| Storage Temperature Range, T <sub>STG</sub>        |                                                 | -55 to 150                    | °C   |  |

| Operating Temperature Range, -40 to 150            |                                                 | °C                            |      |  |

<sup>(1)</sup> Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to Absolute Maximum rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

$T_{\Lambda} = 25^{\circ}$  (unless otherwise noted)

| Parameter                                               | Conditions                                                                             | MIN | MAX  | UNIT |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|------|

| Gate Drive Voltage, V <sub>DD</sub>                     |                                                                                        | 4.5 | 5.5  | V    |

| Input Supply Voltage, V <sub>IN</sub>                   |                                                                                        | 3.3 | 13.2 | V    |

| Output Voltage, V <sub>OUT</sub>                        |                                                                                        |     | 5.5  | V    |

| Continuous Output Current, I <sub>OUT</sub>             | $V_{IN} = 12V, V_{DD} = 5V, V_{OUT} = 1.2V, f_{SW} = 500kHz, L_{OUT} = 0.3\mu H^{(1)}$ |     | 50   | Α    |

| Peak Output Current, I <sub>OUT-PK</sub> <sup>(2)</sup> | $f_{SW} = 500 \text{kHz}, L_{OUT} = 0.3 \mu H^{(1)}$                                   |     | 75   | Α    |

| Switching Frequency, f <sub>SW</sub>                    | $C_{BST} = 0.1 \mu F \text{ (min)}$                                                    | 200 | 2000 | kHz  |

| On Time Duty Cycle                                      |                                                                                        |     | 85%  |      |

| Minimum PWM On Time                                     |                                                                                        | 40  |      | ns   |

| Operating Temperature                                   |                                                                                        | -40 | 125  | °C   |

<sup>(1)</sup> Measurement made with six 10-μF (TDK C3216X5R1C106KT or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins.

#### THERMAL INFORMATION

$T_A = 25$ °C (unless otherwise noted)

|                 | PARAMETER                                                            | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JC}$ | Thermal Resistance, Junction-to-Case (Top of package) <sup>(1)</sup> |     |     | 20  | °C/W |

| $R_{\theta JB}$ | Thermal Resistance, Junction-to-Board (2)                            |     |     | 2   | °C/W |

R<sub>BJC</sub> is determined with the device mounted on a 1-inch<sup>2</sup> (6.45-cm<sup>2</sup>), 2 oz. (0.071-mm thick) Cu pad on a 1.5-inch x 1.5-inch, 0.06-inch (1.52-mm) thick FR4 board.

<sup>(2)</sup>  $V_{IN}$  to  $V_{SW}$  Max = 27V for 10ns

<sup>(3)</sup> Should not exceed 6V

<sup>(2)</sup> System conditions as defined in Note 1. Peak Output Current is applied for  $t_p = 50\mu s$ .

<sup>(2)</sup> R<sub>0JB</sub> value based on hottest board temperature within 1mm of the package.

## **ELECTRICAL CHARACTERISTICS**

$T_A = 25$ °C,  $V_{DD} = POR$  to 5.5V (unless otherwise noted)

| PARAMETER                                                               | CONDITIONS                                                                                                                             | MIN | TYP  | MAX  | UNIT |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| P <sub>LOSS</sub>                                                       |                                                                                                                                        |     |      |      |      |

| Power Loss <sup>(1)</sup>                                               | $V_{IN} = 12V$ , $V_{DD} = 5V$ , $V_{OUT} = 1.2V$ , $I_{OUT} = 30A$ , $f_{SW} = 500kHz$ , $L_{OUT} = 0.29\mu H$ , $T_J = 25^{\circ}C$  |     | 3.4  | 3.7  | W    |

| Power Loss (2)                                                          | $V_{IN} = 12V$ , $V_{DD} = 5V$ , $V_{OUT} = 1.2V$ , $I_{OUT} = 50A$ , $f_{SW} = 500kHz$ , $L_{OUT} = 0.29\mu H$ , $T_J = 125^{\circ}C$ |     | 10.6 | 11.7 | W    |

| V <sub>IN</sub>                                                         |                                                                                                                                        |     |      |      |      |

| V <sub>IN</sub> Quiescent Current (I <sub>Q</sub> )                     | ENABLE = 0V, V <sub>DD</sub> = 5V                                                                                                      |     |      | 100  | μΑ   |

| $V_{DD}$                                                                |                                                                                                                                        |     |      |      |      |

| Standby Supply Current ( I <sub>DD</sub> )                              | ENABLE = 0V, PWM = 0V                                                                                                                  |     |      | 5    | μΑ   |

| Operating Supply Current (I <sub>DD</sub> )                             | ENABLE = 5V, PWM = 50% Duty cycle, f <sub>SW</sub> = 500kHz                                                                            |     | 21   | 25   | mA   |

| POWER-ON RESET AND UNDER VOLTAGE                                        | E LOCKOUT                                                                                                                              |     |      |      |      |

| Power on Reset (V <sub>DD</sub> Rising)                                 |                                                                                                                                        |     | 3.6  | 3.9  | V    |

| UVLO (V <sub>DD</sub> Falling)                                          |                                                                                                                                        | 3.4 | 3.5  |      | V    |

| Hysteresis                                                              |                                                                                                                                        | 100 |      | 250  | mV   |

| Startup Delay <sup>(3)</sup>                                            | ENABLE = PWM = 5V                                                                                                                      |     | 600  | 1000 | ns   |

| ENABLE                                                                  |                                                                                                                                        |     |      |      |      |

| Logic Level Low Threshold (V <sub>IL</sub> )                            |                                                                                                                                        | 0.8 | 1    |      | V    |

| Logic Level High Threshold (V <sub>IH</sub> )                           | Schmitt Trigger Input PWM = 5V (See Figure 5)                                                                                          |     | 1.6  | 2.0  | V    |

| Threshold Hysteresis                                                    |                                                                                                                                        |     | 580  |      | mV   |

| Weak Pull-down Impedance                                                |                                                                                                                                        |     | 100  |      | kΩ   |

| Rising Propagation Delay (t <sub>PDH</sub> )                            |                                                                                                                                        |     | 600  |      | ns   |

| Falling Propagation Delay (t <sub>PDL</sub> )                           |                                                                                                                                        |     | 200  |      | ns   |

| PWM                                                                     |                                                                                                                                        |     |      |      |      |

| I <sub>PWMH</sub>                                                       | PWM = 5V                                                                                                                               |     | 620  | 800  | μA   |

| I <sub>PWML</sub>                                                       | PWM = 0V                                                                                                                               |     | -260 | -340 | μA   |

| PWM Logic Level High (V <sub>PWMH</sub> )                               |                                                                                                                                        |     |      | 2.2  | V    |

| PWM Logic Level Low (V <sub>PWML</sub> )                                |                                                                                                                                        | 0.8 |      |      | V    |

| PWM 3-State open Voltage                                                |                                                                                                                                        |     | 1.5  |      | V    |

| PWM to VSW propagation delay (t <sub>PDLH</sub> and t <sub>PDHL</sub> ) | V <sub>DD</sub> = POR to 5.5V, C <sub>PWM</sub> = 10pF (See Figure 6)                                                                  | i)  |      |      | ns   |

| 3-State Shutdown Hold-off Time (t <sub>3HT</sub> )                      |                                                                                                                                        |     | 100  |      | ns   |

| 3-State Shutdown Propagation Delay (t <sub>3SD</sub> )                  |                                                                                                                                        |     | 650  |      | ns   |

| 3-State Recovery Propagation Delay (t <sub>3RD</sub> )                  |                                                                                                                                        |     |      |      | ns   |

| BOOTSTRAP SWITCH                                                        |                                                                                                                                        |     |      |      |      |

| Forward Voltage (V <sub>FBOOT</sub> )                                   | $V_{DD} - V_{BOOT}$ , $I_F = 20$ mA                                                                                                    |     | 180  | 360  | mV   |

| Reverse Leakage (I <sub>RBOOT</sub> ) <sup>(2)</sup>                    | $V_{BOOT} - V_{DD} = 20V$                                                                                                              |     | 0.15 | 1    | μA   |

<sup>(1)</sup> Measurement made with six 10-μF (TDK C3216X5R1C106KT or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins.

(2) Specified by design

(3) POR to V<sub>SW</sub> rising

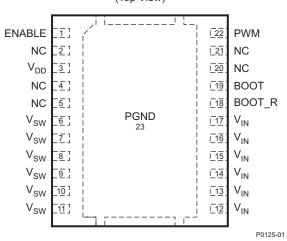

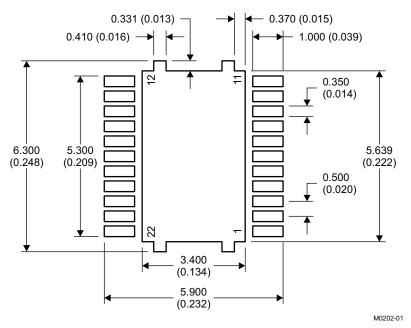

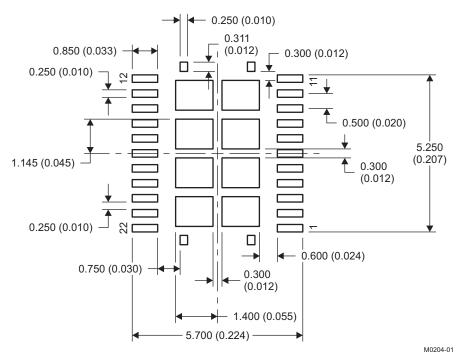

## **PIN CONFIGURATION**

SON 5mm × 6mm 22-Pin Package (Top View)

#### **PIN DESCRIPTION**

| PIN |                  | PERCEIPTION                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO. | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 1   | ENABLE           | Enables device operation. If ENABLE=logic HIGH, turns on the device. If ENABLE=logic LOW, the device is turned off and MOSFET gates are actively pulled low. An internal 100kΩ pull down resistor will pull the ENABLE pin LOW if left floating.                                                |  |  |  |  |  |

| 2   | NC               | Not for electrical connection, connect to floating pad only.                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3   | $V_{DD}$         | Supply Voltage to Gate Drivers and internal circuitry.                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4   | NC               | Not for electrical connection, connect to floating pad only.                                                                                                                                                                                                                                    |  |  |  |  |  |

| 5   | NC               | Not for electrical connection, connect to floating pad only.                                                                                                                                                                                                                                    |  |  |  |  |  |

| 6   | $V_{SW}$         | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 7   | $V_{SW}$         | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 8   | $V_{SW}$         | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 9   | $V_{SW}$         | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 10  | V <sub>SW</sub>  | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 11  | $V_{SW}$         | Voltage Switching Node – pin connection to the output inductor.                                                                                                                                                                                                                                 |  |  |  |  |  |

| 12  | V <sub>IN</sub>  | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 13  | V <sub>IN</sub>  | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 14  | $V_{IN}$         | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 15  | V <sub>IN</sub>  | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 16  | V <sub>IN</sub>  | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 17  | V <sub>IN</sub>  | Input Voltage Pin. Connect input capacitors close to this pin.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 18  | BOOT_R           | Bootstrap capacitor connection. Connect a minimum 0.1µF 16V X5R, ceramic cap from BOOT to BOOT_R pins. The                                                                                                                                                                                      |  |  |  |  |  |

| 19  | BOOT             | bootstrap capacitor provides the charge to turn on the Control FET. The bootstrap diode is integrated.                                                                                                                                                                                          |  |  |  |  |  |

| 20  | NC               | Not for electrical connection, connect to floating pad only.                                                                                                                                                                                                                                    |  |  |  |  |  |

| 21  | NC               | Not for electrical connection, connect to floating pad only.                                                                                                                                                                                                                                    |  |  |  |  |  |

| 22  | PWM              | Pulse Width modulated 3-state input from external controller. Logic Low sets Control FET gate low and Sync FET gate high. Logic High sets Control FET gate high and Sync FET gate Low. Open or High Z sets both MOSFET gates low if greater than the 3-State Shutdown Hold-off Time $(t_{3HT})$ |  |  |  |  |  |

| 23  | P <sub>GND</sub> | Power Ground                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

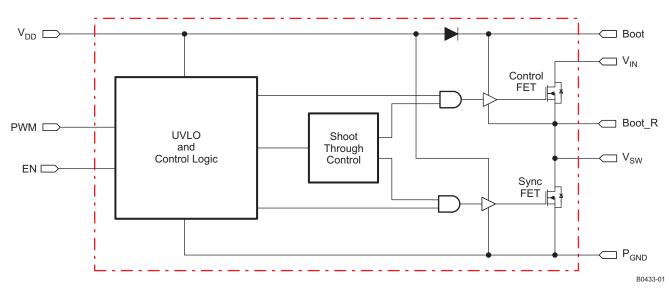

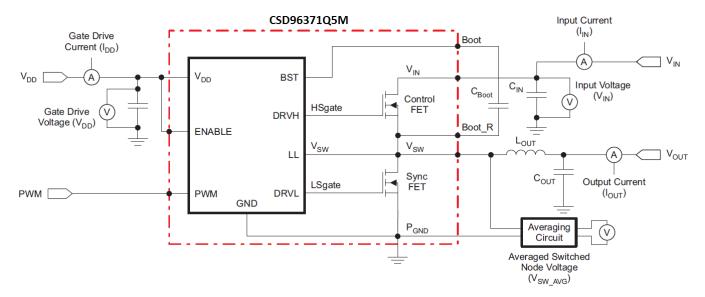

Figure 3. Functional Block Diagram

#### FUNCTIONAL DESCRIPTION

#### POWERING CSD96371Q5M AND GATE DRIVERS

An external V<sub>DD</sub> voltage is required to supply the integrated gate driver IC and provide the necessary gate drive power for the MOSFETS. The gate driver IC is capable of supplying in excess of 4 Amps peak current into the MOSFET gates to achieve fast switching. A 1uF 10V X5R or higher ceramic capacitor is recommended to bypass V<sub>DD</sub> pin to PGND. A bootstrap circuit to provide gate drive power for the Control FET is also included. The bootstrap supply to drive the Control FET is generated by connecting a 100nF 16V X5R ceramic capacitor between BOOT and BOOT\_R pins. An optional R<sub>BOOT</sub> resistor which can be used to slow down the turn on speed of the Control FET and reduce voltage spikes on the Vsw node. A typical  $1\Omega$  to  $4.7\Omega$  value is a compromise between switching loss and V<sub>SW</sub> spike amplitude.

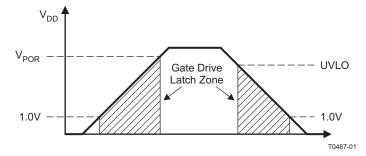

#### **UVLO (Under Voltage Lock Out)**

The V<sub>DD</sub> supply is monitored for UVLO conditions and both Control FET and Sync FET gates are held low until adequate supply is available. An internal comparator evaluates the  $V_{DD}$  voltage level and if  $V_{DD}$  is greater than the Power On Reset threshold (V<sub>POR</sub>) the gate driver becomes active. If V<sub>DD</sub> is less than the UVLO threshold, the gate driver is disabled and the internal MOSFET gates are actively driven low. At the rising edge of the V<sub>DD</sub> voltage, both Control FET and Sync FET gates will be actively held low during V<sub>DD</sub> transitions between 1.0V to V<sub>POR</sub>. This region is referred to the Gate Drive Latch Zone (see Figure 4). In addition, at the falling edge of the V<sub>DD</sub> voltage, both Control FET and Sync FET gates are actively held low during the UVLO to 1.0V transition.

The Power Stage CSD96371Q5M device must be powered up and Enabled before the PWM signal is applied.

Figure 4. POR and UVLO

# TEXAS INSTRUMENTS

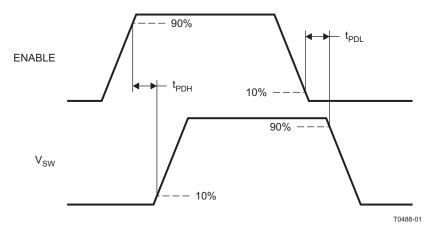

#### **ENABLE**

The ENABLE pin is TTL compatible. The logic level thresholds are sustained under all  $V_{DD}$  operating conditions between  $V_{POR}$  to  $V_{DD}$ . In addition, if this pin is left floating, a weak internal pull down resistor of  $100k\Omega$  will pull the ENABLE pin below the logic level low threshold. The operational functions of this pin should follow the timing diagram outlined in Figure 5. A logic level low will actively hold both Control FET and Sync FET gates low and  $V_{DD}$  pin should typically draw less than  $5\mu A$ .

#### **POWER UP SEQUENCING**

If the ENABLE signal is used, it is necessary to ensure proper co-ordination with the ENABLE and soft-start features of the external PWM controller in the system. If the CSD96371Q5M was disabled through ENABLE without sequencing with the PWM IC controller, the buck converter output will have no voltage or fall below regulation set point voltage. As a result, the PWM controller IC delivers Max duty cycle on the PWM line. If the Power Stage CSD96371Q5M is re-enabled by driving the ENABLE pin high, there will be an extremely large input inrush current when the output voltage builds back up again. The input inrush current might have undesirable consequences such as inductor saturation, driving the input power supply into current limit or even catastrophic failure of the CSD96371Q5M device. Disabling the PWM controller is recommended when the CSD96371Q5M is disabled. The PWM controller should always be re-enabled by going through soft-start routine to control and minimize the input inrush current and reduce current and voltage stress on all buck converter components. It is recommended that the external PWM controller be disabled when CSD96371Q5M is disabled or nonoperational because of UVLO.

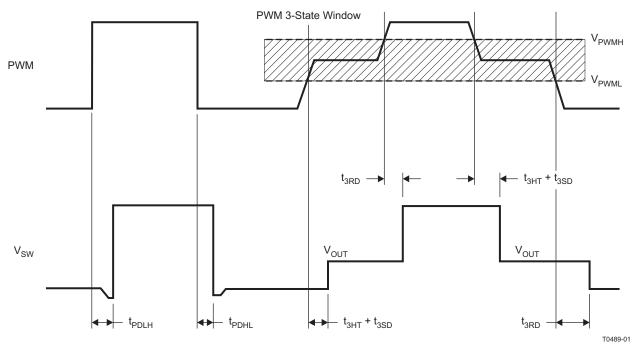

#### **PWM**

The input PWM pin incorporates a 3-State function. The Control FET and Sync FET gates are forced low if the PWM pin is left floating for more than the 3-State Hold off time ( $t_{3HT}$ ), typically 100ns. This requires the source impedance of the driving PWM signal to be a minimum of  $250k\Omega$  when in 3-State mode. Operation in and out of 3-State mode should follow the timing diagram outlined in Figure 6. Both  $V_{PWML}$  and  $V_{PWMH}$  threshold levels are set to accommodate both 3.3V and 5V logic controllers. During normal operation, the PWM signal should be driven to logic levels Low and High with a maximum of  $220\Omega/320\Omega$  sink/source impedance respectively.

#### **GATE DRIVERS**

The CSD96371Q5M has an internal high-performance gate driver IC that ensures minimum MOSFET dead-time while eliminating potential shoot-through currents. Propagation delays between the Control FET and Sync FET gates are kept to a minimum to minimize body diode conduction and improve efficiency. The gate driver IC incorporates an adaptive shoot through protection scheme which ensures that neither MOSFET is turned on while the other one is still conducting at the same time, preventing cross conduction. See Table 1.

**CONTROL FET ENABLE PWM SYNC FET GATE**  $V_{SW}$ **GATE** L Χ L ı 3-State Н <Min ON time L 3-State Н L Н L  $P_{GND}$ 3-State L 3-State Н L  $V_{IN}$ L = Logic Low; H = Logic High; X = Don't care; minimum on time = 40ns

**Table 1. Truth Table**

#### START UP IN PRE-BIASED OUTPUT VOLTAGE

The CSD96371Q5M incorporates a simple pre-bias feature to protect against the discharging of a prebiased output voltage and inducing large negative inductor currents. After the Power On Reset threshold is crossed and the ENABLE pin is set to logic level high, both internal MOSFETs are actively held low until the PWM pin receives a signal that crosses logic level high threshold and meets the minimum on time criteria (see the *Electrical Characteristics Table*). This allows the PWM control IC to provide a soft start routine that creates a monotonic startup of the output voltage. The pre-bias feature is enabled for a single event and subsequent PWM signals creates normal switching of the internal MOSFETs (see Table 1). To reactivate the pre-bias feature, the ENABLE pin needs to be pulled below logic level low or the V<sub>DD</sub> supply voltage needs to cross UVLO.

Figure 5. CSD96371Q5M ENABLE Timing Diagram ( $V_{DD} = PWM = 5V$ )

Figure 6. CSD96371Q5M PWM Timing Diagram

# TEXAS INSTRUMENTS

#### TYPICAL CHARACTERISTICS

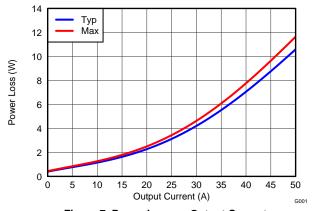

Test conditions:  $V_{IN}$  = 12V,  $V_{DD}$  = 5V,  $f_{SW}$ = 500kHz,  $V_{OUT}$  = 1.2V,  $L_{OUT}$  = 0.29 $\mu$ H, DCR = 0.54 $m\Omega$ ,  $T_J$  = 125 $^{\circ}$ C (Unless otherwise stated)

Figure 7. Power Loss vs Output Current

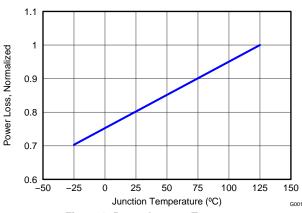

Figure 8. Power Loss vs Temperature

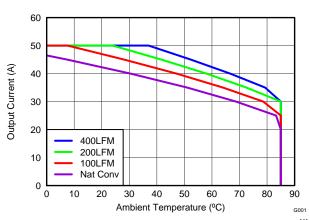

Figure 9. Safe Operating Area – PCB Horizontal Mount (1)

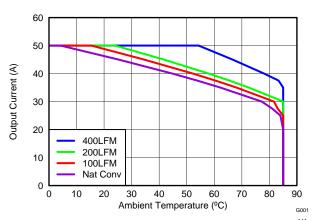

Figure 10. Safe Operating Area – PCB Vertical Mount (1)

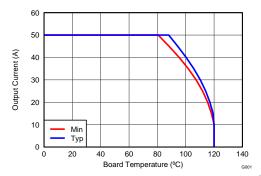

Figure 11. Typical and Min Safe Operating Area (1)

1. The Typical CSD96371Q5M System Characteristic curves are based on measurements made on a PCB design with dimensions of 4.0" (W) x 3.5" (L) x 0.062" (T) and 6 copper layers of 1 oz. copper thickness. See the *Application section* for detailed explanation.

# TYPICAL CHARACTERISTICS (continued)

Test conditions:  $V_{IN}$  = 12V,  $V_{DD}$  = 5V,  $f_{SW}$ = 500kHz,  $V_{OUT}$  = 1.2V,  $L_{OUT}$  = 0.29 $\mu$ H, DCR = 0.54 $m\Omega$ ,  $T_{J}$  = 125 $^{\circ}$ C (Unless otherwise stated)

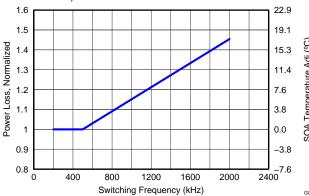

Figure 12. Normalized Power Loss vs Frequency

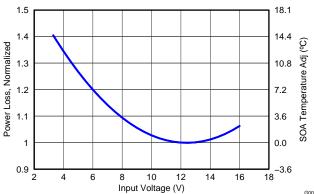

Figure 13. Normalized Power Loss vs Input Voltage

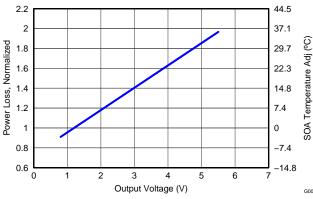

Figure 14. Normalized Power Loss vs Output Voltage

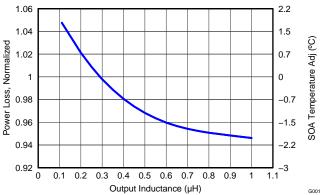

Figure 15. Normalized Power Loss vs Output Inductance

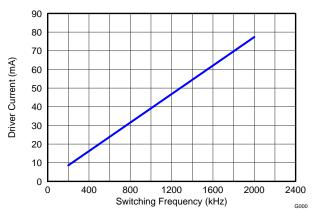

Figure 16. Driver Current vs Frequency

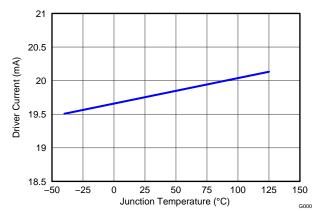

Figure 17. Driver Current vs Temperature

#### APPLICATION INFORMATION

The Power Stage CSD96371Q5M is a highly optimized design for synchronous buck applications using NexFET devices with a 5V gate drive. The Control FET and Sync FET silicon are parametrically tuned to yield the lowest power loss and highest system efficiency. As a result, a rating method is used that is tailored towards a more systems centric environment. The high-performance gate driver IC integrated in the package helps minimize the parasitics and results in extremely fast switching of the power MOSFETs. System level performance curves such as Power Loss, Safe Operating Area and normalized graphs allow engineers to predict the product performance in the actual application.

#### **Power Loss Curves**

MOSFET centric parameters such as  $R_{DS(ON)}$  and  $Q_{gd}$  are primarily needed by engineers to estimate the loss generated by the devices. In an effort to simplify the design process for engineers, Texas Instruments has provided measured power loss performance curves. Figure 7 plots the power loss of the CSD96371Q5M as a function of load current. This curve is measured by configuring and running the CSD96371Q5M as it would be in the final application (see Figure 18). The measured power loss is the CSD96371Q5M device power loss which consists of both input conversion loss and gate drive loss. Equation 1 is used to generate the power loss curve.

Power Loss =

$$(V_{IN} \times I_{IN}) + (V_{DD} \times I_{DD}) - (V_{SW AVG} \times I_{OUT})$$

(1)

The power loss curve in Figure 7 is measured at the maximum recommended junction temperature of  $T_J = 125$ °C under isothermal test conditions.

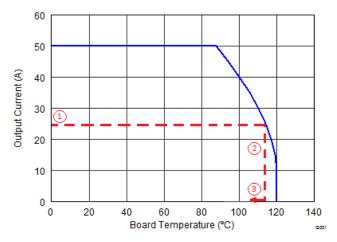

### Safe Operating Curves (SOA)

The SOA curves in the CSD96371Q5M datasheet give engineers guidance on the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. Figure 9, Figure 10, and Figure 11 outline the temperature and airflow conditions required for a given load current. The area under the curve dictates the safe operating area. All the curves are based on measurements made on a PCB design with dimensions of 4.0" (W) x 3.5" (L) x 0.062" (T) and 6 copper layers of 1 oz. copper thickness.

#### **Normalized Curves**

The normalized curves in the CSD96371Q5M data sheet give engineers guidance on the Power Loss and SOA adjustments based on their application specific needs. These curves show how the power loss and SOA boundaries will adjust for a given set of systems conditions. The primary Y-axis is the normalized change in power loss and the secondary Y-axis is the change is system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the Power Loss curve and the change in temperature is subtracted from the SOA curve.

Figure 18. Power Loss Test Circuit

### Calculating Power Loss and SOA

The user can estimate product loss and SOA boundaries by arithmetic means (see the Design Example). Though the Power Loss and SOA curves in this datasheet are taken for a specific set of test conditions, the following procedure will outline the steps engineers should take to predict product performance for any set of system conditions.

#### **Design Example**

Operating Conditions: Output Current ( $I_{OUT}$ ) = 25A, Input Voltage ( $V_{IN}$ ) = 7V, Output Voltage ( $V_{OUT}$ ) = 1V, Switching Frequency ( $I_{SW}$ ) = 800kHz, Output Inductor ( $I_{OUT}$ ) = 0.2 $I_{IN}$ H

#### **Calculating Power Loss**

- Power Loss at 25A = 3.1W (Figure 7)

- Normalized Power Loss for switching frequency ≈ 1.09 (Figure 12)

- Normalized Power Loss for input voltage ≈ 1.15 (Figure 13)

- Normalized Power Loss for output voltage ≈ 0.95 (Figure 14)

- Normalized Power Loss for output inductor ≈ 1.02 (Figure 15)

- Final calculated Power Loss = 3.1W x 1.09 x 1.15 x 0.95 x 1.02 ≈ 3.8W

#### **Calculating SOA Adjustments**

- SOA adjustment for switching frequency ≈ 3.4°C (Figure 12)

- SOA adjustment for input voltage ≈ 5.4°C (Figure 13)

- SOA adjustment for output voltage ≈ -7.7°C (Figure 14)

- SOA adjustment for output inductor ≈ 1.7°C (Figure 15)

- Final calculated SOA adjustment = 3.4 + 5.4 + (-1.9) + 0.7 ≈ 7.6°C

Figure 19. Power Stage CSD96371Q5M SOA

In the design example above, the estimated power loss of the CSD96371Q5M would increase to 3.8W. In addition, the maximum allowable board and/or ambient temperature would have to decrease by 7.6°C. Figure 19 graphically shows how the SOA curve would be adjusted accordingly.

- 1. Start by drawing a horizontal line from the application current to the SOA curve.

- 2. Draw a vertical line from the SOA curve intercept down to the board/ambient temperature.

- 3. Adjust the SOA board/ambient temperature by subtracting the temperature adjustment value.

In the design example, the SOA temperature adjustment yields a reduction in allowable board/ambient temperature of 7.6°C. In the event the adjustment value is a negative number, subtracting the negative number would yield an increase in allowable board/ambient temperature.

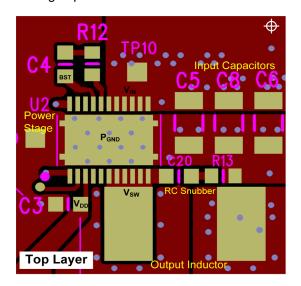

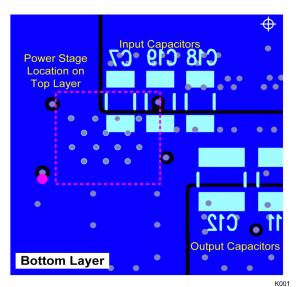

#### RECOMMENDED PCB DESIGN OVERVIEW

There are two key system-level parameters that can be addressed with a proper PCB design: electrical and thermal performance. Properly optimizing the PCB layout will yield maximum performance in both areas. Below is a brief description on how to address each parameter.

#### **Electrical Performance**

The CSD96371Q5M has the ability to switch at voltages rates greater than 10kV/µs. Special care must be then taken with the PCB layout design and placement of the input capacitors, inductor and output capacitors.

- The placement of the input capacitors relative to V<sub>IN</sub> and P<sub>GND</sub> pins of CSD96371Q5M device should have the highest priority during the component placement routine. It is critical to minimize these node lengths. As such, ceramic input capacitors need to be placed as close as possible to the V<sub>IN</sub> and P<sub>GND</sub> pins (see Figure 20). The example in Figure 20 uses 6 x 10μF 1206 25V ceramic capacitors (TDK Part # C3216X5R1C106KT or equivalent). Notice there are ceramic capacitors on both sides of the board with an appropriate amount of vias interconnecting both layers. In terms of priority of placement next to the Power Stage C5, C8 and C7, C19 should follow in order.

- The bootstrap cap C<sub>BOOT</sub> 0.1μF 0603 16V ceramic capacitor should be closely connected between BOOT and BOOT R pins

- The switching node of the output inductor should be placed relatively close to the Power Stage CSD96371Q5M V<sub>SW</sub> pins. Minimizing the V<sub>SW</sub> node length between these two components will reduce the PCB conduction losses and actually reduce the switching noise level. (1)

#### **Thermal Performance**

The CSD96371Q5M has the ability to use the GND planes as the primary thermal path. As such, the use of thermal vias is an effective way to pull away heat from the device and into the system board. Concerns of solder voids and manufacturability problems can be addressed by the use of three basic tactics to minimize the amount of solder attach that will wick down the via barrel:

- Intentionally space out the vias from each other to avoid a cluster of holes in a given area.

- Use the smallest drill size allowed in your design. The example in Figure 20 uses vias with a 10 mil drill hole and a 16 mil capture pad.

- Tent the opposite side of the via with solder-mask.

In the end, the number and drill size of the thermal vias should align with the end user's PCB design rules and manufacturing capabilities.

Figure 20. Recommended PCB Layout (Top Down View)

Keong W. Kam, David Pommerenke, "EMI Analysis Methods for Synchronous Buck Converter EMI Root Cause Analysis", University of Missouri – Rolla

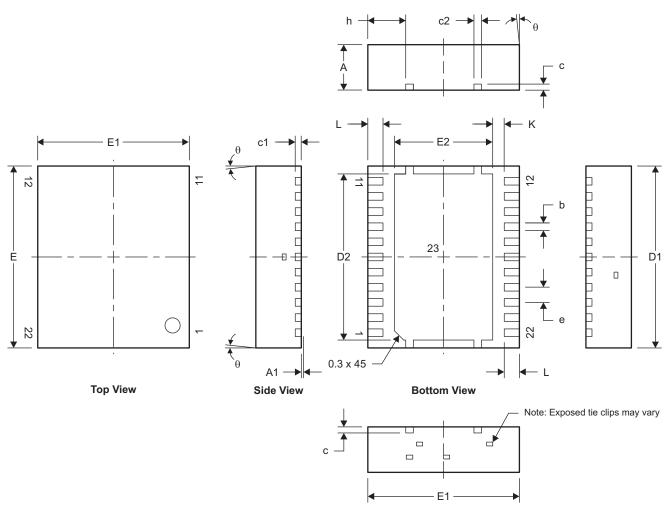

# **MECHANICAL DATA**

M0201-01

| DIM |       | MILLIMETERS INCHES |       |           |           |       |

|-----|-------|--------------------|-------|-----------|-----------|-------|

| DIM | Min   | Nom                | Max   | Min       | Nom       | Max   |

| А   | 1.400 | 1.450              | 1.500 | 0.055     | 0.057     | 0.059 |

| A1  | 0.000 | 0.000              | 0.050 | 0.000     | 0.000     | 0.002 |

| b   | 0.200 | 0.250              | 0.350 | 0.008     | 0.010     | 0.014 |

| С   | 0.150 | 0.200              | 0.250 | 0.006     | 0.008     | 0.010 |

| c1  | 0.150 | 0.200              | 0.250 | 0.006     | 0.008     | 0.010 |

| c2  | 0.200 | 0.250              | 0.300 | 0.008     | 0.010     | 0.012 |

| D1  | 5.900 | 6.000              | 6.100 | 0.232     | 0.236     | 0.240 |

| D2  | 5.379 | 5.479              | 5.579 | 0.212     | 0.216     | 0.220 |

| Е   | 5.900 | 6.000              | 6.100 | 0.232     | 0.236     | 0.240 |

| E1  | 4.900 | 5.000              | 5.100 | 0.193     | 0.197     | 0.201 |

| E2  | 3.140 | 3.240              | 3.340 | 0.124     | 0.128     | 0.132 |

| е   |       | 0.500 TYP          |       | 0.020 TYP |           |       |

| h   | 1.150 | 1.250              | 1.350 | 0.045     | 0.049     | 0.053 |

| K   |       | 0.380 TYP          |       |           | 0.015 TYP |       |

| L   | 0.400 | 0.500              | 0.600 | 0.016     | 0.020     | 0.024 |

| θ   | 0.00  | _                  | _     | 0.00      | _         | _     |

# TEXAS INSTRUMENTS

#### **Land Pattern Recommendation**

NOTE: Dimensions are in mm (inches).

# **Stencil Recommendation**

NOTE: Dimensions are in mm (inches).

11-Nov-2025 www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins       | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| CSD96371Q5M           | Active | Production    | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt     | NIPDAU                        | Level-2-260C-1 YEAR        | -55 to 150   | 96371M           |

| CSD96371Q5M.B         | Active | Production    | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | -               | Call TI                       | Call TI                    | -55 to 150   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No. RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月