**DRV8308**

ZHCSC39B - FEBRUARY 2014 - REVISED NOVEMBER 2017

# DRV8308 无刷直流电机控制器

## 特性

- 三相无刷直流电机控制器

- 具有可编程增益和滤波器的数字闭环速度控制

- 通过 10 至 130mA 可配置栅极驱动器驱动 6 个 N 沟道 MOSFET

- 通过霍尔传感器实现换向

- 时序可提前/延迟

- 120°或 180°正弦电流控制

- 通过单输入控制电机转速

- 工作电源电压范围: 8.5V 至 32V

- 灵活的配置方法

- 读取内部非易失性存储器

- 读取外部 EEPROM

- 写入串行外设接口 (SPI)

- 可配置的电机限流器

- 针对霍尔传感器的 5V 稳压器

- 低功耗待机模式

- 集成过流、过压和过热保护

## 2 应用

- 工业泵、风扇和阀门

- 白色家电

- 电动工具和草坪设备

- 打印机

#### 3 说明

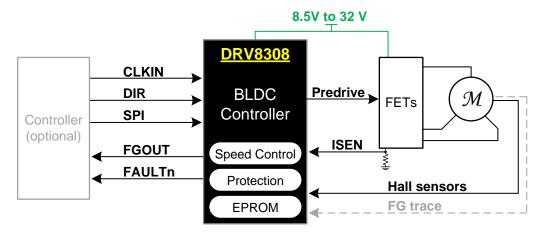

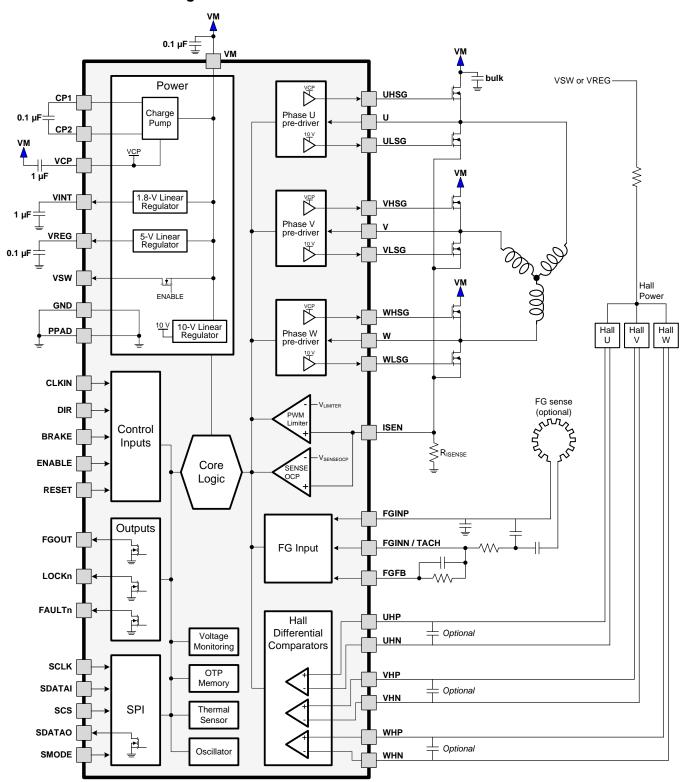

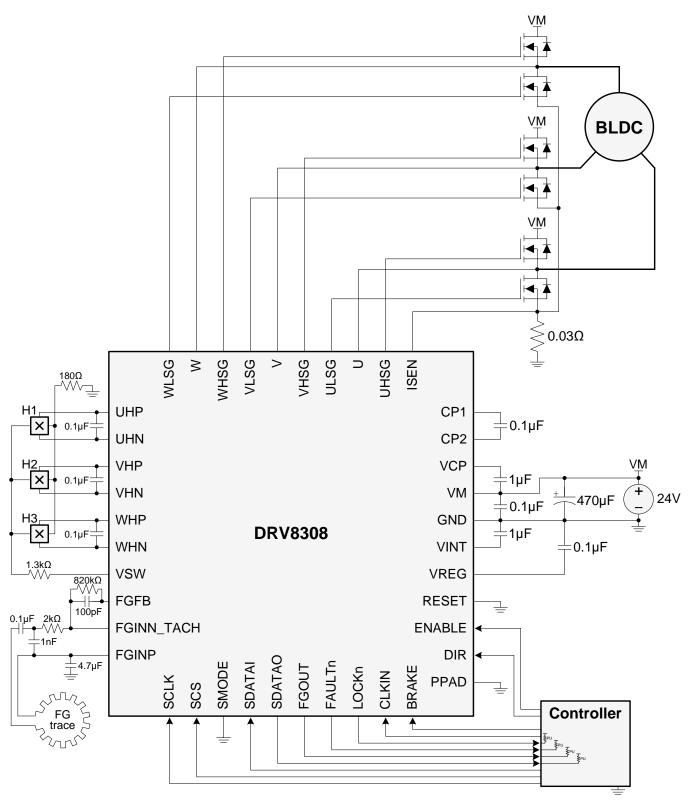

DRV8308 采用高级功能和一个简单的输入接口来 控制 传感器式无刷直流电机作为前置驱动器,它可在 10mA 至 130mA 范围内配置电流以驱动 6 个外部 N 沟道 MOSFET 的栅极,从而实现优异的开关特性。

3 个电机相位根据霍尔传感器输入进行换向。当电机达 到稳定速度后, DRV8308 控制器可仅使用 1 个霍尔传 感器将传感器失配导致的抖动降至最少。霍尔信号驱动 时序可提前或延迟 0.1% 以优化电源效率。可选 180° 换向模式可驱动通过电机的正弦电流,并最大限度减少 可闻噪声和转矩波纹。电机峰值电流可通过调整感测电 阻进行控制。

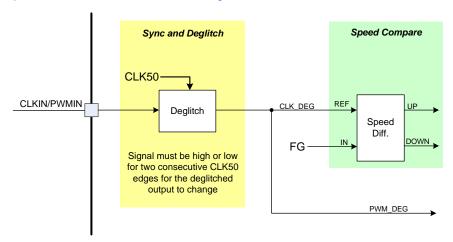

DRV8308 控制器实现了闭环速度控制,能够使电机在 较宽的负载转矩范围内以精准的转速运转。此系统会将 FG 走线或霍尔传感器生成的电机速度与 CLKIN 引脚 的基准频率相匹配。DRV8308 控制器也可利用占空比 命令(通过时钟或寄存器设置实现)来驱动电机开环。

DRV8308 具备多重保护 特性, 增强了系统的稳健 性, 例如可处理并报告过流、过压、低压和过热等故 障。

#### 器件信息(1)

|         | * * * * * * * * * * * * * * * * * * * * |                 |

|---------|-----------------------------------------|-----------------|

| 器件型号    | 封装                                      | 封装尺寸 (标称值)      |

| DRV8308 | VQFN (40)                               | 6.00mm x 6.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

## 简化的原理图

| 1 | 特性1                                  |    | 7.5 Programming                | 35 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                 |    | 7.6 Register Map               | 36 |

| 3 | 说明 1                                 | 8  | Application and Implementation | 41 |

| 4 | 修订历史记录 2                             |    | 8.1 Application Information    | 41 |

| 5 | Pin Configurations and Functions     |    | 8.2 Typical Application        | 44 |

| 6 | Specifications6                      |    | 8.3 Do's and Don'ts            | 49 |

| U | 6.1 Absolute Maximum Ratings         | 9  | Power Supply Recommendations   | 50 |

|   | 6.2 Handling Ratings                 | 10 | Layout                         | 50 |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines         |    |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example            |    |

|   | 6.5 Electrical Characteristics 8     | 11 | 器件和文档支持                        |    |

|   | 6.6 SPI Timing Requirements          |    | 11.1 文档支持                      |    |

|   | 6.7 Typical Characteristics          |    | 11.2 接收文档更新通知                  | 51 |

| 7 | Detailed Description 12              |    | 11.3 社区资源                      | 51 |

| • | 7.1 Overview                         |    | 11.4 商标                        | 51 |

|   | 7.2 Functional Block Diagram         |    | 11.5 静电放电警告                    | 51 |

|   | 7.3 Feature Description              |    | 11.6 Glossary                  | 51 |

|   | 7.4 Device Functional Modes          | 12 | 机械、封装和可订购信息                    |    |

|   |                                      |    |                                |    |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Revision A (October 2014) to Revision B **Page** Deleted extra notes in the Thermal Information table (refer to the Semiconductor and IC Package Thermal Metrics Changes from Original (February 2014) to Revision A Page Added Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation

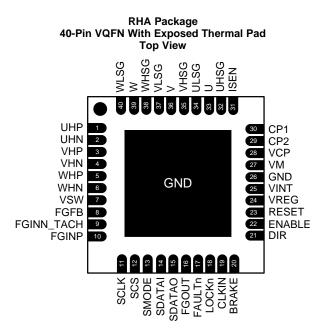

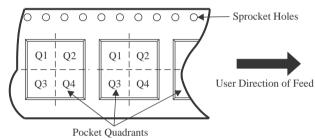

# 5 Pin Configurations and Functions

#### **Pin Functions**

| PIN FUNCTIONS |          |                    |                                                                                                     |                                                                                                                                                                                                            |  |

|---------------|----------|--------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               |          | I/O <sup>(1)</sup> | DESCRIPTION                                                                                         | EXTERNAL COMPONENTS OR CONNECTIONS                                                                                                                                                                         |  |

| NAME          | NO.      | 1/0                | DESCRIPTION                                                                                         | EXTERNAL COMPONENTS ON CONNECTIONS                                                                                                                                                                         |  |

| POWER AND     | ROUND    |                    |                                                                                                     |                                                                                                                                                                                                            |  |

| CP1           | 30       | PWR                | Charge nump flying conscitor                                                                        | Connect a 0.1-μF 35-V capacitor between CP1 and CP2                                                                                                                                                        |  |

| CP2           | 29       | PWR                | Charge pump flying capacitor                                                                        | Connect a 0.1-µF 35-V capacitor between CP1 and CP2                                                                                                                                                        |  |

| GND           | 26, PPAD | PWR                | Ground reference. Pin 26 and the exposed thermal pad are internally connected.                      | Connect to board GND                                                                                                                                                                                       |  |

| VCP           | 28       | PWR                | Charge pump storage capacitor                                                                       | Connect a 1-μF 35-V ceramic capacitor to VM                                                                                                                                                                |  |

| VINT          | 25       | PWR                | Internal 1.8-V core voltage regulator bypass                                                        | Bypass to GND with a 1-μF 6.3-V ceramic capacitor                                                                                                                                                          |  |

| VM            | 27       | PWR                | Motor supply voltage                                                                                | Connect to motor supply voltage. Bypass to GND with a 0.1- $\mu$ F ceramic capacitor, plus a large electrolytic capacitor (47 $\mu$ F or larger is recommended), with a voltage rating of 1.5x to 2.5x VM. |  |

| VREG          | 24       | PWR                | 5-V regulator output. Active when ENABLE is active.                                                 | Bypass to GND with a 0.1- $\mu$ F 10-V ceramic capacitor. Can provide 5-V power to Hall sensors.                                                                                                           |  |

| vsw           | 7        | PWR                | Switched VM power output. When ENABLE is active, VM is applied to this pin.                         | Can be used for powering Hall elements, along with added series resistance.                                                                                                                                |  |

| CONTROL       |          | •                  |                                                                                                     |                                                                                                                                                                                                            |  |

| BRAKE         | 20       | I                  | Causes motor to brake. Polarity is programmable. Internal pulldown resistor.                        |                                                                                                                                                                                                            |  |

| CLKIN         | 19       | I                  | The clock input, used in Clock<br>Frequency Mode and Clock PWM<br>Mode. Internal pulldown resistor. |                                                                                                                                                                                                            |  |

| DIR           | 21       | I                  | Sets motor rotation direction. Polarity is programmable. Internal pulldown resistor.                |                                                                                                                                                                                                            |  |

## Pin Functions (continued)

| PIN                 |          |                    | ,                                                                                         | ,                                                                                                                                                                          |  |

|---------------------|----------|--------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | NO.      | I/O <sup>(1)</sup> | DESCRIPTION                                                                               | EXTERNAL COMPONENTS OR CONNECTIONS                                                                                                                                         |  |

| ENABLE              | 22       | 1                  | Enables and disables motor. Polarity is programmable. Internal pulldown resistor.         |                                                                                                                                                                            |  |

| FAULTn              | 17       | OD                 | Fault indicator – active low when overcurrent, or overtemperature. Opendrain output.      |                                                                                                                                                                            |  |

| FGOUT               | 16       | OD                 | Outputs a TACH signal generated from the FG amplifier or Hall sensors. Open-drain output. |                                                                                                                                                                            |  |

| LOCKn               | 18       | OD                 | Outputs a signal that indicates the speed loop is locked. Open-drain output.              |                                                                                                                                                                            |  |

| RESET               | 23       | I                  | Active high to reset all internal logic. Internal pulldown resistor.                      |                                                                                                                                                                            |  |

| SERIAL INTER        | ACE      |                    |                                                                                           |                                                                                                                                                                            |  |

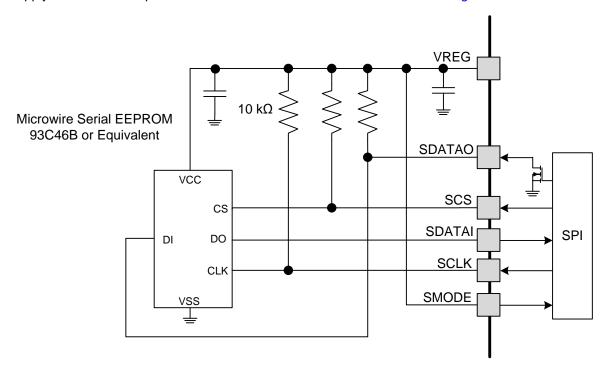

| SCLK <sup>(2)</sup> | 11       | I/OD               | Serial clock                                                                              | SPI mode: Serial clock input. Data is clocked on rising edges. Internal pulldown resistor. EEPROM mode: Connect to EEPROM CLK. Open-drain output requires external pullup. |  |

| SCS <sup>(2)</sup>  | 12       | I/OD               | Serial chip select                                                                        | SPI mode: Active high enables serial interface operation. Internal pulldown resistor. EEPROM mode: Connect to EEPROM CS. Open-drain output requires external pullup.       |  |

| SDATAI              | 14       | I                  | Serial data input                                                                         | SPI mode: Serial data input. Internal pulldown resistor. EEPROM mode: Serial data input. Connect to EEPROM terminal.                                                       |  |

| SDATAO              | 15       | OD                 | Serial data output                                                                        | SPI mode: Serial data output. Open-drain output. EEPROM mode: Connect to EEPROM DI. Open-drain output requires external pullup.                                            |  |

| SMODE               | 13       | I                  | Serial mode                                                                               | SPI mode: leave open or connect to ground for SPI interface mode.  EEPROM mode: Connect to logic high to for EEPROM mode.                                                  |  |

| POWER STAGE         | INTERFAC | E                  |                                                                                           |                                                                                                                                                                            |  |

| ISEN                | 31       | I                  | Low-side current sense resistor                                                           | Connect to low-side current sense resistor                                                                                                                                 |  |

| U                   | 33       | 1                  |                                                                                           |                                                                                                                                                                            |  |

| V                   | 36       | I                  | Measures motor phase voltages for VFETOCP                                                 | Connect to motor windings                                                                                                                                                  |  |

| W                   | 39       | I                  | V FETOCP                                                                                  |                                                                                                                                                                            |  |

| UHSG                | 32       | 0                  |                                                                                           |                                                                                                                                                                            |  |

| VHSG                | 35       | 0                  | High-side FET gate outputs                                                                | Connect to high-side 1/2-H N-channel FET gate                                                                                                                              |  |

| WHSG                | 38       | 0                  | · - · · · ·                                                                               |                                                                                                                                                                            |  |

| ULSG                | 34       | 0                  |                                                                                           |                                                                                                                                                                            |  |

| VLSG                | 37       | 0                  | Low-side FET gate outputs                                                                 | Connect to low-side 1/2-H N-channel FET gate                                                                                                                               |  |

| WLSG                | 40       | 0                  | -                                                                                         |                                                                                                                                                                            |  |

| HALL AND FG         | NTERFACE | •                  |                                                                                           |                                                                                                                                                                            |  |

| FGFB                | 8        | 0                  | FG amplifier feedback pin                                                                 | Connect feedback network to FGIN-                                                                                                                                          |  |

| FGINN_TACH          | 9        | I <sup>(3)</sup>   | FG amplifier negative input or TACH input                                                 | Connect to FG trace and filter components. When using a TACH with FGSEL= 3, connect a logic-level TACH signal. If unused, connect FGFB to FG                               |  |

| FGINP               | 10       | I/O                | FG amplifier positive input                                                               | Connect to FG trace and filter components on the PCB (if used).                                                                                                            |  |

<sup>(2)</sup> In SPI mode, these pins are inputs; in EEPROM mode, they are open-drain outputs.(3) When using FG amplifier, this pin is an analog input. If in TACH mode, this is a logic-level input.

# Pin Functions (continued)

| PIN  |     | I/O <sup>(1)</sup> | DESCRIPTION                  | EVTERNAL COMPONENTS OF CONNECTIONS                      |  |  |  |  |

|------|-----|--------------------|------------------------------|---------------------------------------------------------|--|--|--|--|

| NAME | NO. | 1/0                | DESCRIPTION                  | EXTERNAL COMPONENTS OR CONNECTIONS                      |  |  |  |  |

| UHP  | 1   | I                  | Hall sensor U positive input |                                                         |  |  |  |  |

| UHN  | 2   | I                  | Hall sensor U negative input |                                                         |  |  |  |  |

| VHP  | 3   | I                  | Hall sensor V positive input | Connect to Hall sensors. Noise filter capacitors may be |  |  |  |  |

| VHN  | 4   | - 1                | Hall sensor V negative input | desirable, connected between the + and – Hall inputs.   |  |  |  |  |

| WHP  | 5   | - 1                | Hall sensor W positive input |                                                         |  |  |  |  |

| WHN  | 6   | I                  | Hall sensor W negative input |                                                         |  |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1) (2) (3)

|                                                                                                                                          | MIN         | MAX         | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------|

| Power supply voltage (VM)                                                                                                                | -0.3        | 42          | V    |

| Charge pump and high side gate drivers (VCP, UHSG, VHSG, WHSG)                                                                           | -0.3        | 50          | V    |

| Output pin, low side gate drivers, charge pump flying cap and switched VM power supply voltage (U, V, W, ULSG, VLSG, WLSG, CP1, CP2 VSW) | -0.6        | 40          | V    |

| Internal core voltage regulator (VINT)                                                                                                   | -0.3        | 2           | V    |

| Linear voltage regulator output (VREG)                                                                                                   | -0.3        | 5.5         | V    |

| Sense current pin (ISEN)                                                                                                                 | -0.3        | 2           | V    |

| Digital pin voltage range (SCLK, SCS, SMODE, SDATAI, SDATAO, FGOUT, FAULTn, LOCKn, CLKIN, BRAKE, DIR, ENABLE, RESET)                     | -0.5        | 5.75        | V    |

| Hall sensor input pin voltage (UHP, UHN, VHP, VHN, WHP, WHN, FGFB, FGINN/TACH, FGINP)                                                    | 0           | VREG        | V    |

| Continuous total power dissipation                                                                                                       | See Thermal | Information |      |

| Operating junction temperature range, T <sub>J</sub>                                                                                     | -40         | 150         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground pin.

6.2 Handling Ratings

|                    |                                                                                      |                                                                               | MIN   | MAX  | UNIT |

|--------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub>   | Storage temperature range    Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all |                                                                               | -60   | 150  | °C   |

| V                  | Electrostatic discharge                                                              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | -4000 | 4000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge                                                              | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -1500 | 1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                   |                                                         | MIN | NOM MAX           | UNIT |

|--------------------|-----------------------------------|---------------------------------------------------------|-----|-------------------|------|

| $V_{M}$            | Motor power supply vo             | Itage range, ENABLE = 1, motor operating <sup>(1)</sup> | 8.5 | 32                | V    |

| $V_{MDIS}$         | Motor power supply vo             | Itage range, ENABLE = 0, motor not operating            | 4.5 | 35                | V    |

| $I_{VREG}$         | VREG output current (2            |                                                         | 0   | 30                | A    |

| I <sub>VSW</sub>   | VSW output current <sup>(2)</sup> |                                                         | 0   | 30                | mA   |

| f <sub>HALL</sub>  | Hall sensor input frequ           | ency <sup>(3)</sup>                                     | 0   | 30                |      |

|                    | Francisco en CLIVINI              | SPDMODE = 00 (Clock Frequency Mode)                     | 0   | 90                | kHz  |

| f <sub>CLKIN</sub> | Frequency on CLKIN                | SPDMODE = 01 (Clock PWM Mode)                           | 16  | 50 <sup>(4)</sup> |      |

- (1) Note that at VM < 12 V, gate drive output voltage tracks VM voltage

- (2) Power dissipation and thermal limits must be observed

- (3) f<sub>HALL</sub> of 50 Hz to 6.7 kHz is best

- (4) Operational with frequencies above 50 kHz, but resolution is degraded

<sup>(3)</sup> Power dissipation and thermal limits must be observed

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.4 Thermal Information

|                      |                                              | DRV8308    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHA (VQFN) | UNIT |

|                      |                                              | 40 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 23         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.8        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.8        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.3        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                      | TEST CONDITIONS                                                                      | MIN  | TYP                     | MAX  | UNIT |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------|------|-------------------------|------|------|

| VM SUPI             | PLY                                            |                                                                                      |      |                         |      |      |

| I <sub>VM</sub>     | VM active current                              | ENABLE = active,<br>VREG and VSW open                                                |      | 12                      | 18   | mA   |

| I <sub>STBY</sub>   | VM standby current                             | ENABLE = inactive                                                                    |      |                         | 120  | μA   |

| V                   | VM logic reset voltage                         | VM falling                                                                           |      |                         | 4.6  | V    |

| V <sub>RESET</sub>  | vivi logic reset voltage                       | VM rising                                                                            | 5    |                         |      | V    |

| VREG SI             | UPPLY                                          |                                                                                      |      |                         |      |      |

| $V_{VREG}$          | Output voltage                                 | I <sub>OUT</sub> = 1 to 30 mA                                                        | 4.75 | 5                       | 5.25 | V    |

| I <sub>VREG</sub>   | Output current                                 |                                                                                      |      |                         | 30   | mA   |

| vsw su              | PPLY                                           |                                                                                      |      |                         |      |      |

| R <sub>DS(ON)</sub> | VSW switch on-resistance                       | I <sub>OUT</sub> = 1 to 30 mA                                                        |      | 9                       | 20   | Ω    |

| I <sub>VSW</sub>    | Output current                                 |                                                                                      |      |                         | 30   | mA   |

| INTERNA             | AL CLOCK OSCILLATOR                            |                                                                                      |      |                         | *    |      |

| f <sub>CLK50</sub>  | Internal CLK50 clock frequency                 |                                                                                      |      | 50                      |      | MHz  |

|                     | EVEL INPUTS AND OUTPUTS                        | <del> </del>                                                                         |      |                         | l    |      |

| V <sub>IL</sub>     | Low-level input voltage                        |                                                                                      |      |                         | 0.8  | V    |

| V <sub>IH</sub>     | High-level input voltage                       |                                                                                      | 1.5  |                         | 5.5  | V    |

| I <sub>IL</sub>     | Low-level input current                        |                                                                                      | -50  |                         | 50   | μA   |

| I <sub>IH</sub>     | High-level input current                       | V <sub>IN</sub> = 3.3 V, RESET,<br>DIR, BRAKE, CLKIN,<br>SCS, SCLK, SDATAI,<br>SMODE | 20   |                         | 100  | μA   |

|                     |                                                | V <sub>IN</sub> = 3.3 V, ENABLE                                                      | 6    |                         | 9    |      |

| $V_{HYS}$           | Input hysteresis voltage                       |                                                                                      | 0.1  | 0.3                     | 0.5  | V    |

| R <sub>PD</sub>     | Input pulldown resistance                      | RESET, DIR, BRAKE,<br>CLKIN, SCS, SCLK,<br>SDATAI, SMODE                             | 50   | 100                     | 150  | kΩ   |

|                     |                                                | ENABLE                                                                               | 350  |                         | 550  |      |

| OPEN DI             | RAIN OUTPUTS                                   |                                                                                      |      |                         |      |      |

| V <sub>OL</sub>     | Low-level output voltage                       | I <sub>OUT</sub> = 2.0 mA                                                            |      |                         | 0.5  | V    |

| I <sub>OH</sub>     | Output leakage current                         | V <sub>OUT</sub> = 3.3 V                                                             |      |                         | 1    | μΑ   |

| FG AMP              | LIFIER AND COMPARATOR                          |                                                                                      |      |                         |      |      |

| V <sub>IO</sub>     | FG amplifier input offset voltage              |                                                                                      | -7   |                         | 7    | mV   |

| I <sub>IB</sub>     | FG amplifier input bias current                |                                                                                      | -1   |                         | 1    | μΑ   |

| V <sub>ICM</sub>    | FG amplifier input common mode voltage range   |                                                                                      | 1.5  |                         | 3.5  | V    |

| A <sub>V</sub>      | FG amplifier open loop voltage gain            |                                                                                      | 45   |                         |      | dB   |

| GBW                 | FG amplifier gain bandwidth product            |                                                                                      | 500  |                         |      | kHz  |

| V <sub>REF+</sub>   | FG comparator positive reference voltage       |                                                                                      | -20% | V <sub>VREG</sub> / 2   | 20%  | V    |

| V <sub>IT+</sub>    | FG comparator positive threshold               |                                                                                      | -20% | V <sub>VREG</sub> / 1.8 | 20%  | V    |

| V <sub>IT-</sub>    | FG comparator negative threshold               |                                                                                      | -20% | V <sub>VREG</sub> / 2   | 20%  | V    |

|                     | ENSOR INPUTS                                   |                                                                                      |      | VILO .                  |      |      |

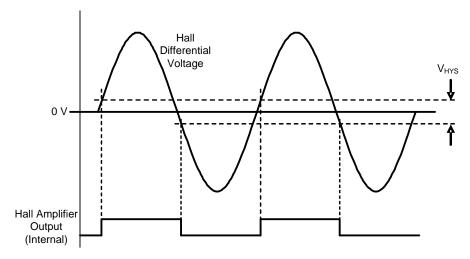

| V <sub>HYS</sub>    | Hall amplifier hysteresis voltage              |                                                                                      | 15   | 20                      | 25   | mV   |

| ΔV <sub>HYS</sub>   | Hall amplifier hysteresis difference           | Between U, V, W                                                                      |      |                         | 5    | mV   |

| V <sub>ID</sub>     | Hall amplifier input differential              |                                                                                      | 50   |                         | 3    | mV   |

| V <sub>CM</sub>     | Hall amplifier input common mode voltage range |                                                                                      | 1.5  |                         | 3.5  | V    |

|                     | Input leakage current                          | H_x+ = H_x-                                                                          | -10  |                         | 10   | μА   |

| I <sub>IN</sub>     |                                                | 11_^1 - 11_^-                                                                        | -10  | 20                      | 10   | •    |

| t <sub>HDEG</sub>   | Hall deglitch time                             |                                                                                      |      | 20                      |      | μS   |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                                                                        | PARAMETER                                                                  | TEST CONDITIONS                   | MIN   | TYP     | MAX   | UNIT |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------|-------|---------|-------|------|

| MOSFET D                                                                               | RIVERS                                                                     |                                   |       |         |       |      |

| V <sub>OUTH</sub>                                                                      | High-side gate drive output voltage                                        | I <sub>O</sub> = 100 μA, VM ≥ 12V |       | VM + 10 |       | V    |

| V <sub>OUTL</sub>                                                                      | Low-side gate drive output voltage                                         | $I_{O} = 100 \mu A$               |       | 10      |       | V    |

|                                                                                        |                                                                            | IDRIVE = 000                      |       | 10      |       |      |

|                                                                                        |                                                                            | IDRIVE = 001                      |       | 20      |       |      |

|                                                                                        |                                                                            | IDRIVE = 010                      |       | 30      |       |      |

|                                                                                        | Deals note drive assument                                                  | IDRIVE = 011                      |       | 50      |       | ^    |

| OUT                                                                                    | Peak gate drive current                                                    | IDRIVE = 100                      |       | 90      |       | mA   |

|                                                                                        |                                                                            | IDRIVE = 101                      |       | 100     |       |      |

| VOUTL  CYCLE-BY- VLIMITER  tblank  PROTECTIO VSENSEOCP  tocp  tucce Vuvlo Vovlo tretry |                                                                            | IDRIVE = 110                      |       | 110     |       |      |

|                                                                                        |                                                                            | IDRIVE = 111                      |       | 130     |       |      |

| CYCLE-BY                                                                               | -CYCLE CURRENT LIMITER                                                     |                                   |       |         |       |      |

| V <sub>LIMITER</sub>                                                                   | Voltage limit across R <sub>ISENSE</sub> for the current limiter           |                                   | 0.225 | 0.25    | 0.275 | V    |

|                                                                                        | Time that $V_{\text{LIMITER}}$ is ignored, from the start of the PWM cycle | OCPDEG = 00                       |       | 2       |       | μs   |

|                                                                                        |                                                                            | OCPDEG = 01                       |       | 3       |       |      |

|                                                                                        |                                                                            | OCPDEG = 10                       |       | 3.75    |       |      |

|                                                                                        |                                                                            | OCPDEG = 11                       |       | 6       |       |      |

| PROTECTI                                                                               | ON CIRCUITS                                                                |                                   |       |         |       |      |

| V <sub>SENSEOCP</sub>                                                                  | Voltage limit across R <sub>ISENSE</sub> for overcurrent protection        |                                   | 1.7   | 1.8     | 1.9   | V    |

|                                                                                        |                                                                            | OCPTH = 00                        | 200   | 250     | 400   | mV   |

| M                                                                                      | Voltage limit across each external FET's drain                             | OCPTH = 01                        | 400   | 500     | 600   |      |

| VLIMITER   1  tBLANK t  PROTECTIO  VSENSEOCP   1  VFETOCP t  tOCP t                    | to source for overcurrent protection                                       | OCPTH = 10                        | 600   | 750     | 850   |      |

|                                                                                        |                                                                            | OCPTH = 11                        | 850   | 1000    | 1200  |      |

|                                                                                        |                                                                            | OCPDEG = 00                       |       | 1.6     |       |      |

|                                                                                        | Deglitch time for V <sub>SENSEOCP</sub> or V <sub>FETOCP</sub> to          | OCPDEG = 01                       |       | 2.3     |       |      |

| CYCLE-BY- VLIMITER  tblank  PROTECTIO VSENSEOCP  tocp  tull Vovlo Vovlo tretry Ttsd    | trigger                                                                    | OCPDEG = 10                       |       | 3       |       | μs   |

|                                                                                        |                                                                            | OCPDEG = 11                       |       | 5       |       |      |

| V                                                                                      | VM undervoltege leeke: t                                                   | VM rising                         |       | 8       |       | V    |

| VUVLO                                                                                  | VM undervoltage lockout                                                    | VM falling                        |       | 7.8     |       | V    |

| V                                                                                      | VM even eltere leekeut                                                     | VM rising, OVTH = 0               | 32    | 34.5    | 36    | \ /  |

| VOVLO                                                                                  | VM overvoltage lockout                                                     | VM rising, OVTH = 1               |       | 28      | 29    | V    |

| t <sub>RETRY</sub>                                                                     | Fault retry time after OTS                                                 | RETRY = 1                         |       | 5       |       | s    |

|                                                                                        | Thermal shutdown die temperature                                           |                                   | 150   | 160     |       | °C   |

| V <sub>CPFAIL</sub>                                                                    | VCP failure threshold (CPFAIL bit)                                         |                                   |       | VM + 3  |       | V    |

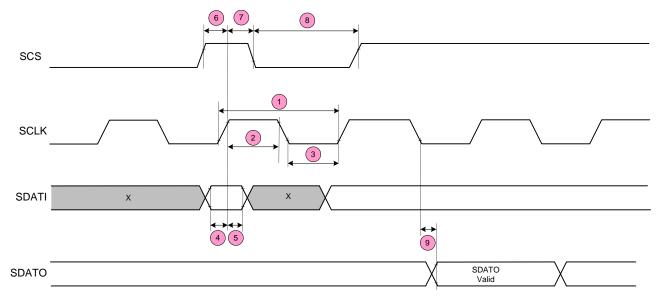

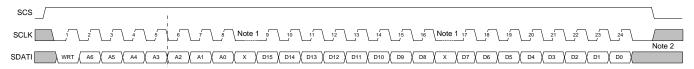

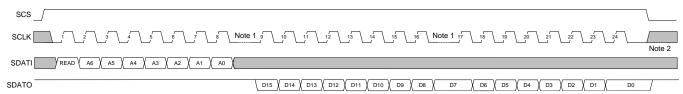

# 6.6 SPI Timing Requirements

$T_A = 25$ °C, over recommended operating conditions unless otherwise noted  $^{(1)}$

| NUMBER (2) |                        |                                                                    | MIN | MAX | UNIT |

|------------|------------------------|--------------------------------------------------------------------|-----|-----|------|

| 1          | t <sub>CYC</sub>       | Clock cycle time                                                   | 62  |     |      |

| 2          | t <sub>CLKH</sub>      | Clock high time                                                    | 25  |     |      |

| 3          | t <sub>CLKL</sub>      | Clock low time                                                     | 25  |     |      |

| 4          | t <sub>SU(SDATI)</sub> | Setup time, SDATI to SCLK                                          | 5   |     |      |

| 5          | t <sub>H(SDATI)</sub>  | Hold time, SDATI to SCLK                                           | 1   |     | ns   |

| 6          | t <sub>SU(SCS)</sub>   | Setup time, SCS to SCLK                                            | 5   |     |      |

| 7          | t <sub>H(SCS)</sub>    | Hold time, SCS to SCLK                                             | 1   |     |      |

| 8          | $t_{L(SCS)}$           | Inactive time, SCS (between writes)                                | 100 |     |      |

| 9          | t <sub>D(SDATO)</sub>  | Delay time, SCLK to SDATO (during read)                            |     | 10  |      |

|            | t <sub>AWAKE</sub>     | Wake time (ENABLE active to high-side gate drive enabled)          |     | 1   | ms   |

|            | t <sub>SPI</sub>       | Delay from power-up or RESET low until serial interface functional |     | 10  | μS   |

- (1) SMODE = Low

- (2) These numbers refer to the corresponding number in Figure 1

Figure 1. SPI Timing Requirements

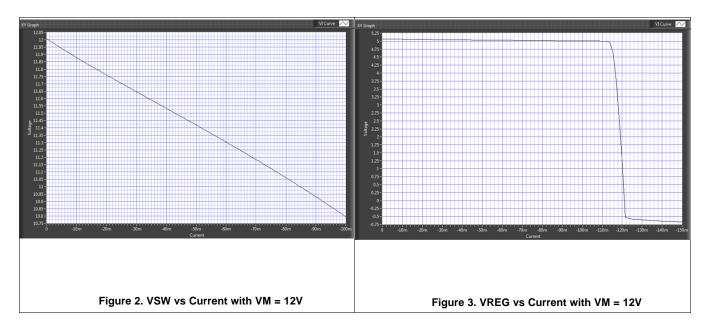

# 6.7 Typical Characteristics

## 7 Detailed Description

#### 7.1 Overview

The DRV8308 device controls 3-phase brushless DC motors using a speed and direction input interface and Hall signals from the motor. The device drives N-channel MOSFETs with 10-V  $V_{GS}$ , and a configurable gate drive current of 10 to 130 mA.

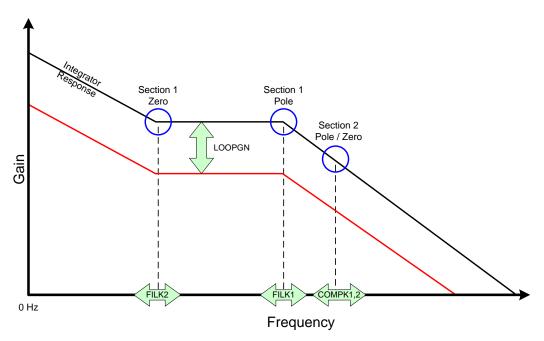

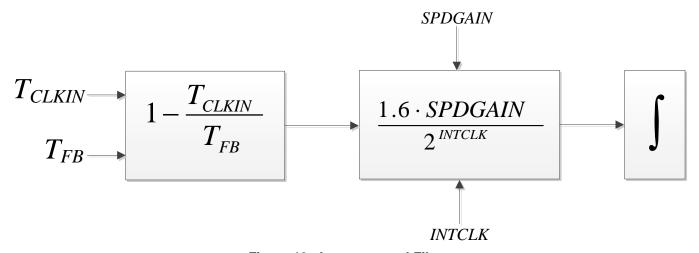

There are three modes of speed input: clock frequency, clock duty cycle (pulse-width modulation), and an internal register that specifies duty cycle. In the Clock Frequency Mode, the device's digital speed control system matches motor speed with the input clock's frequency. Motor speed is either determined from the Halls sensors or signal on the FG input, which can be generated from a board trace underneath the motor that senses magnetic reluctance. The speed control system offers digital tuning of pole and zero frequencies and integrator gain. When properly tuned, the DRV8308 can drive motors with < 0.1% cycle jitter and fast torque compensation for varying loads. The duty cycle speed modes operate in open-loop without speed control.

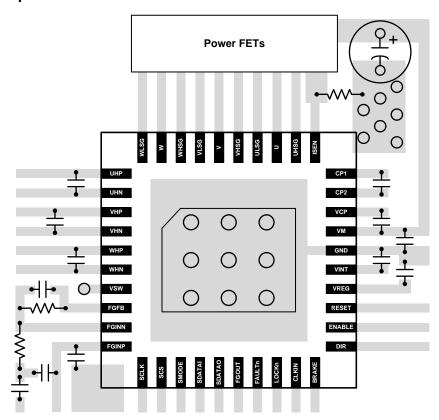

When the DRV8308 device powers up, the configuration registers are set from either the one-time programmable (OTP) non-volatile memory, or from an external EEPROM (depending on the SMODE pin). After power-up, registers can be set in realtime over SPI, and the OTP memory can be permanently written once.

When the DRV8308 device begins spinning a motor, it initially uses all three Hall sensor phases to commutate. After a constant speed is reached, the LOCKn pin is pulled low and only one Hall sensor becomes used; this feature reduces jitter by eliminating the error caused by non-ideal Hall device placement and matching. Also at this time, commutation transitions to sine wave current drive (if enabled), which minimizes acoustic noise and torque ripple. Commutation timing can be tuned using the ADVANCE register for optimal performance and power efficiency.

Numerous protection circuits prevent system components from being damaged during adverse conditions. Monitored aspects include motor voltage and current, gate drive voltage and current, and device temperature. When a fault occurs, the DRV8308 device stops driving and pulls FAULTn low, in order to prevent FET damage and motor overheating.

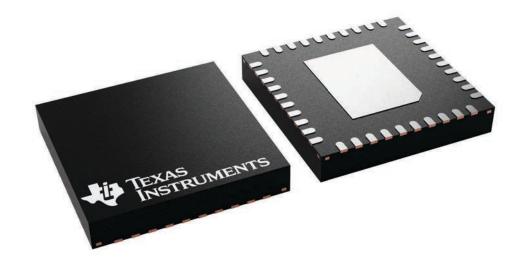

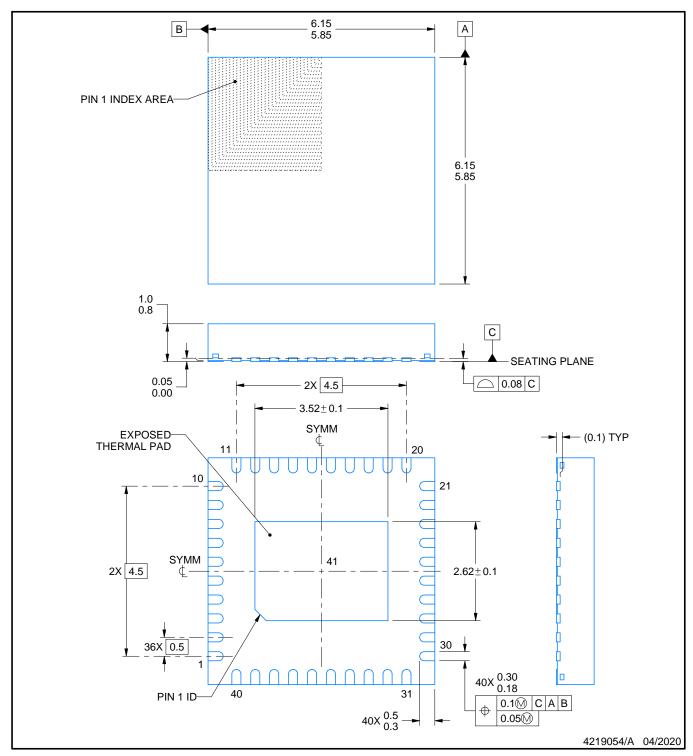

The DRV8308 device is packaged in a compact  $6 \times 6$ -mm, 40-pin QFN with a 0.5-mm pin pitch, and operates through an industrial ambient temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Hall Comparators

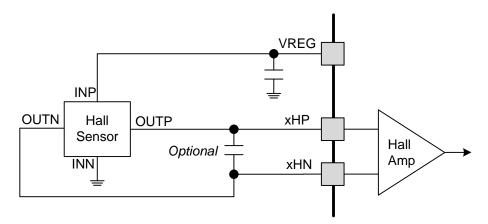

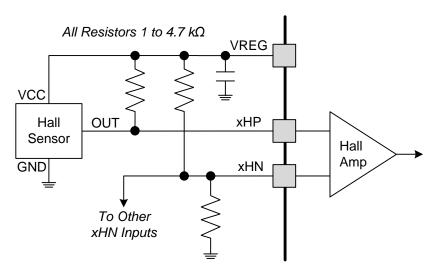

Three comparators are provided to process the raw signals from Hall effect transducers to commutate the motor. The Hall amplifiers sense zero crossings of the differential inputs and pass the information to digital logic.

The Hall amplifiers have hysteresis, and their detect threshold is centered at 0. Note, hysteresis is defined as shown in Figure 4:

Figure 4. Hall Amplifier Hysteresis

In addition to the hysteresis, the Hall inputs are deglitched with a circuit that ignores any extra Hall transitions for a period of 20  $\mu$ s after sensing a valid transition. This prevents PWM noise from being coupled into the Hall inputs, which can result in erroneous commutation.

If excessive noise is still coupled into the Hall comparator inputs, it may be necessary to add capacitors between the + and – inputs of the Hall comparators, and (or) between the input or inputs and ground.

The ESD protection circuitry on the Hall inputs implements a diode to VREG. Because of this diode, the voltage on the Hall inputs should not exceed the VREG voltage.

Since VREG is disabled in standby mode (ENABLE inactive), the Hall inputs should not be driven by external voltages in standby mode. If the Hall sensors are powered from VREG or from VSW, this is specified by the DRV8308 device; however, if the Hall sensors are powered externally, they should be disabled if the DRV8308 is put into standby mode. In addition, they should be powered-up before enabling the motor, or an invalid Hall state may cause a delay in motor operation.

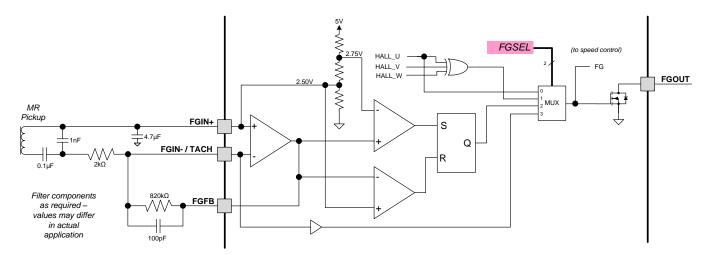

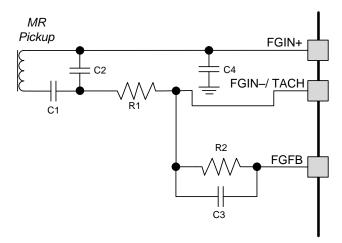

## 7.3.2 FG Amplifier, Comparator, and FG Output

An FG amplifier and comparator provide rotational feedback from an external magnetic reluctance sensor. A diagram of the FG circuit is shown in Figure 5:

## **Feature Description (continued)**

Figure 5. FG Circuit Diagram

The output of the FG amplifier is provided on a pin, so the gain of the FG amplifier can be set by the user. Filter circuits can also be implemented.

Note that the FG signal is also fed back internally to the speed control circuits.

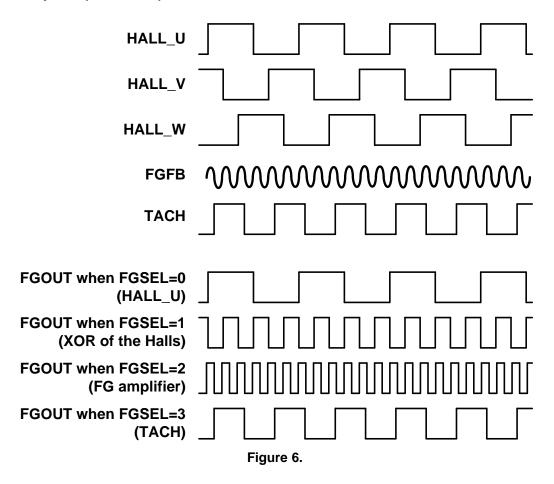

The FG signal that the DRV8308 device uses can be generated from a PCB trace under a motor, or it can be input from a logic-level TACH input, or it can be synthesized from the Hall sensor transitions (selectable by register FGSEL). If generated from Hall transitions, the resulting output can be either an exclusive-or function of the three Hall sensors, or the same as the HALL\_U input, as shown in Figure 6.

Selection of FG operating mode is through the FGSEL register bits.

The FGOUT pin is an open-drain output and requires an external pullup resistor to the logic supply.

# TEXAS INSTRUMENTS

## **Feature Description (continued)**

#### 7.3.3 Enable, Reset, and Clock Generation

The ENABLE pin is used to start and stop motor operation. ENABLE can be programmed to be active high or active low, depending on the state of the ENPOL bit; if ENPOL = 0, ENABLE is active high. If ENPOL = 1, the ENABLE pin is active low.

The polarity of ENABLE cannot be modified during operation through register writes; it is controlled only by the contents of the ENPOL bit in OTP memory.

When ENABLE is active, operation of the motor is enabled. When ENABLE is made inactive, the speed control loop is reset, and the motor either brakes or coasts depending on the state of the BRKMOD bit. After motor rotation has stopped (when no transitions occur on the FGOUT pin for a period of 1 s), the DRV8308 device enters a low-power standby state. In the standby state, the motor driver circuitry is disabled (all gate drive outputs are driven low, so the FET outputs are high-impedance), the gate drive regulator and charge pump are disabled, the VREG regulator and VSW power switch are disabled, and all analog circuitry is placed into a low power state. The digital circuitry in the device still operates in standby mode.

All internal logic is reset in three different ways:

- 1. Upon device power-up.

- 2. When VM drops below V<sub>RESET</sub>.

- 3. When the RESET pin is high while ENABLE is active.

If RESET is high while ENABLE is inactive, then the registers read as 1. If the RESET pin is not needed, it can be connected to GND. The RESET input is deglitched with a 10-µs timer on assertion and deassertion.

An internal clock generator provides all timing for the DRV8308 device. The master oscillator runs at 100 MHz. This clock is divided to a nominal 50-MHz frequency that clocks the remainder of the digital logic.

## **Feature Description (continued)**

#### 7.3.4 Commutation

For 3-phase brushless DC motors, rotor position feedback is provided from Hall effect transducers mounted on the motor. These transducers provide three overlapping signals, each 60° apart. The windings are energized in accordance with the signals from the Hall sensors to cause the motor to move.

In addition to the Hall sensor inputs, commutation is affected by a direction control, which alters the direction of motion by reversing the commutation sequence. Control of commutation direction is by the DIRPOL register bit as well as the DIR input pin. The DIRPOL register bit is combined with the pin with an exclusive-OR function as follows:

**DIR PIN DIRPOL REGISTER BIT RESULTING DIR FOR** COMMUTATION 0 n O 0 1 1 1 0 1 0 1 1

**Table 1. Direction Behavior**

If the commanded direction is changed while the motor is still spinning, this may cause excessive current flow in the output stage.

The DRV8308 device supports three commutation modes: standard 120° commutation using three Hall sensors, 120° commutation using a single Hall sensor, and 180° sine-wave-drive commutation.

In standard 120° commutation, mis-positioning of the Hall sensors can cause motor noise, vibration, and torque ripple. 120° commutation using a single Hall sensor (single-Hall commutation) can improve motor torque ripple and vibration because it relies on only one Hall edge for timing.

180° sine-wave-drive commutation is even more advanced, and excites the windings with a waveform that delivers nearly sinusoidal current to each winding.

#### 7.3.4.1 120° 3-Hall Commutation

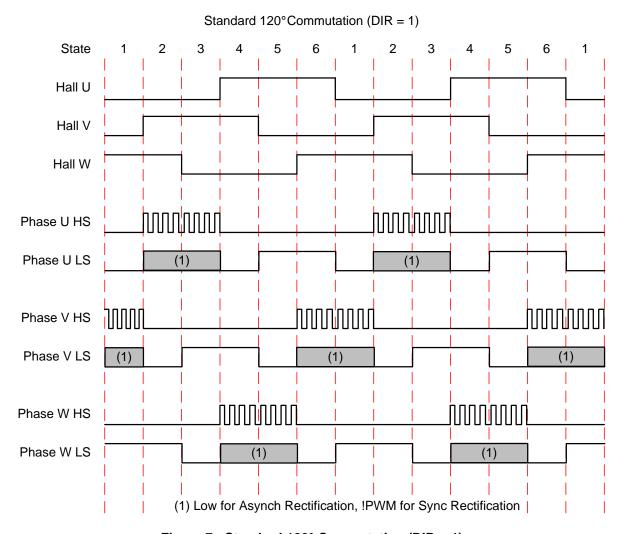

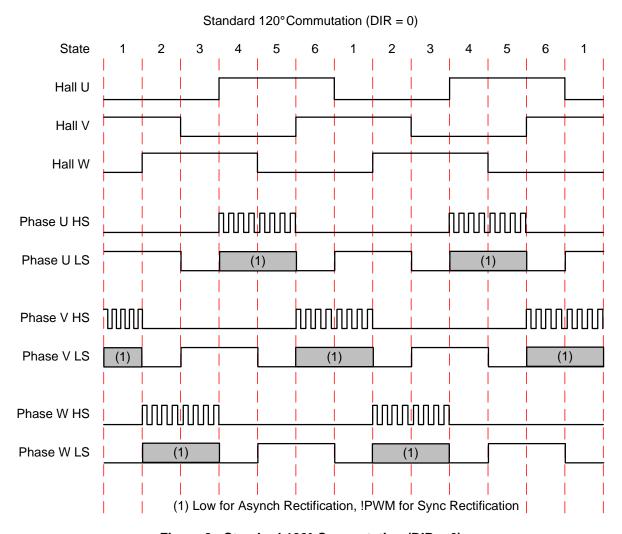

In standard 120° commutation, the motor phases are energized using simple combination logic based on all three Hall sensor inputs. Standard 120° commutation is in accordance with Table 2, Figure 7, and Figure 8:

| Table 2. Standard 120° Commutation | Table 2 | . Standard | 120° | Commutation <sup>(1</sup> |

|------------------------------------|---------|------------|------|---------------------------|

|------------------------------------|---------|------------|------|---------------------------|

|       | HALL INPUTS |       |     |     |         |     | PRE-DRIVE OUTPUTS |                         |          |                         |          |                         |

|-------|-------------|-------|-----|-----|---------|-----|-------------------|-------------------------|----------|-------------------------|----------|-------------------------|

| STATE |             | DIR = | 1   |     | DIR = 0 | )   | PHA               | ASE U                   | PHA      | ASE V                   | PHA      | SE W                    |

|       | U_H         | V_H   | W_H | U_H | V_H     | W_H | U_HSGATE          | U_LSGATE                | V_HSGATE | V_LSGATE                | W_HSGATE | W_LSGATE                |

| 1     | L           | L     | Н   | Н   | Н       | L   | L                 | L                       | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |

| 2     | L           | Н     | Н   | Н   | L       | L   | PWM               | L / !PWM <sup>(2)</sup> | L        | L                       | L        | Н                       |

| 3     | L           | Н     | L   | Н   | L       | Н   | PWM               | L / !PWM <sup>(2)</sup> | L        | Н                       | L        | L                       |

| 4     | Н           | Н     | L   | L   | L       | Н   | L                 | L                       | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |

| 5     | Н           | L     | L   | L   | Н       | Н   | L                 | Н                       | L        | L                       | PWM      | L / !PWM <sup>(2)</sup> |

| 6     | Н           | L     | Н   | L   | Н       | L   | L                 | Н                       | PWM      | L / !PWM <sup>(2)</sup> | L        | L                       |

| 1X    | Н           | Н     | Н   | L   | L       | L   | L                 | L                       | L        | L                       | L        | L                       |

| 2X    | L           | L     | L   | Н   | Н       | Н   | L                 | L                       | L        | L                       | L        | L                       |

<sup>(1)</sup> Hall sensor is "H" if the positive input pin voltage is higher than the negative input pin voltage. States 1X and 2X are illegal input combinations

<sup>(2)</sup> During states where the phase is driven with a PWM signal, using asynchronous rectification, the LS gate is held off (L); using synchronous rectification, the LS gate is driven with the inverse of the HS gate.

Figure 7. Standard 120° Commutation (DIR = 1)

Figure 8. Standard 120° Commutation (DIR = 0)

## 7.3.4.2 120° Single-Hall Commutation

To generate commutation timing for single-Hall commutation, a digital timer is used to create a clock that runs at 960x the Hall sensor frequency. Only one Hall sensor input, HALL\_U, is used for commutation; this eliminates any torque ripple caused by mechanical or electrical offsets of individual Hall sensors.

Single-Hall commutation is only enabled when the register BASIC = 0 and the motor is operating at a nearly constant speed or speed-locked condition. To control this function, logic is used to determine when the speed is constant and the speed control loop is locked. This logic generates the LOCK signal. The LOCK signal is also output on the LOCKn pin.

Except in PWM input modes, LOCK is also prevented from being signaled if the speed control loop integrator is saturated (either at 0 or full-scale), which indicates that the speed control loop is not locked.

Until LOCK goes active (for example, at start-up, stop, or application of a sudden load that causes motor speed to drop very quickly), standard 120° commutation is used. Because of this, three Hall sensors are required regardless of which commutation method is used.

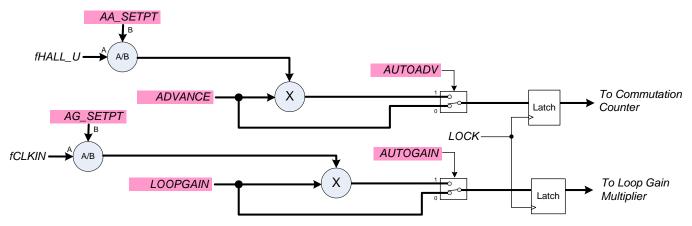

The commutation timer drives a counter that can be offset with a value programmed in the ADVANCE register. This value allows the phase of commutation to be shifted relative to the actual Hall sensor transitions. Note that the phase advance is not functional in standard 120° commutation. The phase advance also has an automatic mode where the advance value is scaled according to motor speed (see *Auto Gain and Advance Compensation*).

Timing of 120° single-Hall commutation is essentially the same as standard 120° commutation shown previously. However, there are small time differences of when the transitions occur.

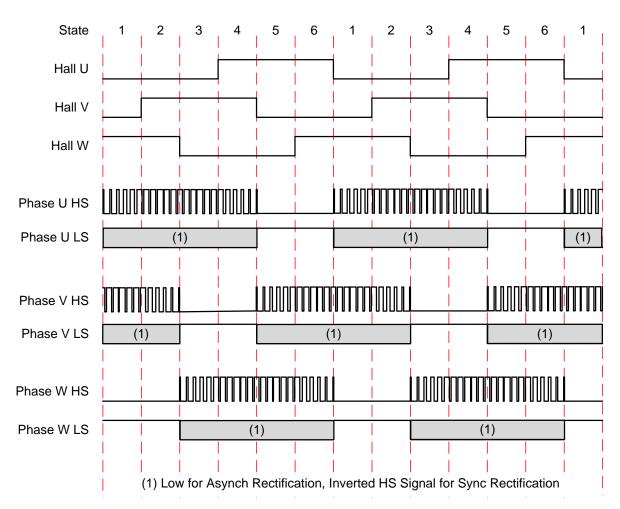

#### 7.3.4.3 180° Sine-Wave-Drive Commutation

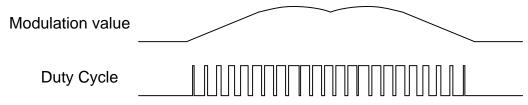

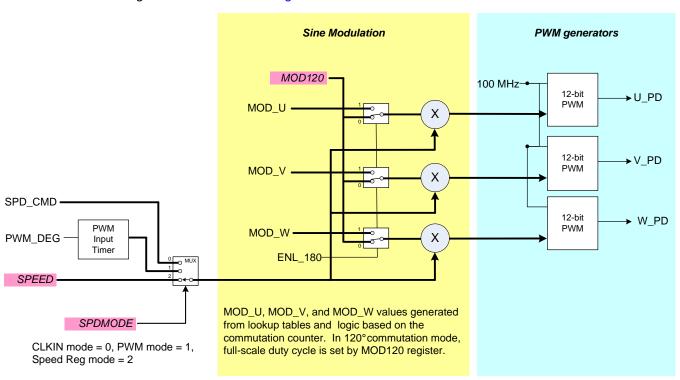

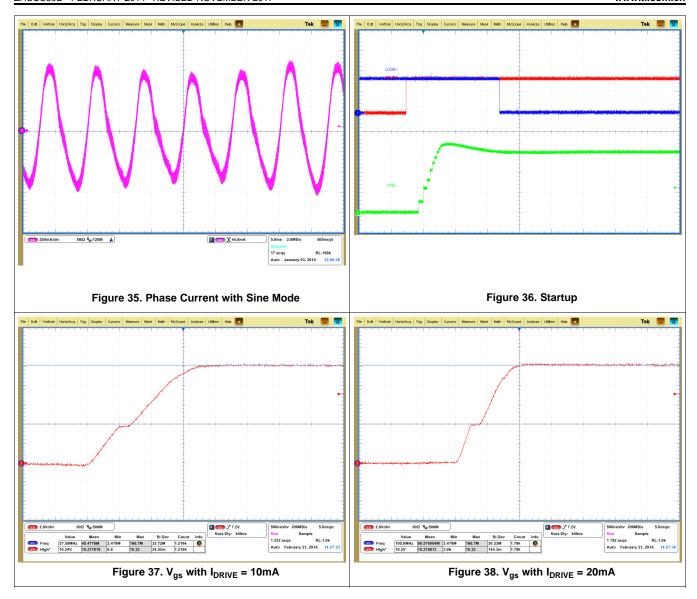

180° sine-wave-drive commutation uses a single Hall sensor to generate commutation timing, as described for 120° single-Hall commutation. In addition, the value of the commutation timer modulates the duty cycle of the outputs in accordance with a fixed pattern that approximates sinusoidal current through the windings.

The output of the commutation block is a 12-bit modulation value for each motor phase (U, V, and W) that represents the duty cycle modulation of the PWM for each output. Note that during 120° commutation, these values are either 0 or set to a constant value derived from the MOD120 register.

When using sine mode, MOD120 should be set to 3970.

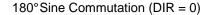

Figure 9. 180° Sine-Wave-Drive Commutation

During 180° sine-wave-drive commutation, commutation transitions occur midway between Hall transitions. The PWM duty cycle is modulated to provide sinusoidal current waveforms. Commutation (shown for asynchronous rectification) is in accordance with the table and diagrams below. Note that the diagrams show a representation of duty cycle, not level, for the PWM states.

Table 3. Commutation for Asynchronous Rectification<sup>(1)</sup>

|       | HALL INPUTS |         |     |     |         |     | PRE-DRIVE OUTPUTS |                         |          |                         |          |                         |

|-------|-------------|---------|-----|-----|---------|-----|-------------------|-------------------------|----------|-------------------------|----------|-------------------------|

| STATE |             | DIR = 1 |     |     | DIR = 0 |     | PHA               | SE U                    | PHA      | ASE V                   | PHAS     | SE W                    |

|       | U_H         | V_H     | W_H | U_H | V_H     | W_H | U_HSGATE          | U_LSGATE                | V_HSGATE | V_LSGATE                | W_HSGATE | W_LSGATE                |

| 1     | L           | L       | Н   | Н   | Н       | L   | PWM               | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |

| 2     | L           | Н       | Н   | Н   | L       | L   | PWM               | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |

| 3     | L           | Н       | L   | Н   | L       | Н   | PWM               | L / !PWM <sup>(2)</sup> | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |

| 4     | Н           | Н       | L   | L   | L       | Н   | PWM               | L / !PWM <sup>(2)</sup> | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |

| 5     | Н           | L       | L   | L   | Н       | Н   | L                 | Н                       | PWM      | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> |

| 6     | Н           | L       | Н   | L   | Н       | L   | L                 | Н                       | PWM      | L / !PWM <sup>(2)</sup> | L        | L / !PWM <sup>(2)</sup> |

| 1X    | Н           | Н       | Н   | L   | L       | L   | L                 | L                       | L        | L                       | L        | L                       |

| 2X    | L           | L       | L   | Н   | Н       | Н   | L                 | L                       | L        | L                       | L        | L                       |

<sup>(1)</sup> Hall sensor is "H" if the positive input pin voltage is higher than the negative input pin voltage. States 1X and 2X are illegal input combinations.

<sup>(2)</sup> During states where the phase is driven with a PWM signal, using asynchronous rectification, the LS gate is held off (L); using synchronous rectification, the LS gate is driven with the inverse of the HS gate.

## 180°Sine Commutation (DIR = 1)

Figure 10. 180° Sine Commutation (DIR = 1)

Figure 11. 180° Sine Commutation (DIR = 0)

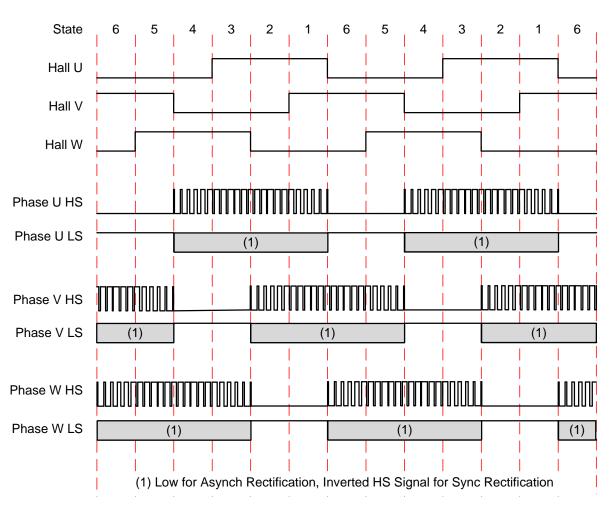

## 7.3.5 Commutation Logic Block Diagram

A block diagram of the commutation logic is shown in Figure 12.

Figure 12. Commutation Logic

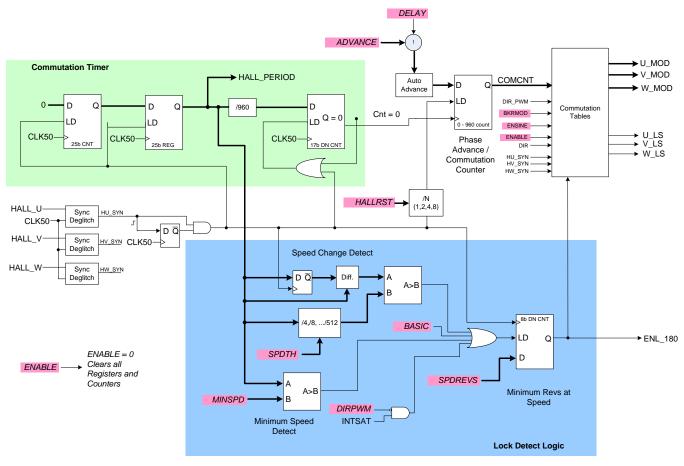

#### 7.3.6 Commutation Parameters

A number of commutation parameters are programmable through registers accessed through the serial interface, including:

- ADVANCE The phase of commutation is advanced (or delayed) relative to the Hall sensor transition by this 8-bit amount. Units are in commutation clocks, which is 1 / 960 of the HALL\_U period. Note that phase advance is only applicable in single-Hall commutation modes. An automatic phase advance compensation mode can also be enabled by the AUTOADV bit (see *Auto Gain and Advance Compensation* for details).

- DELAY if set, commutation is delayed relative to Hall transitions; if cleared, commutation is advanced relative to Hall transitions.

- BASIC If set, commutation is a basic 120° 3-Hall mode with no ADVANCE.

- ENSINE The ENSINE bit, when set, selects 180° sinusoidal commutation. The BASIC bit must also be 0.

- HALLRST HALLRST sets how many HALL\_U cycles pass for each commutation counter reset. In other

words, the commutation counter is reset every N HALL\_U edges. Selections available are 1, 2, 4, and 8.

- MINSPD Sets the minimum Hall\_U period that LOCK can be set. The 8-bit field represents 2.56 ms/count, with a max value of 652.8 ms.

- SPDREVS After the MINSPD and SPEEDTH criteria are met, SPDREVS adds a minimum number of Hall\_U periods that must occur for LOCK to be set.

- SPEEDTH Sets how much speed variation is allowed across Hall\_U periods while keeping LOCK set. This 3-bit field sets the percentage variation allowed by changing a programmable divider. Divisions of 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, and 1/512 are supported. These divisors correspond to 25%, 12.5%, 6.25%,

- 3.13%, 1.56%, 0.78%, 0.39%, and 0.20% variation per revolution.

- SPEED In the Internal Register PWM Mode, SPEED divided by 4095 sets the input duty cycle. In Clock Frequency Mode, SPEED sets the open-loop gain during spin-up before LOCKn goes Low.

The diagram below shows how the lock parameters (MINSPD, SPEEDTH, and SPDREV) affect commutation mode.

Figure 13. Commutation Parameters

#### 7.3.7 Braking

Motor braking can be initiated by the BRKPOL register bit as well as the BRAKE pin. The BRKPOL register bit can also be used to program the polarity of the BRAKE pin, as it is combined with the pin with an exclusive-OR function as follows:

Table 4. Brake Behavior

| BRAKE PIN | BRKPOL REGISTER<br>BIT | RESULTING<br>FUNCTION |

|-----------|------------------------|-----------------------|

| 0         | 0                      | Not brake             |

| 0         | 1                      | Brake                 |

| 1         | 0                      | Brake                 |

| 1         | 1                      | Not brake             |

When the motor is braking, all low-side drivers are held in an on state, causing all low-side FETs to turn on, and the integrator is reset to 0.

In addition, braking can be entered when the ENABLE pin is made inactive. BRKMOD controls the behavior of the outputs when ENABLE is inactive. If BRKMOD= 0, the outputs are 3-stated, resulting in the motor coasting; if BRKMOD = 1, all low-side FETs are turned on, causing the motor to brake.

| Tab     | 5 ما   | RR                     | KМ     |     | ١ |

|---------|--------|------------------------|--------|-----|---|

| 1 4 1 1 | IC :). | $\mathbf{D}\mathbf{D}$ | rs ivi | L)L | , |

|                   | BRKMOD = 0<br>COAST | BRKMOD = 1<br>BRAKE |

|-------------------|---------------------|---------------------|

| RESET = 1         | Coast               | Brake               |

| BRAKE = active    | Brake               | Brake               |

| ENABLE = inactive | Coast               | Brake               |

| DIR               | Coast               | Brake               |

| Clock off         | Brake               | Brake               |

| Power down        | Coast               | Brake               |

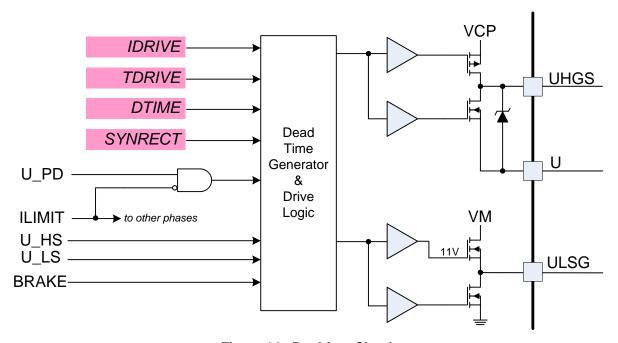

## 7.3.8 Output Pre-Drivers

The output drivers for each phase consist of N-channel and P-channel MOSFET devices arranged as a CMOS buffer. They are designed to directly drive the gate of external N-channel power MOSFETs.

The outputs can provide synchronous or asynchronous rectification. In asynchronous rectification, only the high-side FET is turned on and off with the PWM signal; current is recirculated using external diodes, or the body diodes of the external FETs. In synchronous rectification, the low side FET is turned on when the high side is turned off.

Synchronous rectification is enabled or disabled using the SYNRECT control bit. When set to 1, synchronous rectification is used. In general, synchronous rectification results in better speed control and higher efficiency.

The high-side gate drive output UHSG is driven to VCP whenever the duty cycle output U\_PD from the PWM generator is high, the enable signal U\_HS from the commutation logic is active, and the current limit ( $V_{LIMITER}$ ) is not active. If the high-side FET is on and a current limit event occurs, the high-side FET is immediately turned off until the next PWM cycle.

The low-side gate drive ULSG is driven to VM whenever the internal signal U\_LS is high, or whenever synchronous rectification is active and UHSG is low.

Phases V and W operate in an identical fashion.

Figure 14. Predriver Circuit

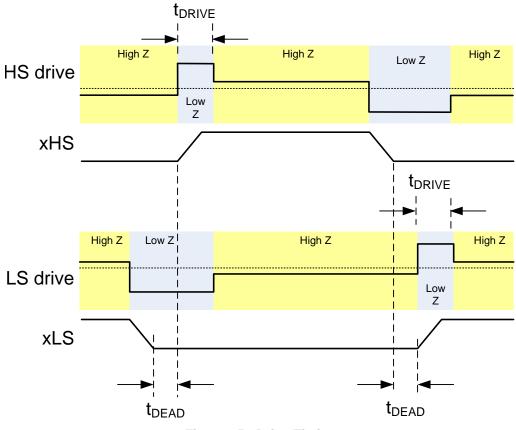

Figure 15. Drive Timing

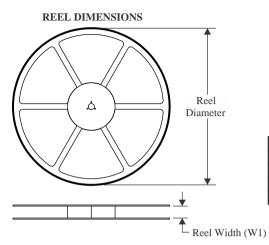

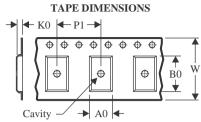

The peak drive current of the pre-drivers is adjustable by setting the IDRIVE register bits. Peak drive currents may be set between 10 and 130 mA. Adjusting the peak current changes the output slew rate, which also depends on the FET input capacitance and gate charge.

When changing the state of the output, the peak current is applied for a short period of time ( $t_{DRIVE}$ ), to charge the gate capacitance. This time is selected by setting the TDRIVE register bits. Times of 1, 5, 10, or 15  $\mu$ s may be selected. After this time, a weak current source is used to keep the gate at the desired state. When selecting the gate drive strength for a given external FET, the selected current must be high enough to fully charge and discharge the gate during the time when driven at full current, or excessive power is dissipated in the FET.

During high-side turn-on, the low-side gate is held low with a low impedance. This prevents the gate-source capacitance of the low-side FET from inducing turn-on. Similarly, during low-side turn-on, the high-side gate is held off with a low impedance.

The pre-driver circuits include enforcement of a dead time in analog circuitry, which prevents the high-side and low-side FETs from conducting at the same time. Additional dead time can be added (in digital logic) by setting the DTIME register bits.

#### 7.3.9 Current Limit

The current limit circuit activates if the voltage detected across the low-side sense resistor exceeds  $V_{LIMITER}$ . This feature restricts motor current to less than  $V_{LIMITER}/R_{ISENSE}$ , and it reduces the requirements of the external power supply. Note that the current limit circuit is ignored immediately after the PWM signal goes active for a short blanking time, to prevent false trips of the current limit circuit.

If current limit activates, the high-side FET is disabled until the beginning of the next PWM cycle. If synchronous rectification is enabled when the current limit activates, the low-side FET is activated while the high-side FET is disabled.

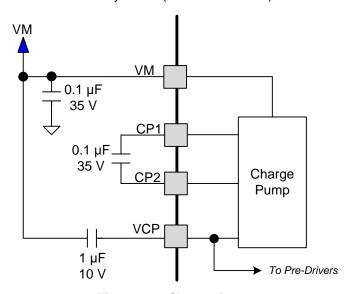

#### 7.3.10 Charge Pump

Since the output stages use N-channel FETs, a gate drive voltage higher than the VM power supply is needed to fully enhance the high-side FETS. The DRV8308 device integrates a charge pump circuit that generates a voltage approximately 10 V more than the VM supply for this purpose.

The charge pump requires two external capacitors for operation. For details on these capacitors (value, connection, and so forth), refer to the *Pin Functions* table in the *Pin Configurations and Functions* section.

The charge pump is shutdown when in standby mode (ENABLE inactive).

Figure 16. Charge Pump

#### 7.3.11 5-V Linear Regulator

A 5-V linear regulator (VREG) is provided to power internal logic and external circuitry, such as the Hall effect sensors.

A capacitor must be connected from the VREG output to ground, even if the output is not used for external circuitry. The recommended capacitor value is a 0.1- $\mu$ F, 10-V ceramic capacitor.

The VREG output is designed to provide up to 30-mA output current, but power dissipation and thermal conditions must be considered. As an example, with 24 V in and 20 mA out, power dissipated in the linear regulator is 19 V  $\times$  20 mA = 380 mW.

The VREG regulator is shutdown in standby mode (when ENABLE is inactive).

#### 7.3.12 Power Switch

A low-current switch is provided in the DRV8308 device that can be used to power the Hall sensors or other external circuitry through the VSW pin. When ENABLE is active the switch is turned on, connecting the VSW pin to VM. When ENABLE is inactive the switch is turned off (standby mode).

#### 7.3.13 Protection Circuits

A number of protection circuits are included in the DRV8308 device. Faults are reported by asserting the FAULTn pin (an active-low, open-drain output signal), as well as setting the appropriate bit or bits in the FAULT register. Note that bits in the FAULT register remain set until either a 0 is written to them, RESET is asserted, or the device power is cycled.

## 7.3.13.1 VM Undervoltage Lockout (UVLO)

If the VM power supply drops, there may not be enough voltage to fully turn on the output FETs. Operation in this condition causes excessive heating in the output FETs. To protect against this, the DRV8308 device contains an undervoltage lockout circuit.

In the event that the VM supply voltage drops below the undervoltage lockout threshold ( $V_{UVLO}$ ), the FAULTn pin is driven active and the motor driver is disabled. After VM returns to a voltage above the undervoltage lockout threshold, the FAULTn pin is high impedance and operation of the motor driver automatically resumes.

The UVLO bit in the FAULT register is set. This bit remains set until a 0 is written to the UVLO bit.

At power-up, the UVLO bit is set.

Note that register reads and writes are still possible during the UVLO condition, as long as VM stays above the VM reset threshold. If VM drops below the VM reset threshold, all registers are reset and register read or write is not functional.

## 7.3.13.2 VM Overvoltage (VMOV)

In some cases, if synchronous rectification is used, energy from the mechanical system can be forced back into the VM power supply. This can result in the VM power supply being boosted by the energy in the mechanical system, causing breakdown of the output FETs, or damaging the DRV8308 device. To protect against this, the DRV8308 device has overvoltage protection.

There are two overvoltage thresholds, selectable by the OVTH bit. An overvoltage event is recognized if the VM voltage exceeds the selected overvoltage threshold ( $VM_{OVLO}$ ). Note that for the output FETs to be protected, they must be rated for a voltage greater than the selected overvoltage threshold.

In the event of an overvoltage, the FAULTn pin is pulled low. If synchronous rectification is enabled, the output stage is forced into asynchronous rectification. After VM returns to a voltage below the overvoltage threshold, the FAULTn pin is high impedance. If synchronous rectification was enabled prior to the overvoltage event, after a fixed 60-µs delay, synchronous rectification is re-enabled.

The VMOV bit in the FAULT register is set. This bit remains set until a 0 is written to the VMOV bit.

## 7.3.13.3 Motor Overcurrent (OCP)

Overcurrent protection (OCP) is provided on each FET in addition to the current limit circuit. The OCP circuit is designed to protect the output FETs from atypical conditions such as a short circuit between the motor outputs and each other, power, or ground.

The OCP circuit is independent from the current limit circuitry. OCP works by monitoring the voltage drop across the external FETs when they are enabled. If the voltage across a driven FET exceeds  $V_{\text{FETOCP}}$  for more than  $t_{\text{OCP}}$  an OCP event is recognized.  $V_{\text{FETOCP}}$  is configurable by register OCPTH and  $t_{\text{OCP}}$  is configurable by register OCPDEG.

In addition to monitoring the voltage across the FETs, an OCP event is triggered if the voltage applied to the ISEN pin exceeds the  $V_{\text{SENSEOCP}}$  threshold voltage.

In the event of an OCP event, FAULTn is pulled low, and the motor driver is disabled.